# DC to VHF DIFFERENTIAL VIDEO AMPLIFIER

## **UPC1663GV**

#### **FEATURES**

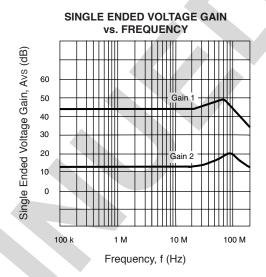

- BANDWIDTH AND TYPICAL GAIN:

- 120 MHz at AVOL = 300 170 MHz at AVOL = 100 700 MHz at AVOL = 10

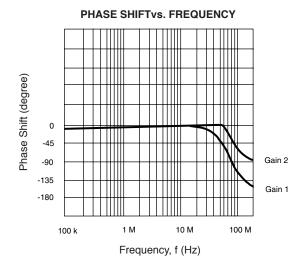

- VERY SMALL PHASE DELAY

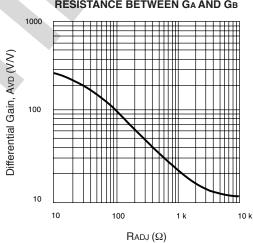

- GAIN ADJUSTABLE FROM 10 TO 300

- NO FREQUENCY COMPENSATION REQUIRED

#### **DESCRIPTION**

NEC's UPC1663GV is a video amplifier with differential input and output stages. A high frequency process (fr = 6 GHz) improves AC performance compared with industry-standard video amplifiers. This device is excellent as a sense amplifier for high-density CCDs, as a video or pulse amplifier in high-resolution displays, and in communications equipment.

#### **ELECTRICAL CHARACTERISTICS** (TA = 25°C, VCC = $\pm 6$ V, Rs = 50 $\Omega$ , f = 10 MHz)

| PART NUMBER PACKAGE OUTLINE |                                                                              |            | UPC1663GV<br>S08 |            |            |

|-----------------------------|------------------------------------------------------------------------------|------------|------------------|------------|------------|

| SYMBOLS                     | PARAMETERS AND CONDITIONS                                                    | UNITS      | MIN              | TYP        | MAX        |

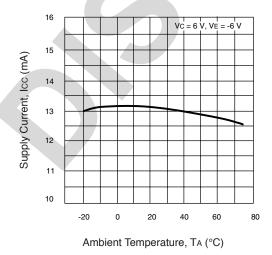

| Icc                         | Power Supply Current                                                         | mA         |                  | 13         | 20         |

| Avd                         | Differential Voltage Gain: Gain¹ Gain²                                       |            | 200<br>8         | 320<br>10  | 500<br>12  |

| BW                          | Bandwidth (Gain is 3 dB down Gain¹ from the gain at 100 KHz) Gain²           | MHz<br>MHz |                  | 120<br>700 |            |

| tr                          | Rise Time, Vout = $1V_{p-p}$ : Gain <sup>1</sup> Gain <sup>2</sup>           | ns<br>ns   |                  | 2.9<br>2.7 |            |

| <b>t</b> pd                 | Propagation Delay, Vout = 1 Vp-p: Gain¹ Gain²                                | ns<br>ns   |                  | 2<br>1.2   |            |

| Rın                         | Input Impedance: Gain¹ Gain²                                                 | kΩ<br>kΩ   | 50               | 4.0<br>180 |            |

| Cin                         | Input Capacitance                                                            | pF         |                  | 2          |            |

| lio                         | Input Offset Current                                                         | μА         |                  | 0.4        | 5.0        |

| lв                          | Input Bias Current                                                           | μА         |                  | 20         | 40         |

| Vn                          | Input Noise Voltage, 10 k to 10 MHz                                          | μVr.m.s.   |                  | 3          |            |

| Vı                          | Input Voltage Range                                                          | V          | ±1.0             |            |            |

| CMRR                        | Common Mode Rejection Ratio, Vcm = ±1 V, f ≤100 kHz<br>Vcm = ±1 V, f = 5 MHz | dB<br>dB   | 55<br>53         | 94<br>60   |            |

| SVRR                        | Supply Voltage Rejection Ratio, ∆V = ±0.5 V                                  | dB         | 50               | 70         |            |

| VO(off)                     | Output Offset Voltage, VO(off) = IOUT1 - OUT2I<br>Gain¹<br>Gain²             | V          |                  | 0.3<br>0.1 | 1.5<br>1.0 |

| Vo (CM)                     | Output Common Mode Voltage                                                   | V          | 2.4              | 2.9        | 3.4        |

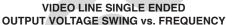

| V <sub>Op-p</sub>           | Max. Output Voltage Swing, Single-ended                                      | Vp-p       | 3.0              | 4.0        |            |

| İsink                       | Output Sink Current                                                          | mA         | 2.5              | 3.6        |            |

|                             | 1                                                                            |            |                  |            |            |

#### Notes:

- 1. Gain select pins GA and GB are connected together.

- 2. All gain select pins are open.

- 3. Insert adjustment resistor (0 to 10 k $\Omega$ ) between GA and GB when variable gain is necessary.

## **ABSOLUTE MAXIMUM RATINGS**<sup>1</sup> (TA = 25°C)

| SYMBOLS | PARAMETERS                           | UNITS | RATINGS     |

|---------|--------------------------------------|-------|-------------|

| Vc-VE   | Voltage between Vc and VE            | V     | -0.3 to 14  |

| Рт      | Total Power Dissipation <sup>2</sup> | mW    | 200         |

| VID     | Differential Input Voltage           | V     | ±5          |

| VIN     | Input Voltage                        | V     | ±6          |

| lo      | Output Current                       | mA    | 35          |

| Тор     | Operating Temperature                | °C    | -45 to +75  |

| Тѕтс    | Storage Temperature                  | °C    | -55 to +150 |

#### Notes:

- Operation in excess of any one of these parameters may result in permanent damage.

- Mounted on 50 cm x 50 cm x 1.6 mm glass epoxy PCB with copper film (Ta = Max Top).

## RECOMMENDED OPERATING CONDITIONS (TA = 25°C)

| SYMBOLS   | CHARACTERISTICS         | UNITS | MIN | TYP | MAX  |

|-----------|-------------------------|-------|-----|-----|------|

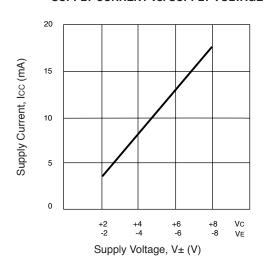

| Vc        | Positive Supply Voltage | V     | +2  | +6  | +6.5 |

| Ve        | Negative Supply Voltage | V     | -2  | -6  | -6.5 |

| IO source | Source Current          | mA    |     |     | 20   |

| IO sink   | Sink Current            | mA    |     |     | 2.5  |

|           | Frequency Range         | MHz   | DC  |     | 200  |

#### Attention:

Due to high frequency characteristics, the physical circuit layout is very critical. Supply voltage line bypass, double-sided printed-circuit board, and wide-area ground line layout are necessary for stable operation. Two signal resistors connected to both inputs and two load resistors connected to both outputs should be balanced for stable operation.

## TYPICAL PERFORMANCE CURVES (TA = 25°C)

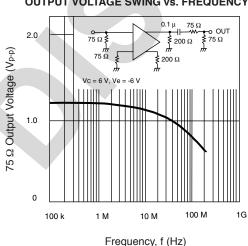

#### **EQUIVALENT CIRCUIT**

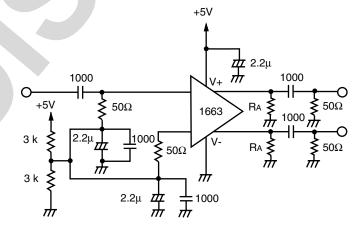

#### TYPICAL PERFORMANCE UNDER SIN-GLE SUPPLY +5 V OPERATION\*

| PARAMETER         | CONDITIONS                                     | TYPICAL | UNITS  |

|-------------------|------------------------------------------------|---------|--------|

| Differential Gain | 15 MHz                                         |         |        |

| Gain 1            |                                                | 35      | dB     |

| Gain 2            |                                                | 11      | dB     |

| Bandwidth         | Gain is 3 dB down from                         |         |        |

| Gain 1            | the gain at 100 KHz                            | 106     | MHz    |

| Gain 2            | _                                              | 115     | MHz    |

| Rise Time         | Rs = 50 $\Omega$ , Vout = 80 mV <sub>p-p</sub> |         |        |

| Gain 1            |                                                | 2.2     | ns     |

| Propagation       |                                                |         |        |

| Delay             |                                                |         |        |

| Gain 1            | RS = 50 $\Omega$ , Vout = 80 mVp-p             | 2.8     | ns     |

| Gain 2            | RS = 50 $\Omega$ , Vout = 60 mVp-p             | 1.8     | ns     |

| Phase Shift       | 100 MHz                                        |         |        |

| Gain 1            |                                                | -123    | degree |

| Gain 2            |                                                | -93     | degree |

| Output Power      | $ZL = 50 \Omega$ , 15 MHz                      |         |        |

| Ra = 240 Ω        |                                                | 5.0     | dBm    |

| Ra = 910 Ω        |                                                | 0       | dBm    |

| $R_A = 80 \Omega$ |                                                | -11.5   | dBm    |

<sup>\*</sup> See Application Circuit

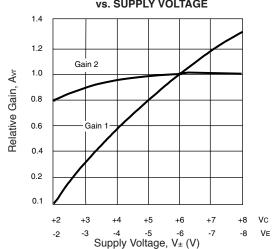

## NORMALIZED VOLTAGE GAIN vs. SUPPLY VOLTAGE

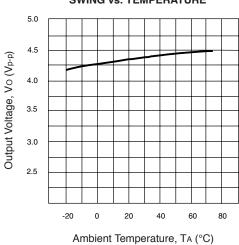

## TYPICAL PERFORMANCE CURVES (TA = 25°C)

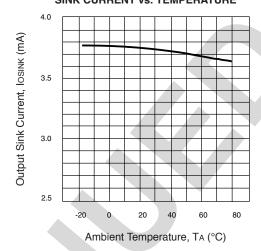

#### SINK CURRENT vs. TEMPERATURE

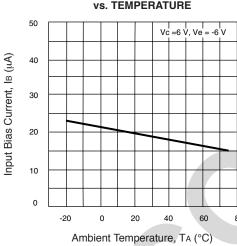

## INPUT BIAS CURRENT vs. TEMPERATURE

#### DIFFERENTIAL VOLTAGE GAIN vs. RESISTANCE BETWEEN GA AND GB

#### SUPPLY CURRENT vs. TEMPERATURE

#### SUPPLY CURRENT vs. SUPPLY VOLTAGE

## TYPICAL PERFORMANCE CURVES (TA = 25°C)

## **TYPICAL APPLICATIONS**

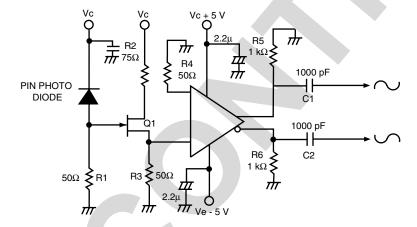

#### · Photo Signal Detector

Since the input impedance of the IC falls when the gain rises, stable operation can be achieved by inserting a FET buffer when necessary as illustrated above.

#### · Application for +5 V Single Supply

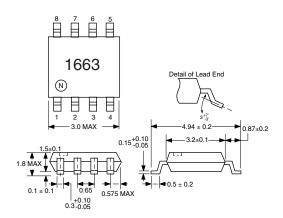

#### **OUTLINE DIMENSIONS** (Units in mm)

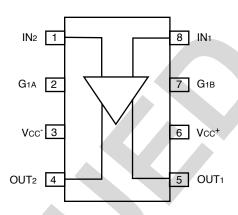

#### **CONNECTION DIAGRAM (TOP VIEW)**

#### UPC1663GV PACKAGE OUTLINE S08

#### Notes:

- Each lead centerline is located within 0.12 mm (0.005 inch) of its true position at maximum material condition.

- 2. All dimensions are typical unless otherwise specified.

#### UPC1663GV

#### **ORDERING INFORMATION**

| PART NUMBER    | QUANTITY  |

|----------------|-----------|

| UPC1663GV-E1-A | 1000/Reel |

#### PIN DESCRIPTION

| Pin<br>No. | Pin<br>Name      | In single<br>Bias<br>(V) | In single<br>bias<br>(V) | Functions and Applications                                                                              | Internal Equivalent Circuit                                       |

|------------|------------------|--------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 8          | IN <sub>1</sub>  | Pin                      | Apply                    | Input pin                                                                                               | 6                                                                 |

| 1          | IN <sub>2</sub>  | voltage                  | voltage                  |                                                                                                         |                                                                   |

|            |                  | 0                        | Vcc/2                    |                                                                                                         |                                                                   |

| 5          | OUT <sub>1</sub> | Pin                      | Apply                    | Output pin                                                                                              |                                                                   |

| 4          | OUT2             | voltage                  | voltage                  |                                                                                                         |                                                                   |

|            |                  | 0                        | Vcc/2                    |                                                                                                         | 8 <sub>2</sub>                                                    |

| 6          | Vcc+             | ±2 to ±6.5               | -0.3 to +14              | Plus voltage supply pin. This pin should be connected with bypass capacitor to minimize AC impedance.   |                                                                   |

| 3          | Vcc              |                          | GND                      | Minus voltage supply pin. This pin should be connected with bypass capacitor to minimize AC impedance.  | 3                                                                 |

| 7          | G1A              |                          | _                        | Gain adjustment pin.                                                                                    |                                                                   |

| 2          | G <sub>1</sub> B |                          |                          | External resistor from 0 to<br>10 kW can be inserted<br>between pin 2 and 7 to<br>determine gain value. | Internal circuit constants should be refered to application note. |

#### Life Support Applications

These NEC products are not intended for use in life support devices, appliances, or systems where the malfunction of these products can reasonably be expected to result in personal injury. The customers of CEL using or selling these products for use in such applications do so at their own risk and agree to fully indemnify CEL for all damages resulting from such improper use or sale.