# **EiceDRIVER**<sup>TM</sup>

## 2ED300C17-S 2ED300C17-ST

Dual IGBT Driver Board for Infineon Medium and High Power IGBT Modules

Power Management & Drives

#### 2ED300C17-S 2ED300C17-ST

| Revision History: |       | 2013-08                                          | V4.03 |  |  |

|-------------------|-------|--------------------------------------------------|-------|--|--|

| Previous Version: |       | V4.02                                            |       |  |  |

| Version Page      |       | Subjects (major changes since last revision)     |       |  |  |

| 4.03              | 2     | Revision history modified. All changes included. |       |  |  |

| 4.03              | 8; 18 | Figure 4 and figure7 size changed.               |       |  |  |

| 4.02              | 19    | Partial discharge test voltage added             |       |  |  |

| 4.02              |       | Chapter 4.5 and 4.6 added                        |       |  |  |

| 4.01              |       | Update figure 2 and figure 6                     |       |  |  |

| 4.00              | all   | General review, new hardware version V6          |       |  |  |

Edition 2013-08-13

Published by

Infineon Technologies AG

59568 Warstein, Germany

© Infineon Technologies AG 2013.

All Rights Reserved.

#### **ATTENTION PLEASE!**

THE INFORMATION HEREIN IS GIVEN TO DESCRIBE CERTAIN COMPONENTS AND SHALL NOT BE CONSIDERED AS A GUARANTEE OF CHARACTERISTICS.

TERMS OF DELIVERY AND RIGHTS TO TECHNICAL CHANGE RESERVED.

WE HEREBY DISCLAIM ANY AND ALL WARRANTIES, INCLUDING BUT NOT LIMITED TO WARRANTIES OF NON-INFRINGEMENT, REGARDING CIRCUITS, DESCRIPTIONS AND CHARTS STATED HEREIN.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## Safety notice

The driver may only be used for the purposes described by the manufacturer. Inadmissible alterations and use of spare parts or accessories not recommend by Infineon may cause fire, electric shock and injuries.

This document has to be available to all users, developers and qualified personnel working with the driver.

If measurements and tests on the device have to be carried out during operation, the regulations of the work on live parts are to be observed and suitable test equipment is to be used.

Prior to installation and commissioning please read this document thoroughly.

- Commissioning is prohibited if there is visible damage by inappropriate handling or transportation.

- Ensure ESD protection during handling.

- Connect or disconnect only when power is turned off.

- Always keep sufficient safety distance during commissioning without closed protective housing.

- Contact under live condition is strictly prohibited.

- Work after turn-off is impermissible until the absence of supply voltage has been verified.

- During work after turn-off it has to be observed that components heat up during operation. Contact can cause injuries.

- Electrically and mechanically, the driver is mounted onto customer's PCB by soldering. The mechanical strength has to be verified by the user and, if necessary, assured with appropriate tests.

- The driver is designed to be used in combination with Infineon IGBT modules, especially IHM, EconoPACK+, PrimePACK<sup>TM</sup> and 62mm. In case of ulterior use, safe operation cannot be ensured.

#### **Exclusion clause:**

The datasheet is part of the Infineon IGBT driver 2ED300C17-S/-ST. To ensure safe and reliable operation it is necessary to read and understand this datasheet.

The Infineon IGBT driver 2ED300C17-S/-ST is only intended for control of Infineon IGBT modules. Infineon cannot warrant against damage and/or malfunction if IGBT modules used not produced by Infineon. In this context, Infineon retains the right to change technical data and product specifications without prior notice to the course of improvement.

This side is intentionally left blank.

## Dual channel high voltage IGBT driver board

## **Product Highlights**

- · Galvanically isolated dual channel IGBT driver

- Reinforced isolation according to EN 50178

- Integrated protection features

- 5kV isolation test performed as 100% test

- High Electromagnetic Compatibility

#### **Features**

- Designed for Infineon IGBT modules up to 1700V

- High peak output current of 30A

- Integrated DC-DC SMPS

- Soft Shut Down in fault conditions

- Dynamic Over Current Detection

- IGBT desaturation monitoring

- Interlocking in half-bridge mode

- · Open drain fault output

- Low impedance 15V inputs for high noise immunity

- ±15 V secondary drive voltage

- · Short propagation delay time

- Optional sense function

- RoHS compliant

- UL94V-2 compliant materials

#### **Typical Applications**

- Renewable energies

- Drives and automation

- Transportation

- Power supplies

- Medical

- UPS systems

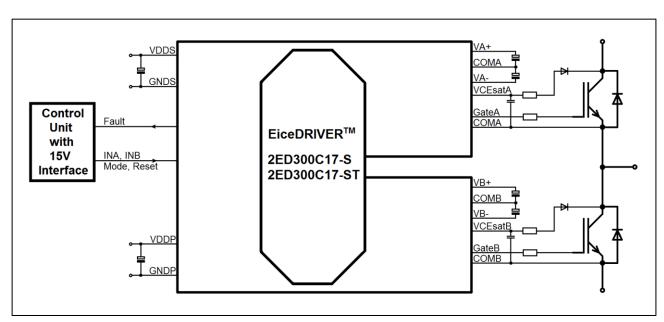

Figure 1: Basic schematic for driver setup

| Table of Contents |                                             |    |  |

|-------------------|---------------------------------------------|----|--|

| 1                 | Block Diagram and Schematic                 | 7  |  |

| 2                 | Functional Description                      | 8  |  |

| 2.1               | Reinforced Isolation                        | 8  |  |

| 2.2               | Integrated SMPS                             | 9  |  |

| 2.3               | Undervoltage Lockout (UVLO)                 |    |  |

| 2.4               | Dynamic Overcurrent Detection (DOCD)        |    |  |

| 2.5               | Soft Shut Down (SSD)                        | 9  |  |

| 2.6               | External Detected Failure Analysis (EDFA)   |    |  |

| 2.7               | Reset                                       |    |  |

| 2.8               | Control Inputs and Outputs 2ED300C17-S /-ST | 9  |  |

| 3                 | Pin Configuration and Functionality         | 10 |  |

| 3.1               | Pin functionalities, Primary side           |    |  |

| 3.2               | Pin functionalities, Secondary side         |    |  |

| 4                 | Electrical Parameters                       | 14 |  |

| 4.1               | Absolute Maximum Ratings                    |    |  |

| 4.2               | Operating Parameters                        | 15 |  |

| 4.3               | Recommended Operating Parameters            | 15 |  |

| 4.4               | Electrical Characteristics                  | 16 |  |

| 4.5               | Driver performance                          |    |  |

| 4.6               | VCESAT reference                            | 18 |  |

| 5                 | Isolation characteristics                   | 19 |  |

| 6                 | Timing diagrams                             | 20 |  |

| 7                 | Mechanical dimensions                       | 21 |  |

| 8                 | Handling and mounting                       | 23 |  |

#### **Block Diagram and Schematic**

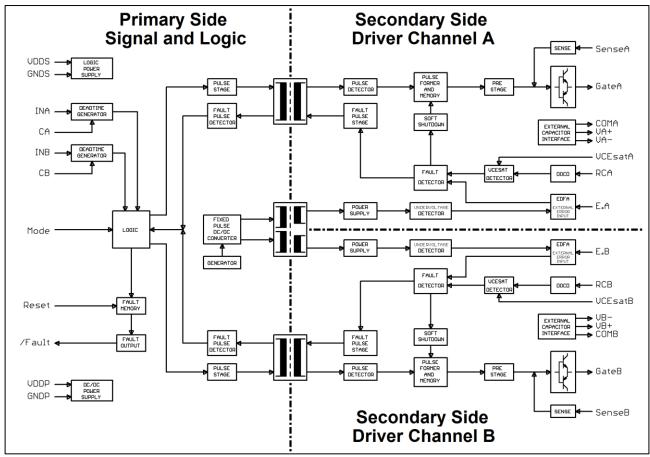

## 1 Block Diagram and Schematic

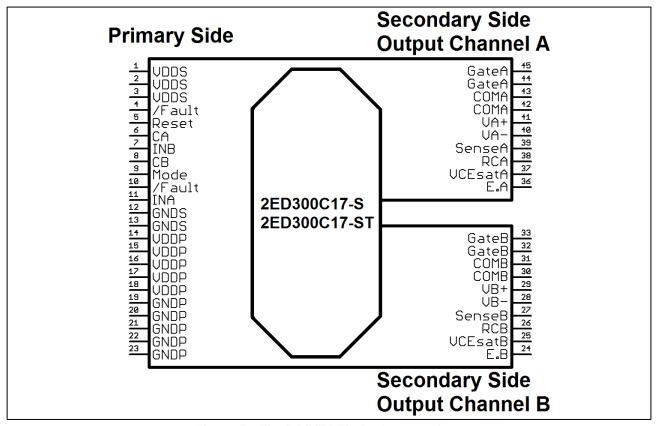

Figure 2: Block Diagram 2ED300C17-S/-ST

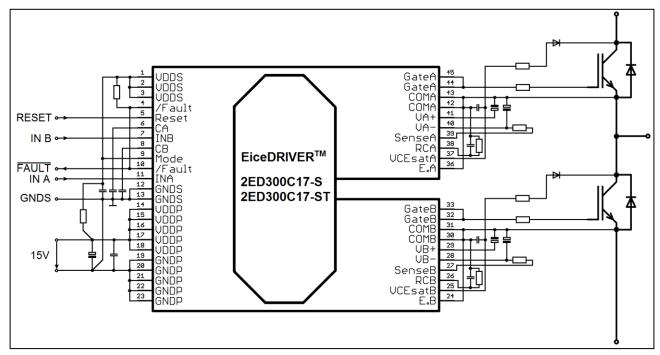

Figure 3: Peripheric components for half-bridge mode

#### **Functional Description**

## **2** Functional Description

EiceDRIVER™ (eupec IGBT controlled efficiency DRIVER) is the name of a family of IGBT-Drivers consisting of IGBT driver boards and IGBT driver ICs.

The 2ED300C17-S/-ST is a dual channel high voltage gate driver board featuring reinforced isolation between logic side and high voltage output.

Control and protection functions are included to ease the design of highly reliable systems.

The 2ED300C17-S is designed for use in industrial applications and the 2ED300C17-ST, with special coating, for the use in more demanding applications like railway traction or windmills.

The device consists of two galvanically separated driver channels and features two operating functions, the direct mode and the half-bridge mode, to drive IGBT modules.

The 2ED300C17-S/-ST is designed for use with Infineon IGBT modules up to 1700V in applications with high safety and reliability requirements and aims for power ratings of 75kW to 1MW.

The driver also includes IGBT desaturation protection, external failure input and Undervoltage Lockout (UVLO) detection. All fault states set the fault memory and activate the open drain fault output.

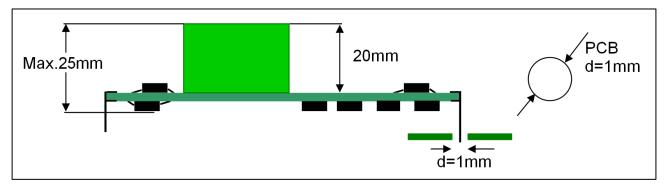

#### 2.1 Reinforced Isolation

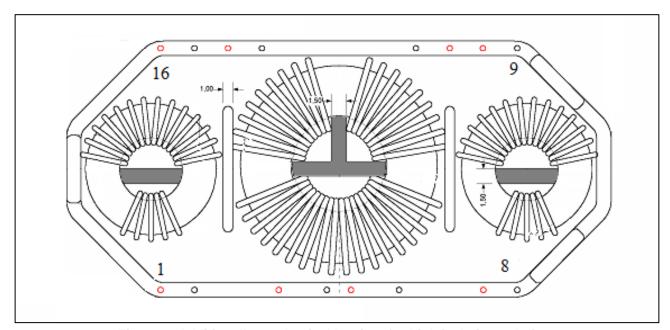

The most important safety feature of the 2ED300C17-S/-ST high voltage driver board is the reinforced isolation between primary and secondary side. This is achieved by using a specially designed transformer characterized by lowest coupling capacitances, , high isolation stability and by appropriate creepage and clearance distances on the printed circuit board. Figure 4 shows the specially transformer design for high isolation solution.

The clearance and creepage distances comply with VDE0110 and VDE0160 / EN50178 and are designed for pollution degree 3, over voltage class III. All materials used within the transformer at least meet the requirements of UL94V-2.

Figure 4: Additionally mechanical barriers for high isolation solution

#### **Functional Description**

#### 2.2 Integrated SMPS

A switch mode power supply with galvanically separated outputs is integrated on the 2ED300C17-S/-ST. It generates the required voltages for both driver channels. The secondary supplies are not protected against external short circuit.

#### 2.3 Undervoltage Lockout (UVLO)

Undervoltage monitoring is implemented for both secondary sides, positive and negative driver supply voltages are monitored. The Signal and Logic side is not monitored. Undervoltage lockout functionality in both driver channels ensures correct IGBT switching operation.

If the absolute value of one of the driver channel's power supplies drops below the UVLO detection level, the IGBT is shut down using the soft shut down functionality; gate-signals are ignored and the fault output is activated.

#### 2.4 Dynamic Overcurrent Detection (DOCD)

The dynamic over current detection protects the IGBT in case of a short circuit. The saturation voltage during IGBT on-state is measured and continuously compared with a defined reference signal.

The shut down reference curve has to be adapted to each individual IGBT connecting an external RC network. If no measures are taken, the reference level for desaturation detection is approx. at 10 V. Adding an RC network allows to tune the characteristics of the detection circuit.

#### 2.5 Soft Shut Down (SSD)

Soft shut down is a technique to limit the current slope di/dt during turn-off. It is activated if the fault memory is set as a consequence of a detected fault condition. A sense terminal can optionally be used to connect an additional external resistor. This is done to adjusting the IGBT turn-off characteristics. This terminal can optionally be used as an input for the active clamping or di/dt and dv/dt control.

#### 2.6 External Detected Failure Analysis (EDFA)

Additional function, customizable according to individual applications such as thermo switches on heat sinks. Digital high level on these terminals set the fault memory. Soft shut down is initiated and further operation inhibited.

#### 2.7 Reset

Resetting the driver can be done by applying a digital high level to the Reset-pin or by applying a digital low level to both gate-signal inputs for at least 60ms. On Reset, the fault memory is deleted and restarting driver operation is possible.

#### 2.8 Control Inputs and Outputs 2ED300C17-S /-ST

Inputs of the Signal and Logic side require 15V CMOS levels according to 40xx CMOS technology. This offers a high signal to noise ratio. In very harsh environments, negative low level input signals can be used with the limits given for the maximum ratings.

The open drain fault output is a very low impedance output. Voltage levels similar to Signal and Logic ground are achieved.

## 3 Pin Configuration and Functionality

| Pin                        | Label   | Function                                                                        |  |  |  |  |

|----------------------------|---------|---------------------------------------------------------------------------------|--|--|--|--|

| 1 2 3                      | VDDS    | Signal and logic supply voltage primary side                                    |  |  |  |  |

| 4                          | /Fault  | Open drain fault output                                                         |  |  |  |  |

| 5                          | Reset   | Active high signal and logic reset input                                        |  |  |  |  |

| 6                          | CA      | External capacitor terminal for half-bridge mode dead time adjustment channel A |  |  |  |  |

| 7                          | INB     | Active high PWM input channel B                                                 |  |  |  |  |

| 8                          | СВ      | External capacitor terminal for half-bridge mode dead time adjustment channel B |  |  |  |  |

| 9                          | Mode    | Operating mode selection input                                                  |  |  |  |  |

| 10                         | /Fault  | Open drain fault output                                                         |  |  |  |  |

| 11                         | INA     | Active high PWM input channel A                                                 |  |  |  |  |

| 12<br>13                   | GNDS    | Signal and logic common ground primary side                                     |  |  |  |  |

| 14<br>15<br>16<br>17<br>18 | VDDP    | DC/DC-SMPS supply voltage primary side                                          |  |  |  |  |

| 19<br>20<br>21<br>22<br>23 | GNDP    | DC/DC-SMPS ground primary side                                                  |  |  |  |  |

| 24                         | E.B     | Active high external digital fault input driver channel B                       |  |  |  |  |

| 25                         | VCEsatB | IGBT desaturation sensing input driver channel B                                |  |  |  |  |

| 26                         | RCB     | Desaturation reference curve RC network terminal driver channel B               |  |  |  |  |

| 27                         | SenseB  | Active clamping input or soft shut down resistor terminal driver channel B      |  |  |  |  |

| 28                         | VB-     | External capacitor terminal for negative power supply driver channel B          |  |  |  |  |

| 29                         | VB+     | External capacitor terminal for positive power supply driver channel B          |  |  |  |  |

| 30<br>31                   | COMB    | Common ground terminal driver channel B                                         |  |  |  |  |

| 32<br>33                   | GateB   | IGBT gate output driver channel B                                               |  |  |  |  |

| 34                         |         | Pin not existing; cut out                                                       |  |  |  |  |

| 35                         |         | Pin not existing; cut out                                                       |  |  |  |  |

| 36                         | E.A     | Active high external digital fault input driver channel A                       |  |  |  |  |

| 37                         | VCEsatA | IGBT desaturation sensing input driver channel A                                |  |  |  |  |

| 38                         | RCA     | Desaturation reference curve RC network terminal driver channel A               |  |  |  |  |

| 39                         | SenseA  | Active clamping input or soft shut down resistor terminal driver channel A      |  |  |  |  |

| 40                         | VA-     | External capacitor terminal for negative power supply driver channel A          |  |  |  |  |

| 41                         | VA+     | External capacitor terminal for positive power supply driver channel A          |  |  |  |  |

| 42<br>43                   | COMA    | Common ground terminal driver channel A                                         |  |  |  |  |

| 44<br>45                   | GateA   | IGBT gate output driver channel A                                               |  |  |  |  |

Table 1 : Pin Configuration of 2ED300C17-S/-ST

In addition to Table 1, Figure 5 gives an overview on the pin positions.

Figure 5 : EiceDRIVER™ pinning top view

#### 3.1 Pin functionalities, Primary side

All input pins are compatible to 15V CMOS logic according to 40xx technology.

#### **VDDS**

15V supply voltage for signal and logic part on the primary side. All pins have to be connected.

#### /Fault

Open drain fault output for signalization of internal and external faults. Reset signal required to delete the fault memory and for restarting operation after fault state.

External pull-up resistor needed.

#### Reset

Active high signal to delete the fault memory.

#### INA

Active high signal for PWM, channel A. Negative input voltage for low level is allowed within the limits given for maximum values.

#### INB

Active high signal for PWM, channel B. Negative input voltage for low level is allowed within the limits given for maximum values.

#### CA

Terminal to connect external capacitor for dead time adjustment of channel A in half-bridge mode.

#### CB

Terminal to connect external capacitor for dead time adjustment of channel B in half-bridge mode.

#### Mode

Terminal for mode selection, choosing direct mode or half-bridge mode. High level or connection to VDDS activates half-bridge mode. Low level or connection to ground GNDS activates direct mode.

#### **GNDS**

Common ground connection for signals and supply voltage of Signal and Logic part.

All pins have to be connected.

Connection between GNDS and GNDP is permissible.

#### **VDDP**

15V supply voltage for DC/DC switch mode power supply. An external capacitor to GNDP is mandatory at this terminal.

All pins have to be connected.

#### **GNDP**

Ground connection for DC/DC switch mode power supply.

All pins have to be connected.

Connection between GNDS and GNDP is permissible.

#### 3.2 Pin functionalities, Secondary side

#### GateA

Output to IGBT gate, driver channel A. Both pins have to be connected.

#### **COMA**

Common ground connection for IGBT auxiliary emitter and all signals of driver channel A. Both pins have to be connected.

#### VA+

Positive power supply, driver channel A. An external capacitor to ground COMA is mandatory at this terminal.

#### VA-

Negative power supply driver channel A. An external capacitor to ground COMA is mandatory at this terminal.

#### **SenseA**

Terminal for additional external soft shut down resistor or input for active clamping, di/dt or dv/dt control, driver channel A

#### **RCA**

Desaturation reference curve RC network terminal, driver channel A

#### **VCEsatA**

IGBT desaturation sensing input, driver channel A.

#### E.A

Active high external digital fault input driver channel A for set fault memory.

#### GateB

Output to IGBT gate, driver channel B. Both pins have to be connected.

#### **COMB**

Common ground connection for IGBT auxiliary emitter and all signals of driver channel B. Both pins have to be connected.

#### VB+

Positive power supply, driver channel B. An external capacitor to ground COMB is mandatory at this terminal.

#### VB-

Negative power supply, driver channel B. An external capacitor to ground COMB is mandatory at this terminal.

#### **SenseB**

Terminal for additional external soft shut down resistor or input for active clamping, di/dt or dv/dt control, driver channel B

#### **RCB**

Desaturation reference curve RC network terminal, driver channel B.

#### **VCEsatB**

IGBT desaturation sensing input, driver channel B.

#### E.B

Active high external digital fault input driver channel B for set fault memory.

#### 4 Electrical Parameters

Electrical parameters are differentiated into maximum values that in no case are to be exceeded and operational conditions typical to the application. All parameters are listed in the following sections.

## 4.1 Absolute Maximum Ratings

Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the driver board. Unless otherwise noted all primary side parameters refer to GNDS. The secondary side signals from driver channel A and driver channel B are measured with respect to their individual COMA or COMB.

| Parameter                                           | Symbol                                  | Limit ' | Values | Unit  | Remarks |

|-----------------------------------------------------|-----------------------------------------|---------|--------|-------|---------|

|                                                     |                                         | min     | max    |       |         |

| Positive power supply voltage Logic and Signal      | $V_{VDDS}$                              |         | 16,5   | V     | 1       |

| Positive power supply voltage DC/DC SMPS            | $V_{VDDP}$                              |         | 16,5   | V     | 2       |

| Total input current $V_{VDDS}$ and $V_{VDDP}$       | $I_{VDD,sum}$                           |         | 670    | mA    | 3       |

| PWM signal input voltage INA, INB                   | $V_{INA}, V_{INB}$                      | -20     | 20     | V     |         |

| Logic signal input voltage Mode, Reset              | V <sub>Mode</sub> , V <sub>Reset</sub>  | -20     | 20     | V     |         |

| Voltage on open drain fault output                  | $V_{Fault}$                             |         | 20     | V     |         |

| Total fault output current on one or both terminals | I <sub>Fault</sub>                      |         | 40     | mA    |         |

| Peak turn on output current                         | I <sub>GateA</sub> , I <sub>GateB</sub> |         | 30     | Α     | 4       |

| Peak turn off output current                        | I <sub>GateA</sub> , I <sub>GateB</sub> |         | -30    | Α     | 4       |

| DC/DC SMPS average current per output               | I <sub>VX</sub>                         |         | 133    | mA    | 5       |

| Total DC/DC SMPS output power                       | P <sub>SMPS</sub>                       |         | 8      | W     |         |

| Collector emitter voltage of IGBT                   | V <sub>CES</sub>                        |         | 1700   | V     |         |

| Minimum total gate resistor                         | $R_{Gmin}$                              | 1       |        | Ω     |         |

| Maximum IGBT gate charge                            | $Q_{Gmax}$                              |         | 52     | μC    |         |

| Maximum slew rate                                   | dvce/dt                                 |         | 50     | kV/µs | 6       |

| Maximum switching frequency                         | f <sub>smax</sub>                       |         | 60     | kHz   | 7       |

| Maximum duty cycle                                  | d <sub>max</sub>                        |         | 100    | %     |         |

| Operating temperature 2ED300C17-S                   | T <sub>op</sub>                         | -25     | 85     | °C    | 7       |

| Operating temperature 2ED300C17-ST                  | T <sub>op</sub>                         | -40     | 85     | °C    | 7       |

| Storage temperature                                 | T <sub>sto</sub>                        | -40     | 85     | °C    |         |

**Table 2: Absolute maximum ratings**

<sup>&</sup>lt;sup>1</sup> With respect to GNDS

<sup>&</sup>lt;sup>2</sup> With respect to GNDP

<sup>&</sup>lt;sup>3</sup> Calculated value for equivalent average DC input current @ maximum SMPS output power of 8W

<sup>&</sup>lt;sup>4</sup> Maximum output current of the transistor power stage

<sup>&</sup>lt;sup>5</sup> Maximum DC output current per DC/DC output voltage calculated for total SMPS power of 8W

<sup>&</sup>lt;sup>6</sup> The parameter is not subject to production test – verified by design/characterization

<sup>&</sup>lt;sup>7</sup> Operating temperature depends on load and environmental conditions.

#### 4.2 Operating Parameters

Within the operating range the driver board operates as described in the functional description. Unless noted otherwise, all primary side parameters refer to GNDS. The secondary side signals from driver channel A and driver channel B are measured with respect to their individual COMA or COMB.

| Parameter                                                 | Symbol                                 | Limit Values |     | Unit | Remarks |

|-----------------------------------------------------------|----------------------------------------|--------------|-----|------|---------|

|                                                           |                                        | min          | max |      |         |

| Positive power supply voltage Logic and Signal            | $V_{VDDS}$                             | 14           | 16  | V    |         |

| Positive power supply voltage DC/DC SMPS                  | $V_{VDDP}$                             | 14           | 16  | V    | 8       |

| PWM signal input voltage INA, INB                         | V <sub>INA</sub> , V <sub>INB</sub>    | -15          | 15  | V    |         |

| Logic signal input voltage Mode, Reset                    | V <sub>Mode</sub> , V <sub>Reset</sub> | -15          | 15  | V    |         |

| Voltage on open drain fault output in non-fault condition | V <sub>Fault</sub>                     |              | 16  | V    |         |

| Switching frequency                                       | f <sub>smax</sub>                      | 0            | 60  | kHz  | 9       |

| Duty cycle                                                | d <sub>max</sub>                       | 0            | 100 | %    |         |

**Table 3: Operating parameters**

#### 4.3 Recommended Operating Parameters

Unless noted otherwise, all primary side signals refer to GNDS. The secondary side signals from driver channel A and driver channel B are measured with respect to their individual COMA or COMB.

| Parameter                                                 | Symbol                                 | Value | Unit | Remarks |

|-----------------------------------------------------------|----------------------------------------|-------|------|---------|

| Positive power supply voltage logic and signal            | V <sub>VDDS</sub>                      | 15    | V    |         |

| Positive power supply voltage DC/DC SMPS                  | $V_{VDDP}$                             | 15    | V    | 10      |

| PWM signal input voltage INA, INB                         | V <sub>INA</sub> , V <sub>INB</sub>    | 15    | V    |         |

| Logic signal input voltage Mode, Reset                    | V <sub>Mode</sub> , V <sub>Reset</sub> | 15    | V    |         |

| Voltage on open drain fault output in non-fault condition | V <sub>Fault</sub>                     | 15    | V    |         |

| Switching frequency @ 65°C operating temperature          | f <sub>smax</sub>                      | 60    | kHz  | 11      |

**Table 4: Recommended operating parameters**

<sup>&</sup>lt;sup>8</sup> With respect to GNDP

<sup>&</sup>lt;sup>9</sup> Operating temperature depends on load and environmental conditions.

<sup>&</sup>lt;sup>10</sup> With respect to GNDP

<sup>&</sup>lt;sup>11</sup> Operating temperature depends on load and environmental conditions.

#### 4.4 Electrical Characteristics

The electrical characteristics involve the spread of values for the supply voltages, load and junction temperatures given below. Typical values represent the median values, which are related to production processes at T =  $25^{\circ}$ C.  $V_{VDDS}$  and  $V_{VDDP}$  are 15V. Unless otherwise noted all voltages are given with respect to GNDS. The specification for all output driver signals is valid for driver channel A and driver channel B without special notice. The secondary signals are measured with respect to their individual COMA or COMB.

| Parameter                                                                              | Symbol                            | Limit Values |      |     | Unit | Remarks |

|----------------------------------------------------------------------------------------|-----------------------------------|--------------|------|-----|------|---------|

|                                                                                        |                                   | min          | typ  | max |      |         |

| No load SMPS average DC input current                                                  | I <sub>VDDS</sub>                 |              | 80   |     | mA   |         |

| Signal and Logic DC input current                                                      | I <sub>VDDP</sub>                 |              | 10   |     | mA   |         |

| Turn on propagation delay time                                                         | t <sub>pd,on</sub>                |              | 670  |     | ns   |         |

| Turn off propagation delay time                                                        | $t_{pd,off}$                      |              | 580  |     | ns   |         |

| Transition time differences                                                            | t <sub>dif</sub>                  |              | 50   |     | ns   |         |

| Minimal pulse suppression                                                              | t <sub>md</sub>                   |              | 400  |     | ns   |         |

| DC input impedance of INA, INB, Mode, Reset                                            |                                   |              | 3300 |     | Ω    |         |

| Input threshold level                                                                  | $V_{INA}, V_{INB}$                |              | 8    |     | V    |         |

| Input threshold for external failure input E.A or E.B                                  | $V_{E.A}, V_{E.B}$                |              | 5    |     | V    | 12      |

| Interlock delay time half-bridge mode                                                  | t <sub>TD</sub>                   | 1,6          |      |     | μs   |         |

| Reactivation after fault condition @ INA and INB with low input signal                 | t <sub>react</sub>                | 50           | 60   |     | ms   |         |

| Reference voltage for IGBT desaturation sensing                                        |                                   |              | 10   |     | V    |         |

| Coupling capacitance primary/secondary                                                 | C <sub>cps</sub>                  |              | 18   |     | pF   |         |

| Coupling capacitance between secondary sides                                           | C <sub>css</sub>                  |              | 15   |     | pF   |         |

| External capacitor for Logic and Signal power supply. Connected between VDDS and GNDS. | $C_{VDDP}$                        | 10           |      |     | μF   |         |

| External capacitor for SMPS power supply. Connected between VDDP and GNDP.             | C <sub>VDDS</sub>                 | 470          |      |     | μF   |         |

| Positive supply voltage driver channel A and B  @ no switching operation               | $V_{VA+}, V_{VB+}$                |              | 16   |     | V    |         |

| Negative supply voltage driver channel A and B  @ no switching operation               | $V_{VA-}, V_{VB-}$                |              | -16  |     | V    |         |

| Internal capacitor on positive supply voltage driver channel VA+ and VB+               | $C_{VA+,int}, \ C_{VB+,int}$      |              | 28   |     | μF   |         |

| Internal capacitor on negative supply voltage driver channel VA- and VB-               | $C_{VA-,int}, \ C_{VB-,int}$      |              | 23   |     | μF   |         |

| Internal UVLO level for positive supply voltage driver channel                         | V <sub>UVLO,pos</sub>             |              | 10,9 |     | V    |         |

| Internal UVLO level for negative supply voltage driver channel                         | V <sub>UVLO,neg</sub>             |              | -9,3 |     | V    |         |

| External capacitor for interlocking generation                                         | C <sub>CA</sub> , C <sub>CB</sub> | 0            |      | 1   | nF   | 13      |

**Table 5: Electrical characteristics**

<sup>&</sup>lt;sup>12</sup> If not use E.A and E.B should be connected to COMA or COMB

<sup>&</sup>lt;sup>13</sup> Capacitor terminal only. Connection to another terminals or voltages not allowed.

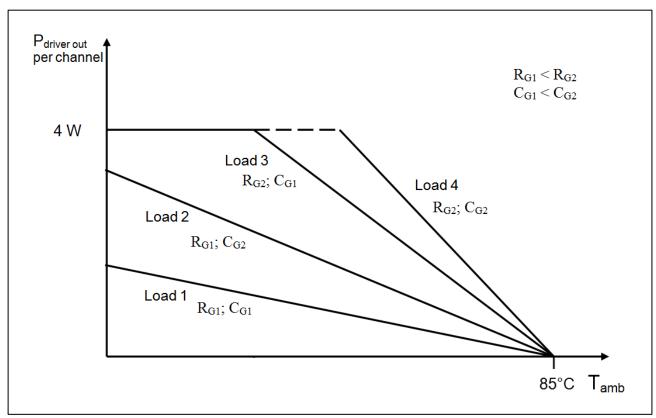

#### 4.5 Driver performance

The 2ED300C17-S can transmit a maximum power of 4 W per channel from primary to secondary side. The power required to drive an IGBT is dependent of gate charge of the IGBT (datasheet value  $Q_{\rm G}$ ), switching frequency  $f_{\rm s}$  and gate voltage difference  $\Delta V$ . The safety factor 1.2 included 20% over all tolerances. The power for IGBT drive may be calculated by the following equation:

$$P_{driver} = 1.2 * Q_G * f_s * \Delta V$$

This power is dissipated in the driver itself, in the external gate resistor and in the internal IGBT gate resistor.

The share of the total power each part has to dissipate varies with load conditions. There is a limit for the power dissipation of each channel of the driver which significantly varies with temperature inside the cabinet and with airflow conditions. Figure 6 shows the usable driver output power for a typical mounting condition with natural connection and several load conditions. Required gate power is considered to be constant. The highest share of power dissipation inside the driver is to be expected when operating a small IGBT with low total  $R_{\rm G}$  at high switching frequency. Whereas driving a larger IGBT with higher  $R_{\rm G}$  at low switching frequency is less demanding regarding thermal considerations.

Figure 6: Power dissipation of the driver for different load conditions

Load 1 > load 2 > load 3 > load 4

Load 1 – small  $R_{\text{G}}$  and small  $C_{\text{G}}$

Load 2 - small R<sub>G</sub> and high C<sub>G</sub>

Load 3 – high  $R_G$  and small  $C_G$

Load 4 – high  $R_G$  and high  $C_G$

The load is a combination of the gate resistors and the gate capacitance.

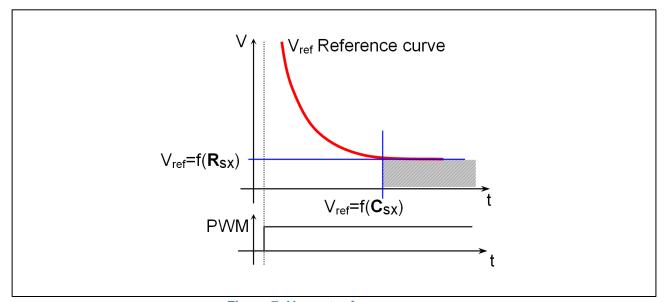

#### 4.6 VCESAT reference

The short circuit detection measurement is integrated in the 2ED300C17-S. The 2ED300C17-S measures the  $V_{CE}$  voltage while the IGBT is turned on. If the  $V_{CE}$  voltage rises above the preset reference voltage during this period, a fault is triggered and the IGBT is turned off via the internal soft shut-down.

The reference curve is only adjustable via an external  $R_{SX}$  and  $C_{SX}$ .  $R_{SX}$  sets the reference voltage and  $C_{SX}$  sets the time constant for the decay to the stationary reference value.

The resistor and the capacitor are connected parallel between RC A and COM A or RC B and COM B.

Figure 7: Vce,sat reference curve

#### **Isolation characteristics**

## 5 Isolation characteristics

Electrical characteristics, at Ta = 25 °C, unless otherwise specified.

| Parameter                                            | Value | Unit | Remarks                                                                          |  |  |

|------------------------------------------------------|-------|------|----------------------------------------------------------------------------------|--|--|

| Isolation test voltage                               | 5000  | V    | Signal and Logic Side - Driver Channel A and Driver Channel B (RMS, 50Hz, 1s)    |  |  |

| Isolation test voltage                               | 2250  | V    | Driver Channel A - Driver Channel B (RMS, 50Hz, 1s)                              |  |  |

| Surge voltage test                                   | 9600  | V    | Surge test according to EN50178 Signal and Logic Side to Driver Channels A and B |  |  |

| Partial discharge test voltage                       | >1920 | V    | RMS; transformer series test According to EN 61800-5-1                           |  |  |

| Clearance and creepage distance primary to secondary |       |      |                                                                                  |  |  |

| Clearance distance secondary to secondary            | >4,59 | mm   | Distance Driver Channel A to Drive Channel B. 4mm air gap included.              |  |  |

| Creepage distance secondary to secondary             | >14   | mm   | Distance Driver Channel A to Driver Channel B                                    |  |  |

**Table 6: Isolation characteristics**

#### **Timing diagrams**

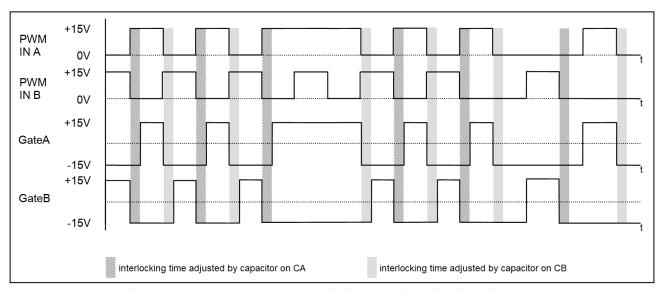

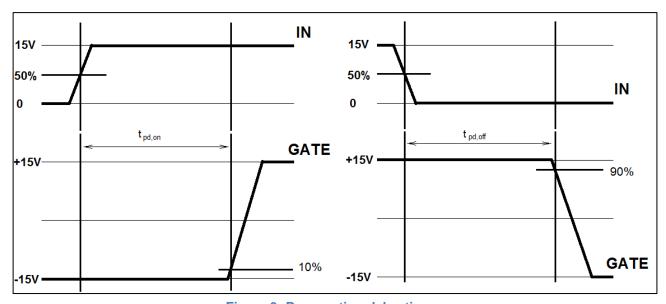

## 6 Timing diagrams

Diagram in Figure 8 shows typical input and output signals. Figure 9 shows propagation delay times.

Figure 8: PWM timing diagram with interlocking time functionality

Figure 9: Propagation delay times

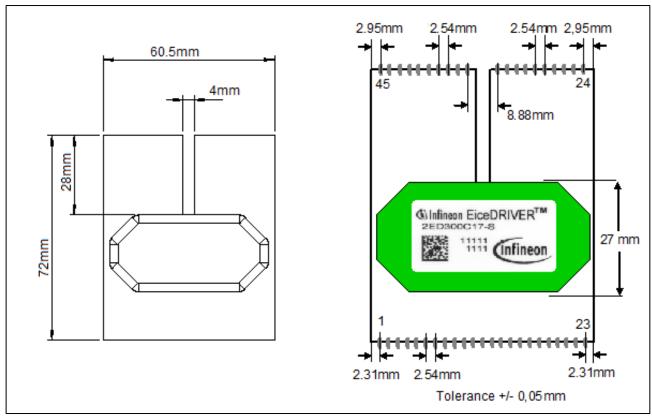

#### **Mechanical dimensions**

## 7 Mechanical dimensions

Figure 10: Package outlines top view

Figure 11: Package outlines side view

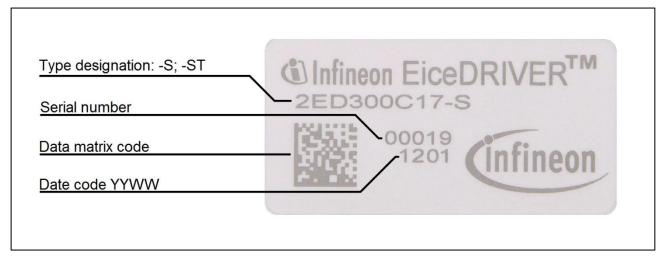

#### **Mechanical dimensions**

Figure 12: Label

| Intent of DMX Code               | DMX Code | DMX Code       |  |

|----------------------------------|----------|----------------|--|

|                                  | digit    | digit quantity |  |

| Serial Number                    | 1-5      | 5              |  |

| SAP Material Number              | 6-11     | 6              |  |

| Internal Production Order Number | 12-19    | 8              |  |

| Datecode (Production Year)       | 20-21    | 2              |  |

| Datecode (Production Week)       | 22-23    | 2              |  |

Table 7: Intent of DMX code

## **Handling and mounting**

## 8 Handling and mounting

The device has been designed to be soldered onto a carrier board as a through-hole component. Dual wave soldering process or selective soldering can be done. For more information see IFX Additional Information, DS1, March 2008

The -ST version differentiates from the -S as it features an additional coating. The coating used is type 1306N made by the company Peters. The soldering pins are not coated. When further coating processes are done on the customer assembly, the compatibility of the coated type has to be established first.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Infineon:

2ED300C17-ST 2ED300C17-S 2ED300C17-S ROHS 2ED300C17-ST ROHS