# STK672-060-E

Thick-Film Hybrid IC Unipolar Constant-current Chopper (external excitation PWM) Circuit with Built-in Microstepping Controller Stepping Motor Driver (sine wave drive) Output Current 1.2A (no heat sink\*)

#### Overview

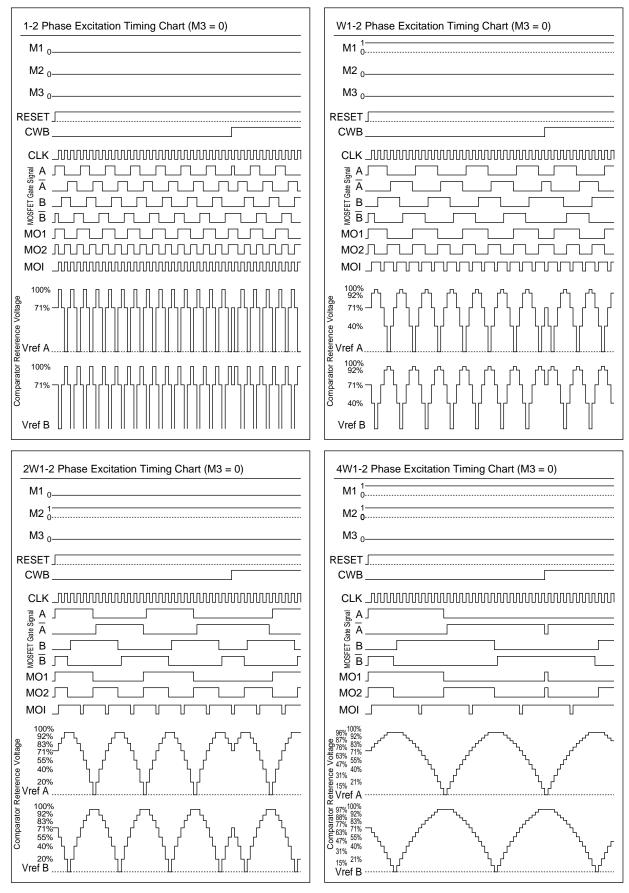

The STK672-060-E is a stepping motor driver hybrid IC that uses power MOSFETs in the output stage. It includes a built-in microstepping controller and is based on a unipolar constant-current PWM system. The STK672-060-E supports application simplification and standardization by providing a built-in 4 phase distribution stepping motor controller. It supports five excitation methods: 2 phase, 1-2 phase, W1-2 phase, 2W1-2 phase, and 4W1-2 phase excitations, and can provide control of the basic stepping angle of the stepping motor divided into 1/16 step units. It also allows the motor speed to be controlled with only a clock signal.

The use of this hybrid IC allows designers to implement systems that provide high motor torques, low vibration levels, low noise, fast response, and high-efficiency drive.

#### Applications

- Facsimile stepping motor drive (send and receive)

- Paper feed and optical system stepping motor drive in copiers

- Laser printer drum drive

- Printer carriage stepping motor drive

- X-Y plotter pen drive

- Other stepping motor applications

Note\*: Conditions: V<sub>CC</sub>1 = 24V, I<sub>OH</sub> = 1.2A, 2W1-2 excitation mode.

#### Features

- Can implement stepping motor drive systems simply by providing a DC power supply and a clock pulse generator.

- <Control Block Features>

- One of five drive types can be selected with the drive mode settings (M1, M2, and M3)

- 1) 2 phase excitation drive

- 2) 1-2 phase excitation drive

- 3) W1-2 phase excitation drive

- 4) 2W1-2 phase excitation drive

- 5) 4W1-2 phase excitation drive

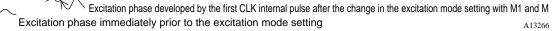

- Provides four freely selectable modes for the vector locus during microstepping drive: circular mode, one inside mode, and two outside modes.

- Phase retention even if excitation is switched.

- The excitation phase state can be verified in real time using the MO1, MO2, and MOI signal output pins.

- The CLK input counter block can be selected to be one of the following by the high/low setting of the M3 input pin.

- 1) Rising edge only

- 2) Both rising and falling edges

- The CLK and RETURN input pins include built-in malfunction prevention circuits for external pulse noise.

- ENABLE and  $\overline{\text{RESET}}$  pins provided. These are Schmitt trigger inputs with built-in 20k $\Omega$  (typical) pull-up resistors.

- No noise generation due to the difference between the A and B phase time constants during motor hold since external excitation is used.

- Microstepping operation supported even for small motor currents, since the reference voltage Vref can be set to any value between 0V and  $1/2V_{CC}2$ .

<Driver Block>

- External excitation PWM drive allows a wide operating supply voltage range ( $V_{CC}1 = 10$  to 45V) to be used.

- Current detection resistor  $(0.22\Omega)$  built-in the hybrid IC itself.

- Power MOSFETs adopted for low drive loss.

- Provides a motor output drive current of  $I_{OH} = 1.2A$ .

#### **Specifications**

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                       | Parameter Symbol Conditions |                                        | Ratings      | Unit |

|---------------------------------|-----------------------------|----------------------------------------|--------------|------|

| Maximum supply voltage 1        | V <sub>CC</sub> 1 max       | No signal                              | 52           | V    |

| Maximum supply voltage 2        | V <sub>CC</sub> 2 max       | No signal                              | -0.3 to +7.0 | V    |

| Input voltage                   | V <sub>IN</sub> max         | Logic input pins                       | -0.3 to +7.0 | V    |

| Output current                  | I <sub>OH</sub> max         | 0.5s, 1 pulse, when $V_{CC}$ 1 applied | 1.6          | А    |

| Repeated avalanche capacity     | Ear max                     |                                        | 25           | mJ   |

| Allowable power dissipation     | Pd max                      | θc-a = 0                               | 7            | W    |

| Operating substrate temperature | Tc max                      |                                        | 105          | °C   |

| Junction temperature            | Tj max                      |                                        | 150          | °C   |

| Storage temperature             | Tstg                        |                                        | -40 to +125  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Allowable Operating Ranges at Ta = 25°C

| Parameter                      | Symbol            | Conditions                                                               | Ratings                | Unit |

|--------------------------------|-------------------|--------------------------------------------------------------------------|------------------------|------|

| Supply voltage 1               | V <sub>CC</sub> 1 | With signals applied                                                     | 10 to 45               | V    |

| Supply voltage 2               | V <sub>CC</sub> 2 | With signals applied                                                     | 5 ± 5%                 | V    |

| Input voltage                  | VIH               |                                                                          | 0 to V <sub>CC</sub> 2 | V    |

| Phase driver withstand voltage | V <sub>DSS</sub>  | Tr1, 2, 3, and 4 (the A, $\overline{A}$ , B, and $\overline{B}$ outputs) | 100 (min)              | V    |

| Output current                 | Iон               | Duty 50%                                                                 | 1.2                    | А    |

| Demonstere                         | Quere la sta    | O an dition a                                                               |       | Rating |       | unit |

|------------------------------------|-----------------|-----------------------------------------------------------------------------|-------|--------|-------|------|

| Parameters                         | Symbols         | Conditions                                                                  | min   | typ    | max   | unit |

| Control supply current             | <sup>I</sup> CC | Pin 7, with ENABLE pin held low.                                            |       | 2.5    | 14    | mA   |

| Output saturation voltage          | Vsat            | $R_L = 23\Omega (I \approx 1A)$                                             |       | 0.8    | 1.1   | V    |

| Average output current             | loave           | Load: R = $3.5\Omega$ / L = $3.8mH$<br>For each phase, Vref $\approx 1.69V$ | 0.470 | 0.524  | 0.580 | A    |

| FET diode forward voltage          | Vdf             | lf = 1A                                                                     |       | 1.2    | 1.8   | V    |

| [Control Inputs]                   |                 |                                                                             |       |        |       |      |

| lange to the sec                   | VIH             | Except for the Vref pin                                                     | 4     |        |       | V    |

| Input voltage                      | VIL             | Except for the Vref pin                                                     |       |        | 1     | V    |

| 1                                  | Чн              | Except for the Vref pin                                                     | 0     | 1      | 10    | μA   |

| Input current                      | ۱ <sub>IL</sub> | Except for the Vref pin                                                     | 125   | 250    | 510   | μA   |

| [Vref Input Pin]                   | ·               |                                                                             |       |        |       |      |

| Input voltage                      | VI              | Pin 8                                                                       | 0     |        | 2.5   | V    |

| Input current                      | Ц               | Pin 8, VI = 2.5V                                                            | 330   | 415    | 545   | μA   |

| [Control Outputs]                  | ·               |                                                                             |       |        |       |      |

|                                    | VOH             | I = -3mA, pins MOI, MO1, MO2                                                | 2.4   |        |       | V    |

| Output voltage                     | VOL             | I = +3mA, pins MOI, MO1, MO2                                                |       |        | 0.4   | V    |

| [Current Distribution Ratio (A·B)] |                 |                                                                             |       |        |       |      |

| 2W1-2, W1-2, 1-2                   | Vref            | $\theta = 1/8$                                                              |       | 100    |       | %    |

| 2W1-2, W1-2                        | Vref            | $\theta = 2/8$                                                              |       | 92     |       | %    |

| 2W1-2                              | Vref            | $\theta = 3/8$                                                              |       | 83     |       | %    |

| 2W1-2, W1-2, 1-2                   | Vref            | $\theta = 4/8$                                                              |       | 71     |       | %    |

| 2W1-2                              | Vref            | $\theta = 5/8$                                                              |       | 55     |       | %    |

| 2W1-2, W1-2                        | Vref            | $\theta = 6/8$                                                              |       | 40     |       | %    |

| 2W1-2                              | Vref            | $\theta = 7/8$                                                              |       | 21     |       | %    |

| 2                                  | Vref            |                                                                             |       | 100    |       | %    |

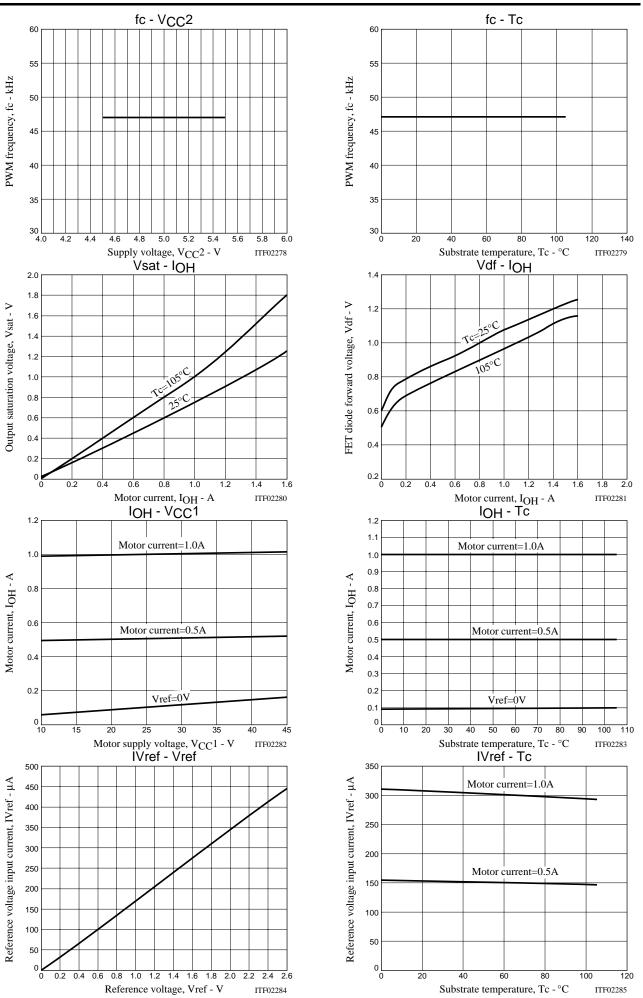

| PWM frequency                      | fc              |                                                                             | 37    | 47     | 57    | kHz  |

#### Electrical Char ctoristics at To 25°C Vool 24V Voo2 5V

Note: A constant-voltage power supply must be used.

The design target value is shown for the current distribution ratio.

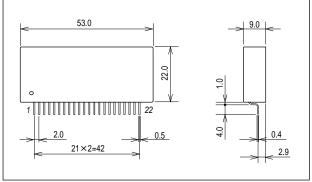

### **Package Dimensions**

unit:mm (typ) 4161

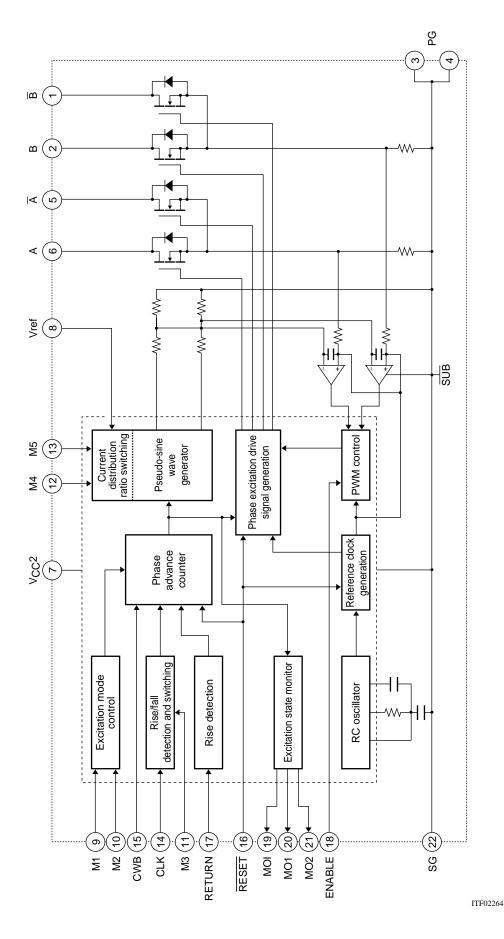

#### **Internal Block Diagram**

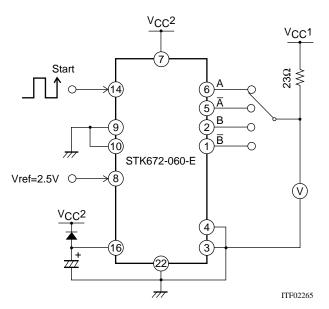

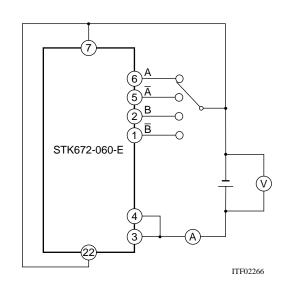

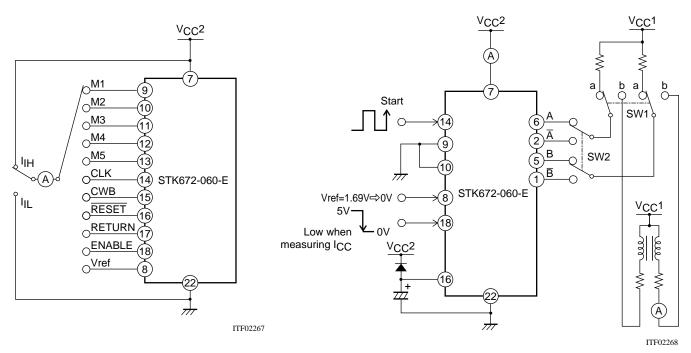

#### **Test Circuit Diagrams**

Vsat

Vdf

I<sub>IH</sub>, I<sub>IL</sub>

Ioave, ICC, fc

When measuring Ioave: With SW1 set to 'b', Vref = 1.69VWhen measuring fc: With SW1 set to 'a', Vref = 0VWhen measuring I<sub>CC</sub>: Set ENABLE low

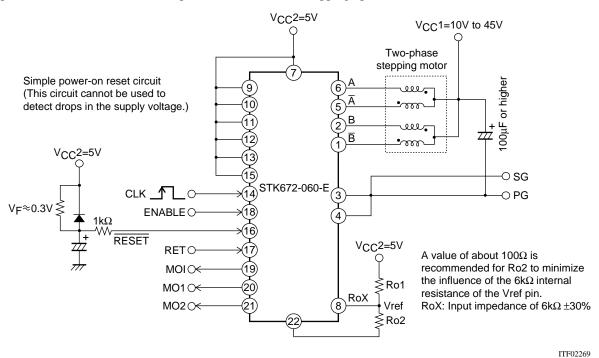

#### **Power-on Reset**

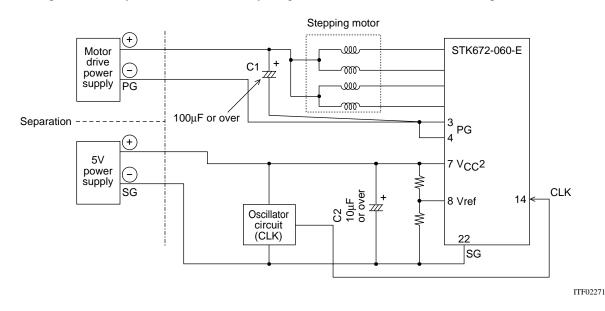

The application must perform a power-on reset operation when  $V_{CC}^2$  power is first applied to this hybrid IC. Application circuit that used 2W1-2 phase excitation (microstepping operation) mode.

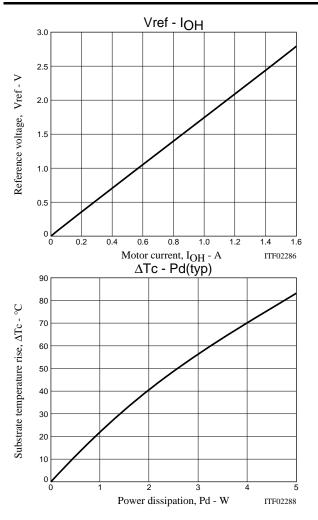

#### **Setting the Motor Current**

The motor current  $I_{OH}$  is set by the Vref voltage on the hybrid IC pin 8. The following formula gives the relationship between  $I_{OH}$  and Vref.

$$RoX = (Ro2 \times 6k\Omega) \div (Ro2 + 6k\Omega)$$

(1)

Vref = VCC2 × RoX ÷ (Ro1 + RoX) (2)

$$I_{OH} = \frac{1}{K} \times \frac{Vref}{Rs}$$

(3)

K: 7.66 (voltage divider ratio),

Rs:  $0.22\Omega$  (This is the hybrid IC's internal current detection resistor. It has a tolerance of  $\pm 3\%$ .)

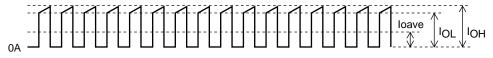

Motor current waveform

Applications can use motor currents from the current (0.05 to 0.1A) set by the duty of the frequency set by the oscillator up to the limit of the allowable operating range,  $I_{OH} = 1.2A$

#### **Function Table**

| M2       | 0                    | 0                     | 1                      | 1                      |                                   |  |

|----------|----------------------|-----------------------|------------------------|------------------------|-----------------------------------|--|

| M1<br>M3 | 0 1                  |                       | 0 1                    |                        | Phase switching clock edge timing |  |

| 1        | 2 phase excitation   | 1-2 phase excitation  | W1-2 phase excitation  | 2W1-2 phase excitation | Rising edge only                  |  |

| 0        | 1-2 phase excitation | W1-2 phase excitation | 2W1-2 phase excitation | 4W1-2 phase excitation | Rising and falling edges          |  |

|     | Forward | Reverse |   | ENABLE | Motor current is cut off when low |

|-----|---------|---------|---|--------|-----------------------------------|

| CWB | 0       | 1       |   | RESET  | Active low                        |

|     |         |         |   |        |                                   |

|     | А       | Ā       | В | B      |                                   |

| MO1 | 1       | 0       | 0 | 1      |                                   |

| MO2 | 0       | 0       | 1 | 1      |                                   |

A13262

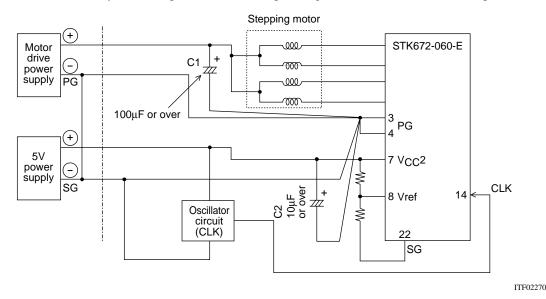

#### **Printed Circuit Board Design Recommendations**

This hybrid IC has two grounds, the PG pins (pins 3 and 4) and the SG pin (pin 22). These are connected internally in the hybrid IC.

Two power supplies are required: a motor drive supply and a 5V supply for the hybrid IC itself. If the ground connections for these supplies are not good, the motor current waveforms may become unstable, motor noise may increase, and vibration levels may increase. Use appropriate wiring for these grounds. Here we present two methods for implementing these ground connections.

If the grounds for the motor drive supply and the hybrid IC 5V supply are connected in the immediate vicinity of the power supplies:

- If PG and SG are shorted at the power supply, connect only the PG line to pins 3 and 4 on the hybrid IC. Also, be sure that no problems occur due to voltage drops due to common impedances. In the specifications, this must be  $V_{CC}2 \pm 5\%$ .

- The current waveforms will be more stable if the Vref ground is connected to pin 22.

- For initial values, use 100μF or over for C1 and 10μF or over for C2.

Locate C1 as close to the hybrid IC as possible, and the capacitor ground line must be as short as possible.

If the grounds for the motor drive supply and the hybrid IC 5V supply are separated:

• Insert a capacitor (C1) of  $100\mu$ F or over as close as possible to the hybrid IC. The capacitor ground line must be as short as possible.

The capacitor C2 may be included if necessary. Its ground line should also be as short as possible.

#### **Functional Description**

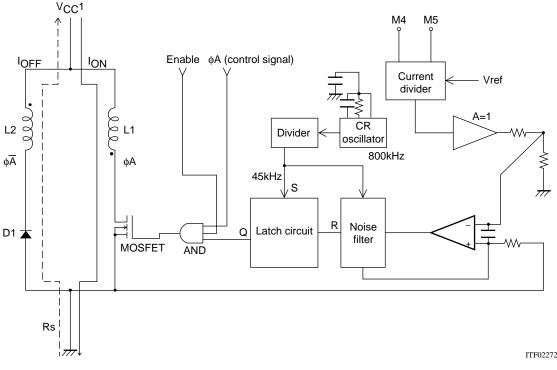

External Excitation Chopper Drive Block Description

Driver Block Basic Circuit Structure

Since this hybrid IC adopts an external excitation method, no external oscillator circuit is required. When a high level is input to  $\phi A$  in the basic driver block circuit shown in the figure and the MOSFET is turned on, the comparator + input will go low and the comparator output will go low. Since a set signal with the PWM period will be input, the Q output will go high, and the MOSFET will be turned on as its initial value.

The current I<sub>ON</sub> flowing in the MOSFET passes through L1 and generates a potential difference in Rs. Then, when the Rs potential and the Vref potential become the same, the comparator output will invert, and the reset signal Q output will invert to the low level. Then, the MOSFET will be turned off and the energy stored in L1 will be induced in L2 and the current I<sub>OFF</sub> will be regenerated to the power supply. This state will be maintained until the time when an input to the latch circuit set pin occurs.

In this manner, the Q output is turned off and on repeatedly by the reset and set signals, thus implementing constant current control. The resistor and capacitor on the comparator input are spike removal circuit elements and synchronize with the PWM frequency. Since this hybrid IC uses a fixed frequency due to the external excitation method and at the same time also adopts a synchronized PWM technique, it can suppress the noise associated with holding a position when the motor is locked.

| Pin No.   | Symbol     | Function                            | Pin circuit type                                     |

|-----------|------------|-------------------------------------|------------------------------------------------------|

| 14        | CLK        | Phase switching clock               | Built-in pull-up resistor CMOS Schmitt trigger input |

| 15        | CWB        | Rotation direction setting (CW/CCW) | Built-in pull-up resistor CMOS Schmitt trigger input |

| 17        | RETURN     | Forced phase origin return          | Built-in pull-up resistor CMOS Schmitt trigger input |

| 18        | ENABLE     | Output cutoff                       | Built-in pull-up resistor CMOS Schmitt trigger input |

| 9, 10, 11 | M1, M2, M3 | Excitation mode setting             | Built-in pull-up resistor CMOS Schmitt trigger input |

| 12, 13    | M4, M5     | Vector locus setting                | Built-in pull-up resistor CMOS Schmitt trigger input |

| 16        | RESET      | System reset                        | Built-in pull-up resistor CMOS Schmitt trigger input |

| 8         | Vref       | Current setting                     | Operational amplifier input                          |

#### **Input Pin Functions**

#### Input Signal Functions and Timing

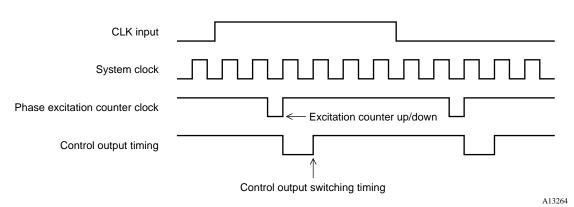

- CLK (phase switching clock)

- 1) Input frequency range: DC to 50kHz

- 2) Minimum pulse width: 10µs

- 3) Duty: 40 to 60% (However, the minimum pulse width takes precedence when M3 is high.)

- 4) Pin circuit type: Built-in pull-up resistor (20kΩ, typical) CMOS Schmitt trigger structure

- 5) Built-in multi-stage noise rejection circuit

- 6) Function:

- When M3 is high or open: The phase excited (driven) is advanced one step on each CLK rising edge.

- When M3 is low: The phase is advanced one step by both rising and falling edges, for a total of two steps per cycle.

CLK Input Acquisition Timing (M3 = Low)

• CWB (Method for setting the rotation direction)

- 1) Pin circuit type: Built-in pull-up resistor ( $20k\Omega$ , typical) CMOS Schmitt trigger structure

- 2) Function:

- When CWB is low: The motor turns in the clockwise direction.

- When CWB is high: The motor turns in the counterclockwise direction.

- Notes: When M3 is low, the CWB input must not be changed for about 6.25µs before or after a rising or falling edge on the CLK input.

- RETURN (Forcible return to the origin for the currently excited phase)

- 1) Pin circuit type: Built-in pull-up resistor (20kΩ, typical) CMOS Schmitt trigger structure

- 2) Built-in noise rejection circuit

- 3) Notes: The currently excited (driven) phase can be forcibly moved to the origin by switching this input from low to high. Normally, if this input is unused, it must be left open or connected to V<sub>CC</sub>2.

- ENABLE (Controls the on/off state of the A,  $\overline{A}$ , B, and  $\overline{B}$  excitation drive outputs and selects either operating or hold as the internal state of this hybrid IC.)

- 1) Pin circuit type: Built-in pull-up resistor (20kΩ, typical) CMOS Schmitt trigger structure

- 2) Function:

- When ENABLE is high or open: Normal operating state

- When ENABLE is low: This hybrid IC goes to the hold state and excitation drive output (motor current) is forcibly turned off. In this mode, the hybrid IC system clock is stopped and no inputs other than the reset input have any effect on the hybrid IC state.

#### STK672-060-E

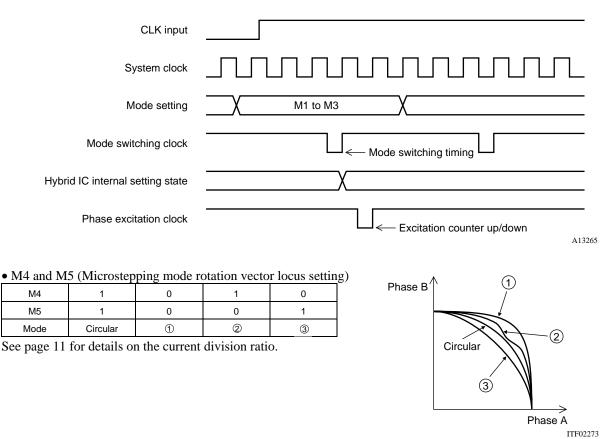

- M1, M2, and M3 (Excitation mode and CLK input edge timing selection)

- 1) Pin circuit type: Built-in pull-up resistor ( $20k\Omega$ , typical) CMOS Schmitt trigger structure

2) Function:

| 2)101    | ietion.              |                       |                        |                        |                                   |

|----------|----------------------|-----------------------|------------------------|------------------------|-----------------------------------|

| M2       | 0                    | 0                     | 1                      | 1                      |                                   |

| M1<br>M3 | 0                    | 1                     | 0                      | 1                      | Phase switching clock edge timing |

| 1        | 2 phase excitation   | 1-2 phase excitation  | W1-2 phase excitation  | 2W1-2 phase excitation | Rising edge only                  |

| 0        | 1-2 phase excitation | W1-2 phase excitation | 2W1-2 phase excitation | 4W1-2 phase excitation | Rising and falling edges          |

3) Valid mode setting timing: Applications must not change the mode in the period 5µs before or after a CLK signal rising or falling edge.

#### • RESET (Resets all parts of the system.)

1) Pin circuit type: Built-in pull-up resistor (20kΩ, typical) CMOS Schmitt trigger structure

2) Function:

- All circuit states are set to their initial values by setting the  $\overline{\text{RESET}}$  pin low. (Note that the pulse width must be at least 10 $\mu$ s.)

At this time, the A and  $\overline{B}$  phases are set to their origin, regardless of the excitation mode. The output current goes to about 71% after the reset is released.

- 3) Notes: When power is first applied to this hybrid IC, Vref must be established by applying a reset. Applications must apply a power on reset when the V<sub>CC</sub>2 power supply is first applied.

- Vref (Sets the current level used as the reference for constant-current detection.)

- 1) Pin circuit type: Analog input structure

2) Function:

- Constant-current control can be applied to the motor excitation current at 100% of the rated current by applying a voltage less than the control system power supply voltage  $V_{CC}2$  minus 2.5V.

- Applications can apply constant-current control proportional to the Vref voltage, with this value of 2.5V as the upper limit.

#### **Output Pin Functions**

| Pin No. | Symbol   | Function                        | Pin circuit type        |

|---------|----------|---------------------------------|-------------------------|

| 19      | MOI      | Phase excitation origin monitor | Standard CMOS structure |

| 20, 21  | MO1, MO2 | Phase excitation state monitor  | Standard CMOS structure |

#### **Output Signal Functions and Timing**

- A,  $\overline{A}$ , B, and  $\overline{B}$  (Motor phase excitation outputs)

- 1) Function:

- In the 4 phase and 2 phase excitation modes, a 3.75 $\mu$ s (typical) interval is set up between the A and  $\overline{A}$  and B and  $\overline{B}$  output signal transition times.

- MO1, MO2, and MOI (Phase excitation state monitors)

- 1) Pin circuit type: Standard CMOS structure

- 1) Function:

- Output of the current phase excitation output state.

| Phase coordinate | Phase A Phase B |   | Phase A | Phase B |

|------------------|-----------------|---|---------|---------|

| MO1              | 1               | 0 | 0       | 1       |

| MO2              | 0               | 1 | 0       | 1       |

MOI outputs a 0 when each phase is at the origin, and outputs a 1 otherwise.

• Current division ratios set by M3, M4, and M5 ...... Values provided for reference purposes.

|                                    | Mode           |        | Circular | 1      | 2      | 3      |             |                 |       |

|------------------------------------|----------------|--------|----------|--------|--------|--------|-------------|-----------------|-------|

| 0                                  | Setting M3 = 0 |        | M4 = 1   | M4 = 0 | M4 = 1 | M4 = 1 | Units       | Number of steps |       |

| Setting                            |                | M3 = 1 | M5 = 1   | M5 = 0 | M5 = 0 | M5 = 1 |             |                 |       |

|                                    |                |        | 15       | 16     | 16     | 15     |             |                 | 1/16  |

|                                    |                | 2W1-2  | 21       | 25     | 24     | 20     |             | 1/8             | 2/16  |

|                                    |                |        | 31       | 34     | 33     | 28     | -<br>-<br>- |                 | 3/16  |

|                                    |                | 2W1-2  | 40       | 44     | 41     | 38     |             | 2/8             | 4/16  |

|                                    |                |        | 47       | 50     | 49     | 44     |             |                 | 5/16  |

|                                    |                | 2W1-2  | 55       | 59     | 56     | 53     |             | 3/8             | 6/16  |

| Current<br>division 4W1-2<br>ratio | 414/4 0        |        | 63       | 67     | 63     | 60     | %           |                 | 7/16  |

|                                    | 2W1-2          | 71     | 75       | 70     | 67     | %      | 4/8         | 8/16            |       |

|                                    |                |        | 76       | 81     | 76     | 73     |             |                 | 9/16  |

|                                    | 2W1-2          | 2W1-2  | 83       | 87     | 84     | 81     |             | 5/8             | 10/16 |

|                                    |                |        | 87       | 92     | 88     | 84     |             |                 | 11/16 |

|                                    |                | 2W1-2  | 92       | 95     | 95     | 91     |             | 6/8             | 12/16 |

|                                    |                |        | 96       | 98     | 98     | 93     |             |                 | 13/16 |

|                                    |                | 2W1-2  | 100      | 100    | 100    | 100    |             | 7/8             | 14/16 |

[Load conditions]

$$V_{CC}1 = 24V, V_{CC}2 = 5V, R/L = 3.5/3.8mH$$

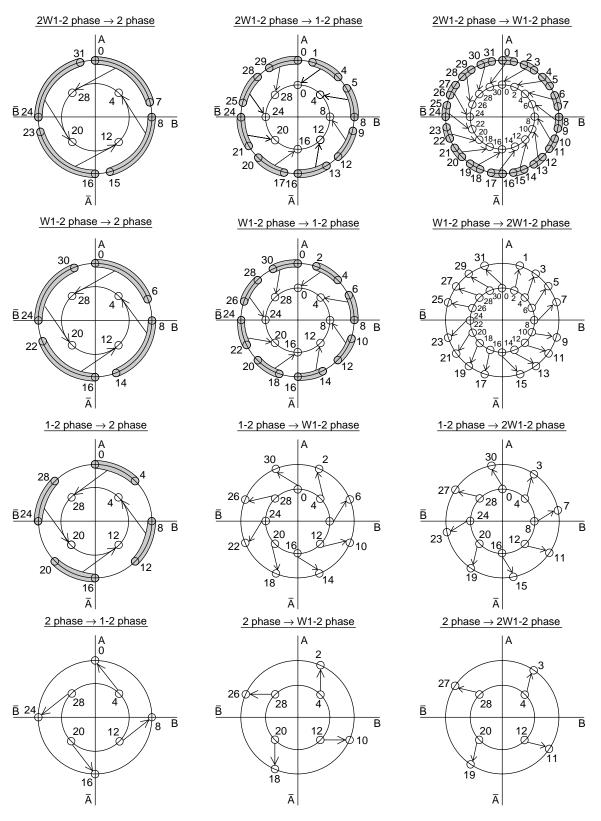

#### **Phase States During Excitation Switching**

R

• Excitation phases before and after excitation mode switching <clockwise direction>

• Excitation phases before and after excitation mode switching <counterclockwise direction>

A13267

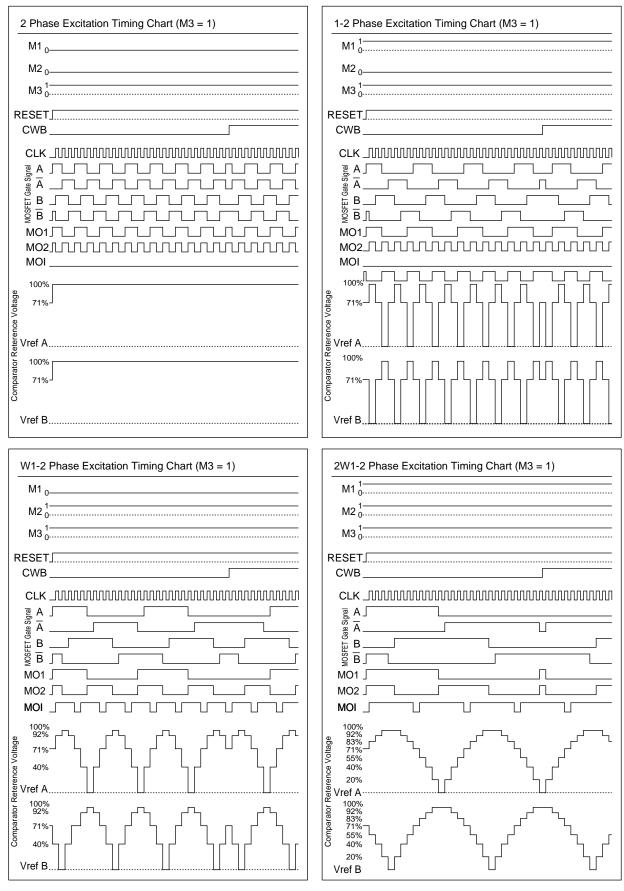

#### **Excitation Time and Timing Charts**

• CLK rising edge operation

#### • CLK rising and falling edge operation

ITF02275

#### **Thermal Design**

<Hybrid IC Average Internal Power Loss Pd>

The main elements internal to this hybrid IC with large average power losses are the current control devices, the regenerative current diodes, and the current detection resistor. Since sine wave drive is used, the average power loss during microstepping drive can be approximated by applying a waveform factor of 0.64 to the square wave loss during 2 phase excitation.

The losses in the various excitation modes are as follows.

2 phase excitation

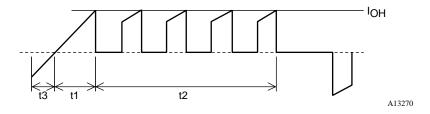

$$Pd_{2EX} = (Vsat+Vdf) \cdot \frac{fclock}{2} \cdot I_{OH} \cdot t2 + \frac{I_{OH} \cdot fclock}{2} \cdot (Vsat \cdot t1 + Vdf \cdot t3)$$

1-2 phase excitation

$$Pd_{1-2EX} = 0.64 \cdot \{(Vsat+Vdf) \cdot \frac{fclock}{4} \cdot I_{OH} \cdot t_{2} + \frac{I_{OH} \cdot fclock}{4} \cdot (Vsat \cdot t_{1} + Vdf \cdot t_{3})\}$$

W1-2 phase excitation  $PdW_{1-2EX} = 0.64 \cdot \{(Vsat+Vdf) \cdot \frac{fclock}{8} \cdot I_{OH} \cdot t_2 + \frac{I_{OH} \cdot fclock}{8} \cdot (Vsat \cdot t_1 + Vdf \cdot t_3)\}$

2W1-2 phase excitation Pd<sub>2W1-2EX</sub> =  $0.64 \cdot \{(Vsat+Vdf) \cdot \frac{fclock}{16} \cdot I_{OH} \cdot t_2 + \frac{I_{OH} \cdot fclock}{16} \cdot (Vsat \cdot t_1 + Vdf \cdot t_3)\}$

4W1-2 phase excitation Pd4W1-2EX =  $0.64 \cdot \{(Vsat+Vdf) \cdot \frac{fclock}{16} \cdot I_{OH} \cdot t2 + \frac{I_{OH} \cdot fclock}{16} \cdot (Vsat \cdot t1 + Vdf \cdot t3)\}$

Here, t1 and t3 can be determined from the same formulas for all excitation methods.

$$t1 = \frac{-L}{R+0.7} \quad \ell n \ (1 - \frac{R+0.7}{V_{CC}1} + I_{OH}) \qquad \qquad t3 = \frac{-L}{R} \cdot \ell n \ (\frac{V_{CC}1+0.7}{I_{OH} \cdot R + V_{CC}1+0.7})$$

However, the formula for t2 differs with the excitation method.

2 phase excitation  $t2 = \frac{2}{\text{fclock}} - (t1+t3)$  1-2 phase excitation  $t2 = \frac{3}{\text{fclock}} - t1$

W1-2 phase excitation  $t2 = \frac{7}{\text{fclock}} - t1$ 4W1-2 phase excitation  $t2 = \frac{15}{\text{fclock}} - t1$

Motor Phase Current Model Figure (2 Phase Excitation)

fclock : CLK input frequency (Hz)

| Vsat | : The voltage drop of the power MOSFET and the current detection resistor (V) |

|------|-------------------------------------------------------------------------------|

|------|-------------------------------------------------------------------------------|

- Vdf : The voltage drop of the body diode and the current detection resistor (V)

- I<sub>OH</sub> : Phase current peak value (A)

- t1 : Phase current rise time (s)

t3

- t2 : Constant-current operating time (s)

- V<sub>CC</sub>1 : Supply voltage applied to the motor (V)

- L : Motor inductance (H)

- : Phase switching current regeneration time (s)

- R : Motor winding resistance  $(\Omega)$

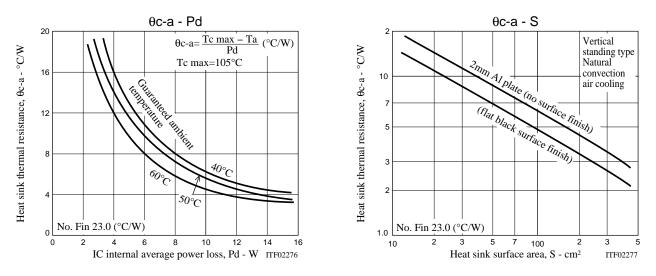

<Determining the Size of the Hybrid IC Heat Sink>

Determine  $\theta$ c-a for the heat sink from the average power loss determined in the previous item.

$$\theta c-a = \frac{Tc \max - Ta}{Pd} [^{\circ}C/W]$$

Tc max: Hybrid IC substrate temperature (°C) Ta: Application internal temperature (°C)

PdEX: Hybrid IC internal average loss (W)

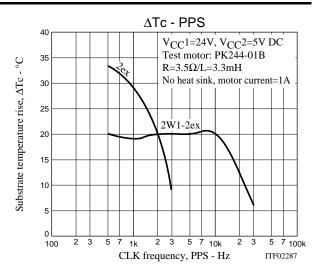

Determine  $\theta$ c-a from the above formula and then size S (in cm<sup>2</sup>) of the heat sink from the graphs shown below. The ambient temperature of the device will vary greatly according to the air flow conditions within the application. Therefore, always verify that the size of the heat sink is adequate to assure that the Hybrid IC back surface (the aluminum plate side) will never exceed a Tc max of 105°C, whatever the operating conditions are.

Next we determine the usage conditions with no heat sink by determining the allowable hybrid IC internal average loss from the thermal resistance of the hybrid IC substrate, namely 23°C/W.

For a Tc max of 105°C at an ambient temperature of 50°C

For a Tc max of 105°C at an ambient temperature of 40°C

$$Pd_{EX} = \frac{105 - 50}{23} = 2.3W$$

$Pd_{EX} = \frac{105 - 40}{23} = 2.8W$ This hybrid IC can be used with no heat sink as long as it is used at operating conditions below the losses listed above.

<Hybrid IC internal power element (MOSFET) junction temperature calculation>

The junction temperature, Tj, of each device can be determined from the loss Pds in each transistor and the thermal resistance  $\theta j$ -c.

$T_j = T_c + \theta_{j-c} \times Pds$  (°C)

(See  $\Delta Tc$  – Pd curve in the graph on page 19.)

Here, we determine Pds, the loss for each transistor, by determining PdFX in each excitation mode.  $Pds = Pd_{EX}/4$

The steady-state thermal resistance  $\theta_j$ -c of a power MOSFET is 18°C/W.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employeer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor: <u>STK672-060-E</u> <u>STK672-060GEVB</u>