SLUS318B - APRIL 1999 - REVISED JANUARY 2002

# BRUSHLESS DC MOTOR CONTROLLER

#### **FEATURES**

- Two-Quadrant and Four-Quadrant Operation

- Integrated Absolute Value Current Amplifier

- Pulse-by-Pulse and Average Current Sensing

- Accurate, Variable Duty-Cycle Tachometer Output

- Trimmed Precision Reference

- Precision Oscillator

- Direction Output

## **DESCRIPTION**

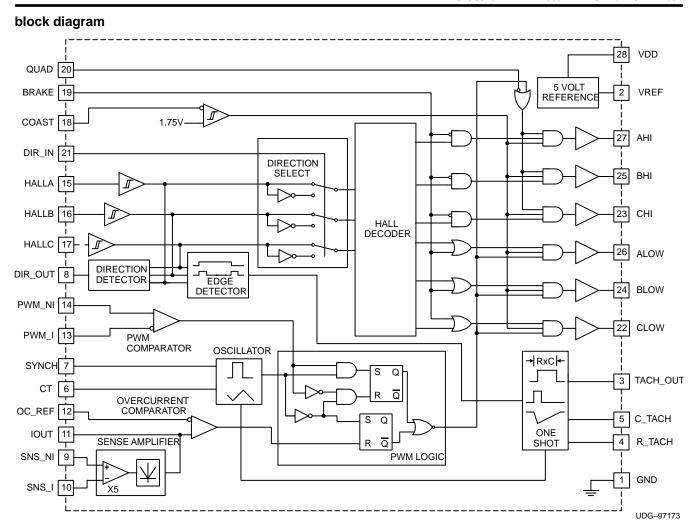

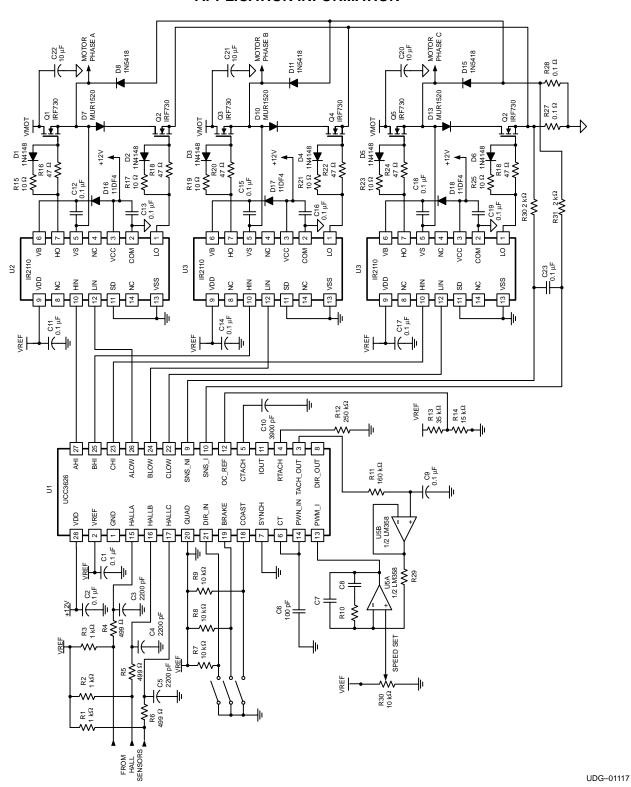

The UCC3626 motor controller device combines many of the functions required to design a high-performance, two- or four-quadrant, three-phase, brushless dc motor controller into one package. Rotor position inputs are decoded to provide six outputs that control an external power stage. A precision triangle oscillator and latched comparator provide PWM motor control in either

voltage- or current-mode configurations. The oscillator is easily synchronized to an external master clock source via the SYNCH input. Additionally, a QUAD select input configures the chip to modulate either the low-side switches only, or both upper and lower switches, allowing the user to minimize switching losses in less demanding two-quadrant applications.

The device includes a differential current-sense amplifier and absolute-value circuit which provide an accurate reconstruction of motor current, useful for pulse-by-pulse overcurrent protection, as well as closing a current control loop. A precision tachometer is also provided for implementing closed-loop speed control. The TACH\_OUT signal is a variable duty-cycle, frequency output, which can be used directly for digital control or filtered to provide an analog feedback signal. Other features include COAST, BRAKE, and DIR\_IN commands, along with a direction output, DIR\_OUT.

#### **AVAILABLE OPTIONS**

|               | PACKAGED DEVICES |                           |                            |  |  |

|---------------|------------------|---------------------------|----------------------------|--|--|

| TA            | PDIP<br>(N)      | SOIC <sup>†</sup><br>(DW) | TSSOP <sup>†</sup><br>(PW) |  |  |

| –40°C to 85°C | UCC2626N         | UCC2626DW                 | UCC2626PW                  |  |  |

| 0°C to 70°C   | UCC3626N         | UCC3626DW                 | UCC3626PW                  |  |  |

†The DW and PW packages are available taped and reeled. Add TR suffix to device type (e.g. UCC2626DWTR) to order quantities of 2,000 devices per reel.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I PACKAG<br>TOP VIEW                                                                             | _                                              | ים                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DW and PW PACKAGES<br>(TOP VIEW)                                                                                  |                                              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| GND [ VREF [ ] VREF [ | 2 27<br>3 26<br>4 25<br>5 24<br>6 23<br>7 22<br>8 21<br>9 20<br>10 19<br>11 18<br>12 17<br>13 16 | ALOW BHI BLOW CHI CLOW DIR_IN QUAD BRAKE COAST | GND UVREF UV | 1 28<br>2 27<br>3 26<br>4 25<br>5 24<br>6 23<br>7 22<br>8 21<br>9 20<br>10 19<br>11 18<br>12 17<br>13 16<br>14 15 | CHI CLOW DIR_IN QUAD BRAKE COAST HALLC HALLB |  |

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage V <sub>DD</sub>                                         | 15 V                     |

|------------------------------------------------------------------------|--------------------------|

| Input voltage, BRAKE, COAST, DIR_IN, HALLA, HALLB, HALLC,              |                          |

| OC_REF, QUAD, SYNCH, PWM_I, PWM_NI                                     | 0.3 V to V <sub>DD</sub> |

| SNS_I, SNS_NI                                                          | 0.5 V to V <sub>DD</sub> |

| Output current AHI, ALOW, BHI, BLOW, CHI, CLOW                         | ±200 mA                  |

| DIR_OUT, IOUT, TACH_OUT,                                               | 1 mA                     |

| VREF                                                                   | –20 mA                   |

| Junction temperature range, T <sub>J</sub>                             | –55°C to 150°C           |

| Storage temperature range, T <sub>stq</sub>                            | –65°C to 150°C           |

| Lead temperature soldering 1,6 mm (1/16 inch) from case for 10 seconds | 300°C                    |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> All voltages are with respect to GND. Currents are positive into negative out of the specified terminal.

electrical characteristics over recommended operating conditions, VCC = 12 V; CT = 1 nF, R\_TACH = 250 k $\Omega$ , C\_TACH = 100 pF,  $T_A$  =  $T_J$ ,  $T_A$  =  $-40^{\circ}$ C to 85°C for the UCC2626, and 0°C to 70°C for the UCC3626 (unless otherwise noted)

#### overall

| PARAMETER      | TEST CONDITIONS       | MIN | TYP | MAX | UNIT |

|----------------|-----------------------|-----|-----|-----|------|

| Supply current | Outputs not switching | 1   | 3   | 5   | mA   |

# undervoltage lockout

| PARAMETER       | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|-----------------|-----------------|------|------|------|------|

| Start threshold |                 | 9.0  | 10.5 | 11.0 | ٧    |

| UVLO hysteresis |                 | 0.35 | 0.40 | 0.50 | V    |

## 5-V reference

| PARAMETER               | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|-------------------------|-----------------------------------|-----|-----|-----|------|

| Output voltage          | I <sub>VREF</sub> = -2 mA         | 4.9 | 5   | 5.1 | ٧    |

| Line regulation voltage | 11 V < VCC < 14.5 V               |     |     | 10  | mV   |

| Load regulation voltage | -1 mA > I <sub>VREF</sub> > -5 mA |     |     | 10  | mV   |

| Short circuit current   |                                   | 40  | 120 | 240 | mA   |

#### coast input comparator

| PARAMETER         | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|-------------------|-----------------|------|------|------|------|

| Threshold voltage |                 | 1.60 | 1.75 | 2.00 | V    |

| Hysteresis        |                 | 0.04 | 0.10 | 0.16 | V    |

# current sense amplifier

| •                         |         |                             |      |      |      |      |

|---------------------------|---------|-----------------------------|------|------|------|------|

| PARAMETER                 | _       | TEST CONDITIONS             | MIN  | TYP  | MAX  | UNIT |

| Input offset voltage      |         | VCM = 0 V                   |      |      | 8    | mV   |

| Input bias current        |         | VCM = 0 V                   | 5    | 10   | 15   | μΑ   |

| Gain                      |         | VCM = 0 V                   | 4.85 | 5.00 | 5.15 | V/V  |

| PSRR                      |         | 11 V < VCC < 14.5 V         | 60   |      |      | dB   |

| High-level output voltage |         | I <sub>IOUT</sub> = -100 μA | 6.3  |      |      | V    |

| Low-level output voltage  |         | I <sub>IOUT</sub> = 100 μA  |      |      | 70   | mV   |

|                           | UCC3626 | V <sub>IOUT</sub> = 2 V     | 500  |      |      | μΑ   |

| Output source current     | UCC2626 | V <sub>IOUT</sub> = 2 V     | 300  |      |      | μΑ   |

## pwm comparator

| PARAMETER               | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|-------------------------|-----------------|-----|---------|------|

| Input common mode range |                 | 2.0 | 8.      | ) V  |

| Propagation delay time  |                 | 75  | 15      | ) ns |

## overcurrent comparator

| PARAMETER               | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------------|-----------------|-----|-----|-----|------|

| Input common mode range |                 | 0.0 |     | 5.0 | ٧    |

| Propagation delay time  |                 | 50  | 175 | 250 | ns   |

# logic inputs

| PARAMETER                      | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|--------------------------------|-------------------------|-----|-----|-----|------|

| High-level logic input voltage | QUAD, BRAKE, DIR, SYNCH | 3.6 |     |     | V    |

| Low-level logic input voltage  | QUAD, BRAKE, DIR, SYNCH |     |     | 1.4 | V    |

electrical characteristics over recommended operating conditions, VCC = 12 V; CT = 1 nF, R\_TACH = 250 k $\Omega$ , C\_TACH = 100 pF,  $T_A$  =  $T_J$ ,  $T_A$  =  $-40^{\circ}$ C to 85°C for the UCC2626, and 0°C to 70°C for the UCC3626 (unless otherwise noted)

# hall buffer inputs

| PARAMETER                | TEST CONDITIONS     | MIN | TYP | MAX | UNIT |

|--------------------------|---------------------|-----|-----|-----|------|

| High-level input voltage | HALLA, HALLB, HALLC | 1.7 | 1.9 | 2.1 | V    |

| Hysteresis               | HALLA, HALLB, HALLC | 0.6 |     | 1.0 | ٧    |

| Input current            | 0V < VIN < 5 V      |     | -25 |     | μΑ   |

## oscillator

| PARAMETER                     | TEST CONDITIONS                  | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|----------------------------------|------|------|------|------|

| Frequency                     | $R_{TACH}$ = 250 kΩ, $C_T$ = 1nF | 9.0  | 10.0 | 11.0 | kHz  |

| Frequency change with voltage | 12 V < VCC < 14.5 V              |      |      | 3%   |      |

| CT peak voltage               |                                  | 7.25 | 7.5  | 7.75 | V    |

| CT peak-to-valley voltage     |                                  | 4.75 | 5.0  | 5.25 | V    |

| SYNCH pin minimum pulse width |                                  | 500  |      |      | ns   |

## tachometer

| PARAMETI                          | ER      | TEST CONDITIONS              | MIN     | TYP   | MAX   | UNIT |

|-----------------------------------|---------|------------------------------|---------|-------|-------|------|

| High-level output voltage/VREF    |         | $I_{OUT} = -10 \mu A$        | 99%     |       | 100%  |      |

| Low-level output voltage          |         | I <sub>OUT</sub> = 10 μA     | 0       |       | 20    | mV   |

| High-level on-resistance          |         | $I_{OUT} = -100 \mu\text{A}$ | –100 μΑ |       |       |      |

| Low-level on-resistance           |         | I <sub>OUT</sub> = 100 μA    |         | 1     | 1.5   | kΩ   |

| High-level ramp threshold voltage | Э       |                              |         | 2.5   |       | V    |

| Ramp voltage                      |         |                              | 2.375   | 2.500 | 2.625 | V    |

| CTACH charge current              |         | R <sub>TACH</sub> = 49.9 kΩ  | 48      | 51    | 53    | μΑ   |

| 0                                 | UCC3626 | See Note 1                   | -3%     |       | 3%    |      |

| On-time accuracy                  | UCC2626 | See Note 1                   | -4%     |       | 3%    |      |

# direction output

| PARAMETER                 | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|---------------------------|----------------------------|-----|-----|-----|------|

| High-level output voltage | I <sub>OUT</sub> = -100 μA | 4.5 |     | 5.2 | V    |

| Low-level output voltage  | I <sub>OUT</sub> = 100 μA  | 0   |     | 0.5 | V    |

## output

| PARAMETER                        | TEST CONDITIONS              | MIN | TYP | MAX  | UNIT |

|----------------------------------|------------------------------|-----|-----|------|------|

| Maximum duty cycle               |                              |     |     | 100% |      |

| Level and autoritizations        | I <sub>OUT</sub> = 2 mA      |     |     | 0.5  | >    |

| Low-level output voltage         | I <sub>OUT</sub> = 100 μA    | 0.0 |     | 0.1  | >    |

| I Pale Level and such as the sec | $I_{OUT} = -2 \text{ mA}$    | 4.0 | 4.8 | 5.2  | V    |

| High-level output voltage        | $I_{OUT} = -100 \mu\text{A}$ | 4.7 |     | 5.2  | >    |

| Rise and fall time               | CI = 10 pF                   |     |     | 100  | ns   |

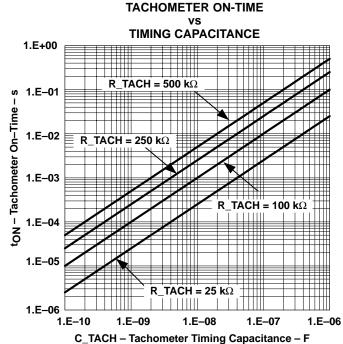

NOTE 1:  $t_{ON}$  is calculated using the formula  $t_{ON} = \frac{C_{TACH} \times (V_{HI} - V_{LO})}{I_{CHARGE}}$

## pin descriptions

**AHI, BHI, CHI**: Digital outputs used to control the high-side switches in a three-phase inverter. For specific decoding information reference Table I.

**ALOW, BLOW, CLOW**: Digital outputs used to control the low-side switches in a three-phase inverter. For specific decoding information reference Table I.

**BRAKE**: BRAKE is a digital input which causes the device to enter brake mode. In brake mode all three high-side outputs (AHI, BHI & CHI) are turned off, while all three lowside outputs (ALOW, BLOW, CLOW) are turned on. During brake mode the tachometer output remains operational. The only conditions that can inhibit the low-side commands during brake are UVLO, exceeding peak current, the output of the PWM comparator, or the COAST command.

**COAST**: The COAST input consists of a hysteretic comparator which disables the outputs. The input is useful in implementing an overvoltage bus clamp in four-quadrant applications. The outputs are disabled when the input is above 1.75 V.

**CT**: This pin is used in conjunction with the R\_TACH pin to set the frequency of the oscillator. A timing capacitor is normally connected between this point and ground and is alternately charged and discharged between 2.5 V and 7.5 V.

**C\_TACH**: A timing capacitor is connected between this pin and ground to set the width of the TACH\_OUT pulse. The capacitor is charged with a current set by the resistor on pin R\_TACH.

**DIR\_IN**: DIR\_IN is a digital input which determines the order in which the HALLA, HALLB, and HALLC inputs are decoded. For specific decode information reference Table I.

**DIR\_OUT**: DIR\_OUT represents the actual direction of the rotor as decoded from the HALLA, HALLB, and HALLC inputs. For any valid combination of HALLA, HALLB, and HALLC inputs there are two valid transitions; one of which translates to a clockwise rotation and another which translates to a counterclockwise rotation. The polarity of DIR\_OUT is the same as DIR\_IN while motoring, (i.e. sequencing from top to bottom in Table 1.)

**GND**: GND is the reference ground for all functions of the part. Bypass and timing capacitors should be terminated as close as possible to this point.

**HALLA, HALLB, HALLC**: These three inputs are designed to accept rotor position information positioned 120° apart. For specific decode information reference Table I. These inputs should be externally pulled up to VREF or another appropriate external supply.

**IOUT**: IOUT represents the output of the current sense and absolute value amplifiers. The output signal appearing is a representation of the following expression:

$$I_{OUT} = ABS(I_{SNS I} - I_{SNS NI}) \times 5$$

This output can be used to close a current control loop as well as provide additional filtering of the current sense signal.

**OC\_REF**: OC\_REF is an analog input which sets the trip voltage of the overcurrent comparator. The sense input of the comparator is internally connected to the output of the current sense amplifier and absolute value circuit.

**PWM\_NI**: PWM\_NI is the noninverting input to the PWM comparator.

**PWM\_I**: PWM\_I is the inverting input to the PWM comparator.

**QUAD**: The QUAD input selects between two-quadrant operation (QUAD = 0) and four-quadrant operation (QUAD = 1). When in two-quadrant mode, only the low-side devices are effected by the output of the PWM comparator. In four-quadrant mode both high- and low-side devices are controlled by the PWM comparator.

# pin descriptions

**SYNCH**: The SYNCH input is used to synchronize the PWM oscillator with an external digital clock. When using the SYNCH feature, a resistor equal to R\_TACH must be placed in parallel with CT. When not using the SYNCH feature, SYNCH must be grounded.

**SNS\_NI, SNS\_I**: These inputs are the noninverting and inverting inputs to the current sense amplifier, respectively. The integrated amplifier is configured for a gain of five. An absolute value function is also incorporated into the output in order to provide a representation of actual motor current when operating in four-quadrant mode.

**TACH\_OUT**: TACH\_OUT is the output of a monostable triggered by a change in the commutation state, thus providing a variable duty cycle, frequency output. The on time of the monostable is set by the timing capacitor connected to C\_TACH. The monostable is capable of being retriggered if a commutation occurs during its on-time.

**R\_TACH**: A resistor connected between R\_TACH and ground programs the current for both the oscillator and tachometer.

**VDD**: VDD is the input supply connection for this device. Undervoltage lockout keeps the outputs off for input below 10.5 V. The input should be bypassed with a 0.1-μF ceramic capacitor, minimum.

**VREF**: VREF is a 5-V, 2% trimmed reference output with 5 mA of maximum available output current. This pin should be bypassed to ground with a ceramic capacitor with a value of at least 0.1  $\mu$ F.

#### **APPLICATION INFORMATION**

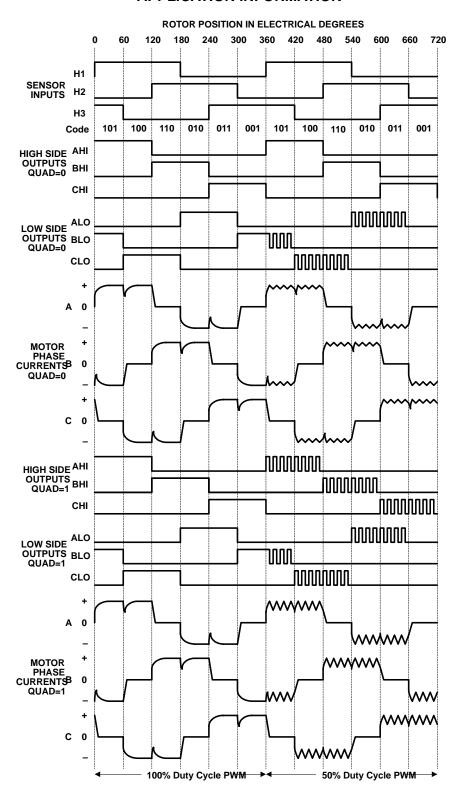

Table 1 provides the decode logic for the six outputs, AHI, BHI, CHI, ALOW, BLOW, and CLOW as a function of the BRAKE, COAST, DIR\_IN, HALLA, HALLB, and HALLC inputs.

HALL HIGH-SIDE LOW-SIDE **INPUTS OUTPUTS OUTPUTS** DIR\_IN **BRAKE COAST** Α В С Α В Α В Χ Χ Χ Χ Χ Χ Х Χ Χ Χ Χ

**Table 1. Commutation Truth Table**

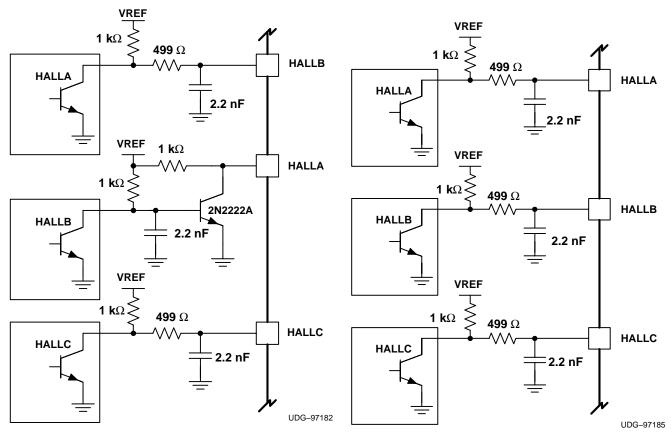

The UCC3626 is designed to operate with  $120^{\circ}$  position sensor encoding. In this format, the three position sensor signals are never simultaneously high or low. Motors whose sensors provide  $60^{\circ}$  encoding, can be converted to  $120^{\circ}$  using the circuit shown in Figure 1.

In order to prevent noise from commanding improper commutation states, some form of low-pass filtering on HALLA, HALLB, and HALLC is recommended. Passive RC networks generally work well and should be located as close as possible to the device. Figure 2 illustrates these techniques.

Figure 1. Converting Hall Code From 60° to 120°

Figure 2. Passive Hall Filtering Technique

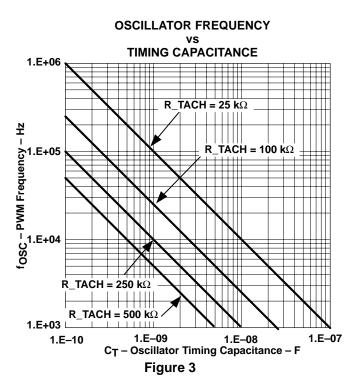

## configuring the oscillator

The UCC3626 oscillator is designed to operate at frequencies up to 250 kHz and provide a triangle waveform on CT with a peak-to-peak amplitude of 5 V for improved noise immunity. The current used to program CT is derived from the R\_TACH resistor according to the following equation:

$$I_{OSC} = \frac{25}{R\_TACH}$$

Amps (1)

The oscillator frequency is set by R\_TACH and CT according to the following relationship:

$$f_{OSC} = \frac{2.5}{R\_TACH \times CT} Hz$$

(2)

Timing resistor values should be between 25 k $\Omega$  and 500 k $\Omega$ , while capacitor values should be between 100 pF and 1  $\mu$ F. Figure 3 provides a graph of oscillator frequency for various combinations of timing components. As with any high-frequency oscillator, timing components should be located as close as possible to the device pins when laying out the printed-circuit board. It is also important to reference the timing capacitor directly to the ground pin on the UCC3626 rather than daisy chaining it to another trace or the ground plane. This technique prevents switching current spikes in the local ground from causing jitter in the oscillator.

## synchronizing the oscillator

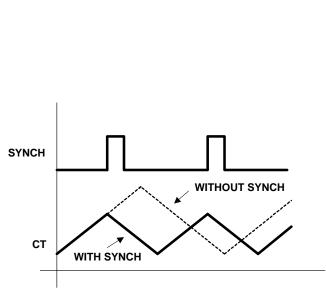

A common system specification is to have all oscillators synchronized to a master clock. The UCC3626 provides a SYNCH input for this purpose. The SYNCH input is designed to interface with a digital clock pulse generated by the master oscillator. A positive-going edge on this input causes the UCC3626 oscillator to begin discharging. In order for the slave oscillator to function properly, it must be programmed for a frequency slightly lower than that of the master. Also, a resistor equal to R\_TACH must be placed in parallel with CT. Figure 4 illustrates the waveforms for a slave oscillator programmed to 20 kHz with a master frequency of 30 kHz. The SYNCH pin must be grounded when not used.

## programming the tachometer

The UCC3626 tachometer consists of a precision 5-V monostable, triggered by either a rising or falling edge on any of the three Hall inputs, HALLA, HALLB, and HALLC. The resulting TACH\_OUT waveform is a variable duty-cycle square wave whose frequency is proportional to motor speed, as given by:

$$TACH\_OUT = \frac{V \times P}{20} Hz$$

(3)

where P is the number of motor pole pairs and V is motor velocity in RPM.

The on time of the monostable is programmed via timing resistor R\_TACH and capacitor C\_TACH according to the following equation:

$$t_{ON} = R_TACH \times C_TACH \text{ sec}$$

(4)

Figure 5 provides a graph of on times for various combinations of R\_TACH and C\_TACH. On time is typically set to a value less than the minimum TACH OUT period as given by:

$$t_{PERIOD (min)} = \frac{20}{V_{MAX} \times P} \text{ sec}$$

(5)

where P is the number of motor pole pairs and V is motor velocity in RPM.

Figure 4. Oscillator Waveforms

Figure 5

UDG-97188

#### **APPLICATION INFORMATION**

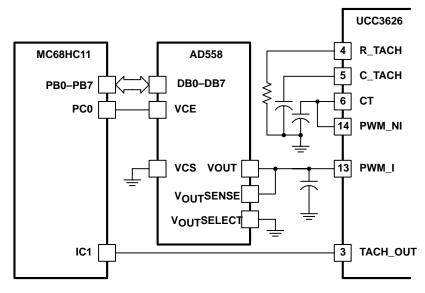

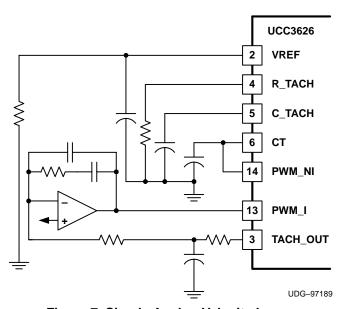

The TACH\_OUT signal can be used to close a digital velocity loop using a microcontroller, as shown in Figure 6, or directly low-pass filtered in an analog implementation, Figure 7.

Figure 6. Digital Velocity Loop Implementation Using MC68HC11

#### two quadrant vs four quadrant control

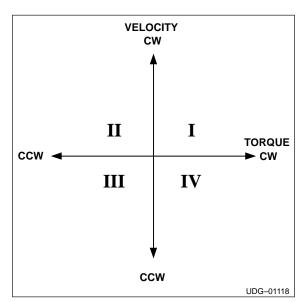

Figure 8 illustrates the four possible quadrants of operation for a motor. *Two-quadrant control* refers to a system in which operation is limited to quadrants I and III (where torque and velocity are in the same direction). With a two-quadrant brushless dc amplifier, there are no provisions other than friction to decelerate the load, limiting the approach to less demanding applications. *Four-quadrant controllers*, on the other hand, provide controlled operation in all quadrants, including II and IV, where torque and rotation are of opposite direction.

Figure 7. Simple Analog Velocity Loop

Figure 8. Four Quadrants of Operation

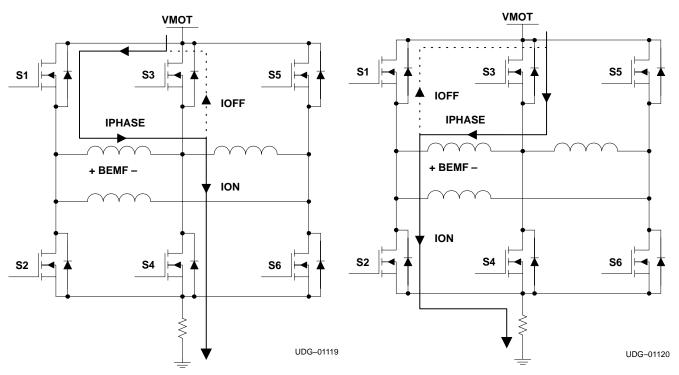

When configured for two-quadrant operation, (QUAD=0), the UCC3626 modulates only the low-side devices of the output power stage. The current paths within the output stage during the PWM on- and off-times are illustrated in Figure 9. During the *on* interval, both switches are on, and current flows through the load down to ground. During the *off* time, the lower switch is shut off, and the motor current circulates through the upper half bridge via the flyback diode. The motor is assumed to be operating in either quadrant I or III.

If operation is attempted in quadrants II or IV by changing the DIR bit and reversing the torque, switches 1 and 4 are turned off and switches 2 and 3 turned on. Under this condition motor current very quickly decays, reverses direction and increases until the control threshold is reached. At this point, switch 2 turns off and current once again circulates in the upper half bridge. However, in this case, the motor's BEMF is in phase with the current, (i.e. the motor's direction of rotation has not yet changed.) Figure 10 illustrates the current paths when operating in this mode. Under these conditions there is nothing to limit the current other than motor and drive impedance. These high-circulating currents can result in damage to the power devices in addition to high, uncontrolled torque.

Figure 9. Two-Quadrant Chopping

Figure 10. Two-Quadrant Reversal

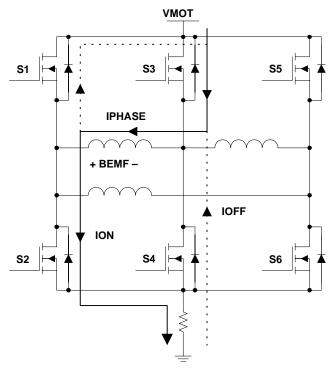

By pulse width modulating both the upper and lower power devices (QUAD=1), motor current always decays during the PWM *off* time, eliminating any uncontrolled circulating currents. In addition, current always flows through the current sense resistor, providing a suitable feedback signal. Figure 11 illustrates the current paths during a four-quadrant torque reversal. Motor drive waveforms for both two- and four-quadrant operation are illustrated in Figure 12.

Figure 11. Four-Quadrant Reversal

UDG-01121

Figure 12. Motor Drive and Current Waveforms for Two-Quadrant (QUAD=0) and Four-Quadrant (QUAD=1) Operation

UDG-97190

#### power stage design considerations

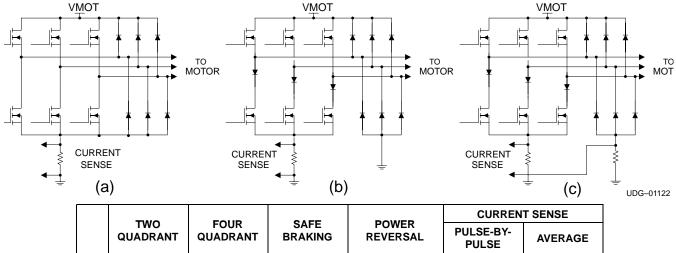

The flexible architecture of the UCC3626 requires the user to pay close attention to the design of the power output stage. Two- and four-quadrant applications not requiring the brake function are able to use the power stage approach illustrated in Figure 13a. In many cases the body diode of the MOSFET can be used to reduce parts count and cost. If efficiency is a key requirement, Schottky diodes can be used in parallel with the switches.

UDG-97190

NO YES YES Four-Quad Only YES YES (a) YES NO (b) NO YES No YES YES YES YES YES (c) YES Four-Quad Only

Figure 13. Power Stage Topologies

If the system requires a braking function, diodes must be added in series with the lower power devices and the lower flyback diodes must be returned to ground, as pictured in Figure 13b, and 13c. This requirement prevents brake currents from circulating in the lower half bridge and bypassing the sense resistor. In addition, the combination of braking and four-quadrant control necessitates an additional resistor in the diode path to sense current during the PWM *off* time as illustrated in Figure 13c.

#### current sensing

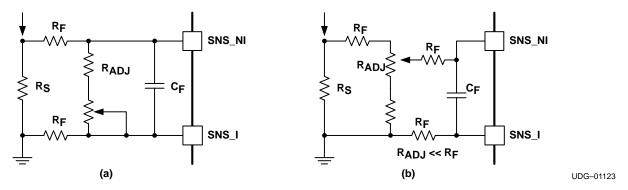

The UCC3626 includes a differential current-sense amplifier with a fixed gain of five, along with an absolute value circuit. The current-sense signal should be low pass filtered to eliminate leading-edge spikes. In order to maximize performance, the input impedance of the amplifier should be balanced. If the sense voltage must be trimmed for accuracy reasons, a low-value input divider or a differential divider should be used to maintain impedance matching, as shown in Figure 14.

Figure 14. (a) Differential Divider and (b) Low-Value Divider

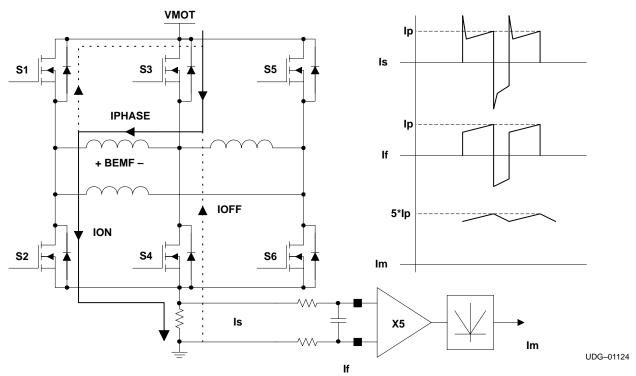

With four-quadrant chopping, motor current always flows through the sense resistor. However, during the flyback period the polarity across the sense resistor is reversed. The absolute value amplifier cancels the polarity reversal by inverting the negative sense signal during the flyback time, see Figure 15. Therefore, the output of the absolute value amplifier is a reconstructed analog of the motor current, suitable for protection as well as feedback loop closure.

Figure 15. Current Sense Amplifier Waveform

Figure 17 illustrates a simple 175-V, 2-A, two-quadrant velocity controller using the UCC3626. The power stage is designed to operate with a rectified off-line supply using IR2210s to provide the interface between the low voltage control signals and the power MOSFETs. The power topology illustrated in Figure 13c is implemented in order to provide braking capability.

Figure 16. Four-Quadrant Control Loop

The controller's speed command is set by potentiometer R30, while the speed feedback signal is obtained by low-pass filtering and buffering the TACH\_OUT signal using R11 and C9. Small signal compensation of the velocity control loop is provided by amplifier U5A, whose output is used to control the PWM duty cycle. The integrating capacitor, C8, places a pole at 0 Hz and a zero in conjunction with R10. This zero can be used to cancel the low-frequency motor pole and to cross the loop-over with a –20 dB gain response.

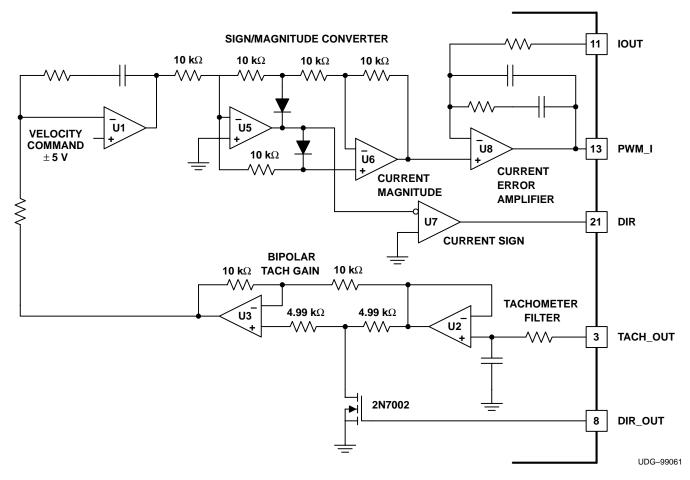

Four-quadrant applications require the control of motor current. Figure 16 illustrates a sign/magnitude current control loop within an outer bipolar velocity loop using the UCC3626. U1 serves as the velocity loop error amplifier and accepts a  $\pm$  5-V command signal. Velocity feedback is provided by low-pass filtering and scaling the TACH\_OUT signal using U2. The direction output switch, DIR\_OUT, and U3 set the polarity of the tachometer gain according to the direction of rotation. The output of the velocity error amplifier, U1, is then converted to sign/magnitude form using U5 and U6. The sign portion is used to drive the DIR input while the magnitude commands the current error amplifier, U8. Current feedback is provided by the internal current sense amplifier via the IOUT pin.

Figure 17. Two-Quadrant Velocity Controller

6-Feb-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish (6) | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|----------------------|---------------------|--------------|----------------------|---------|

| UCC2626DW        | ACTIVE | SOIC         | DW                 | 28   | 20             | Green (RoHS<br>& no Sb/Br) | NIPDAU               | Level-2-260C-1 YEAR | -40 to 85    | UCC2626DW            | Samples |

| UCC2626PW        | ACTIVE | TSSOP        | PW                 | 28   | 50             | Green (RoHS<br>& no Sb/Br) | NIPDAU               | Level-2-260C-1 YEAR | -40 to 85    | UCC2626PW            | Samples |

| UCC2626PWG4      | ACTIVE | TSSOP        | PW                 | 28   | 50             | Green (RoHS<br>& no Sb/Br) | NIPDAU               | Level-2-260C-1 YEAR | -40 to 85    | UCC2626PW            | Samples |

| UCC3626DW        | ACTIVE | SOIC         | DW                 | 28   | 20             | Green (RoHS<br>& no Sb/Br) | NIPDAU               | Level-2-260C-1 YEAR | 0 to 70      | UCC3626DW            | Samples |

| UCC3626DWTR      | ACTIVE | SOIC         | DW                 | 28   | 1000           | Green (RoHS<br>& no Sb/Br) | NIPDAU               | Level-2-260C-1 YEAR | 0 to 70      | UCC3626DW            | Samples |

| UCC3626PW        | ACTIVE | TSSOP        | PW                 | 28   | 50             | Green (RoHS<br>& no Sb/Br) | NIPDAU               | Level-2-260C-1 YEAR | 0 to 70      | UCC3626PW            | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

# **PACKAGE OPTION ADDENDUM**

6-Feb-2020

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 14-Jul-2012

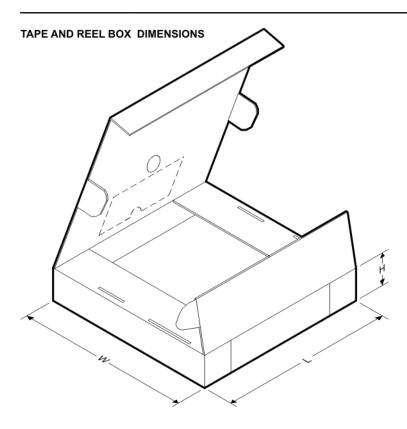

# TAPE AND REEL INFORMATION

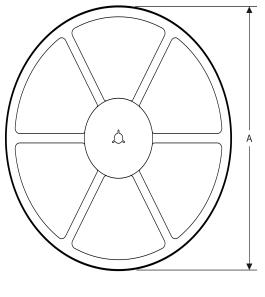

## **REEL DIMENSIONS**

## **TAPE DIMENSIONS**

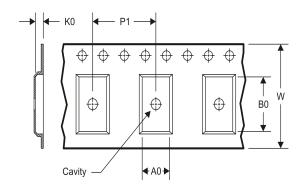

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## TAPE AND REEL INFORMATION

## \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UCC3626DWTR | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 14-Jul-2012

#### \*All dimensions are nominal

|   | Device      | Device Package Type |    | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|-------------|---------------------|----|------|------|-------------|------------|-------------|--|

| I | UCC3626DWTR | SOIC                | DW | 28   | 1000 | 367.0       | 367.0      | 55.0        |  |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated