## **General Description**

The MAX1084/MAX1085 10-bit analog-to-digital converters (ADCs) combine a high-bandwidth track/hold, a serial interface with high conversion speed, an internal +2.5V reference, and low power consumption. The MAX1084 operates from a single +4.5V to +5.5V supply; the MAX1085 operates from a single +2.7V to +3.6V supply.

The 3-wire serial interface connects directly to SPI™/QSPI™/MICROWIRE™ devices without external logic. The devices use an external serial-interface clock to perform successive-approximation analog-to-digital conversions.

Low power combined with ease of use and small package size make these converters ideal for remote-sensor and data-acquisition applications, or for other circuits with demanding power consumption and space requirements. The MAX1084/MAX1085 are available in 8-pin SO packages.

These devices are pin-compatible, higher-speed versions of the MAX1242/MAX1243; for more information, refer to the respective data sheets.

# **Applications**

Portable Data Logging

**Data Acquisition**

Medical Instruments

**Battery-Powered Instruments**

Pen Digitizers

**Process Control**

# \_\_\_\_\_Features

- ♦ Single-Supply Operation +4.5V to +5.5V (MAX1084)

- +2.7V to +3.6V (MAX1085)

- ♦ 10-Bit Resolution

- ♦ 400ksps Sampling Rate (MAX1084)

- ♦ Internal Track/Hold

- ♦ Internal +2.5V Reference

- ♦ Low Power: 2.5mA (400ksps)

- ♦ SPI/QSPI/MICROWIRE 3-Wire Serial Interface

- Pin-Compatible, High-Speed Upgrade to MAX1242/MAX1243

- ♦ 8-Pin SO Package

# **Ordering Information**

| PART         | TEMP<br>RANGE  | PIN-<br>PACKAGE | INL<br>(LSB) |

|--------------|----------------|-----------------|--------------|

| MAX1084ACSA+ | 0°C to +70°C   | 8 SO            | ±1/2         |

| MAX1084BCSA+ | 0°C to +70°C   | 8 SO            | ±1           |

| MAX1084AESA+ | -40°C to +85°C | 8 SO            | ±1/2         |

| MAX1084BESA+ | -40°C to +85°C | 8 SO            | ±1           |

| MAX1085ACSA+ | 0°C to +70°C   | 8 SO            | ±1/2         |

| MAX1085BCSA+ | 0°C to +70°C   | 8 SO            | ±1           |

| MAX1085AESA+ | -40°C to +85°C | 8 SO            | ±1/2         |

| MAX1085BESA+ | -40°C to +85°C | 8 SO            | ±1           |

|              |                |                 |              |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

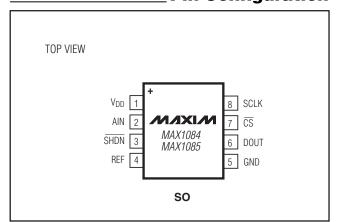

# **Pin Configuration**

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

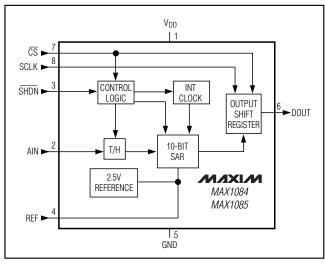

# Functional Diagram

## NIXIN

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND               | 0.3V to +6V                      | Operating Temperature Ranges      |                |

|--------------------------------------|----------------------------------|-----------------------------------|----------------|

| AIN to GND                           | 0.3V to (V <sub>DD</sub> + 0.3V) | MAX1084_CSA/MAX1085_CSA           | 0°C to +70°C   |

| REF to GND                           | 0.3V to (V <sub>DD</sub> + 0.3V) | MAX1084_ESA/MAX1085_ESA           | 40°C to +85°C  |

| Digital Inputs to GND                | 0.3V to +6V                      | Storage Temperature Range         | 60°C to +150°C |

| DOUT to GND                          | 0.3V to (V <sub>DD</sub> + 0.3V) | Lead Temperature (soldering, 10s) | +300°C         |

| DOUT Current                         | ±25mÅ                            | Soldering Temperature (reflow)    | +260°C         |

| Continuous Power Dissipation (TA = + | 70°C)                            |                                   |                |

| 8-Pin SO (derate 5.88mW/°C above     | +70°C) 471mW                     |                                   |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS—MAX1084**

$(V_{DD} = +4.5V \text{ to } +5.5V, f_{SCLK} = 6.4MHz, 50\% \text{ duty cycle}, 16 \text{ clocks/conversion cycle } (400ksps), 4.7 \mu F \text{ capacitor at REF, T}_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                             | SYMBOL     | CONDITIONS                                         | MIN | TYP  | MAX  | UNITS  |

|---------------------------------------|------------|----------------------------------------------------|-----|------|------|--------|

| DC ACCURACY (Note 1)                  |            | 1                                                  |     |      |      |        |

| Resolution                            |            |                                                    | 10  |      |      | Bits   |

| Deletive Assuracy (Nets 2)            | INL        | MAX1084A                                           |     |      | ±0.5 | - LSB  |

| Relative Accuracy (Note 2)            | IINL       | MAX1084B                                           |     |      | ±1.0 | LSB    |

| Differential Nonlinearity             | DNL        | No missing codes over temperature                  |     |      | ±1.0 | LSB    |

| Offset Error                          |            |                                                    |     |      | ±4.0 | LSB    |

| Gain Error (Note 3)                   |            |                                                    |     |      | ±3.0 | LSB    |

| Gain-Error Temperature<br>Coefficient |            |                                                    |     | ±0.8 |      | ppm/°C |

| DYNAMIC SPECIFICATIONS (1             | 00kHz sine | wave, 2.5V <sub>P-P</sub> , clock = 6.4MHz)        | '   |      |      |        |

| Signal-to-Noise Plus Distortion Ratio | SINAD      |                                                    |     | 60   |      | dB     |

| Total Harmonic Distortion             | THD        | Up to the 5th harmonic                             |     | -70  |      | dB     |

| Spurious-Free Dynamic Range           | SFDR       |                                                    |     | 70   |      | dB     |

| Intermodulation Distortion            | IMD        | f <sub>IN1</sub> = 99kHz, f <sub>IN2</sub> =102kHz |     | 76   |      | dB     |

| Full-Power Bandwidth                  |            | -3dB point                                         |     | 6    |      | MHz    |

| Full-Linear Bandwidth                 |            | SINAD > 58dB                                       |     | 350  |      | kHz    |

| CONVERSION RATE                       | -          |                                                    |     |      |      |        |

| Conversion Time (Note 4)              | tconv      |                                                    | 2.5 |      |      | μs     |

| Track/Hold Acquisition Time           | tACQ       |                                                    |     |      | 468  | ns     |

| Aperture Delay                        |            |                                                    |     | 10   |      | ns     |

| Aperture Jitter                       |            |                                                    |     | < 50 |      | ps     |

| Serial Clock Frequency                | fsclk      |                                                    | 0.5 |      | 6.4  | MHz    |

| Duty Cycle                            |            |                                                    | 40  |      | 60   | %      |

| ANALOG INPUT (AIN)                    |            |                                                    |     |      |      |        |

| Input Voltage Range                   | VAIN       |                                                    | 0   |      | 2.5  | V      |

| Input Capacitance                     |            |                                                    |     | 18   |      | pF     |

# **ELECTRICAL CHARACTERISTICS—MAX1084 (continued)**

$(V_{DD} = +4.5V \text{ to } +5.5V, f_{SCLK} = 6.4MHz, 50\% \text{ duty cycle}, 16 \text{ clocks/conversion cycle } (400ksps), 4.7 \mu F \text{ capacitor at REF, T}_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                           | SYMBOL              | CONDITIONS                                | MIN  | TYP  | MAX  | UNITS  |

|-------------------------------------|---------------------|-------------------------------------------|------|------|------|--------|

| INTERNAL REFERENCE                  |                     |                                           | •    |      |      |        |

| REF Output Voltage                  | V <sub>REF</sub>    | T <sub>A</sub> = +25°C                    | 2.48 | 2.50 | 2.52 | V      |

| REF Short-Circuit Current           |                     |                                           |      | 30   |      | mA     |

| REF Output Tempco                   | TC V <sub>REF</sub> |                                           |      | ±15  |      | ppm/°C |

| Load Regulation (Note 5)            |                     | 0 to 1.0mA output load                    |      | 0.1  | 2.0  | mV/mA  |

| Capacitive Bypass at REF            |                     |                                           | 4.7  |      | 10   | μF     |

| <b>DIGITAL INPUTS</b> (SCLK, CS, SF | IDN)                |                                           | •    |      |      |        |

| Input High Voltage                  | VINH                |                                           | 3.0  |      |      | V      |

| Input Low Voltage                   | VINL                |                                           |      |      | 0.8  | V      |

| Input Hysteresis                    | VHYST               |                                           |      | 0.2  |      | V      |

| Input Leakage                       | I <sub>IN</sub>     | V <sub>IN</sub> = 0V or V <sub>DD</sub>   |      |      | ±1   | μΑ     |

| Input Capacitance                   | C <sub>IN</sub>     |                                           |      | 15   |      | pF     |

| DIGITAL OUTPUT (DOUT)               |                     |                                           | •    |      |      |        |

| Output Voltage Low                  | V <sub>OL</sub>     | ISINK = 5mA                               |      |      | 0.4  | V      |

| Output Voltage High                 | V <sub>OH</sub>     | ISOURCE = 1mA                             | 4    |      |      | V      |

| Three-State Leakage Current         | ΙL                  | V <sub>CS</sub> = 5V                      |      |      | ±10  | μΑ     |

| Three-State Output Capacitance      | Cout                | VCS = 5V                                  |      | 15   |      | pF     |

| POWER SUPPLY                        |                     |                                           |      |      |      |        |

| Positive Supply Voltage (Note 6)    | $V_{DD}$            |                                           | 4.5  |      | 5.5  | V      |

| Positive Supply Current (Note 7)    | I <sub>DD</sub>     | $V_{DD} = 5.5V$                           |      | 2.5  | 4.0  | mA     |

| Shutdown Supply Current             | ISHDN               | SCLK = V <sub>DD</sub> , SHDN = GND       |      | 2    | 10   | μA     |

| Power-Supply Rejection              | PSR                 | V <sub>DD</sub> = 5V ±10%, midscale input |      | ±0.5 | ±2.0 | mV     |

## **ELECTRICAL CHARACTERISTICS—MAX1085**

$(V_{DD} = +2.7 V \text{ to } +3.6 V, f_{SCLK} = 4.8 MHz, 50\% \text{ duty cycle}, 16 clocks/conversion cycle (300ksps), 4.7 \mu F capacitor at REF, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C.}$ )

| PARAMETER                             | SYMBOL | CONDITIONS                        | MIN | TYP  | MAX  | UNITS  |

|---------------------------------------|--------|-----------------------------------|-----|------|------|--------|

| DC ACCURACY (Note 1)                  |        |                                   |     |      |      |        |

| Resolution                            |        |                                   | 10  |      |      | Bits   |

| Relative Accuracy (Note 2)            | INL    | MAX1085A                          |     |      | ±0.5 | LSB    |

|                                       | IINL   | MAX1085B                          |     |      | ±1.0 | LOD    |

| Differential Nonlinearity             | DNL    | No missing codes over temperature |     |      | ±1.0 | LSB    |

| Offset Error                          |        |                                   |     |      | ±3.0 | LSB    |

| Gain Error (Note 3)                   |        |                                   |     |      | ±3.0 | LSB    |

| Gain-Error Temperature<br>Coefficient |        |                                   |     | ±1.6 |      | ppm/°C |

# **ELECTRICAL CHARACTERISTICS—MAX1085 (continued)**

$(V_{DD} = +2.7 \text{V to } +3.6 \text{V}, f_{SCLK} = 4.8 \text{MHz}, 50\%$  duty cycle, 16 clocks/conversion cycle (300ksps), 4.7 µF capacitor at REF,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C.}$ )

| PARAMETER                                                      | SYMBOL              | CONDITIONS                                                                       | MIN                   | TYP  | MAX  | UNITS  |

|----------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------|-----------------------|------|------|--------|

| DYNAMIC SPECIFICATIONS (75                                     | 5kHz sinewa         | ave, $2.5\text{Vp-p}$ , $\text{fSAMPLE} = 300\text{ksps}$ , $\text{fSCLK} = 4$ . | 8MHz)                 |      |      |        |

| Signal-to-Noise Plus Distortion Ratio                          | SINAD               |                                                                                  |                       | 60   |      | dB     |

| Total Harmonic Distortion                                      | THD                 | Up to the 5th harmonic                                                           |                       | -70  |      | dB     |

| Spurious-Free Dynamic Range                                    | SFDR                |                                                                                  |                       | 70   |      | dB     |

| Intermodulation Distortion                                     | IMD                 | f <sub>IN1</sub> = 99kHz, f <sub>IN2</sub> =102kHz                               |                       | 76   |      | dB     |

| Full-Power Bandwidth                                           |                     | -3dB point                                                                       |                       | 3    |      | MHz    |

| Full-Linear Bandwidth                                          |                     | SINAD > 58dB                                                                     |                       | 250  |      | kHz    |

| CONVERSION RATE                                                |                     |                                                                                  | -                     |      |      | '      |

| Conversion Time (Note 4)                                       | tCONV               |                                                                                  | 3.3                   |      |      | μs     |

| Track/Hold Acquisition Time                                    | tACQ                |                                                                                  |                       |      | 625  | ns     |

| Aperture Delay                                                 |                     |                                                                                  |                       | 10   |      | ns     |

| Aperture Jitter                                                |                     |                                                                                  |                       | < 50 |      | ps     |

| Serial Clock Frequency                                         | fsclk               |                                                                                  | 0.5                   |      | 4.8  | MHz    |

| Duty Cycle                                                     |                     |                                                                                  | 40                    |      | 60   | %      |

| ANALOG INPUT                                                   |                     |                                                                                  | -                     |      |      | '      |

| Input Voltage Range                                            | VAIN                |                                                                                  | 0                     |      | 2.5  | V      |

| Input Capacitance                                              | CIN                 |                                                                                  |                       | 18   |      | pF     |

| INTERNAL REFERENCE                                             |                     |                                                                                  | -                     |      |      | '      |

| REF Output Voltage                                             | V <sub>REF</sub>    | T <sub>A</sub> = +25°C                                                           | 2.48                  | 2.50 | 2.52 | V      |

| REF Short Circuit Current                                      |                     |                                                                                  |                       | 15   |      | mA     |

| REF Output Tempco                                              | TC V <sub>REF</sub> |                                                                                  |                       | ±15  |      | ppm/°C |

| Load Regulation (Note 5)                                       |                     | 0 to 0.75mA output load                                                          |                       | 0.1  | 2.0  | mV/mA  |

| Capacitive Bypass at REF                                       |                     |                                                                                  | 4.7                   |      | 10   | μF     |

| <b>DIGITAL INPUTS</b> (SCLK, $\overline{CS}$ , $\overline{SH}$ | DN)                 |                                                                                  | -                     |      |      | '      |

| Input High Voltage                                             | VINH                |                                                                                  | 2.0                   |      |      | V      |

| Input Low Voltage                                              | V <sub>INL</sub>    |                                                                                  |                       |      | 0.8  | V      |

| Input Hysteresis                                               | V <sub>HYST</sub>   |                                                                                  |                       | 0.2  |      | V      |

| Input Leakage                                                  | I <sub>IN</sub>     | V <sub>IN</sub> = 0V or V <sub>DD</sub>                                          |                       |      | ±1   | μΑ     |

| Input Capacitance                                              | CIN                 |                                                                                  |                       | 15   |      | pF     |

| <b>DIGITAL OUTPUTS</b> (DOUT)                                  | l                   | 1                                                                                | 1                     |      |      | ,      |

| Output Voltage Low                                             | V <sub>OL</sub>     | ISINK = 5mA                                                                      |                       |      | 0.4  | V      |

| Output Voltage High                                            | Voh                 | ISOURCE = 0.5mA                                                                  | V <sub>DD</sub> - 0.5 | δV   |      | V      |

| Three-State Leakage Current                                    | IL                  | VCS = 3V                                                                         |                       |      | ±10  | μΑ     |

| Three-State Output Capacitance                                 | Cout                | VCS = 3V                                                                         |                       | 15   |      | pF     |

| POWER SUPPLY                                                   |                     |                                                                                  | '                     |      |      |        |

| Positive Supply Voltage (Note 6)                               | V <sub>DD</sub>     |                                                                                  | 2.7                   |      | 3.6  | V      |

| Positive Supply Current (Note 7)                               | I <sub>DD</sub>     | V <sub>DD</sub> = 3.6V                                                           |                       | 2.5  | 3.5  | mA     |

| Shutdown Supply Current                                        | ISHDN               | SCLK = V <sub>DD</sub> , SHDN = GND                                              |                       | 2    | 10   | μΑ     |

| Power-Supply Rejection                                         | PSR                 | V <sub>DD</sub> = 2.7V to 3.6V, midscale input                                   |                       | ±0.5 | ±2.0 | mV     |

4 \_\_\_\_\_\_*N*I/JXI/VI

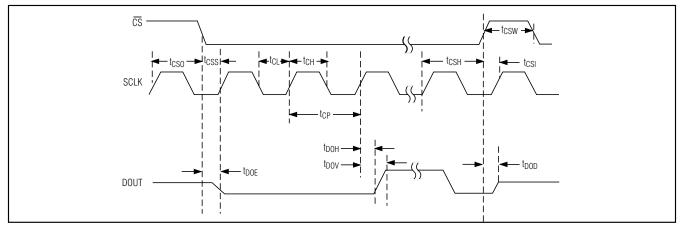

## **TIMING CHARACTERISTICS—MAX1084**

(Figures 1, 2, 8, 9;  $V_{DD}$  = +4.5V to +5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                   | SYMBOL           | CONDITIONS               | MIN | TYP | MAX | UNITS |

|-----------------------------|------------------|--------------------------|-----|-----|-----|-------|

| SCLK Period                 | tcp              |                          | 156 |     |     | ns    |

| SCLK Pulse-Width High       | tCH              |                          | 62  |     |     | ns    |

| SCLK Pulse-Width Low        | tcL              |                          | 62  |     |     | ns    |

| CS Fall to SCLK Rise Setup  | tcss             |                          | 35  |     |     | ns    |

| SCLK Rise to CS Rise Hold   | tcsh             |                          | 0   |     |     | ns    |

| SCLK Rise to CS Fall Ignore | tcso             |                          | 35  |     |     | ns    |

| CS Rise to SCLK Rise Ignore | tcs1             |                          | 35  |     |     | ns    |

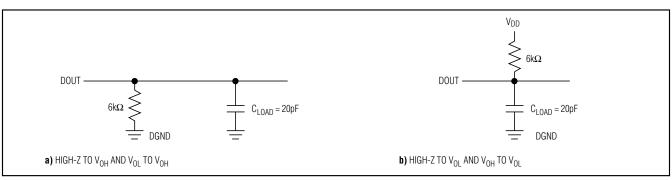

| SCLK Rise to DOUT Hold      | t <sub>DOH</sub> | C <sub>LOAD</sub> = 20pF | 10  |     |     | ns    |

| SCLK Rise to DOUT Valid     | tDOV             | C <sub>LOAD</sub> = 20pF |     |     | 80  | ns    |

| CS Rise to DOUT Disable     | tDOD             | C <sub>LOAD</sub> = 20pF | 10  |     | 65  | ns    |

| CS Fall to DOUT Enable      | tDOE             | C <sub>LOAD</sub> = 20pF |     |     | 65  | ns    |

| CS Pulse-Width High         | tcsw             |                          | 100 |     |     | ns    |

## TIMING CHARACTERISTICS—MAX1085

(Figures 1, 2, 8, 9;  $V_{DD}$  = +2.7V to +3.6V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                   | SYMBOL           | CONDITIONS               | MIN | TYP | MAX | UNITS |

|-----------------------------|------------------|--------------------------|-----|-----|-----|-------|

| SCLK Period                 | t <sub>CP</sub>  |                          | 208 |     |     | ns    |

| SCLK Pulse-Width High       | tcH              |                          | 83  |     |     | ns    |

| SCLK Pulse-Width Low        | t <sub>CL</sub>  |                          | 83  |     |     | ns    |

| CS Fall to SCLK Rise Setup  | tcss             |                          | 45  |     |     | ns    |

| SCLK Rise to CS Rise Hold   | tcsh             |                          | 0   |     |     | ns    |

| SCLK Rise to CS Fall Ignore | tcso             |                          | 45  |     |     | ns    |

| CS Rise to SCLK Rise Ignore | t <sub>CS1</sub> |                          | 45  |     |     | ns    |

| SCLK Rise to DOUT Hold      | tDOH             | C <sub>LOAD</sub> = 20pF | 13  |     |     | ns    |

| SCLK Rise to DOUT Valid     | tDOV             | C <sub>LOAD</sub> = 20pF |     |     | 100 | ns    |

| CS Rise to DOUT Disable     | tDOD             | $C_{LOAD} = 20pF$        | 13  |     | 85  | ns    |

| CS Fall to DOUT Enable      | tDOE             | C <sub>LOAD</sub> = 20pF |     |     | 85  | ns    |

| CS Pulse-Width High         | tcsw             | C <sub>LOAD</sub> = 20pF | 100 |     |     | ns    |

- **Note 1:** Tested at  $V_{DD} = V_{DD,MIN}$ .

- **Note 2:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated.

- Note 3: Internal reference, offset, and reference errors nulled.

- Note 4: Conversion time is defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle.

- Note 5: External load should not change during conversion for specified accuracy. Guaranteed specification limit of 2mV/mA due to production test limitation.

- **Note 6:** Electrical characteristics are guaranteed from V<sub>DD,MIN</sub> to V<sub>DD,MAX</sub>. For operations beyond this range, see *Typical Operating Characteristics*.

- Note 7: MAX1084 tested with 20pF on DOUT and  $f_{SCLK} = 6.4$ MHz, 0 to 5V. MAX1085 tested with same loads,  $f_{SCLK} = 4.8$ MHz, 0 to 3V. DOUT = full scale.

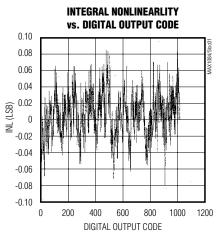

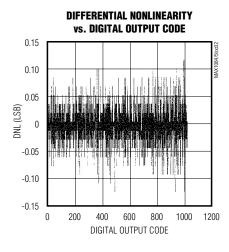

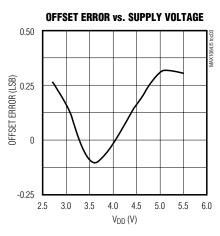

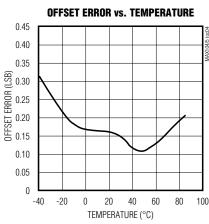

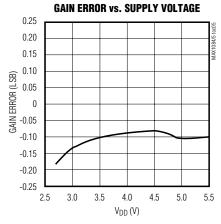

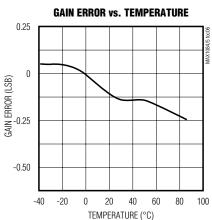

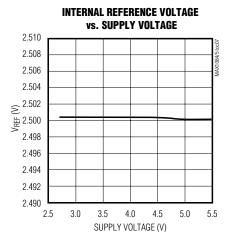

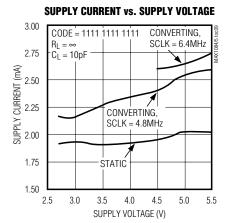

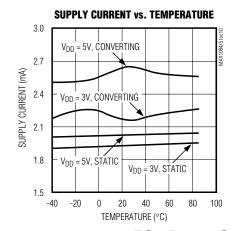

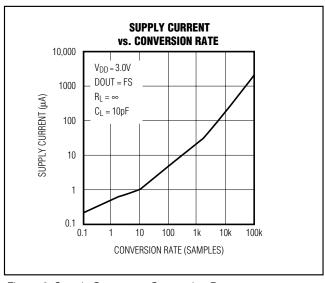

# **Typical Operating Characteristics**

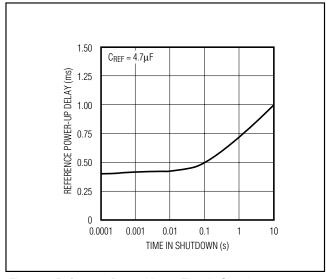

(MAX1084:  $V_{DD}$  = +5.0V,  $f_{SCLK}$  = 6.4MHz; MAX1055:  $V_{DD}$  = +3.0V,  $f_{SCLK}$  = 4.8MHz;  $C_{LOAD}$  = 20pF, 4.7 $\mu$ F capacitor at REF,  $T_A$  = +25°C, unless otherwise noted.)

# Typical Operating Characteristics (continued)

(MAX1084:  $V_{DD}$  = +5.0V,  $f_{SCLK}$  = 6.4MHz; MAX1085:  $V_{DD}$  = +3.0V,  $f_{SCLK}$  = 4.8MHz;  $C_{LOAD}$  = 20pF, 4.7 $\mu$ F capacitor at REF,  $T_A$  = +25°C, unless otherwise noted.)

#### INTERNAL REFERENCE VOLTAGE vs. TEMPERATURE 2.510 2.508 2.506 2.504 €<sup>2.502</sup> 上 2.500 2.498 2.496 2.494 2.492 2 490 -40 -20 80 0 20 40 TEMPERATURE (°C)

# Pin Description

| PIN | NAME     | FUNCTION                                                                                                                        |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------|

| 1   | $V_{DD}$ | Positive Supply Voltage                                                                                                         |

| 2   | AIN      | Sampling Analog Input, 0 to V <sub>REF</sub> Range                                                                              |

| 3   | SHDN     | Active-Low Shutdown Input. Pulling SHDN low shuts down the device and reduces the supply current to 2μA (typ).                  |

| 4   | REF      | Reference Voltage for Analog-to-Digital Conversion. Internal 2.5V reference output. Bypass with a 4.7µF capacitor.              |

| 5   | GND      | Analog and Digital Ground                                                                                                       |

| 6   | DOUT     | Serial-Data Output. DOUT changes state at SCLK's rising edge. High impedance when $\overline{\text{CS}}$ is high.               |

| 7   | CS       | Active-Low Chip Select. Initiates conversions on the falling edge. When $\overline{\text{CS}}$ is high, DOUT is high impedance. |

| 8   | SCLK     | Serial-Clock Input. SCLK drives the conversion process and clocks data out at rates up to 6.4MHz (MAX1084) or 4.8MHz (MAX1085). |

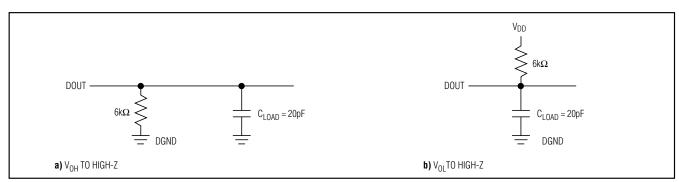

Figure 1. Load Circuits for DOUT Enable Time

Figure 2. Load Circuits for DOUT Disable Time

# **Detailed Description**

### **Converter Operation**

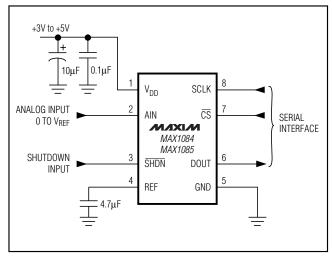

The MAX1084/MAX1085 use an input track/hold (T/H) and successive-approximation register (SAR) circuitry to convert an analog input signal to a digital 10-bit output. Figure 3 shows the MAX1084/MAX1085 in their simplest configuration. The internal reference is trimmed to 2.5V. The serial interface requires only three digital lines (SCLK,  $\overline{CS}$ , and DOUT) and provides an easy interface to microprocessors (µPs).

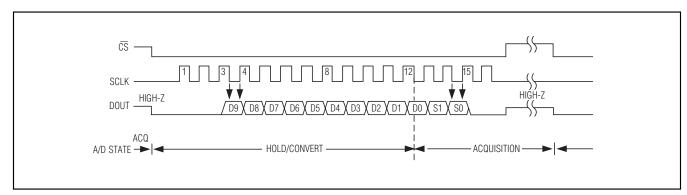

The MAX1084/MAX1085 have two modes: normal and shutdown. Pulling  $\overline{SHDN}$  low shuts the device down and reduces supply current to  $2\mu A$  (typ); pulling  $\overline{SHDN}$  high puts the device into operational mode. Pulling  $\overline{CS}$  low initiates a conversion that is driven by SCLK. The conversion result is available at DOUT in unipolar serial format. The serial data stream consists of three zeros, followed by the data bits (MSB first). All transitions on DOUT occur 20ns after the rising edge of SCLK. Figures 8 and 9 show the interface timing information.

### Analog Input

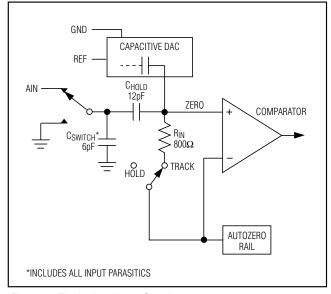

Figure 4 shows the sampling architecture of the ADC's comparator. The full-scale input voltage is set by the internal reference ( $V_{REF} = +2.5V$ ).

### Track/Hold

In track mode, the analog signal is acquired and stored in the internal hold capacitor. In hold mode, the T/H switch opens and maintains a constant input to the ADC's SAR section.

During acquisition, the analog input AIN charges capacitor  $C_{HOLD}$ . Bringing  $\overline{CS}$  low ends the acquisition interval. At this instant, the T/H switches the input side of  $C_{HOLD}$  to GND. The retained charge on  $C_{HOLD}$  represents a sample of the input, unbalancing node ZERO at the comparator's input.

In hold mode, the capacitive digital-to-analog converter (DAC) adjusts during the remainder of the conversion cycle to restore node ZERO to 0 within the limits of 10-bit resolution. This action is equivalent to transferring a charge from  $C_{\mbox{\scriptsize HOLD}}$  to the binary-weighted capacitive

MIXIM

DAC, which in turn forms a digital representation of the analog input signal. At the conversion's end, the input side of  $C_{\mbox{\scriptsize HOLD}}$  switches back to AIN, and  $C_{\mbox{\scriptsize HOLD}}$  charges to the input signal again.

The time required for the T/H to acquire an input signal is a function of how quickly its input capacitance is charged. If the input signal's source impedance is high, the acquisition time lengthens, and more time must be allowed between conversions. The acquisition time, tACQ, is the maximum time the device takes to acquire the signal and the minimum time needed for the signal to be acquired. Acquisition time is calculated by:

$$t_{ACQ} = 7(R_S + R_{IN}) \times 12pF$$

where  $R_{IN}=800\Omega,~R_S=$  the input signal's source impedance, and  $t_{ACQ}$  is never less than 468ns (MAX1284) or 625ns (MAX1085). Source impedance below  $4k\Omega$  does not significantly affect the ADC's AC performance.

Higher source impedances can be used if a 0.01µF capacitor is connected to the analog input. Note that the input capacitor forms an RC filter with the input source impedance, limiting the ADC's input signal bandwidth.

### Input Bandwidth

The ADC's input tracking circuitry has a 6MHz (MAX1084) or 3MHz (MAX1085) small-signal bandwidth, so it is possible to digitize high-speed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. To avoid aliasing of unwanted high-frequency signals into the frequency band of interest, anti-alias filtering is recommended.

### Analog Input Protection

Internal protection diodes, which clamp the analog input to  $V_{DD}$  and GND, allow the input to swing from (GND - 0.3V) to ( $V_{DD}$  + 0.3V) without damage.

If the analog input exceeds 50mV beyond the supplies, limit the input current to 2mA.

## Internal Reference

The MAX1084/MAX1085 have an on-chip voltage reference trimmed to 2.5V. The internal reference output is connected to REF and also drives the internal capacitive DAC. The output can be used as a reference voltage source for other components and can source up to  $800\mu A$ . Bypass REF with a  $4.7\mu F$  capacitor. Larger capacitors increase wake-up time when exiting shutdown (see *Using SHDN* to *Reduce Supply Current*). The internal reference is disabled in shutdown (SHDN = 0).

Figure 3. Typical Operating Circuit

Figure 4. Equivalent Input Circuit

### Serial Interface

# Initialization After Power-Up and Starting a Conversion

When power is first applied, and if SHDN is not pulled low, it takes the fully discharged 4.7µF reference bypass capacitor up to 1.4ms to acquire adequate charge for specified accuracy. No conversions should be performed during this time.

To start a conversion, pull  $\overline{\text{CS}}$  low. At  $\overline{\text{CS}}$ 's falling edge, the T/H enters its hold mode and a conversion is initiated. Data can then be shifted out serially with the external clock.

## **Using SHDN** to Reduce Supply Current

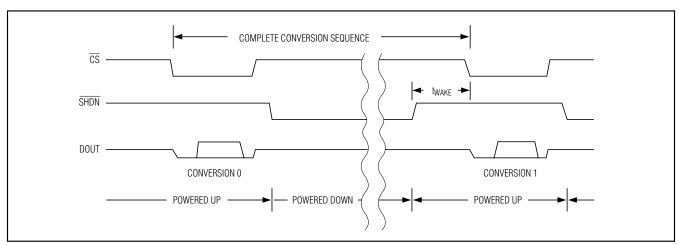

Power consumption can be reduced significantly by shutting down the MAX1084/MAX1085 between conversions. Figure 6 shows a plot of average supply current vs. conversion rate. The wake-up time, twake, is the time from SHDN deasserted to the time when a conversion may be initiated (Figure 5). This time depends on the time in shutdown (Figure 7) because the external 4.7µF reference bypass capacitor loses charge slowly during shutdown and can be as long as 1.4ms.

## **Timing and Control**

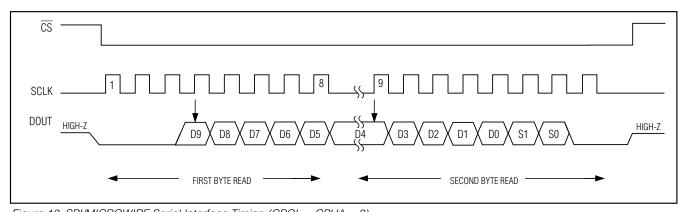

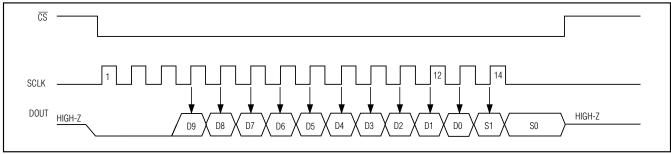

Conversion-start and data-read operations are controlled by the  $\overline{\text{CS}}$  and SCLK digital inputs. The timing diagrams of Figures 8 and 9 outline serial-interface operation.

A  $\overline{\text{CS}}$  falling edge initiates a conversion sequence: the T/H stage holds the input voltage, the ADC begins to convert, and DOUT changes from high impedance to logic low. SCLK is used to drive the conversion process, and it shifts data out as each bit of conversion is determined.

SCLK begins shifting out the data after the rising edge of the third SCLK pulse. DOUT transitions 20ns after each SCLK rising edge. The third rising clock edge produces the MSB of the conversion at DOUT, followed by the remaining bits. Since there are 12 data bits and 3 leading zeros, at least 15 rising clock edges are

needed to shift out these bits. Extra clock pulses occurring after the conversion result has been clocked out, and prior to a rising edge of  $\overline{\text{CS}}$ , produce trailing zeros at DOUT and have no effect on converter operation.

Pull  $\overline{CS}$  high after reading the conversion's LSB. For maximum throughput,  $\overline{CS}$  can be pulled low again to initiate the next conversion immediately after the specified minimum time (t<sub>CS</sub>).

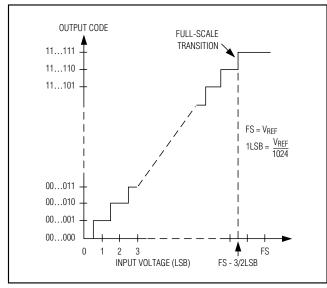

## **Output Coding and Transfer Function**

The data output from the MAX1084/MAX1085 is binary. Figure 10 depicts the nominal transfer function. Code transitions occur halfway between successive-integer LSB values; VREF = 2.5V, and 1LSB = 2.44mV or 2.5V/1024.

# Applications Information

### **Connection to Standard Interfaces**

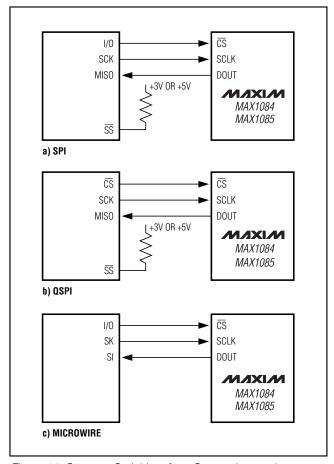

The MAX1084/MAX1085 serial interface is fully compatible with SPI, QSPI, and MICROWIRE (Figure 11).

If a serial interface is available, set the CPU's serial interface in master mode so the CPU generates the serial clock. Choose a clock frequency up to 6.4MHz (MAX1084) or 4.8MHz (MAX1085).

- 1) Use a general-purpose I/O line on the CPU to pull  $\overline{\text{CS}}$  low. Keep SCLK low.

- 2) Activate SCLK for a minimum of 13 clock cycles. The first two clocks produce zeros at DOUT. DOUT output data transitions 20ns after SCLK rising edge and is available in MSB-first format. Observe the SCLK-to-DOUT valid timing characteristic. Data can be clocked into the µP on SCLK's falling or rising edge.

Figure 5. Shutdown Sequence

Figure 6. Supply Current vs. Conversion Rate

Figure 7. Reference Power-Up vs. Time in Shutdown

Figure 8. Interface Timing Sequence

Figure 9. Detailed Serial-Interface Timing

Figure 10. Unipolar Transfer Function, Full Scale (FS) = V<sub>REF</sub>, Zero Scale (ZS) = GND

- 3) Pull  $\overline{\text{CS}}$  high at or after the 13th rising clock edge. If  $\overline{\text{CS}}$  remains low, the two sub-bits and trailing zeros are clocked out after the LSB.

- 4) With  $\overline{\text{CS}}$  = high, wait the minimum specified time, t<sub>CS</sub>, before initiating a new conversion by pulling  $\overline{\text{CS}}$  low. If a conversion is aborted by pulling  $\overline{\text{CS}}$  high before the conversion completes, wait the minimum acquisition time, t<sub>ACQ</sub>, before starting a new conversion.  $\overline{\text{CS}}$  must be held low until all data bits are clocked out.

Data can be output in 2 bytes or continuously, as shown in Figure 8. The bytes contain the result of the conversion padded with three leading zeros, 2 sub-bits, and trailing zeros if SCLK is still active with  $\overline{\text{CS}}$  kept low.

#### **SPI** and Microwire

When using SPI or QSPI, set CPOL = 0 and CPHA = 0. Conversion begins with a  $\overline{CS}$  falling edge. DOUT goes low, indicating a conversion is in progress. Two consecutive 1-byte reads are required to get the full 10+2 bits from the ADC. DOUT output data transitions on SCLK's rising edge and is clocked into the  $\mu P$  on the following rising edge.

The first byte contains 3 leading zeros, and 5 bits of conversion result. The second byte contains the remaining 5 bits, 2 sub-bits, and 1 trailing zero. See Figure 11 for connections and Figure 12 for timing.

Figure 11. Common Serial-Interface Connections to the MAX1084/MAX1085

## QSPI

Unlike SPI, which requires two 1-byte reads to acquire the 10 bits of data from the ADC, QSPI allows the minimum number of clock cycles necessary to clock in the data. The MAX1084/MAX1085 require 13 clock cycles from the  $\mu P$  to clock out the 10 bits of data. Additional clock cycles clock out the 2 sub-bits followed by trailing zeros. Figure 13 shows a transfer using CPOL = 0 and CPHA = 1. The result of conversion contains two zeros followed by the 10 bits of data in MSB-first format.

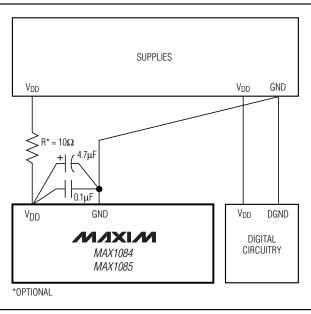

### Layout and Grounding

For best performance, use PC boards. Wire-wrap boards are not recommended. Board layout should ensure that digital and analog signal lines are separated from each other. Do not run analog and digital (especially clock) lines parallel to one another, or digital lines underneath the ADC package.

Figure 14 shows the recommended system ground connections. Establish a single-point analog ground ("star" ground point) at GND, separate from the logic ground. Connect all other analog grounds and GND to this star ground point for further noise reduction. No other digital system ground should be connected to this single-point analog ground. The ground return to the power supply for this ground should be low impedance and as short as possible for noise-free operation.

High-frequency noise in the  $V_{DD}$  power supply may affect the ADC's high-speed comparator. Bypass this supply to the single-point analog ground with  $0.1\mu F$  and  $10\mu F$  bypass capacitors. Minimize capacitor lead lengths for best supply-noise rejection. To reduce the effect of supply noise, a  $10\Omega$  resistor can be connected as a lowpass filter to attenuate supply noise (Figure 14).

### **Definitions**

## Integral Nonlinearity

Integral nonlinearity (INL) is the deviation of the values on an actual transfer function from a straight line. This straight line can be either a best-straight-line fit or a line drawn between the endpoints of the transfer function, once offset and gain errors have been nullified. The static linearity parameters for the MAX1084/MAX1085 are measured using the endpoints method.

### Differential Nonlinearity

Differential nonlinearity (DNL) is the difference between an actual step width and the ideal value of 1LSB. A DNL error specification of 1LSB or less guarantees no missing codes and a monotonic transfer function.

## **Aperture Jitter**

Aperture jitter (t<sub>AJ</sub>) is the sample-to-sample variation in the time between the samples.

### **Aperture Delay**

Aperture delay (t<sub>AD</sub>) is the time defined between the falling edge of CS and the instant when an actual sample is taken.

## Signal-to-Noise Ratio

For a waveform perfectly reconstructed from digital samples, signal-to-noise ratio (SNR) is the ratio of full-scale analog input (RMS value) to the RMS quantization error (residual error). The theoretical minimum analog-to-digital noise is caused by quantization error and results directly from the ADC's resolution, (N bits):

Figure 12. SPI/MICROWIRE Serial Interface Timing (CPOL = CPHA = 0)

Figure 13. QSPI Serial Interface Timing (CPOL = 0, CPHA = 1)

Figure 14. Power-Supply Grounding Condition

$$SNR = (6.02 \times N + 1.76)dB$$

In reality, there are other noise sources besides quantization noise, including thermal noise, reference noise, clock jitter, etc. Therefore, SNR is computed by taking the ratio of the RMS signal to the RMS noise, which includes all spectral components minus the fundamental, the first five harmonics, and the DC offset.

### **Signal-to-Noise Plus Distortion**

Signal-to-noise plus distortion (SINAD) is the ratio of the fundamental input frequency's RMS amplitude to RMS equivalent of all other ADC output signals.

$SINAD (dB) = 20 \times log (SignalRMS/NoiseRMS)$

### **Effective Number of Bits**

Effective number of bits (ENOB) indicates the global accuracy of an ADC at a specific input frequency and sampling rate. An ideal ADC's error consists of quantization noise only. With an input range equal to the full-scale range of the ADC, calculate the effective number of bits as follows:

$$ENOB = (SINAD - 1.76)/6.02$$

### **Total Harmonic Distortion**

Total harmonic distortion (THD) is the ratio of the RMS sum of the first five harmonics of the input signal to the fundamental itself. This is expressed as:

THD =

$$20 \times LOG \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2}}{V_4}$$

where V1 is the fundamental amplitude, and V2 through V5 are the amplitudes of the 2nd- through 5th-order harmonics, respectively.

## **Spurious-Free Dynamic Range**

Spurious-free dynamic range (SFDR) is the ratio of RMS amplitude of the fundamental (maximum signal component) to the RMS value of the next-largest distortion component.

\_\_\_\_\_Chip Information

PROCESS: BICMOS

# Package Information

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/package">www.maxim-ic.com/package</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO. | LAND PATTERN NO. |

|--------------|--------------|-------------|------------------|

| 8 SO         | S8+5         | 21-0041     | 90-0096          |

# **Revision History**

| 1 | VISION<br>JMBER | REVISION<br>DATE | DESCRIPTION                                                                     |                          |

|---|-----------------|------------------|---------------------------------------------------------------------------------|--------------------------|

|   | 0               | 5/00             | Initial release                                                                 | _                        |

|   | 1               | 12/10            | Add lead-free, update Absolute Maximum Ratings, update Figure 10, style updates | 1–5, 7–12,<br>14, 15, 16 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Maxim Integrated:

<u>MAX1084BESA+</u> <u>MAX1085BESA+</u> <u>MAX1084ACSA+</u> <u>MAX1084ACSA+T</u> <u>MAX1084AESA+</u> <u>MAX1084AESA+T</u> <u>MAX1084BCSA+</u> <u>MAX1084BCSA+T</u> <u>MAX1085ACSA+</u> <u>MAX1085ACSA+T</u> <u>MAX1085BCSA+T</u> <u>MAX1085BCSA+T</u> <u>MAX1085BCSA+T</u> <u>MAX1085BCSA+T</u> <u>MAX1085BCSA+T</u>