### ISL8120

Dual/n-Phase Buck PWM Controller with Integrated Drivers

FN6641 Rev.3.00 July 20, 2016

The ISL8120 integrates two voltage-mode PWM leading-edge modulation control, with input feed-forward synchronous buck PWM controllers, to control a dual independent voltage regulator or a 2-phase single output regulator. It also integrates current sharing control for the power module to operate in parallel, which offers high system flexibility.

The ISL8120 integrates an internal linear regulator, which generates VCC from input rail for applications with only one single supply rail. The internal oscillator is adjustable from 150kHz to 1.5MHz, and is able to synchronize to an external clock signal for frequency synchronization and phase paralleling applications. Its PLL circuit can output a phase-shift programmable clock signal for the system to be expanded to 3-, 4-, 6-, 12- phases with desired interleaving phase shift.

The ISL8120's Fault Hand Shake feature protects any channel from overloading/stressing due to system faults or phase failure. The undervoltage fault protection features are also designed to prevent a negative transient on the output voltage during falling down. This eliminates the Schottky diode that is used in some systems for protecting the load device from reversed output voltage damage.

#### **Related Literature**

- Technical Brief <u>TB389</u> "PCB Land Pattern Design and Surface Mount Guidelines for QFN (MLFP) Packages"

- AN1528, "ISL8120EVAL3Z Evaluation Board Setup Procedure"

- AN1607, "ISL8120EVAL4Z Evaluation Board Setup Procedure"

### **Features**

- Wide V<sub>IN</sub> range operation: 3V to 22V

- V<sub>CC</sub> operation from 3V to 5.60V

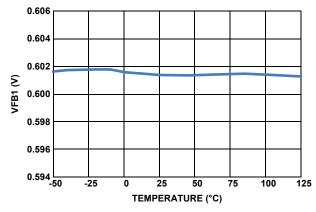

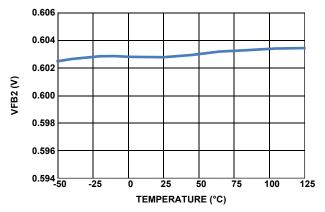

- Excellent output voltage regulation: 0.6V ±0.6%/±0.9% internal reference over commercial/industrial temperature

- · Frequency synchronization

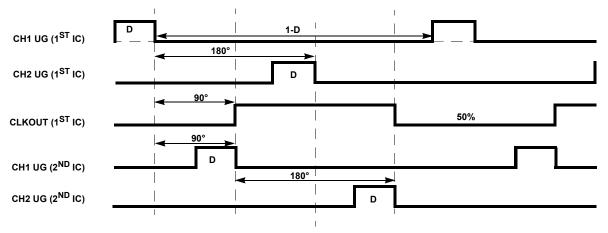

- Programmable phase shift for 1-, 2-, 3-, 4-, 6-, up to 12-phase applications

- Fault hand shake capability for high system reliability

- · Digital soft-start with precharged output start-up capability

- Dual independent channel enable inputs with precision voltage monitor and voltage feed-forward capability

- Programmable input voltage POR and its hysteresis with a resistor divider at EN input

- Extensive circuit protection functions: output overvoltage, undervoltage, overcurrent protection, over temperature and pre-power-on reset overvoltage protection option

### **Applications**

- Power supply for datacom/telecom and POL

- · Paralleling power module

- · Wide and narrow input voltage range buck regulators

- · DDR I and II applications

- · High current density power supplies

- Multiple outputs VRM and VRD

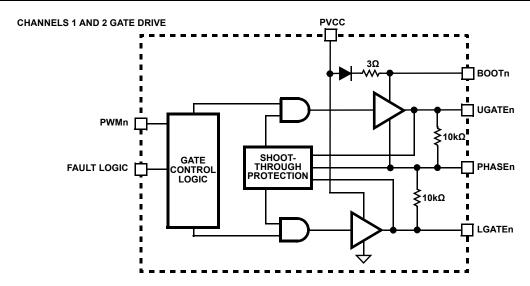

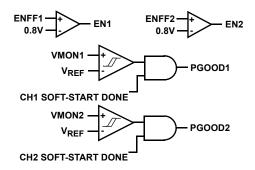

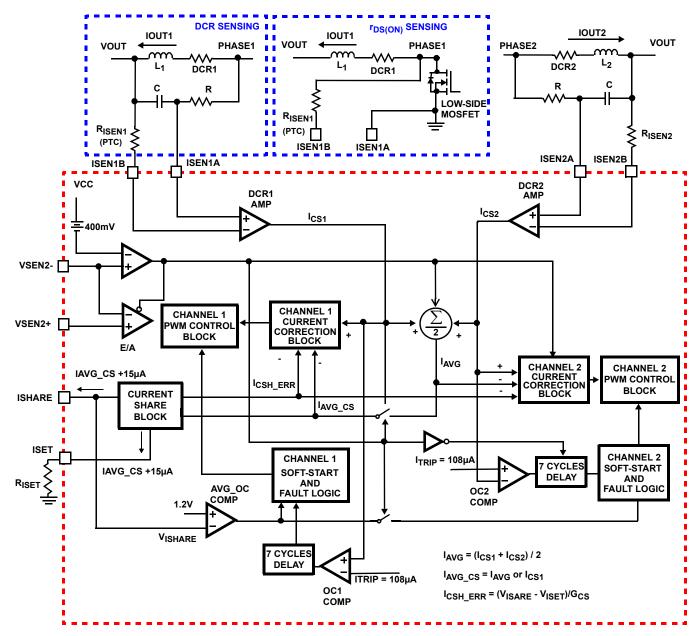

FIGURE 1. INTEGRATED DRIVER BLOCK DIAGRAM

# **Table of Contents**

| Pin Configuration                                               | . 3 |

|-----------------------------------------------------------------|-----|

| Functional Pin Descriptions                                     | . 3 |

| Ordering Information                                            | . 5 |

| Controller Block Diagram                                        | . 6 |

| Typical Application Circuits                                    |     |

| 2-Phase Operation with DCR Sensing.                             |     |

| 2-Phase Operation with r <sub>DS(ON)</sub> Sensing              | 8   |

| Dual Regulators with DCR Sensing and Remote Sense               | 9   |

| Double Data Rate I or II                                        |     |

| 3-Phase Regulator with Precision Resistor Sensing               | 11  |

| 4-Phase Operation with DCR Sensing                              |     |

| Multiple Power Modules in Parallel with Current Sharing Control |     |

| 3-Phase Regulator with Resistor Sensing and 1 Phase Regulator   |     |

| 6-Phase Operation with DCR Sensing                              |     |

| Absolute Maximum Ratings                                        | 16  |

| Thermal Information                                             | 16  |

| Recommended Operating Conditions                                | 16  |

| Electrical Specifications                                       |     |

| •                                                               |     |

| Typical Performance Curves                                      |     |

| Modes of Operation                                              | 21  |

| Functional Description                                          | 23  |

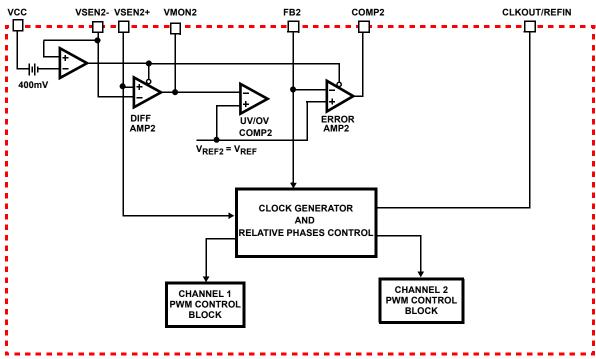

| Initialization                                                  | 24  |

| Voltage Feed-Forward                                            |     |

| Soft-Start                                                      |     |

| Power-Good                                                      |     |

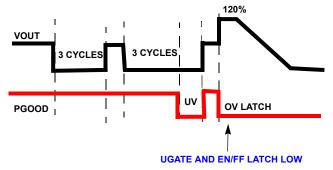

| Overvoltage and Undervoltage Protection                         | 25  |

| PRE-POR Overvoltage Protection (PRE-POR-OVP)                    | 26  |

| Over-Temperature Protection (OTP)                               |     |

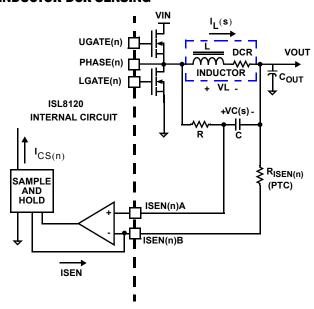

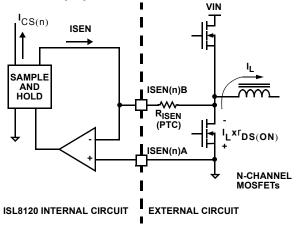

| Inductor Current Sensing                                        |     |

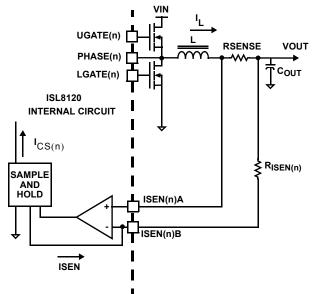

| Resistive Sensing                                               |     |

| Current Sharing Loop                                            |     |

| Internal Series Linear and Power Dissipation                    |     |

| Oscillator                                                      |     |

| Frequency Synchronization and Phase Lock Loop                   |     |

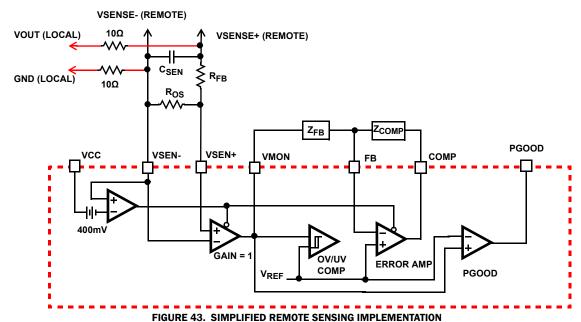

| Differential Amplifier for Remote Sense                         |     |

| Internal Reference and System Accuracy                          |     |

| DDR and Dual Mode Operation                                     |     |

| Layout Considerations                                           |     |

| Revision History                                                | 38  |

| About Intersil                                                  | 38  |

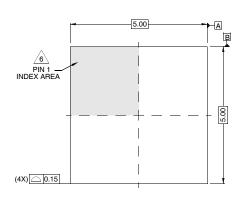

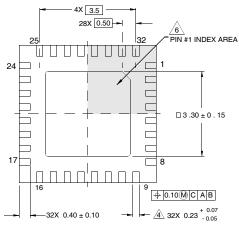

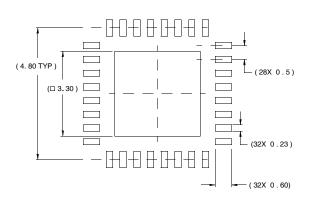

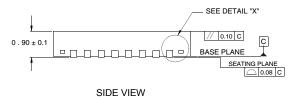

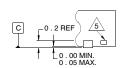

| Package Outline Drawing                                         | 39  |

|                                                                 |     |

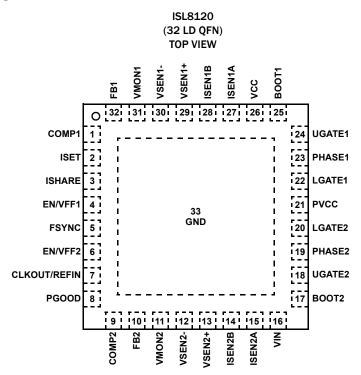

# **Pin Configuration**

## **Functional Pin Descriptions**

| PIN    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | SYMBOL  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1      | COMP1   | These pins are the error amplifier outputs. They should be connected to FB1, FB2 pins through desired compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9      | COMP2   | networks when both channels are operating independently. When VSEN1-, VSEN2- are pulled within 400mV of VCC, the corresponding error amplifier is disabled and its output (COMP pin) is high impedance. Thus, in multiphase operations, all other SLAVE phases' COMP pins can tie to the MASTER phase's COMP1 pin (1st phase), which modulates each phase's PWM pulse with a single voltage feedback loop. While the error amplifier is not disabled, an independent compensation network is required for each cascaded IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2      | ISET    | This pin sources a 15µA offset current plus the average current of both channels in multiphase mode or only Channel 1's current in independent mode. The voltage (VISET) set by an external resistor (RISET) represents the average current level of the local active channel(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3      | ISHARE  | This pin is used for current sharing purposes and is configured to current share bus representing all modules' average current. It sources 15 $\mu$ A offset current plus the average current of both channels in multiphase mode or Channel 1's current in independent mode. The share bus (ISHARE pins connected together) voltage (VISHARE) set by an external resistor (RISHARE) represents the average current level of all ISL8120 controller connected to current share bus. The ISHARE bus voltage compares with ISET voltage to generates current share error signal for current correction block of each cascaded controller. The share bus impedance RISHARE should be set as RISET/NCTRL (RISET divided by number of ISL8120 in current sharing controllers). There is a 1.2V threshold for average overcurrent protection on this pin. VISHARE is compared with a 1.2V threshold for average overcurrent protections. For full-scale current, RISHARE should be 1.2V/123 $\mu$ A = ~10k $\Omega$ . Typically 10k $\Omega$ is used for RSHARE and RSET. |

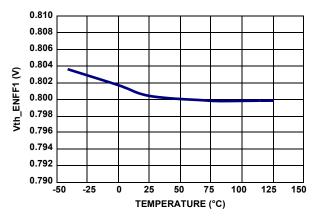

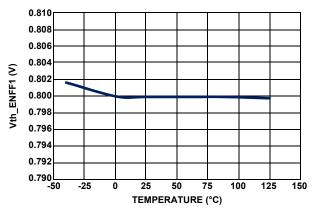

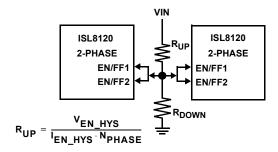

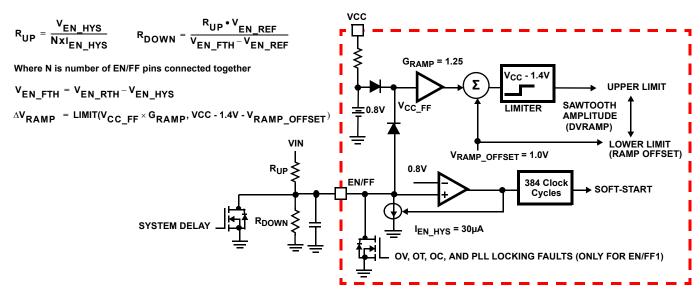

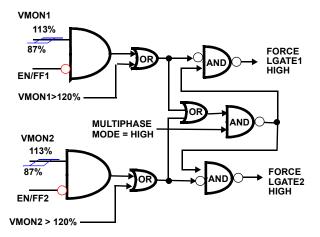

| 4      | EN/VFF1 | These pins have triple functions. The voltage on EN/FF_ pin is compared with a precision 0.8V threshold for system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6      | EN/VFF2 | enable to initiate soft-start. With a voltage lower than the threshold, the corresponding channel can be disabled independently. By connecting these pins to the input rail through a voltage resistor divider, the input voltage can be monitored for UVLO (Undervoltage Lockout) function. The undervoltage lockout and its hysteresis levels can be programmed by these resistor dividers. The voltages on these pins are also fed into the controller to adjust the sawtooth amplitude of each channel independently to realize the feed-forward function.  Furthermore, during fault (such as overvoltage, overcurrent, and over-temperature) conditions, these pins are pulled low to communicate the information to other cascaded ICs.                                                                                                                                                                                                                                                                                                                      |

# Functional Pin Descriptions (Continued)

| PIN<br>NUMBER | SYMBOL       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

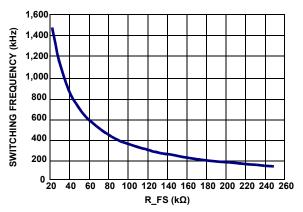

| 5             | FSYNC        | The oscillator switching frequency is adjusted by placing a resistor (RFS) from this pin to GND. The internal oscillator will lock to an external frequency source if this pin is connected to a switching square pulse waveform, typically the CLKOUT input signal from another ISL8120 or an external clock. The internal oscillator synchronizes with the leading edge of the input signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

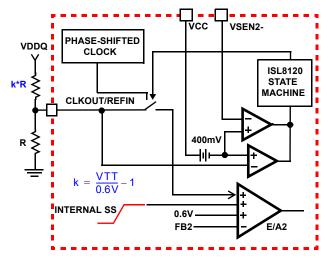

| 7             | CLKOUT/REFIN | This pin has a dual function depending on the mode in which the chip is operating. It provides a clock signal to synchronize with other ISL8120(s) with its VSEN2- pulled within 400mV of VCC for multiphase (3-, 4-, 6-, 8-, 10-, or 12-phase) operation. When the VSEN2- pin is not within 400mV of VCC, ISL8120 is in dual mode (dual independent PWM output). The clockout signal of this pin is not available in this mode, however, the ISL8120 can be synchronized to external clock. In dual mode, this pin works as the following two functions:  1. An external reference (0.6V target only) can be in place of the Channel 2's internal reference through this pin for DDR/tracking applications (see "DDR and Dual Mode Operation" on page 35).  2. The ISL8120 operates as a dual-PWM controller for two independent regulators with selectable phase degree shift,                                                                                                                                                                                                                                                                                                                                                                                                                       |

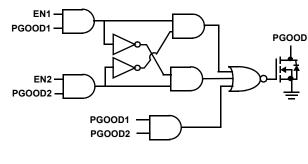

| 8             | PGOOD        | which is programmed by the voltage level on REFIN (see "DDR and Dual Mode Operation" on page 35).  Provides an open drain power-good signal when both channels are within 9% of the nominal output regulation point with 4% hysteresis (13%/9%) and soft-start complete. PGOOD monitors the outputs (VMON1/2) of the internal differential amplifiers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 32            | FB1          | These pins are the inverting inputs of the error amplifiers. These pins should be connected to VMON1, VMON2 with the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10            | FB2          | compensation feedback network. No direct connection between FB and VMON pins is allowed. With VSEN2- pulled within 400mV of VCC, the corresponding error amplifier is disabled and the amplifier's output is high impedance. FB2 is one of the two pins to determine the relative phase relationship between the internal clock of both channels and the CLKOUT signal. See Table 1 on page 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 31            | VMON1        | These pins are outputs of the unity gain amplifiers. They are connected internally to the OV/UV/PGOOD comparators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11            | VMON2        | These pins should be connected to the FB1, FB2 pins by a standard feedback network when both channels are operating independently. When VSEN1-, VSEN2- are pulled within 400mV of VCC, the corresponding differential amplifier is disabled and its output (VMON pin) is high impedance. In such an event, the VMON pin can be used as an additional monitor of the output voltage with a resistor divider to protect the system against single point of failure, which occurs in the system using the same resistor divider for both of the UV/OV comparator and output voltage feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

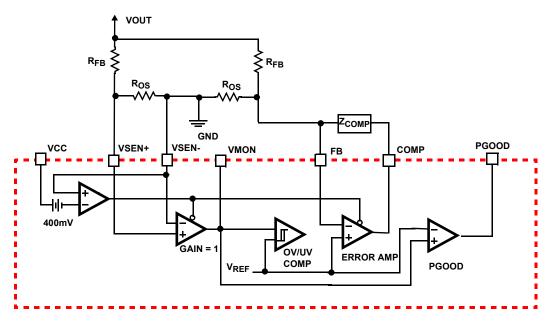

| 30            | VSEN1-       | These pins are the negative inputs of standard unity gain operational amplifier for differential remote sense for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12            | VSEN2-       | corresponding regulator (Channels 1and 2), and should be connected to the negative rail of the load/processor. When VSEN1-, VSEN2- are pulled within 400mV of VCC, the corresponding error amplifier and differential amplifier are disabled and their outputs are high impedance. Both VSEN2+ and FB2 input signal levels determine the relative phases between the internal controllers as well as the CLKOUT signal. See Table 1 on page 22. When configured as multiple power modules (each module with independent voltage loop) operating in parallel, in order to implement the current sharing control, a resistor (100Ω typical) needs to be inserted between the VSEN1- pin and the output voltage negative sense point (between VSEN1- and lower voltage sense resistor), as shown in the "Typical Application Circuits" "Multiple Power Modules in Parallel with Current Sharing Control" on page 13. This introduces a correction voltage for the modules with lower load current to keep the current distribution balanced among modules. The module with the highest load current will automatically become the master module. The recommended value for the VSEN1- resistor is 100Ω and it should not be large in order to keep the unit gain amplifier input impedance compatibility. |

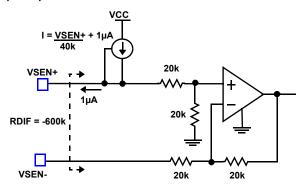

| 29            | VSEN1+       | These pins are the positive inputs of the standard unity gain operational amplifier for differential remote sense for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13            | VSEN2+       | corresponding channel (Channels 1 and 2), and should be connected to the positive rail of the load/processor. These pins can also provide precision output voltage trimming capability by pulling a resistor from this pin to the positive rail of the load (trimming down) or the return (typical VSEN1-, VSEN2- pins) of the load (trimming up). The typical input impedance of VSEN+ with respect to VSEN- is 600kΩ. By setting the resistor divider connected from the output voltage to the input of the differential amplifier, the desired output voltage can be programmed. To minimize the system accuracy error introduced by the input impedance of the differential amplifier, a resistor below 1k is recommended to be used for the lower leg (ROS) of the feedback resistor divider.  With VSEN2- pulled within 400mV of VCC, the corresponding error amplifier is disabled and VSEN2+ is one of the two pins to determine the relative phase relationship between the internal clock of both channels and the CLKOUT signal. See Table 1 on page 22 for details.                                                                                                                                                                                                                        |

| 28            | ISEN1B       | These pins are the inverting (-) inputs of the current sensing amplifiers to provide r <sub>DS(ON)</sub> , DCR, or precision resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14            | ISEN2B       | current sensing together with the ISEN1A, ISEN2A pins. Refer to "Typical Application Circuits" "2-Phase Operation with DCR Sensing" on page 7 for DCR sensing set up and "2-Phase Operation with r <sub>DS(ON)</sub> . Sensing" on page 8 for r <sub>DS(ON)</sub> sensing set up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Functional Pin Descriptions (Continued)

| PIN<br>NUMBER | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27            | ISEN1A | These pins are the noninverting (+) inputs of the current sensing amplifiers to provide r <sub>DS(ON)</sub> , DCR, or precision resistor                                                                                                                                                                                                                                                                                                                                                                                              |

| 15            | ISEN2A | current sensing together with the ISEN1B, ISEN2B pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

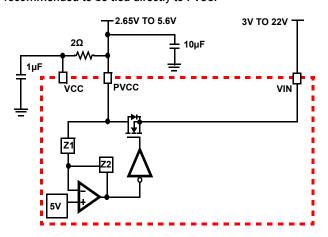

| 16            | VIN    | This pin is the input of the internal linear regulator. It should be tied directly to the input rail. The internal linear device is protected against reverse bias generated by the remaining charge of the decoupling capacitor at PVCC when losing the input rail. When used with an external 3.3V to 5V supply, this pin should be tied directly to PVCC.                                                                                                                                                                          |

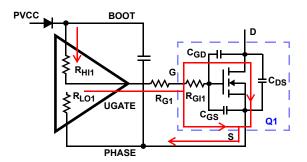

| 25            | B00T1  | These pins provide the bootstrap biases for the high-side drivers. Internal bootstrap diodes connected to the PVCC pin                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17            | B00T2  | provide the necessary bootstrap charge. Its typical operational voltage range is 2.5V to 5.6V.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 24            | UGATE1 | These pins provide the gate signals to drive the high-side devices and should be connected to the MOSFETs' gates.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18            | UGATE2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23            | PHASE1 | Connect these pins to the source of the high-side MOSFETs and the drain of the low-side MOSFETs. These pins represent                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19            | PHASE2 | the return path for the high-side gate drives.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

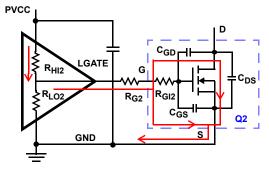

| 22            | LGATE1 | These pins provide the drive for the low-side devices and should be connected to the MOSFETs' gates.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20            | LGATE2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

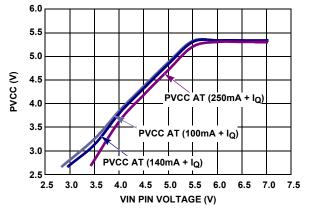

| 21            | PVCC   | This pin is the output of the internal series linear regulator. It provides the bias for both low-side and high-side drives. Its operational voltage range is 3V to 5.6V. The decoupling ceramic capacitor in the PVCC pin is 10μF.                                                                                                                                                                                                                                                                                                   |

| 26            | VCC    | This pin provides bias power for the analog circuitry. An RC filter is recommended between the connection of this pin to a 3V to 5.6V bias (typically PVCC). R is suggested to be a $5\Omega$ resistor. And in 3.3V applications, the R could be shorted to allow the low end input in concerns of the VCC falling threshold. The VCC decoupling capacitor is strongly recommended to be as large as a $10\mu$ F ceramic capacitor. This pin can be powered either by the internal linear regulator or by an external voltage source. |

| 33            | GND    | The bottom pad is the signal and power ground plane. All voltage levels are referenced to this pad. This pad provides a return path for the low-side MOSFET drives and internal power circuitries as well as all analog signals. Connect this pad to the circuit ground with the shortest possible path (more than 5 to 6 vias to the internal ground plane, placed on the soldering pad are recommended).                                                                                                                            |

## **Ordering Information**

| PART NUMBER<br>(Notes 3, 4)  | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS COMPLIANT) | PKG.<br>DWG.# |

|------------------------------|-----------------|---------------------|-----------------------------|---------------|

| ISL8120CRZ ( <u>Note 1</u> ) | ISL8120 CRZ     | 0 to +70            | 32 Ld QFN                   | L32.5x5B      |

| ISL8120IRZ (Note 2)          | ISL8120 IRZ     | -40 to +85          | 32 Ld QFN                   | L32.5x5B      |

- 1. Add "-T" suffix for 6000 unit Tape and Reel option. Please refer to TB347 for details on reel specifications.

- 2. Add "-T" suffix for 6000 unit or "-TK" suffix for 1000 unit Tape and Reel options. Please refer to TB347 for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see device information page for ISL8120. For more information on MSL please see techbrief TB363.

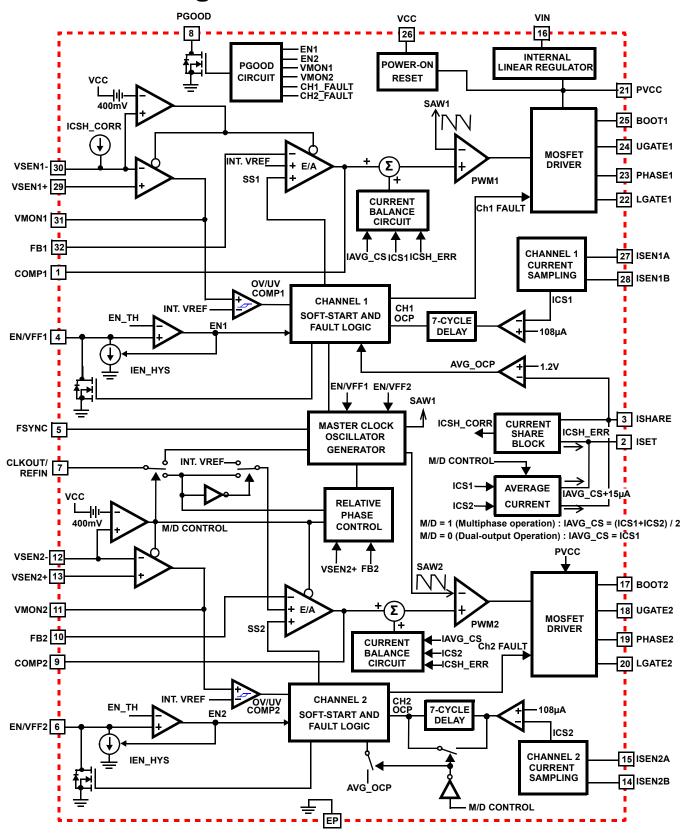

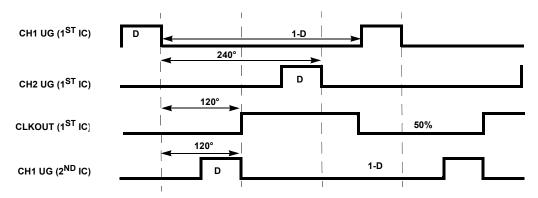

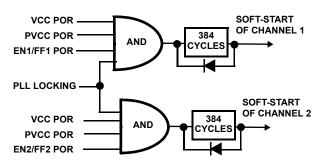

### **Controller Block Diagram**

FIGURE 2. CONTROLLER BLOCK DIAGRAM

# **Typical Application Circuits**

### 2-Phase Operation with DCR Sensing

FIGURE 3. 2-PHASE OPERATION WITH DCR SENSING

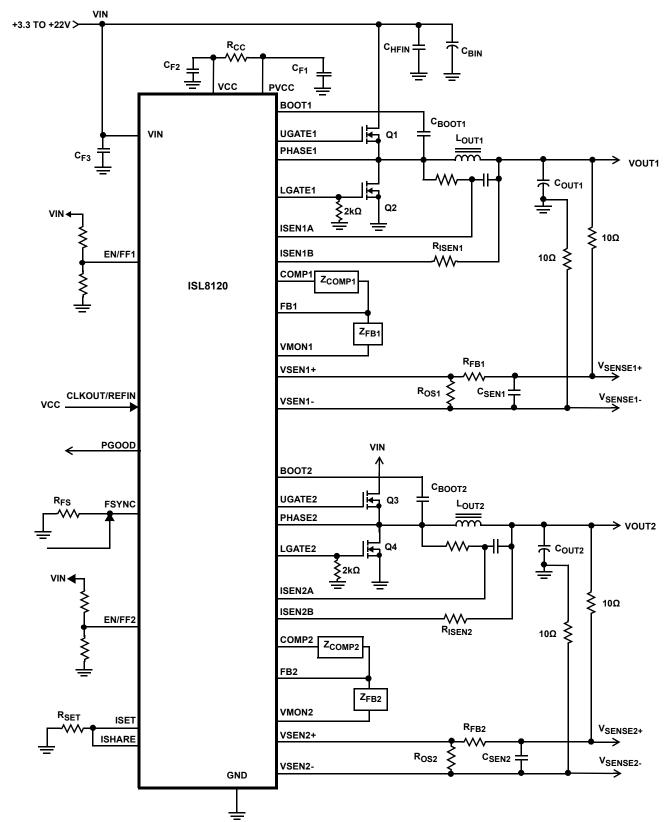

# 2-Phase Operation with $r_{DS(ON)}$ Sensing

FIGURE 4. 2-PHASE OPERATION WITH  $r_{DS(ON)}$  SENSING

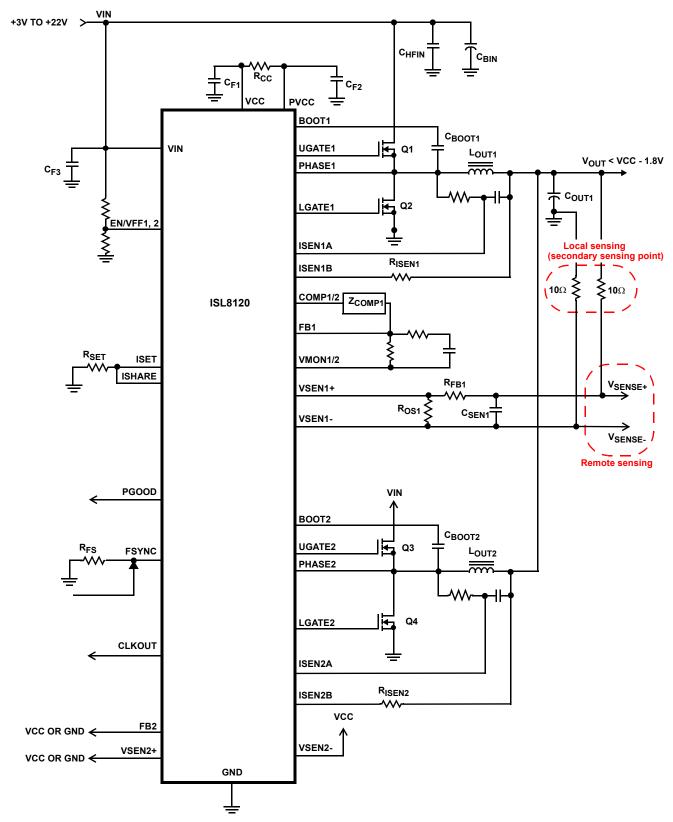

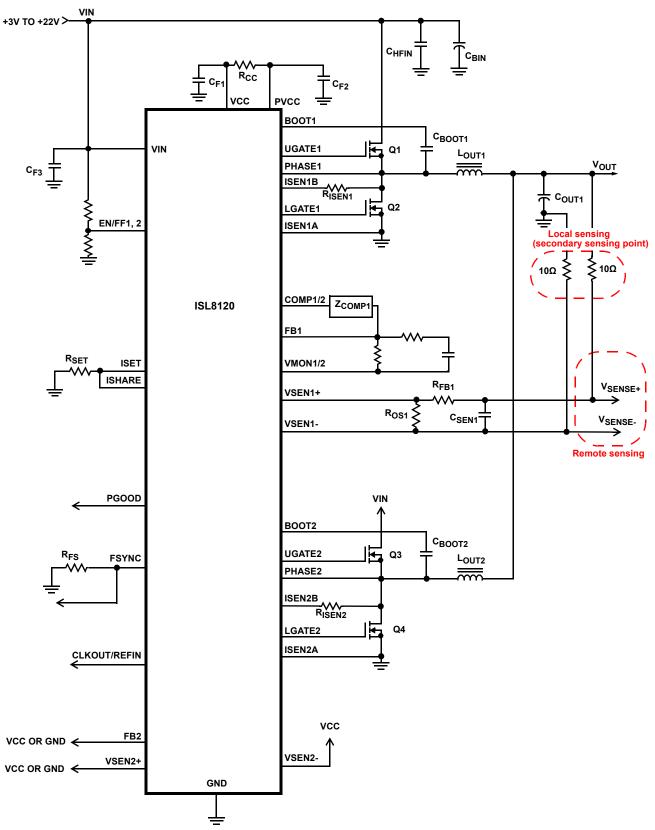

### **Dual Regulators with DCR Sensing and Remote Sense**

FIGURE 5. DUAL REGULATORS WITH DCR SENSING AND REMOTE SENSE

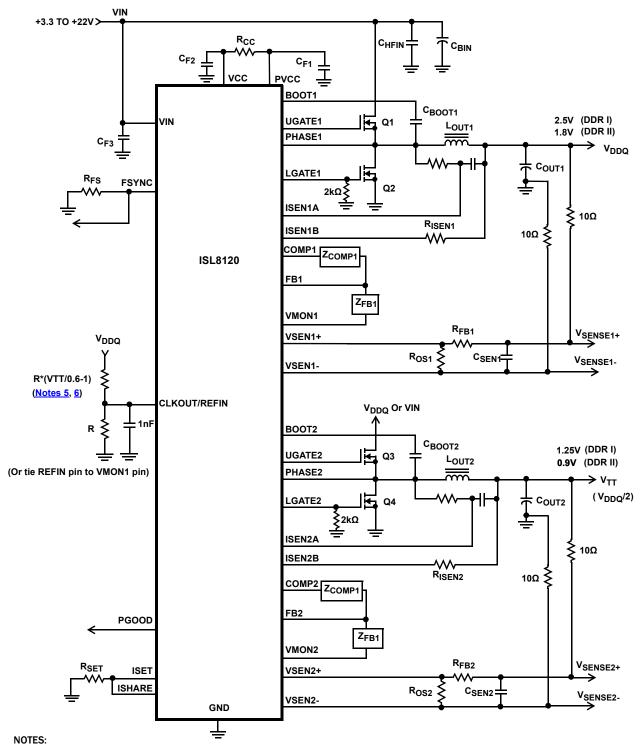

### **Double Data Rate I or II**

- 5. Setting the upper resistor to be a little higher than R\*(VDDQ/0.6 1) will set the final REFIN voltage (stead state voltage after soft-start) derived from the VDDQ to be a little higher than internal 0.6V reference. In this way, the VTT final voltage will use the internal 0.6V reference after soft-start. The other way is to add more delay at EN/VFF1 pin to have Channel 2 tracking VDDQ (check Table 1 on page 22 for more details).

- 6. Another way to set REFIN voltage is to connect VMON1 directly to the REFIN pin.

FIGURE 6. DOUBLE DATA RATE I OR II

### 3-Phase Regulator with Precision Resistor Sensing

FIGURE 7. 3-PHASE REGULATOR WITH PRECISION RESISTOR SENSING

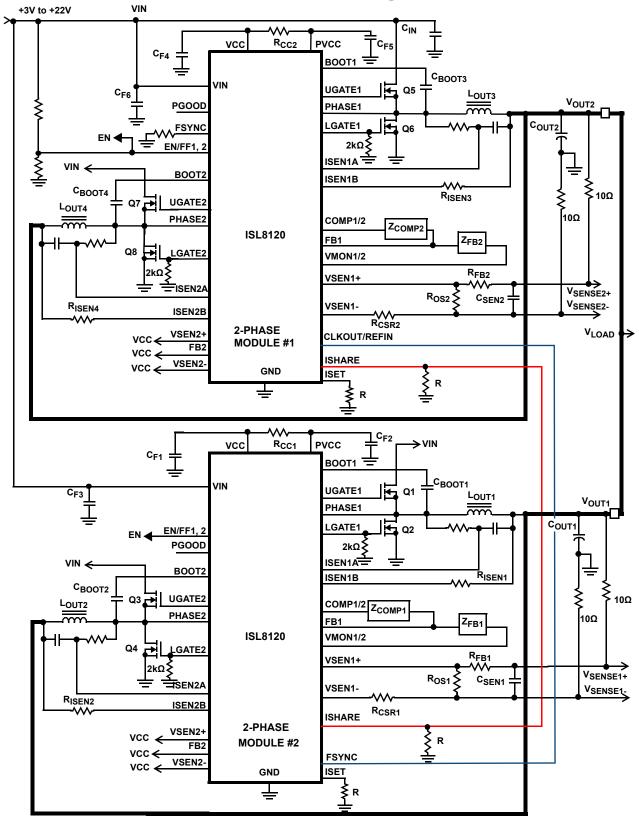

### **4-Phase Operation with DCR Sensing**

FIGURE 8. 4-PHASE OPERATION WITH DCR SENSING

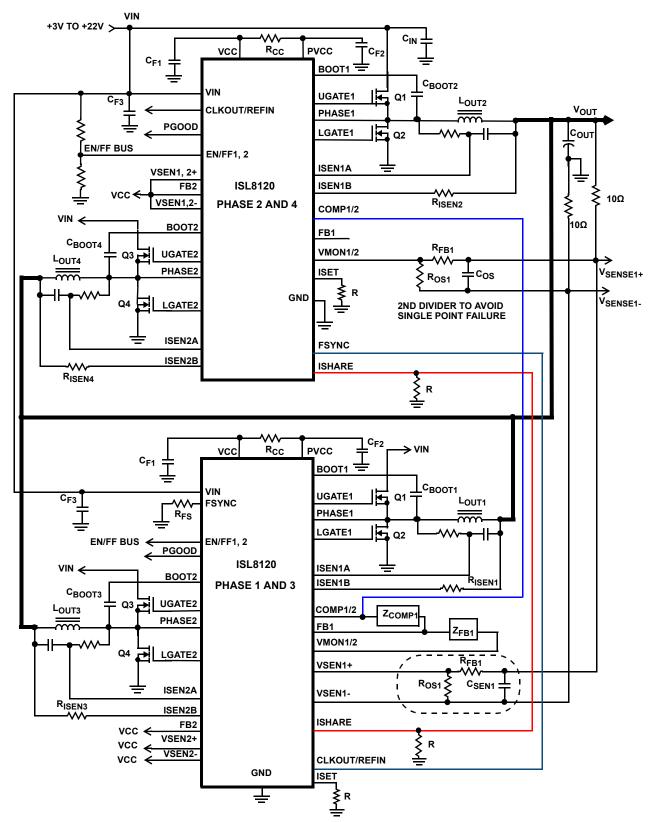

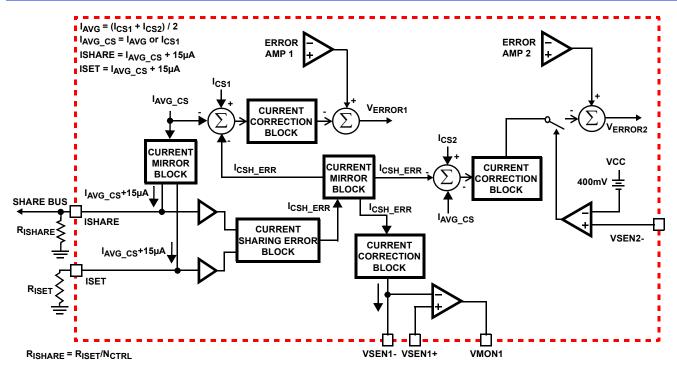

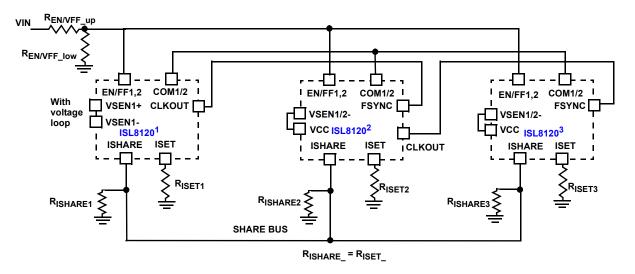

### **Multiple Power Modules in Parallel with Current Sharing Control**

FIGURE 9. MULTIPLE POWER MODULES IN PARALLEL WITH CURRENT SHARING CONTROL

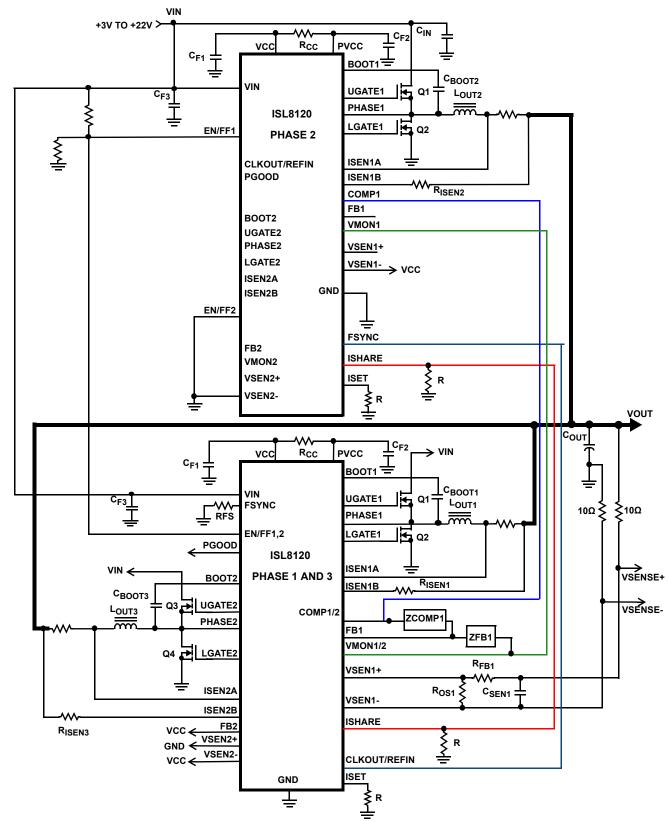

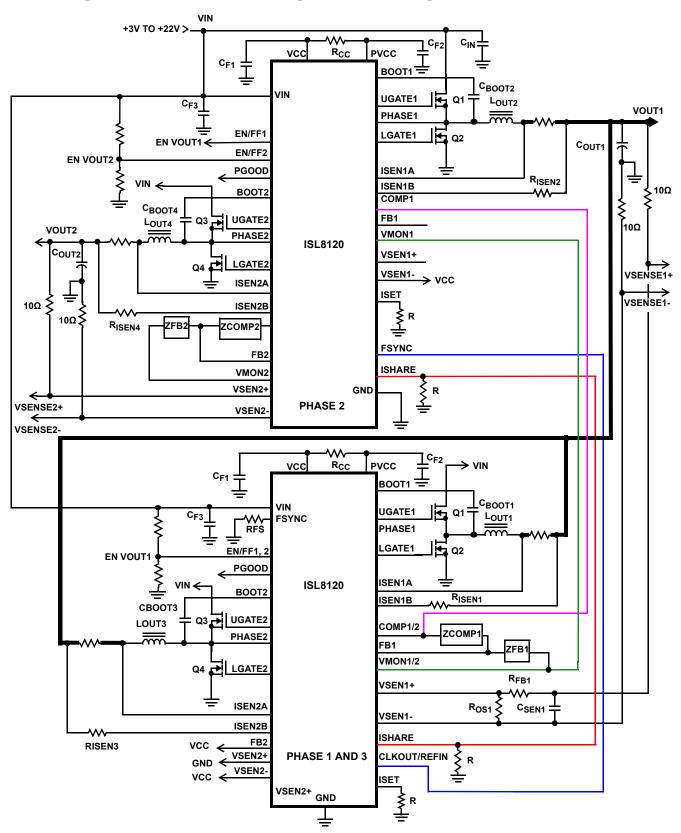

### 3-Phase Regulator with Resistor Sensing and 1 Phase Regulator

FIGURE 10. 3-PHASE REGULATOR WITH RESISTOR SENSING AND 1 PHASE REGULATOR

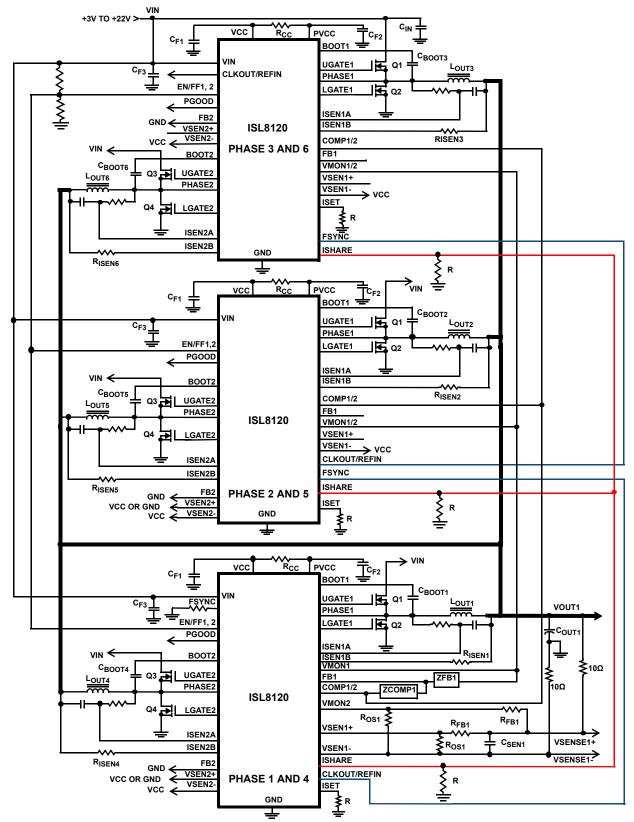

### **6-Phase Operation with DCR Sensing**

FIGURE 11. 6-PHASE OPERATION WITH DCR SENSING

### **Absolute Maximum Ratings**

| Input Voltage, VIN                        | 0.3V to +27V                             |

|-------------------------------------------|------------------------------------------|

| Driver Bias Voltage, PVCC                 | 0.3V to +6.5V                            |

| Signal Bias Voltage, VCC                  | 0.3V to +6.5V                            |

| BOOT/UGATE Voltage, VBOOT                 | 0.3V to +36V                             |

| Phase Voltage, V <sub>PHASE</sub>         | . $(V_{BOOT} - 7V)$ to $V_{BOOT} + 0.3V$ |

| BOOT to PHASE Voltage, (VBOOT - VPHASE) . | 0.3V to VCC +0.3V                        |

| Input, Output or I/O Voltage              | 0.3V to VCC +0.3V                        |

### **Thermal Information**

| Thermal Resistance (Typical Notes 7, 8) | $\theta_{JA}(^{\circ}C/W)$ | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|----------------------------|------------------------|

| 32 Ld QFN Package                       | 32                         | 3.5                    |

| Maximum Junction Temperature            |                            | 55°C to +150°C         |

| Maximum Storage Temperature Range       |                            | 65°C to +150°C         |

| Pb-Free Reflow Profile                  |                            | see <u>TB493</u>       |

### **Recommended Operating Conditions**

| Input Voltage, VIN                                    | . 3V to 22V |

|-------------------------------------------------------|-------------|

| Driver Bias Voltage, PVCC                             | .3V to 5.6V |

| Signal Bias Voltage, VCC                              | .3V to 5.6V |

| Boot to Phase Voltage (Overcharged), (VBOOT - VPHASE) | <6V         |

| Commercial Ambient Temperature Range 0°               | 'C to +70°C |

| Industrial Ambient Temperature Range40°               | 'C to +85°C |

| Maximum Junction Temperature Range                    | +125°C      |

|                                                       |             |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 7. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 8. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Recommended operating conditions, unless otherwise noted. **Boldface limits apply across the operating** temperature range, -40°C to +85°C (Industrial) or 0°C to +70°C (Commercial).

| PARAMETER                               | SYMBOL               | TEST CONDITIONS                                                                      | MIN<br>( <u>Note 10</u> ) | TYP  | MAX<br>( <u>Note 10</u> ) | UNIT |

|-----------------------------------------|----------------------|--------------------------------------------------------------------------------------|---------------------------|------|---------------------------|------|

| VCC SUPPLY CURRENT                      |                      |                                                                                      | <u>'</u>                  |      |                           |      |

| Nominal Supply VIN Current              | I <sub>Q_VIN</sub>   | V <sub>IN</sub> = 20V; VCC = PVCC; f <sub>SW</sub> = 500kHz;<br>UGATE, LGATE = open  | 11                        | 15   | 20                        | mA   |

| Nominal Supply VIN Current              | I <sub>Q_VIN</sub>   | V <sub>IN</sub> = 3.3V; VCC = PVCC;<br>f <sub>SW</sub> = 500kHz; UGATE, LGATE = open | 8                         | 12   | 14                        | mA   |

| Shutdown Supply PVCC Current            | I <sub>PVCC</sub>    | EN = OV, PVCC = 5V                                                                   | 0.5                       | 1.0  | 1.4                       | mA   |

| Shutdown Supply VCC Current             | lvcc                 | EN = OV, VCC = 3V                                                                    | 7                         | 10   | 12                        | mA   |

| INTERNAL LINEAR REGULATOR               |                      |                                                                                      |                           |      |                           |      |

| Maximum Current (Note 9)                | I <sub>PVCC</sub>    | PVCC = 4V to 5.6V                                                                    |                           | 250  |                           | mA   |

|                                         |                      | PVCC = 3V to 4V                                                                      |                           | 150  |                           | mA   |

| Saturated Equivalent Impedance (Note 9) | R <sub>LDO</sub>     | P-Channel MOSFET (V <sub>IN</sub> = 5V)                                              |                           | 1    |                           | Ω    |

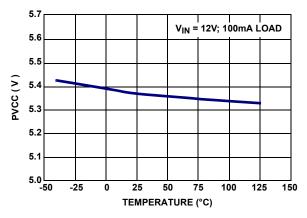

| PVCC Voltage Level                      | PVCC                 | I <sub>PVCC</sub> = 0mA; 0°C < T <sub>A</sub> < +85°C;<br>V <sub>IN</sub> = 12V      | 5.15                      | 5.40 | 5.65                      | V    |

|                                         |                      | I <sub>PVCC</sub> = 0mA; -40 °C < T <sub>A</sub> < +85 °C;<br>V <sub>IN</sub> = 12V  | 5.15                      | 5.40 | 5.95                      | V    |

| Equivalent LDO Output Resistance        | R <sub>LDO_OUT</sub> | V <sub>IN</sub> = 12V                                                                |                           | 0.3  |                           | Ω    |

| POWER-ON RESET                          |                      |                                                                                      |                           |      |                           |      |

| Rising V <sub>CC</sub> Threshold        |                      |                                                                                      |                           | 2.85 | 2.97                      | ٧    |

| Falling V <sub>CC</sub> Threshold       |                      |                                                                                      |                           | 2.65 | 2.75                      | ٧    |

| Rising PVCC Threshold                   |                      | 0°C < T <sub>A</sub> < +75°C                                                         |                           | 2.85 | 2.97                      | ٧    |

|                                         |                      | -40°C < T <sub>A</sub> < +85°C                                                       |                           | 2.85 | 3.05                      | ٧    |

| Falling PVCC Threshold                  |                      |                                                                                      |                           | 2.65 | 2.75                      | V    |

# **Electrical Specifications** Recommended operating conditions, unless otherwise noted. **Boldface limits apply across the operating** temperature range, 40°C to +85°C (Industrial) or 0°C to +70°C (Commercial). (Continued)

| PARAMETER                                  | SYMBOL                 | TEST CONDITIONS                                                                           | MIN<br>( <u>Note 10</u> ) | TYP                   | MAX<br>( <u>Note 10</u> ) | UNIT             |

|--------------------------------------------|------------------------|-------------------------------------------------------------------------------------------|---------------------------|-----------------------|---------------------------|------------------|

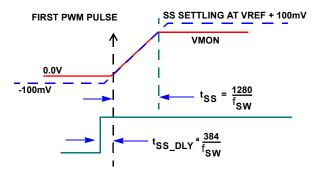

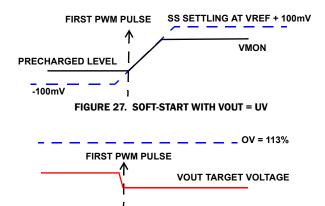

| System Soft-Start Delay (Note 9)           | tss_dly                | After PLL, V <sub>CC</sub> , and PVCC PORs, and EN(s) above their thresholds              |                           | 384                   |                           | Cycles           |

| ENABLE                                     |                        |                                                                                           |                           |                       |                           |                  |

| Turn-On Threshold Voltage                  |                        |                                                                                           | 0.75                      | 0.8                   | 0.86                      | V                |

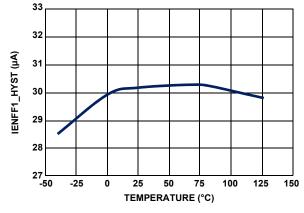

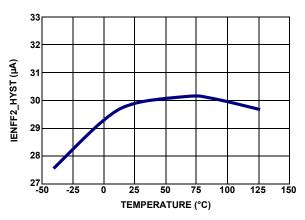

| Hysteresis Sink Current                    | I <sub>EN_HYS</sub>    | 0°C < T <sub>A</sub> < +85°C                                                              | 25                        | 30                    | 35                        | μΑ               |

|                                            |                        | -40°C < T <sub>A</sub> < +85°C                                                            | 23                        | 30                    | 35                        | μΑ               |

| Undervoltage Lockout Hysteresis (Note 9)   | V <sub>EN_HYS</sub>    | $V_{EN\_RTH} = 10.6V; V_{EN\_FTH} = 9V$<br>$R_{UP} = 53.6k\Omega, R_{DOWN} = 5.23k\Omega$ |                           | 1.6                   |                           | V                |

| Sink Current                               | I <sub>EN_SINK</sub>   | V <sub>ENFF</sub> = 1V                                                                    | 15.4                      |                       |                           | mA               |

| Sink Impedance                             | R <sub>EN_SINK</sub>   | V <sub>ENFF</sub> = 1V                                                                    |                           |                       | 64                        | Ω                |

| OSCILLATOR                                 |                        |                                                                                           |                           |                       |                           |                  |

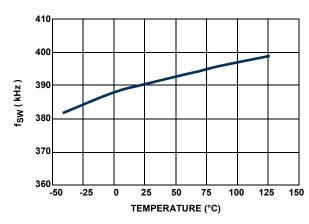

| Oscillator Frequency Range                 |                        |                                                                                           | 150                       |                       | 1500                      | kHz              |

| Oscillator Frequency                       |                        | R <sub>FS</sub> = 100k, <u>Figure 42 on page 33</u>                                       | 344                       | 377                   | 406                       | kHz              |

| Total Variation                            |                        | V <sub>CC</sub> = 5V; -40°C < T <sub>A</sub> < +85°C                                      | -9                        |                       | +9                        | %                |

| Peak-to-Peak Ramp Amplitude                | $\Delta V_{RAMP}$      | V <sub>CC</sub> = 5V, V <sub>EN</sub> = 0.8V                                              |                           | 1                     |                           | V <sub>P-P</sub> |

| Linear Gain of Ramp Over V <sub>EN</sub>   | G <sub>RAMP</sub>      | $G_{RAMP} = \Delta V_{RAMP} / V_{EN}$                                                     |                           | 1.25                  |                           |                  |

| Ramp Peak Voltage                          | V <sub>RAMP_PEAK</sub> | $V_{EN} = V_{CC}$                                                                         |                           | V <sub>CC</sub> - 1.4 |                           | ٧                |

| Peak-to-Peak Ramp Amplitude                | $\Delta V_{RAMP}$      | V <sub>EN</sub> = V <sub>CC</sub> = 5.4V, R <sub>UP</sub> = 2k                            |                           | 3                     |                           | V <sub>P-P</sub> |

| Peak-to-Peak Ramp Amplitude                | $\Delta V_{RAMP}$      | V <sub>EN</sub> = V <sub>CC</sub> = 3V; R <sub>UP</sub> = 2k                              |                           | 0.6                   |                           | V <sub>P-P</sub> |

| Ramp Amplitude Upon Disable                | $\Delta V_{RAMP}$      | V <sub>EN</sub> = 0V; V <sub>CC</sub> = 3.5V to 5.5V                                      |                           | 1                     |                           | V <sub>P-P</sub> |

| Ramp Amplitude Upon Disable                | $\Delta V_{RAMP}$      | V <sub>EN</sub> = 0V; V <sub>CC</sub> < 3.4V                                              |                           | V <sub>CC</sub> - 2.4 |                           | V <sub>P-P</sub> |

| Ramp DC Offset                             | V <sub>RAMP_OS</sub>   |                                                                                           |                           | 1                     |                           | ٧                |

| FREQUENCY SYNCHRONIZATION AND PHAS         | E LOCK LOOP            |                                                                                           |                           | ı                     | 1                         |                  |

| Synchronization Frequency                  |                        | V <sub>CC</sub> = 5V                                                                      | 150                       |                       | 1500                      | kHz              |

| PLL Locking Time                           |                        | V <sub>CC</sub> = 5.4V; f <sub>SW</sub> = 400kHz                                          |                           | 105                   |                           | μs               |

|                                            |                        | V <sub>CC</sub> = 2.97V; f <sub>SW</sub> = 400kHz                                         |                           | 150                   |                           | μs               |

| Input Signal Duty Cycle Range (Note 9)     |                        |                                                                                           | 10                        |                       | 90                        | %                |

| PWM                                        |                        | 1                                                                                         |                           |                       |                           |                  |

| Minimum PWM OFF Time                       | t <sub>MIN_OFF</sub>   |                                                                                           | 310                       | 345                   | 410                       | ns               |

| Current Sampling Blanking Time (Note 9)    | <sup>t</sup> BLANKING  |                                                                                           |                           | 175                   |                           | ns               |

| REFERENCE                                  |                        | 1                                                                                         |                           | I                     | 1                         | 1                |

| Channel 1 Reference Voltage (Include Error | V <sub>REF1</sub>      | -0°C < T <sub>A</sub> < +70°C                                                             |                           | 0.6                   |                           | V                |

| and Differential Amplifiers' Offsets)      |                        |                                                                                           | -0.6                      |                       | 0.6                       | %                |

|                                            |                        | -40°C < T <sub>A</sub> < +85°C                                                            |                           | 0.6                   |                           | ٧                |

|                                            |                        |                                                                                           | -0.7                      |                       | 0.7                       | %                |

| Channel 2 Reference Voltage (Include Error | V <sub>REF2</sub>      | -0°C < T <sub>A</sub> < +70°C                                                             |                           | 0.6                   |                           | V                |

| and Differential Amplifiers' Offsets)      |                        |                                                                                           | -0.75                     |                       | 0.75                      | %                |

|                                            |                        | -40°C < T <sub>A</sub> < +85°C                                                            |                           | 0.6                   |                           | V                |

|                                            |                        |                                                                                           | -0.75                     |                       | 0.95                      | %                |

# **Electrical Specifications** Recommended operating conditions, unless otherwise noted. **Boldface limits apply across the operating** temperature range, 40°C to +85°C (Industrial) or 0°C to +70°C (Commercial). (Continued)

| PARAMETER                                                                                         | SYMBOL                          | TEST CONDITIONS                                                                                                       | MIN<br>( <u>Note 10</u> ) | TYP                   | MAX<br>( <u>Note 10</u> ) | UNIT |

|---------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|---------------------------|------|

| ERROR AMPLIFIER                                                                                   |                                 |                                                                                                                       | 1                         | l                     | '                         |      |

| DC Gain (Note 9)                                                                                  |                                 | R <sub>L</sub> = 10k, C <sub>L</sub> = 100pF, at COMP Pin                                                             |                           | 98                    |                           | dB   |

| Unity Gain-Bandwidth ( <u>Note 9</u> )                                                            | UGBW_EA                         | $R_L = 10k$ , $C_L = 100pF$ , at COMP Pin                                                                             |                           | 80                    |                           | MHz  |

| Input Common-Mode Range (Note 9)                                                                  |                                 |                                                                                                                       | -0.2                      |                       | V <sub>CC</sub> - 1.8     | ٧    |

| Output Voltage Swing                                                                              |                                 | V <sub>CC</sub> = 5V                                                                                                  | 0.85                      |                       | V <sub>CC</sub> - 1.0     | ٧    |

| Slew Rate (Note 9)                                                                                | SR_EA                           | R <sub>L</sub> = 10k, C <sub>L</sub> = 100pF, at COMP Pin                                                             |                           | 20                    |                           | V/µs |

| Input Current (Note 9)                                                                            | I <sub>FB</sub>                 | Positive direction Into the FB pin                                                                                    |                           | 100                   |                           | nA   |

| Output Sink Current                                                                               | Ісомр                           |                                                                                                                       |                           | 3                     |                           | mA   |

| Output Source Current                                                                             | Ісомр                           |                                                                                                                       |                           | 6                     |                           | mA   |

| Disable Threshold ( <u>Note 9</u> )                                                               | V <sub>VSEN-</sub>              |                                                                                                                       |                           | V <sub>CC</sub> - 0.4 |                           | ٧    |

| DIFFERENTIAL AMPLIFIER                                                                            |                                 |                                                                                                                       |                           |                       |                           |      |

| DC Gain (Note 9)                                                                                  | UG_DA                           | Unity Gain Amplifier                                                                                                  |                           | 0                     |                           | dB   |

| Unity Gain Bandwidth ( <u>Note 9</u> )                                                            | UGBW_DA                         |                                                                                                                       |                           | 5                     |                           | MH   |

| VSEN+ pin Sourcing Current                                                                        | I <sub>VSEN+</sub>              |                                                                                                                       | 0.2                       | 1                     | 2.5                       | μA   |

| Maximum Source Current for Current<br>Sharing (See <u>Figure 7 on page 11</u> ) ( <u>Note 9</u> ) | I <sub>VSEN1</sub> -            | VSEN1- Source current for current<br>Sharing when parallel multiple modules<br>each of which has its own voltage loop |                           | 350                   |                           | μA   |

| Input Impedance                                                                                   | R <sub>VSEN+_to</sub><br>_VSEN- | $V_{VSEN+}/I_{VSEN+}$ , $V_{VSEN+} = 0.6V$                                                                            |                           | -600                  |                           | kΩ   |

| Output Voltage Swing (Note 9)                                                                     |                                 |                                                                                                                       | 0                         |                       | V <sub>CC</sub> - 1.8     | ٧    |

| Input Common-Mode Range (Note 9)                                                                  |                                 |                                                                                                                       | -0.2                      |                       | V <sub>CC</sub> - 1.8     | ٧    |

| Disable Threshold (Note 9)                                                                        | V <sub>VSEN</sub> -             | V <sub>MON1</sub> , V <sub>MON2</sub> = Tri-state                                                                     |                           | V <sub>CC</sub> - 0.4 |                           | ٧    |

| GATE DRIVERS                                                                                      |                                 |                                                                                                                       | 1                         | l                     |                           |      |

| Upper Drive Source Resistance                                                                     | R <sub>UGATE</sub>              | 45mA source current                                                                                                   |                           | 1.0                   |                           | Ω    |

| Upper Drive Sink Resistance                                                                       | R <sub>UGATE</sub>              | 45mA sink current                                                                                                     |                           | 1.0                   |                           | Ω    |

| Lower Drive Source Resistance                                                                     | R <sub>LGATE</sub>              | 45mA source current                                                                                                   |                           | 1.0                   |                           | Ω    |

| Lower Drive Sink Resistance                                                                       | R <sub>LGATE</sub>              | 45mA sink current                                                                                                     |                           | 0.4                   |                           | Ω    |

| OVERCURRENT PROTECTION                                                                            |                                 |                                                                                                                       | I                         |                       | 1                         |      |

| Channel Overcurrent Limit (Note 9)                                                                | I <sub>SOURCE</sub>             | V <sub>CC</sub> = 2.97V to 5.6V                                                                                       |                           | 108                   |                           | μΑ   |

| Channel Overcurrent Limit                                                                         | I <sub>SOURCE</sub>             | $V_{CC} = 5V; 0 ^{\circ}C < T_A < +70 ^{\circ}C$                                                                      | 94                        | 108                   | 122                       | μΑ   |

|                                                                                                   |                                 | $V_{CC} = 5V; -40 ^{\circ}\text{C} < T_{A} < +85 ^{\circ}\text{C}$                                                    | 89                        | 108                   | 122                       | μΑ   |

| Share Pin OC Threshold                                                                            | V <sub>OC_ISHARE</sub>          | V <sub>CC</sub> = 2.97V to 5.6V<br>(comparator offset included)                                                       |                           | 1.20                  |                           | V    |

|                                                                                                   |                                 | V <sub>CC</sub> = 5V<br>(comparator offset included)                                                                  | 1.16                      | 1.20                  | 1.22                      | V    |

| CURRENT SHARE                                                                                     |                                 | •                                                                                                                     | 1                         |                       | 1                         |      |

| Internal Balance Accuracy (Note 9)                                                                |                                 | V <sub>CC</sub> = 2.97V and 5.6V, 1% resistor sense, 10mV signal                                                      |                           | ±5                    |                           | %    |

| Internal Balance Accuracy (Note 9)                                                                |                                 | V <sub>CC</sub> = 4.5V and 5.6V, 1% resistor sense, 10mV signal                                                       |                           | ±5                    |                           | %    |

**Electrical Specifications** Recommended operating conditions, unless otherwise noted. **Boldface limits apply across the operating** temperature range, -40°C to +85°C (Industrial) or 0°C to +70°C (Commercial). (Continued)

| PARAMETER                                   | SYMBOL               | TEST CONDITIONS                                                  | MIN<br>( <u>Note 10</u> ) | TYP | MAX<br>(Note 10) | UNIT |

|---------------------------------------------|----------------------|------------------------------------------------------------------|---------------------------|-----|------------------|------|

| External Current Share Accuracy (Note 9)    |                      | V <sub>CC</sub> = 2.97V and 5.6V, 1% resistor sense, 10mV signal |                           | ±20 |                  | %    |

| POWER-GOOD MONITOR                          |                      |                                                                  |                           |     |                  |      |

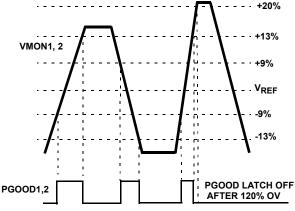

| Undervoltage Falling Trip Point             | V <sub>UVF</sub>     | Percentage below reference point                                 | -15                       | -13 | -11              | %    |

| Undervoltage Rising Hysteresis              | V <sub>UVR_HYS</sub> | Percentage above UV trip point                                   |                           | 4   |                  | %    |

| Overvoltage Rising Trip Point               | V <sub>OVR</sub>     | Percentage above reference point                                 | 11                        | 13  | 15               | %    |

| Overvoltage Falling Hysteresis              | V <sub>OVF_HYS</sub> | Percentage below OV trip point                                   |                           | 4   |                  | %    |