MCF5206EUM/D, rev.1

# MCF5206e ColdFire<sup>®</sup> Integrated Microprocessor

# User's Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and @ ar registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© MOTOROLA, 1998 All Rights Reserved. For More Information On This Product, Go to: www.freescale.com

ColdFire is a Registered Trademark of Motorola, Inc. All other trademarks reside with their respective owners.

For More Information On This Product, Go to: www.freescale.com

### **DOCUMENTATION FEEDBACK**

# FAX 512-891-8593—Documentation Comments Only (no technical questions please) http://www.mot.com/hpesd/docs\_survey.html—Documentation Feedback Only

The Technical Communications Department welcomes your suggestions for improving our documentation and encourages you to complete the documentation feedback form at the World Wide Web address listed above. In return for your efforts, you will receive a small token of our appreciation. Your help helps us measure how well we are serving your information requirements.

The Technical Communications Department also provides a fax number for you to submit any questions or comments about this document or how to order other documents. Please provide the part number and revision number (located in upper right-hand corner of the cover) and the title of the document. When referring to items in the manual, please reference by the page number, paragraph number, figure number, table number, and line number if needed. **Please do not fax technical questions to this number**.

When sending a fax, please provide your name, company, fax number, and phone number including area code.

#### For Internet Access:

Web Only: http://www.motorola.com/coldfire

#### For Hotline Questions:

FAX (US or Canada): 1-800-248-8567

### **Applications and Technical Information**

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

### - Sales Offices -

Field Applications Engineering Available Through All Sales Offices

| UNITED STATES                                                                | (205) 464-6800                   | GERMANY, Langenhagen/ Hanover GERMANY, Munich                                                                  | 49(511)789911<br>49 89 92103-0   |

|------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------|

| ALABAMA, Huntsville<br>ARIZONA, Tempe                                        |                                  | GERMANY, Nuremberg                                                                                             | 49 911 64-3044                   |

| CALIFORNIA, Agoura Hills<br>CALIFORNIA, Los Angeles                          | (818) 706-1929                   | GERMANY, Nuremberg<br>GERMANY, Sindelfingen<br>GERMANY, Wiesbaden                                              | 49 7031 69 910                   |

| CALIFORNIA, Irvine                                                           | (/ 14) / 33-/ 300                | GERMANY, Wiesbaden                                                                                             | 49 611 761921                    |

| CALIFORNIA, Roseville                                                        | (916) 922-7152                   | HONG KONG, Kwai Fong<br>Tai Po                                                                                 | 852-4808333<br>852-6668333       |

| CALIFORNIA, San Diego                                                        | (619) 541-2163<br>(408) 749-0510 | INDIA, Bangalore                                                                                               | (91-812)627094                   |

| CALIFORNIA, San Diego<br>CALIFORNIA, Sunnyvale<br>COLORADO, Colorado Springs | (719) 599-7497                   | ISRAEL, Tel Aviv                                                                                               | 972(3)753-8222                   |

| COLORADO. Denver                                                             | (303) 337-3434<br>(203) 949-4100 | ITALY, Milan                                                                                                   | 39(2)82201                       |

| CONNECTICUT, Wallingford<br>FLORIDA, Maitland                                | (407) 628-2636                   | JAPAN, Aizu<br>JAPAN, Atsugi                                                                                   | 81(241)272231<br>81(0462)23-0761 |

| FLORIDA, Pompano Beach/                                                      | ( )                              | JAPAN, Kumagaya                                                                                                | 81(0485)26-2600                  |

| Fort Lauderdale<br>FLORIDA, Clearwater                                       | (305) 486-9776<br>(813) 538-7750 | JAPAN, Kyushu                                                                                                  | 81(092)771-4212                  |

| GEORGIA, Atlanta                                                             | (404) 729-7100                   | JAPAN, Mito                                                                                                    | 81(0292)26-2340                  |

| IDAHO. Boise                                                                 | (208) 323-9413                   | JAPAN, Nagoya                                                                                                  | 81(052)232-1621                  |

| ILLINOIS, Chicago/Hoffman Estates<br>INDIANA, Fort Wayne                     | (708) 490-9500<br>(219) 436-5818 | JAPAN, Osaka<br>JAPAN, Sendai                                                                                  | 81(06)305-1801<br>81(22)268-4333 |

| INDIANA, Indianapolis                                                        | (317) 571-0400<br>(317) 457-6634 | JAPAN, Tachikawa                                                                                               | 81(0425)23-6700                  |

| INDIANA, Kokomo                                                              | (317) 457-6634                   |                                                                                                                | 81(03)3440-3311                  |

| IOWA, Cedar Rapids<br>KANSAS, Kansas City/Mission                            | (319) 373-1328<br>(913) 451-8555 | JAPAN, Yokohama<br>KOREA, Pusan                                                                                | 81(045)472-2751                  |

| MARYLAND. Columbia                                                           | (410) 381-1570                   |                                                                                                                | 82(51)4635-035<br>82(2)554-5188  |

| MASSACHUSETTS, Marborough<br>MASSACHUSETTS, Woburn                           | (508) 481-8100<br>(617) 932-9700 | KOREA, Seoul<br>MALAYSIA, Penang<br>MEXICO, Mexico City                                                        | 60(4)374514                      |

| MICHIGAN, Detroit                                                            | (313) 347-6800                   | MEXICO, Mexico City                                                                                            | 52(5)282-2864                    |

| MINNESOTA, Minnetonka<br>MISSOURI, St. Louis                                 | (612) 932-1500                   | MEXICO, Guadalajara                                                                                            | 52(36)21-8977                    |

| NEW JERSEY, Fairfield                                                        | (314) 275-7380<br>(201) 808-2400 | Marketing<br>Customer Service                                                                                  | 52(36)21-9023<br>52(36)669-9160  |

| NEW YORK Fairport                                                            | (716) 425-4000                   | NETHERLANDS, Best                                                                                              | (31)49988 612 11                 |

| NEW YORK, Hauppauge<br>NEW YORK, Poughkeepsie/Fishkill                       | (516) 361-7000<br>(914) 473-8102 | Customer Service<br>NETHERLANDS, Best<br>PUERTO RICO, San Juan<br>SINGAPORE                                    | (809)793-2170                    |

| NORTH CAROLINA, Raleidh                                                      | (919) 870-4355                   | SINGAPORE<br>SPAIN, Madrid                                                                                     | (65)2945438<br>34(1)457-8204     |

| OHIO, Cleveland<br>OHIO, Columbus/Worthington                                | (216) 349-3100<br>(614) 431-8492 | SPAIN, Madrid<br>or                                                                                            | 34(1)457-8254                    |

| OHIO, Dayton                                                                 | (513) 495-6800                   | SWEDEN Solna                                                                                                   | 46(8)734-8800                    |

| OKLAHOMA, Tulsa                                                              | (800) 544-9496                   | SWITZERLAND, Geneva                                                                                            | 41(22)7991111                    |

| OREGON, Portland<br>PENNSYLVANIA, Colmar                                     | (503) 641-3681<br>(215) 997-1020 | SWITZERLAND, Zurich                                                                                            | 41(1)730 4074<br>886(2)717-7089  |

| Philadelphia/Horsham                                                         | (215) 997-1020<br>(215) 957-4100 | THAILAND. Bangkok                                                                                              | (66-2)254-4910                   |

| TENNESSEE, Knoxville                                                         | (615) 584-4841                   | SWITZERLAND, Geneva<br>SWITZERLAND, Zurich<br>TAIWAN, Taipei<br>THAILAND, Bangkok<br>UNITED KINGDOM, Aylesbury | 44(296)395-252                   |

| TEXAS, Austin<br>TEXAS, Houston                                              | (512) 873-2000<br>(800) 343-2692 | FULL LINE REPRESENT                                                                                            | ATIVES                           |

| TEXAS Plano                                                                  | (214) 516-5100                   | COLORADO, Grand Junction                                                                                       |                                  |

| VIRGINIA, Richmond<br>WASHINGTON, Bellevue                                   | (804) 285-2100<br>(206) 454-4160 | Cheryl Lee Whltely<br>KANSAS, Wichita                                                                          | (303) 243-9658                   |

| Seattle Access                                                               | (206) 622-9960                   | Melinda Shores/Kelly Greiving                                                                                  | (316) 838 0190                   |

| WISCONSIN, Milwaukee/Brookfield                                              | (414) 792-0122                   | NEVADA, Reno                                                                                                   |                                  |

| CANADA<br>BRITISH COLUMBIA, Vancouver                                        | (604) 293-7605                   | Galena Technology Group                                                                                        | (702) 746 0642                   |

| ONTARIO, Toronto                                                             | (416) 497-8181                   | NEW MEXICO, Albuquerque<br>S&S Technologies, Inc.                                                              | (505) 298-7177                   |

| ONTARIO, Ottawa                                                              | (613) 226-3491                   | UTAH, Salt Lake City                                                                                           | (303) 230-1111                   |

| QUEBEC, Montreal                                                             | (514) 731-6881                   | Utah Component Sales, Inc.                                                                                     | (801) 561-5099                   |

|                                                                              | (04.0)007.0744                   | WASHINGTON, Spokane                                                                                            | (500) 004 0000                   |

| AUSTRALIA, Melbourne<br>AUSTRALIA, Sydney                                    | (61-3)887-0711<br>(61(2)906-3855 | Doug Kenley<br>ARGENTINA, Buenos Aires                                                                         | (509) 924-2322                   |

| BRAZIL, Sao Paulo                                                            | 55(11)815-4200                   | Argonics, S.A.                                                                                                 | (541) 343-1787                   |

| CHINA, Beijing                                                               | 86 505-2180                      | HYBRID COMPONENTS RE                                                                                           | SELLERS                          |

| FINLAND, Helsinki                                                            | 358-0-35161191                   | Elmo Semiconductor                                                                                             | (818) 768-7400                   |

| Car Phone<br>FRANCE, Paris/Vanves                                            | 358(49)211501<br>33(1)40 955 900 | Minco Technology Labs Inc.                                                                                     | (512) 834-2022                   |

|                                                                              | 000 000 070 000                  | Semi Dice Inc.                                                                                                 | (310) 594-4631                   |

# PREFACE

The *MCF5206e ColdFire®* Integrated Microprocessor User's Manual describes the programming, capabilities, and operation of the MCF5206e device. Refer to the *ColdFire Family Programmer's Reference Manual Rev 1.0* (MCF5200PRMREV1/D) for information on the ColdFire Family of microprocessors.

#### CONTENTS

This user manual is organized as follows:

Section 1: Introduction Section 2: Signal Description Section 3: ColdFire Core Section 4: Instruction Cache Section 5: SRAM Section 6: Bus Operation Section 7: DMA Controller Module Section 8: System Integration Module (SIM) Section 9: Chip-Select Module Section 10: Parallel Port (General-Purpose I/O) Module Section 11: DRAM Controller Section 12: UART Modules Section 13: M-Bus Module Section 14: Timer Module Section 15: Debug Support Section 16: IEEE 1149.1 Test Access Port (JTAG) Section 17: Electrical Characteristics Section 18: Mechanical Characteristics Appendix A: MCF5206e Memory Map Appendix B: Porting from M68000

Index

| 1  | Introduction                        |

|----|-------------------------------------|

| 2  | Signal Description                  |

| 3  | ColdFire Core                       |

| 4  | Instruction Cache                   |

| 5  | SRAM                                |

| 6  | Bus Operation                       |

| 7  | DMA Controller Module               |

| 8  | System Integration Module (SIM)     |

| 9  | Chip Select Module                  |

| 10 | Parallel Port (General-Purpose I/O) |

| 11 | DRAM Controller                     |

| 12 | UART Modules                        |

| 13 | MBus Module                         |

| 14 | Timer Module                        |

| 15 | Debug Support                       |

| 16 | IEEE 1149.1 JTAG                    |

| 17 | <b>Electrical Characteristics</b>   |

| 18 | Mechanical Characteristics          |

| Α  | Appendix A: MCF5206e Memory Map     |

| В  | Appendix B: Porting from M68000     |

|    |                                     |

|   | 1                                      | Introduction                        |

|---|----------------------------------------|-------------------------------------|

|   | 2                                      | Signal Description                  |

|   | 3                                      | ColdFire Core                       |

|   | 4                                      | Instruction Cache                   |

|   | 5                                      | SRAM                                |

| ( | 6                                      | Bus Operation                       |

|   | 7                                      | DMA Controller Module               |

|   | 8                                      | System Integration Module (SIM)     |

|   | 8<br>9<br>10                           | Chip Select Module                  |

|   | 10                                     | Parallel Port (General-Purpose I/O) |

|   | 11                                     | DRAM Controller                     |

|   | <b>D</b> 12                            | UART Modules                        |

|   | <b>b</b> 13                            | M-Bus Module                        |

|   | <b>1</b> 3<br><b>1</b> 4<br><b>1</b> 5 | Timer Module                        |

|   | <b>b</b> 15                            | Debug Support                       |

| l | 16                                     | IEEE 1149.1 JTAG                    |

|   | 17                                     | Electrical Characteristics          |

|   | 18                                     | Mechanical Characteristics          |

|   | Α                                      | Appendix A: MCF5206e Memory Map     |

|   | В                                      | Appendix B: Porting from M68000     |

|   |                                        |                                     |

### TABLE OF CONTENTS

Paragraph Number

Title

Page Number

#### Section 1 Introduction

| 1.1      | Background                                | 1-1  |

|----------|-------------------------------------------|------|

| 1.2      | MCF5206e Features                         |      |

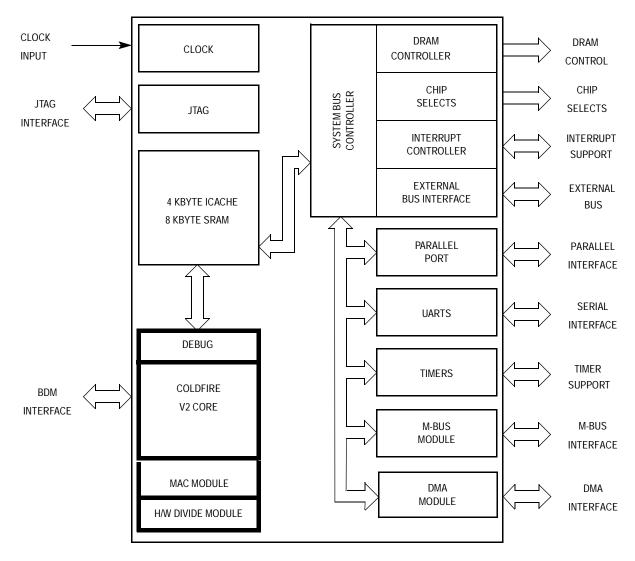

| 1.3      | Functional Blocks                         | 1-4  |

| 1.3.1    | ColdFire Processor Core                   |      |

| 1.3.1.1  | Processor States                          |      |

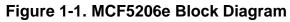

| 1.3.1.2  | Programming Model                         | 1-6  |

| 1.3.1.3  | MAC Registers Summary                     | 1-10 |

| 1.3.1.4  | Addressing Capabilities Summary           | 1-10 |

| 1.3.1.5  | Instruction Set Overview                  | 1-10 |

| 1.3.2    | MAC Module                                | 1-15 |

| 1.3.3    | Hardware Divide Module                    | 1-15 |

| 1.3.4    | Instruction Cache                         | 1-15 |

| 1.3.5    | Internal SRAM                             | 1-15 |

| 1.3.6    | DRAM Controller                           | 1-16 |

| 1.3.7    | Direct Memory Access (DMA)                | 1-16 |

| 1.3.8    | UART Modules                              | 1-16 |

| 1.3.9    | Timer Module                              | 1-16 |

| 1.3.10   | Motorola Bus (M-Bus) Module               | 1-16 |

| 1.3.11   | System Interface                          | 1-17 |

| 1.3.11.1 | External Bus Interface                    | 1-17 |

| 1.3.11.2 | Chip Selects                              | 1-17 |

| 1.3.12   | 8-Bit Parallel Port (General Purpose I/O) | 1-17 |

| 1.3.13   | Interrupt Controller                      | 1-17 |

| 1.3.14   | System Protection                         | 1-18 |

| 1.3.15   | JTAG                                      | 1-18 |

| 1.3.16   | System Debug Interface                    | 1-18 |

| 1.3.17   | Pinout and Package                        | 1-18 |

#### Section 2 Signal Description

| 2.1   | Introduction                             | 2-1 |

|-------|------------------------------------------|-----|

| 2.2   | Address Bus                              | 2-3 |

| 2.2.1 | Address Bus (A[27:24]/ CS[7:4]/ WE[0:3]) | 2-4 |

| 2.2.2 | Address Bus (A[23:0])                    | 2-4 |

| 2.2.3 | Data Bus (D[31:0])                       |     |

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                           | Page<br>Number |

|---------------------|-------------------------------------------------|----------------|

| 2.3                 | Chip Selects                                    | 2-4            |

| 2.3.1               | Chip Selects (A[27:24]/ CS[7:4]/ WE[0:3])       | 2-5            |

| 2.3.2               | Chip Selects (CS[3:0])                          |                |

| 2.3.3               | Byte Write Enables (A[27:24]/ CS[7:4]/ WE[0:3]) |                |

| 2.4                 | Interrupt control signals                       |                |

| 2.4.1               | Interrupt Priority Level/ Interrupt Request     |                |

| 2.5                 | Bus Control Signals                             |                |

| 2.5.1               | Read/Write (R/W) Signal                         |                |

| 2.5.2               | Size (SIZ[1:0])                                 |                |

| 2.5.3               | Transfer Type (TT[1:0])                         |                |

| 2.5.4               | Access Type and Mode (ATM)                      |                |

| 2.5.5               | Transfer Start (TS)                             |                |

| 2.5.6               | Transfer Acknowledge (TA)                       |                |

| 2.5.7               | Asynchronous Transfer Acknowledge (ATA)         |                |

| 2.5.8               | Transfer Error Acknowledge (TEA)                |                |

| 2.6                 | Bus Arbitration Signals                         |                |

| 2.6.1               | Bus Request (BR)                                |                |

| 2.6.2<br>2.6.3      | Bus Grant (BG)                                  |                |

| 2.0.3               | Bus Driven (BD)                                 |                |

| 2.7.1               | Clock and Reset Signals                         |                |

| 2.7.2               | Clock Input (CLK)<br>Reset (RSTI)               |                |

| 2.7.3               | Reset Out (RTS[2]/RSTO)                         |                |

| 2.8                 | DRAM Controller Signals                         |                |

| 2.8.1               | Row Address Strobes (RAS[1:0])                  |                |

| 2.8.2               | Column Address Strobes (CAS[3:0])               |                |

| 2.8.3               | DRAM Write (DRAMW)                              |                |

| 2.9                 | UART Module Signals                             |                |

| 2.9.1               | Receive Data (RxD[1], RxD[2])                   |                |

| 2.9.2               | Transmit Data (TxD[1], TxD[2])                  |                |

| 2.9.3               | Request To Send (RTS[1], RTS[2]/RSTO)           |                |

| 2.9.4               | Clear To Send (CTS[1], CTS[2])                  |                |

| 2.10                | Timer Module Signals                            | 2-15           |

| 2.10.1              | Timer Input (TIN[2], TIN[1])                    | 2-15           |

| 2.10.2              | Timer Output (TOUT[2], TOUT[1])                 |                |

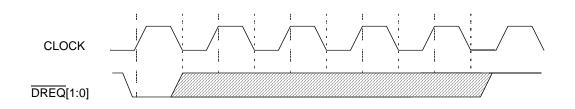

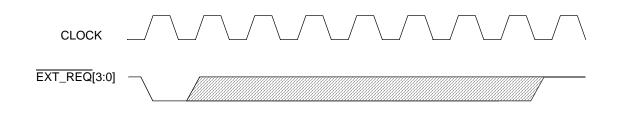

| 2.11                | DMA Module Signals                              |                |

| 2.11.1              | DMA Request (DREQ[0], DREQ[1])                  |                |

| 2.12                | M-Bus Module Signals                            | 2-16           |

| 2.12.1              | M-Bus Serial Clock (SCL)                        | 2-16           |

| 2.12.2              | M-Bus Serial Data (SDA)                         | 2-16           |

| 2.13                | General Purpose I/O Signals                     | 2-16           |

| 2.13.1              | General Purpose I/O (PP[7:4]/PST[3:0])          | 2-16           |

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                                      | Page<br>Number |

|---------------------|------------------------------------------------------------|----------------|

| 2.13.2              | Parallel Port (General-Purpose I/O) (PP[3:0]/DDATA[3:0]) . | 2-16           |

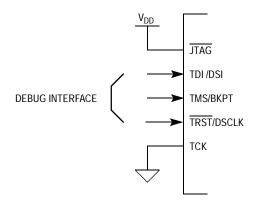

| 2.14                | Debug Support Signals                                      | 2-16           |

| 2.14.1              | Processor Status (PP[7:4]/PST[3:0])                        |                |

| 2.14.2              | Debug Data (PP[3:0]/DDATA[3:0])                            |                |

| 2.14.3              | Development Serial Clock (TRST/DSCLK)                      |                |

| 2.14.4              | Break Point (TMS/BKPT)                                     |                |

| 2.14.5              | Development Serial Input (TDI/DSI)                         |                |

| 2.14.6              | Development Serial Output (TDO/DSO)                        |                |

| 2.15                | JTAG Signals                                               |                |

| 2.15.1              | Test Clock (TCK)                                           |                |

| 2.15.2              | Test Reset (TRST/DSCLK)                                    | 2-18           |

| 2.15.3              | Test Mode Select (TMS/BKPT)                                |                |

| 2.15.4              | Test Data Input (TDI/DSI)                                  | 2-19           |

| 2.15.5              | Test Data Output (TDO/DSO)                                 | 2-19           |

| 2.16                | Test Signals                                               | 2-20           |

| 2.16.1              | Motorola Test Mode (MTMOD)                                 | 2-20           |

| 2.16.2              | High Impedance (HIZ)                                       | 2-20           |

| 2.17                | Signal Summary                                             | 2-20           |

#### Section 3 ColdFire Core

| 3.1     | Processor Pipelines              | 3-1 |

|---------|----------------------------------|-----|

| 3.2     | Processor Register Description   |     |

| 3.2.1   | User Programming Model           | 3-2 |

| 3.2.1.1 | Data Registers (D0–D7)           | 3-2 |

| 3.2.1.2 | Address Registers (A0–A6)        | 3-2 |

| 3.2.1.3 | Stack Pointer (A7)               | 3-2 |

| 3.2.1.4 | Program Counter                  |     |

| 3.2.1.5 | Condition Code Register          |     |

| 3.2.2   | MAC Unit User Programming Model  | 3-4 |

| 3.2.3   | Hardware Divide Module           | 3-4 |

| 3.2.4   | Supervisor Programming Model     | 3-4 |

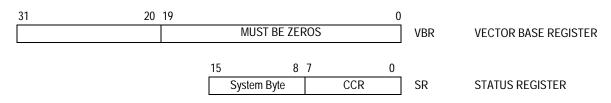

| 3.2.4.1 | Status Register                  |     |

| 3.2.4.2 | Vector Base Register (VBR)       | 3-5 |

| 3.3     | Exception Processing Overview    |     |

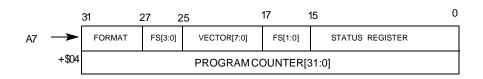

| 3.4     | Exception Stack Frame Definition |     |

| 3.5     | Processor Exceptions             | 3-8 |

| 3.5.1   | Access Error Exception           |     |

| 3.5.2   | Address Error Exception          |     |

| 3.5.3   | Illegal Instruction Exception    |     |

| 3.5.4   | Privilege Violation              |     |

|         | 5                                |     |

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                          | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

| 3.5.5<br>3.5.6      | Trace Exception<br>Debug Interrupt             |                |

| 3.5.7               | RTE and Format Error Exceptions                |                |

| 3.5.8               | TRAP Instruction Exceptions                    |                |

| 3.5.9               | Interrupt Exception                            |                |

| 3.5.10              | Fault-on-Fault Halt                            |                |

| 3.5.11              | Reset Exception                                |                |

| 3.6                 | Instruction Execution Timing                   |                |

| 3.6.1               | Timing Assumptions                             |                |

| 3.6.2               | MOVE Instruction Execution Times               | 3-12           |

|                     | Section 4<br>Instruction Cache                 |                |

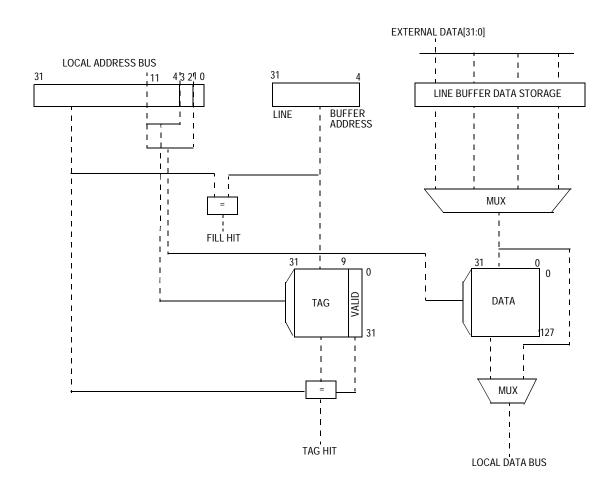

| 4.1                 | Features of Instruction Cache                  |                |

| 4.2                 | Instruction Cache Physical Organization        |                |

| 4.3                 | Instruction Cache Operation                    |                |

| 4.3.1               | Interaction With Other Modules                 |                |

| 4.3.2               | Memory Reference Attributes                    |                |

| 4.3.3<br>4.3.4      | Cache Coherency and Invalidation               |                |

| 4.3.4<br>4.3.5      | Reset<br>Cache Miss Fetch Algorithm/Line Fills |                |

| 4.3     | Instruction Cache Operation            |     |

|---------|----------------------------------------|-----|

| 4.3.1   | Interaction With Other Modules         |     |

| 4.3.2   | Memory Reference Attributes            |     |

| 4.3.3   | Cache Coherency and Invalidation       |     |

| 4.3.4   | Reset                                  | 4-4 |

| 4.3.5   | Cache Miss Fetch Algorithm/Line Fills  | 4-4 |

| 4.4     | Instruction Cache Programming Model    |     |

| 4.4.1   | Instruction Cache Registers Memory Map |     |

| 4.4.2   | Instruction Cache Register             |     |

| 4.4.2.1 | Cache Control Register (CACR)          |     |

| 4.4.2.2 | Access Control Registers (ACR0, ACR1)  |     |

|         |                                        |     |

#### Section 5 SRAM

| SRAM Features                       | 5-1                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRAM Operation                      | 5-1                                                                                                                                                                                 |

| Programming Model                   | 5-1                                                                                                                                                                                 |

|                                     |                                                                                                                                                                                     |

|                                     |                                                                                                                                                                                     |

| SRAM Base Address Register (RAMBAR) | 5-2                                                                                                                                                                                 |

| SRAM Initialization                 | 5-3                                                                                                                                                                                 |

| Power Management                    | 5-4                                                                                                                                                                                 |

|                                     | SRAM Features<br>SRAM Operation<br>Programming Model<br>SRAM Register Memory Map<br>SRAM Register<br>SRAM Base Address Register (RAMBAR)<br>SRAM Initialization<br>Power Management |

### **TABLE OF CONTENTS (Continued)**

#### Paragraph Number

Title

Page Number

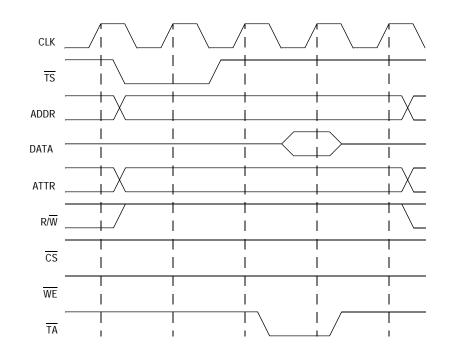

#### Section 6 Bus Operation

| 6.1    | Features                                                       |

|--------|----------------------------------------------------------------|

| 6.2    | Bus and Control Signals                                        |

| 6.2.1  | Address Bus (A[27:0])6-1                                       |

| 6.2.2  | Data Bus (D[31:0])                                             |

| 6.2.3  | Transfer Start (TS)6-2                                         |

| 6.2.4  | Read/Write (R/W)                                               |

| 6.2.5  | Size (SIZ[1:0])                                                |

| 6.2.6  | Transfer Type (TT[1:0])6-3                                     |

| 6.2.7  | Access Type and Mode (ATM)6-3                                  |

| 6.2.8  | Asynchronous Transfer Acknowledge (ATA)6-4                     |

| 6.2.9  | Transfer Acknowledge (TA)6-4                                   |

| 6.2.10 | Transfer Error Acknowledge (TEA)6-5                            |

| 6.3    | Bus Exceptions                                                 |

| 6.3.1  | Double Bus Fault6-5                                            |

| 6.4    | Bus Characteristics                                            |

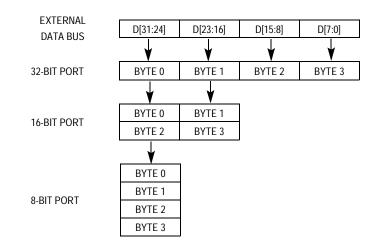

| 6.5    | Data Transfer Mechanism6-6                                     |

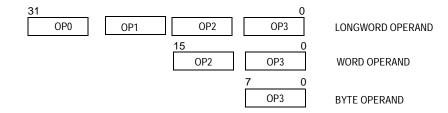

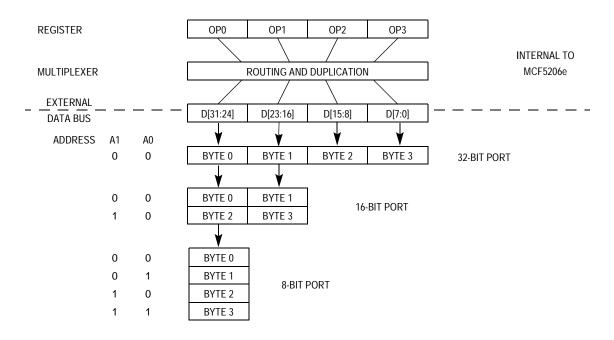

| 6.5.1  | Bus Sizing6-7                                                  |

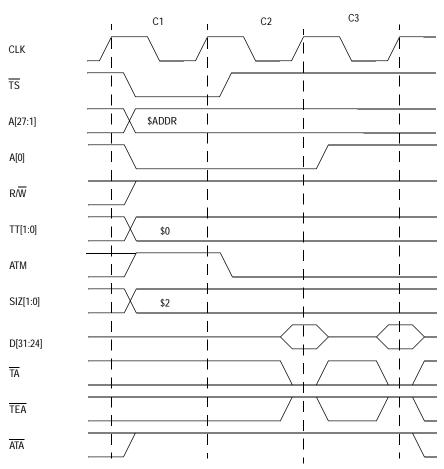

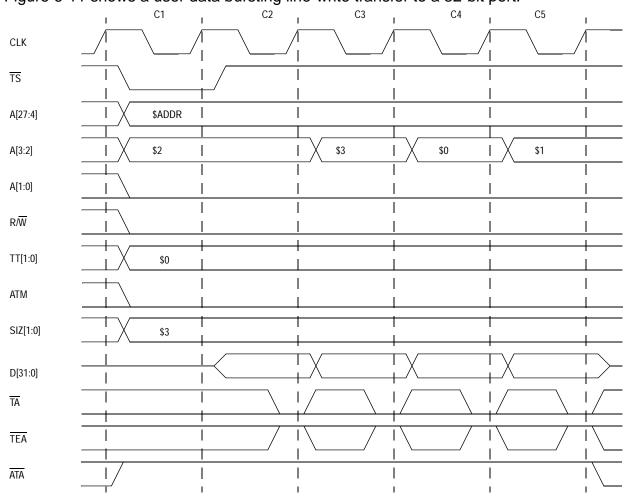

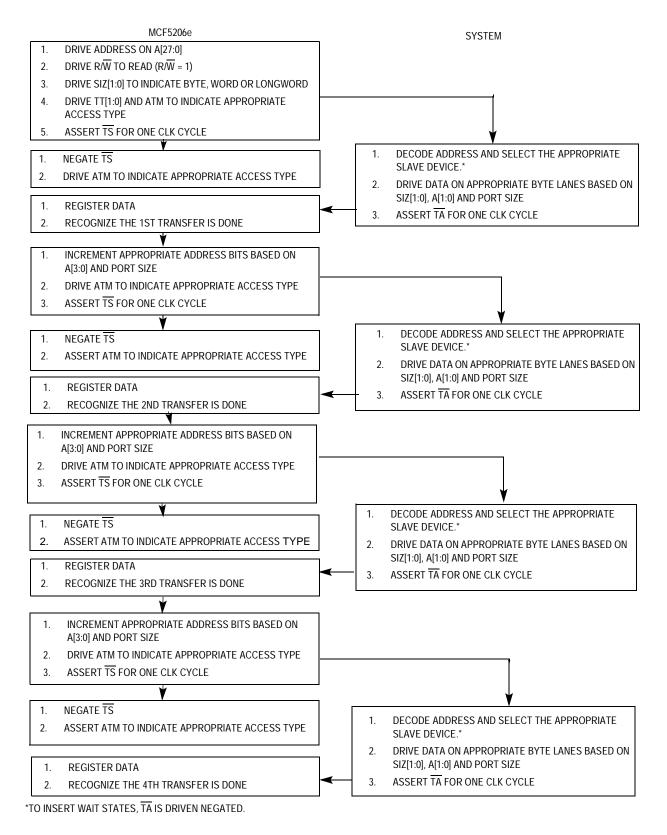

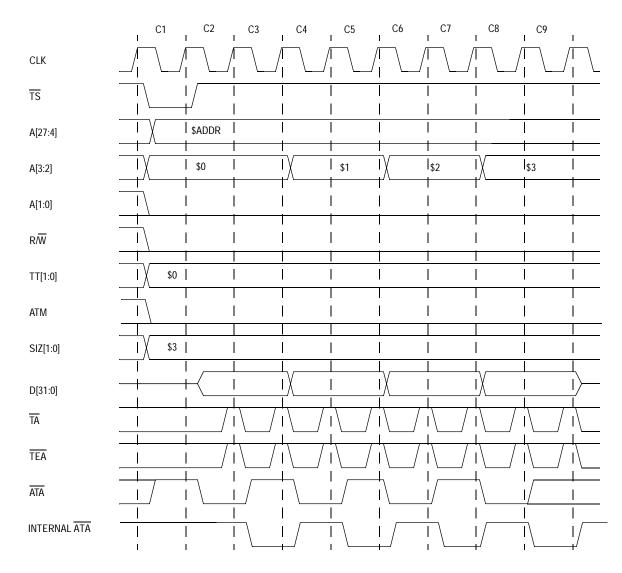

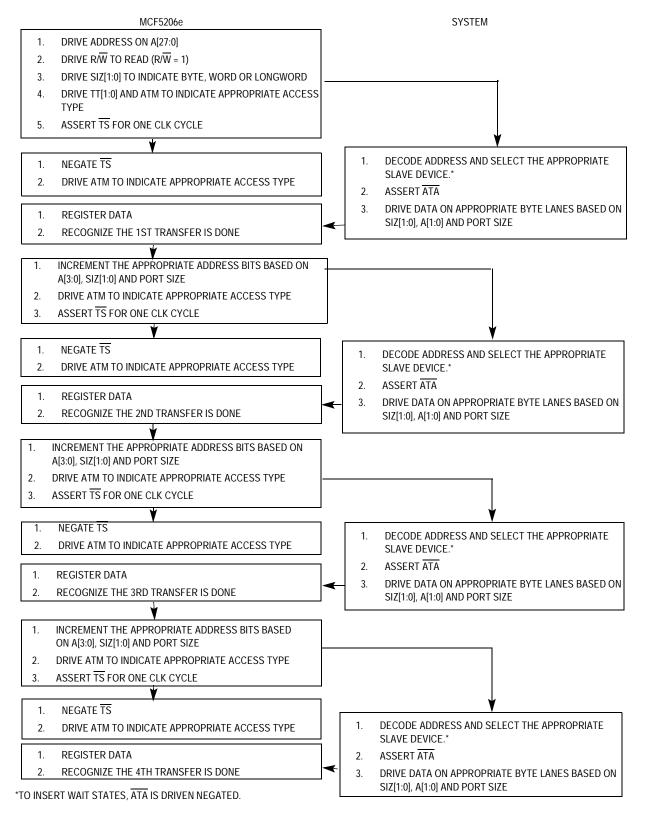

| 6.5.2  | Bursting Read Transfers: Word, Longword, and Line              |

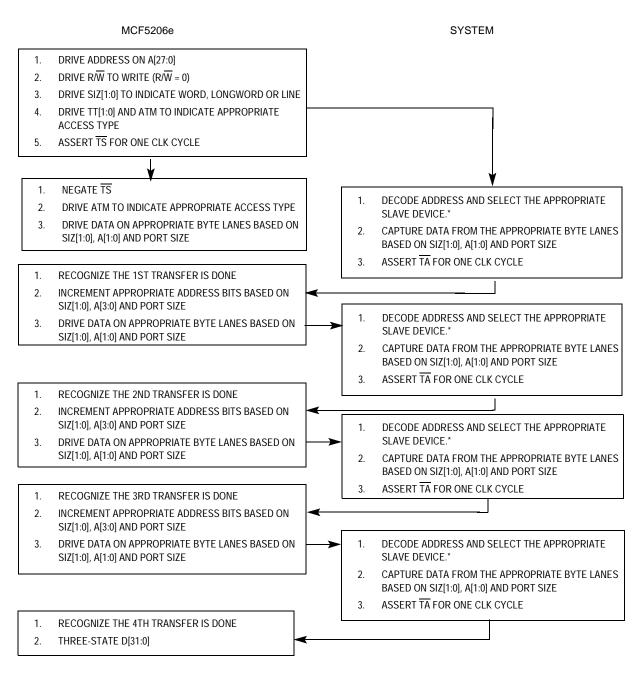

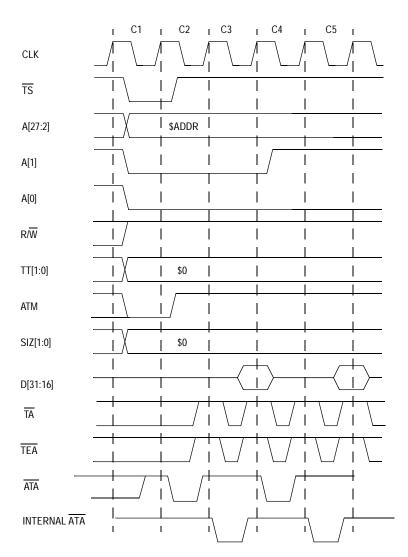

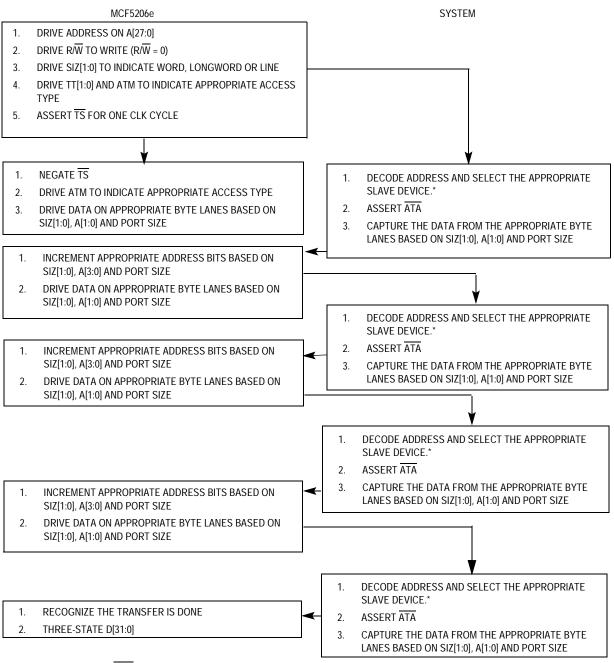

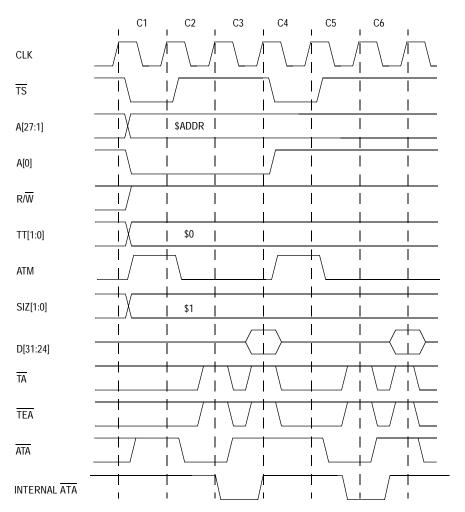

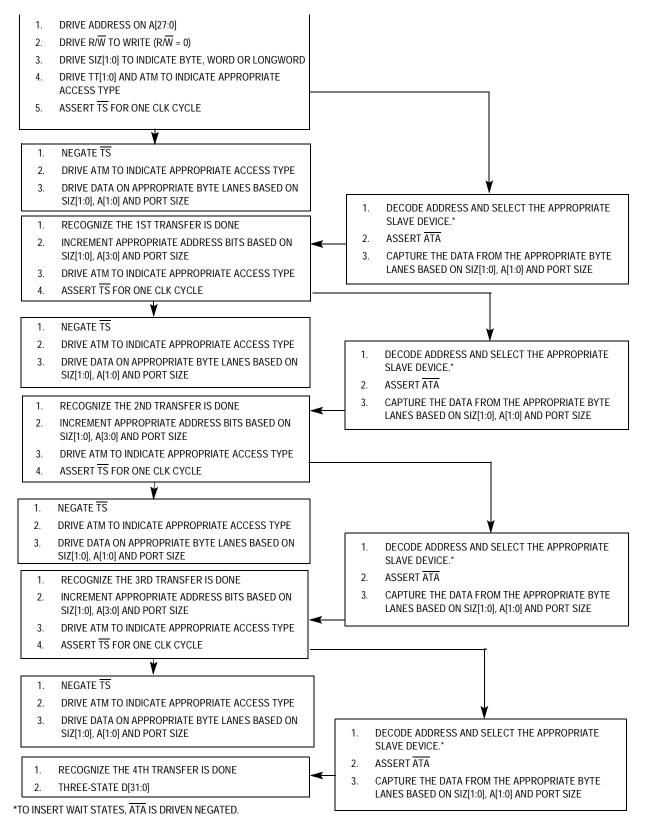

| 6.5.3  | Bursting Write Transfers: Word, Longword, and Line             |

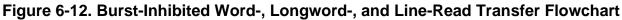

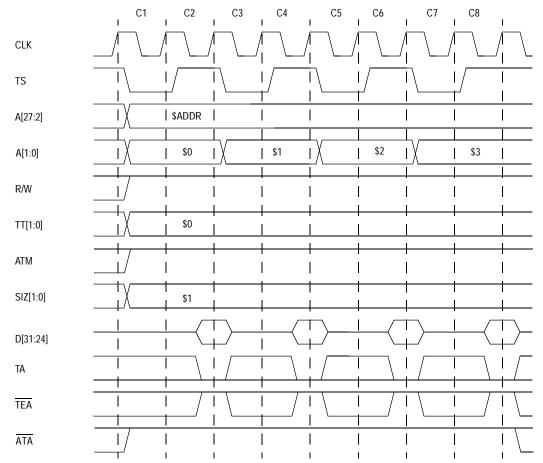

| 6.5.4  | Burst-Inhibited Read Transfer: Word, Longword, and Line6-22    |

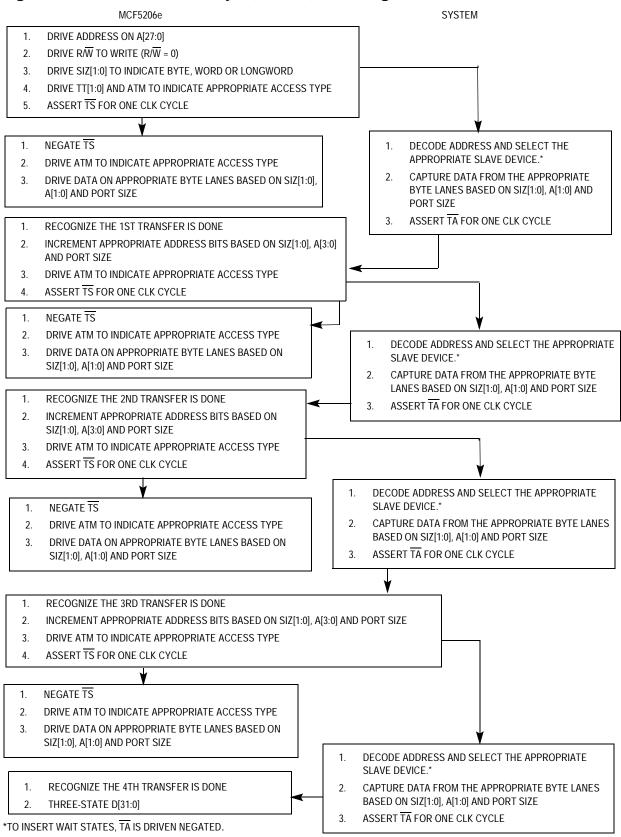

| 6.5.5  | Burst-Inhibited Write Transfer: Word, Longword, and Line6-26   |

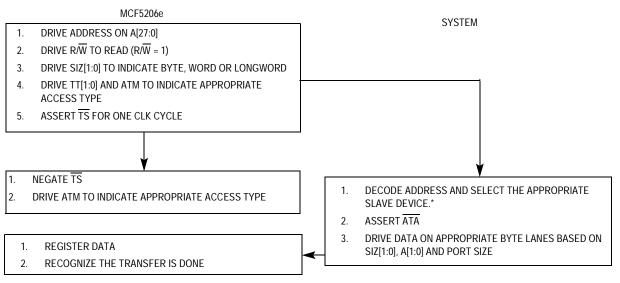

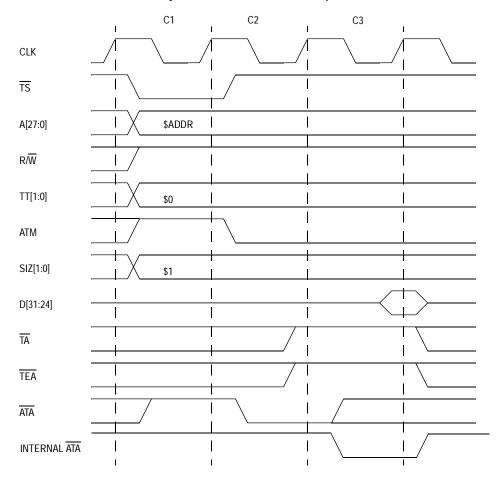

| 6.5.6  | Asynchronous-Acknowledge Read Transfer                         |

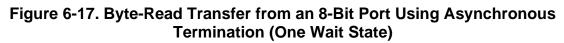

| 6.5.7  | Asynchronous Acknowledge Write Transfer                        |

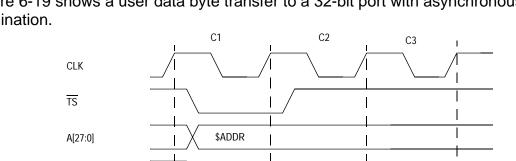

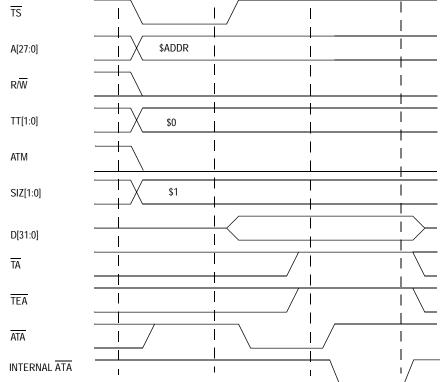

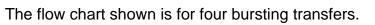

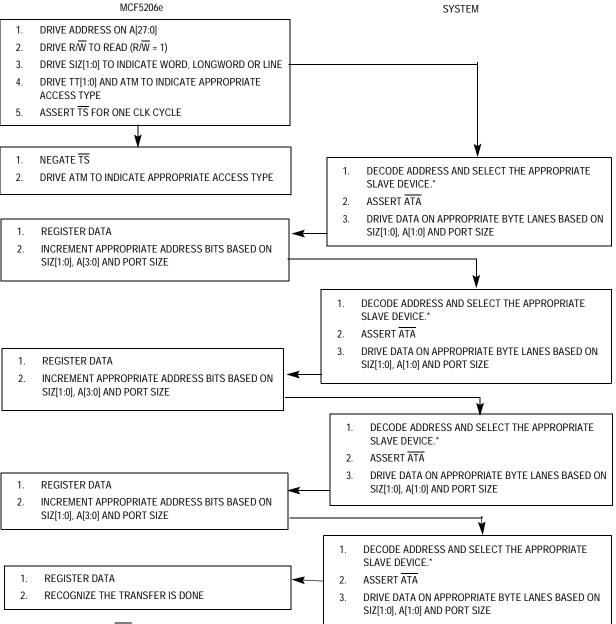

| 6.5.8  | Bursting Read Transfers with Asynchronous Acknowledge 6-34     |

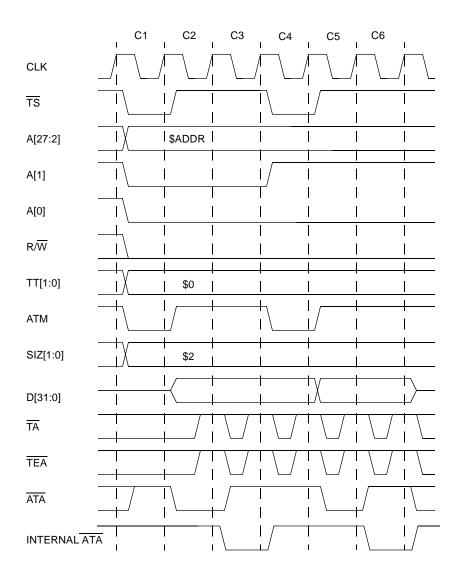

| 6.5.9  | Bursting Write Transfers with Asynchronous Acknowledge 6-37    |

| 6.5.10 | Burst-Inhibited Read Transfers with Asynch. Acknowledge 6-41   |

| 6.5.11 | Burst-Inhibited Write Transfers with Asynch. Acknowledge 6-44  |

| 6.5.12 | Termination Tied to GND6-47                                    |

| 6.6    | Misaligned Operands6-48                                        |

| 6.7    | Acknowledge Cycles6-49                                         |

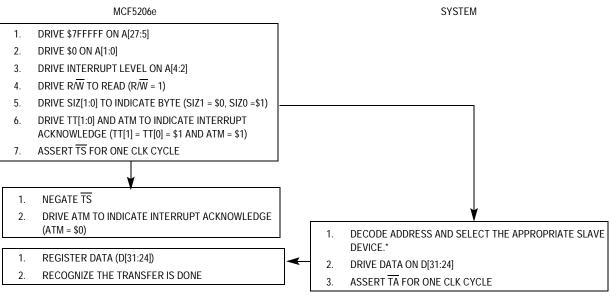

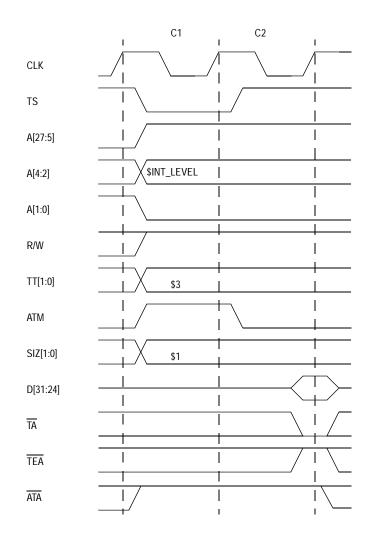

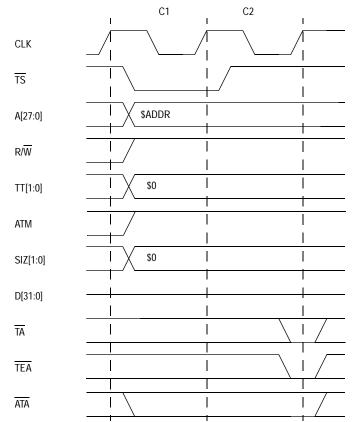

| 6.7.1  | Interrupt Acknowledge Cycle6-50                                |

| 6.8    | Bus Errors                                                     |

| 6.9    | Bus Arbitration6-54                                            |

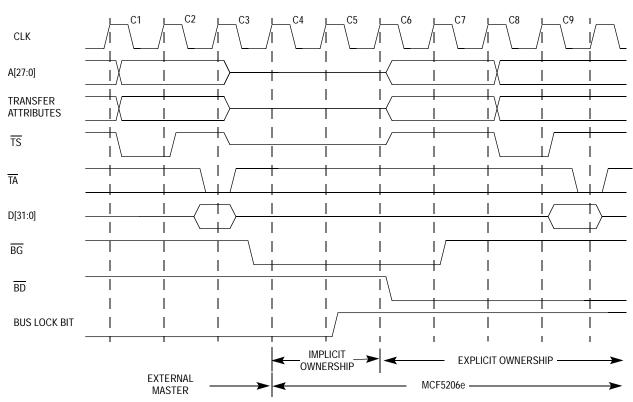

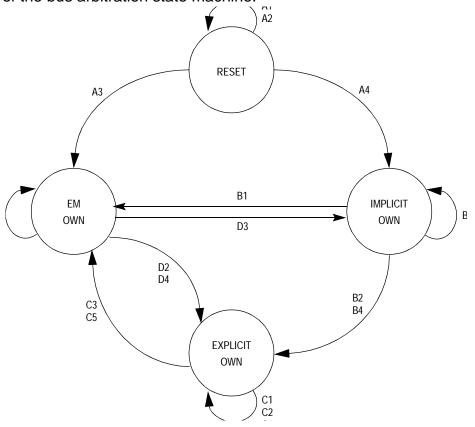

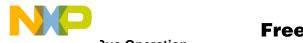

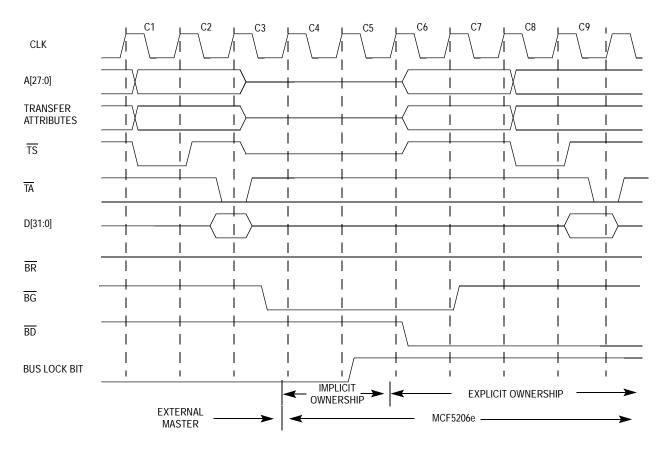

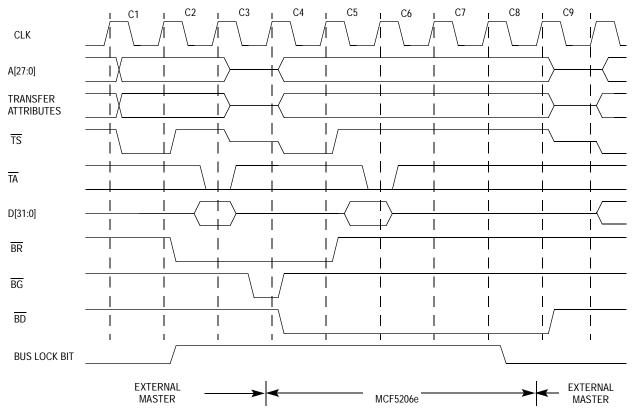

| 6.9.1  | Two Master Bus Arbitration Protocol (Two-Wire Mode)6-54        |

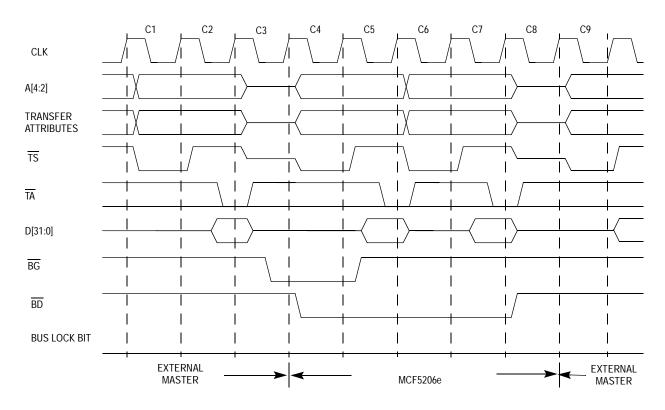

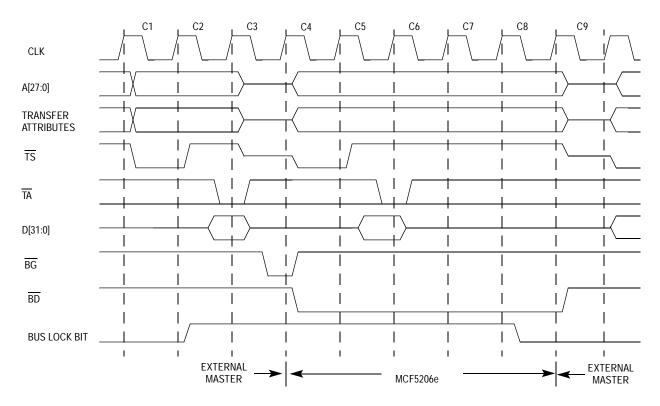

| 6.9.2  | Multiple Bus Master Arbitration Protocol (Three-Wire Mode)6-61 |

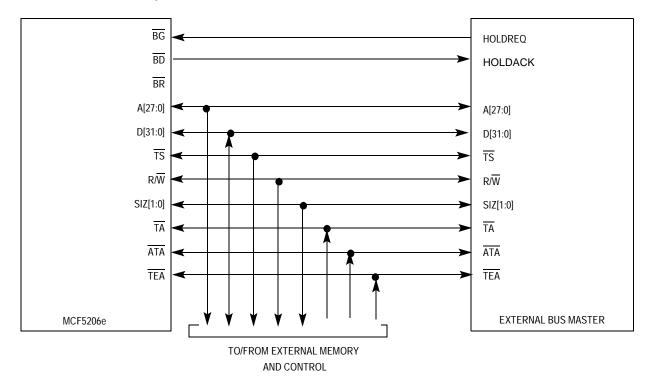

| 6.10   | External Bus Master Operation                                  |

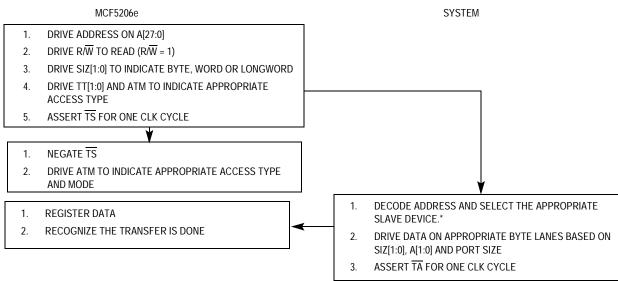

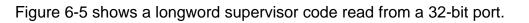

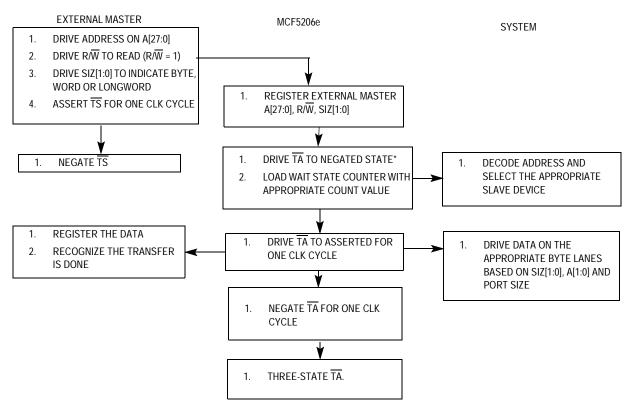

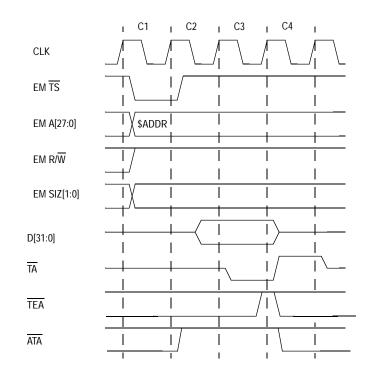

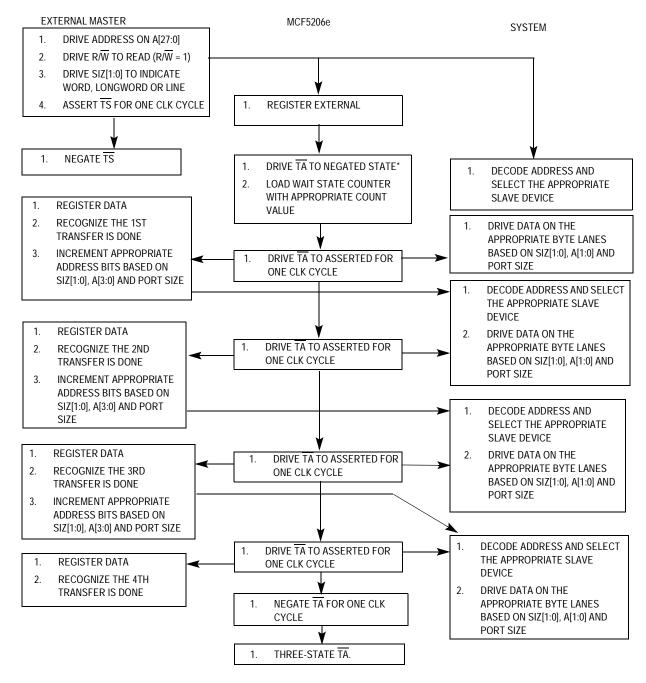

| 6.10.1 | External Master Read Transfer 6-69                             |

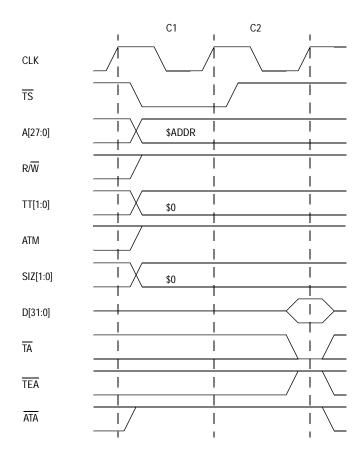

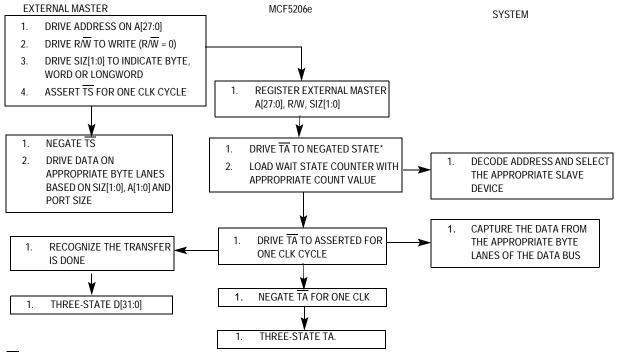

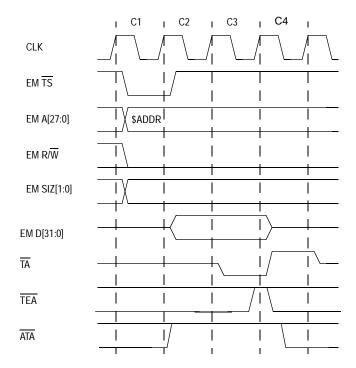

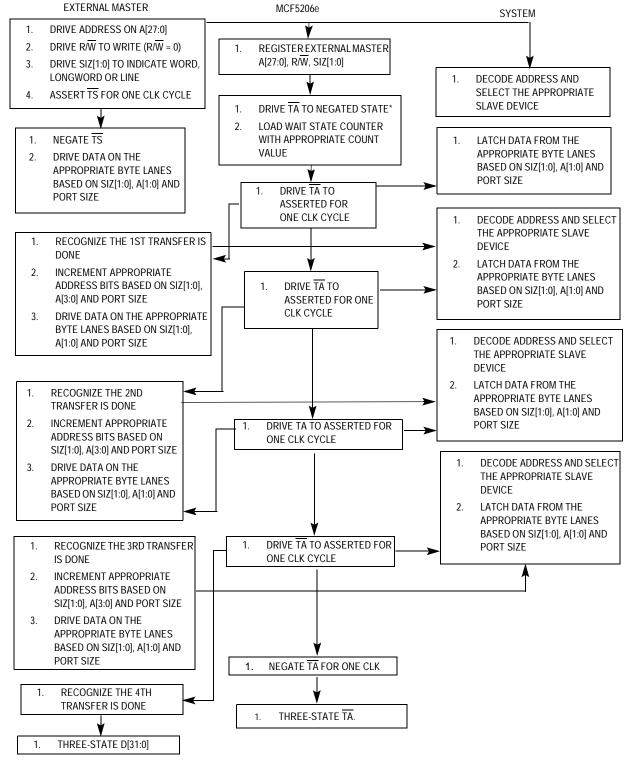

| 6.10.2 | External Master Write Transfer 6-72                            |

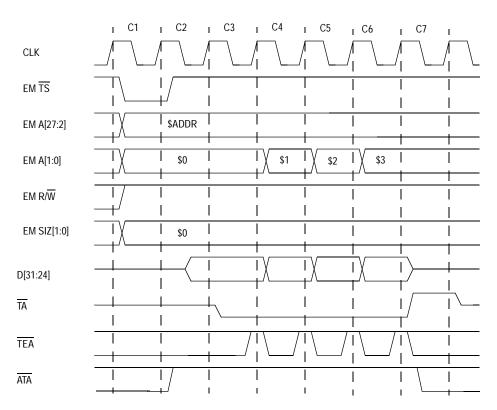

| 6.10.3 | External Master Bursting Read6-74                              |

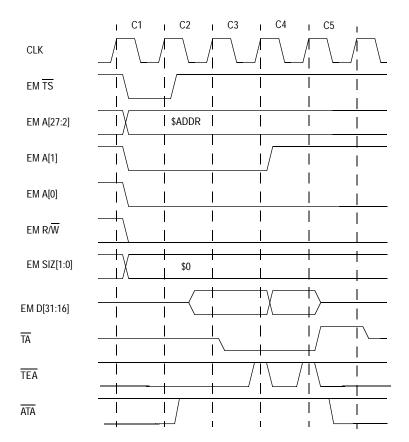

| 6.10.4 | External Master Bursting Write6-77                             |

### **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                   | Page<br>Number |

|---------------------|-----------------------------------------|----------------|

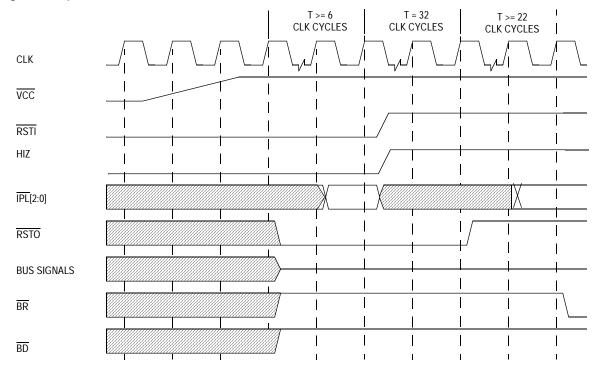

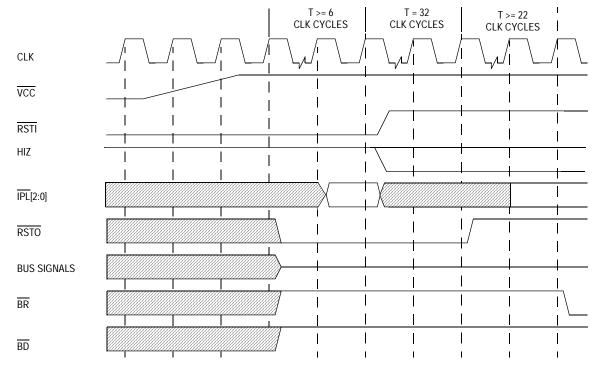

| 6.11                | Reset Operation                         | 6-81           |

| 6.11.1              | Master Reset                            | 6-81           |

| 6.11.2              | Normal reset                            | 6-83           |

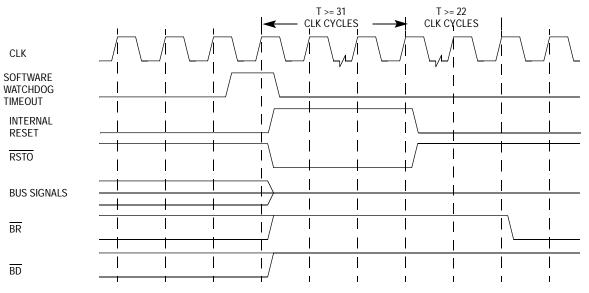

| 6.11.3              | Software Watchdog Timer Reset Operation | 6-84           |

#### Section 7 DMA Controller Module

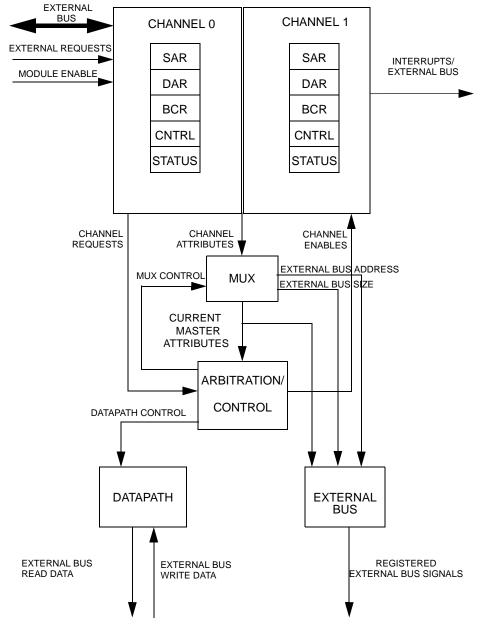

| 7.1     | Introduction                                 | 7-1  |

|---------|----------------------------------------------|------|

| 7.2     | DMA Signal Description                       | 7-3  |

| 7.3     | DMA Module Overview                          |      |

| 7.4     | DMA Controller Module Programming Model      | 7-6  |

| 7.4.1   | Source Address Register (SAR)                |      |

| 7.4.2   | Destination Address Register (DAR)           |      |

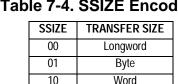

| 7.4.3   | Byte Count Register (BCR)                    |      |

| 7.4.4   | DMA Control Register                         | 7-8  |

| 7.4.5   | DMA Status Register (DSR)                    |      |

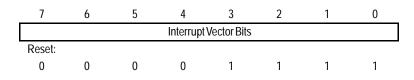

| 7.4.6   | DMA Interrupt Vector Register                |      |

| 7.5     | Transfer Request Generation                  |      |

| 7.5.1   | Cycle Steal Mode                             | 7-12 |

| 7.5.2   | Continuous Mode                              |      |

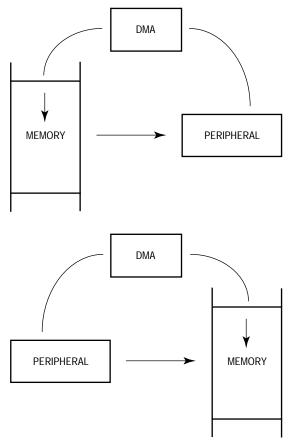

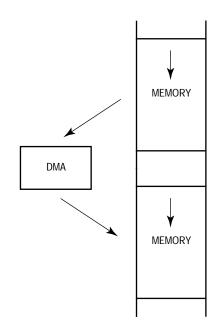

| 7.6     | Data Transfer Modes                          | 7-13 |

| 7.6.1   | Single Address Transactions                  | 7-13 |

| 7.6.2   | Dual Address Transactions                    |      |

| 7.6.2.1 | Dual Address Reads                           | 7-13 |

| 7.6.2.2 | Dual Address Writes                          | 7-13 |

| 7.7     | DMA Controller Module Functional Description | 7-14 |

| 7.7.1   | Channel Initialization and Startup           | 7-14 |

| 7.7.1.1 | Channel Prioritization                       |      |

| 7.7.1.2 | Programming the DMA Controller Module        | 7-14 |

| 7.7.2   | Data Transfers                               | 7-15 |

| 7.7.2.1 | External DMA Request Operation               | 7-15 |

| 7.7.2.2 | Auto-Alignment                               | 7-16 |

| 7.7.2.3 | BandWidth Control                            | 7-17 |

| 7.7.3   | Channel Termination                          | 7-17 |

| 7.7.3.1 | Error Conditions                             |      |

| 7.7.3.2 | Interrupts                                   | 7-17 |

#### Section 8

#### **System Integration Module**

| 8.1 | Introduction | 8- | 1 |

|-----|--------------|----|---|

|-----|--------------|----|---|

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Page<br>Title Number                                     |

|---------------------|----------------------------------------------------------|

| 8.1.1               | Features8-1                                              |

| 8.2                 | SIM Operation8-1                                         |

| 8.2.1               | Module Base Address Register (MBAR)8-1                   |

| 8.2.2               | Bus Timeout Monitor8-2                                   |

| 8.2.3               | Spurious Interrupt Monitor8-2                            |

| 8.2.4               | Software Watchdog Timer8-3                               |

| 8.2.5               | Interrupt Controller8-3                                  |

| 8.3                 | Programming Model8-6                                     |

| 8.3.1               | SIM Registers Memory Map8-6                              |

| 8.3.2               | SIM Registers8-7                                         |

| 8.3.2.1             | Module Base Address Register (MBAR)8-7                   |

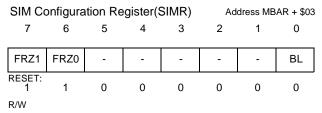

| 8.3.2.2             | SIM Configuration Register (SIMR)8-8                     |

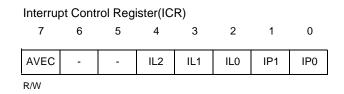

| 8.3.2.3             | Interrupt Control Register (ICR)                         |

| 8.3.2.4             | Interrupt Mask Register (IMR)8-11                        |

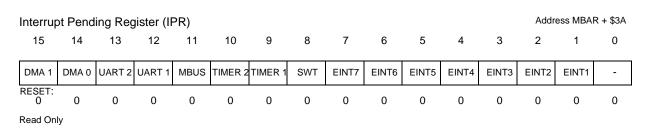

| 8.3.2.5             | Interrupt Pending Register (IPR)8-12                     |

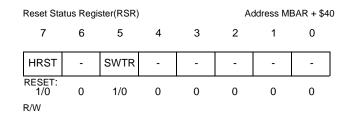

| 8.3.2.6             | Reset Status Register (RSR)8-13                          |

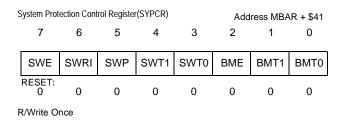

| 8.3.2.7             | System Protection Control Register (SYPCR)               |

| 8.3.2.8             | Software Watchdog Interrupt Vector Register (SWIVR) 8-15 |

| 8.3.2.9             | Software Watchdog Service Register (SWSR)                |

| 8.3.2.10            | Pin Assignment Register (PAR)8-16                        |

| 8.4                 | Bus Arbitration Control                                  |

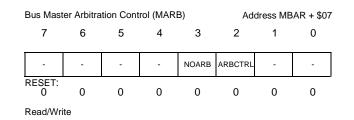

| 8.4.1               | Bus Master Arbitration Control (MARB)8-18                |

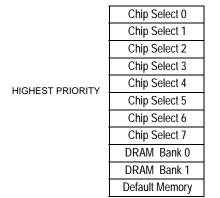

#### Section 9 Chip-Select Module

| 9.1     | Introduction                     | 9-1 |

|---------|----------------------------------|-----|

| 9.1.1   | Features                         | 9-1 |

| 9.2     | Chip Select Module I/O           | 9-1 |

| 9.2.1   | Control Signals                  |     |

| 9.2.1.1 | Chip Select (CS[7:0])            |     |

| 9.2.1.2 | Write Enable (WE[3:0])           |     |

| 9.2.1.3 | Address Bus                      |     |

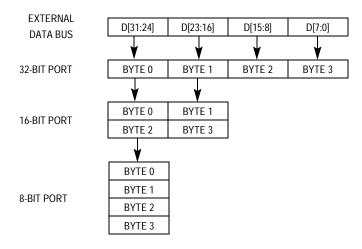

| 9.2.1.4 | Data Bus                         | 9-4 |

| 9.2.1.5 | Transfer acknowledge (TA)        | 9-4 |

| 9.3     | Chip Select Operation            |     |

| 9.3.1   | Chip Select Bank Definition      |     |

| 9.3.1.1 | Base Address and Address masking |     |

| 9.3.1.2 | Access Permissions               |     |

| 9.3.1.3 | Control Features                 | 9-6 |

| 9.3.2   | Global Chip Select Operation     | 9-8 |

| 9.3.3   | General Chip Select Operation    |     |

|         |                                  |     |

## **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

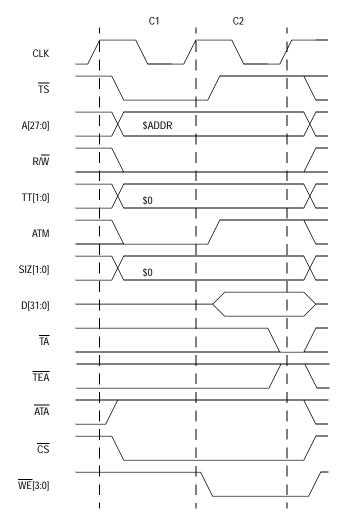

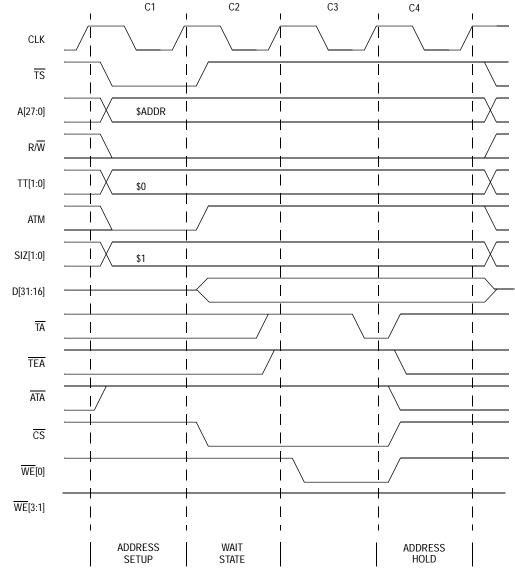

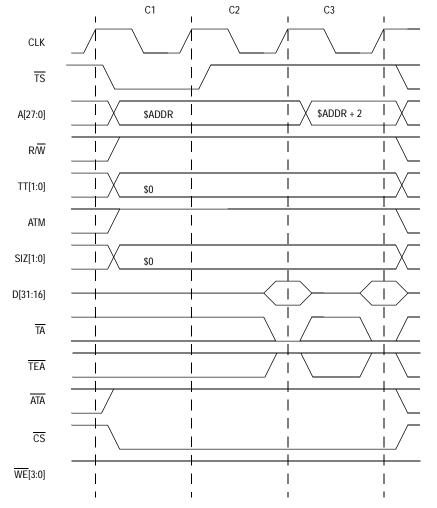

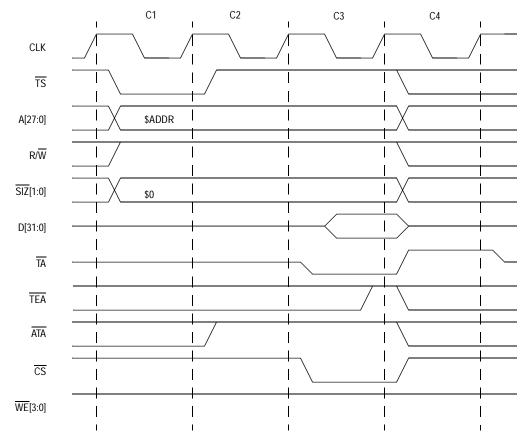

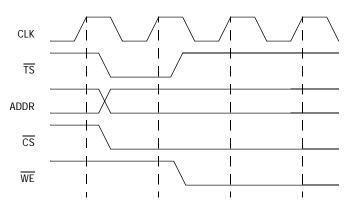

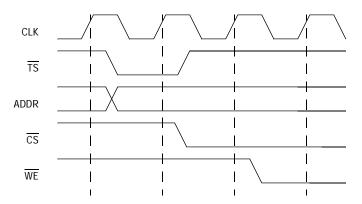

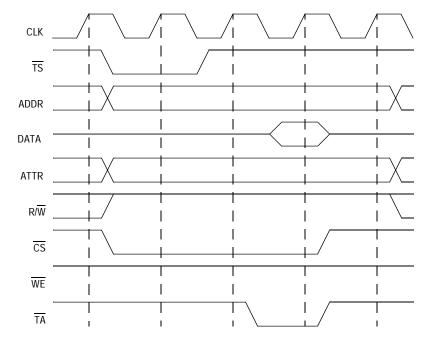

| 9.3.3.1             | Nonburst Transfer with no Address Setup or Hold    | 9-9            |

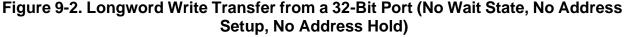

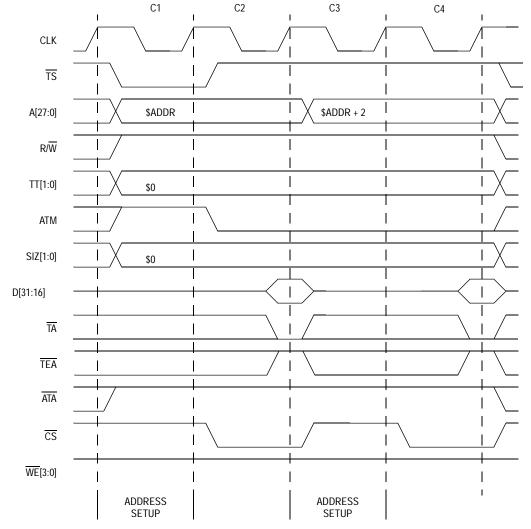

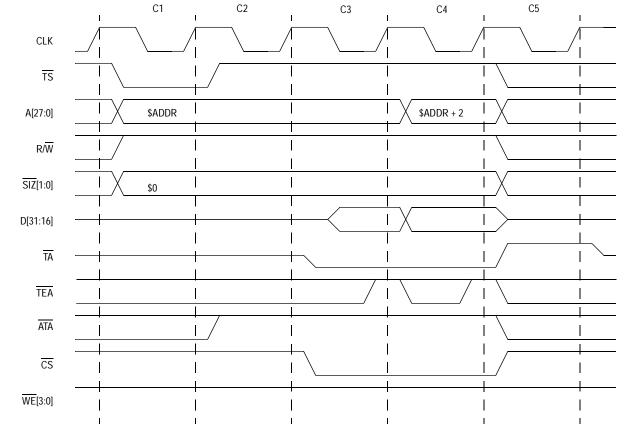

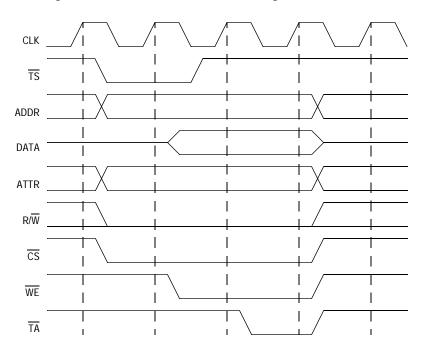

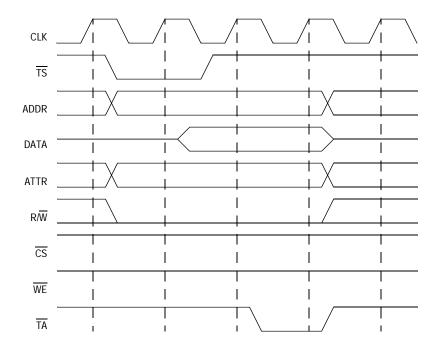

| 9.3.3.2             | Nonburst Transfer With Address Setup               | 9-10           |

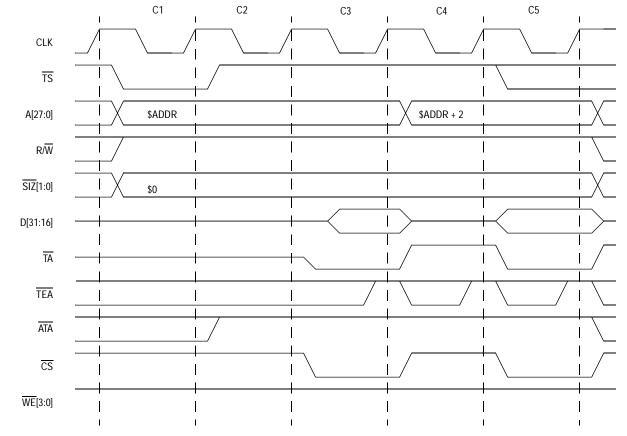

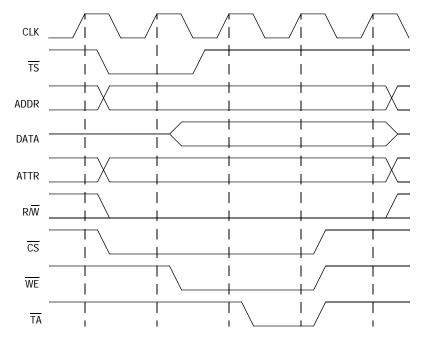

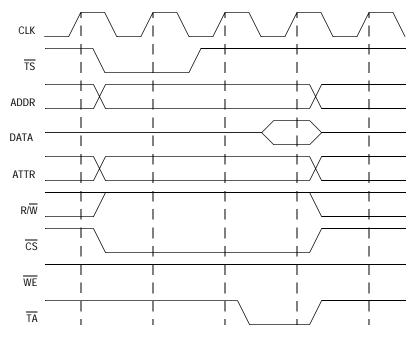

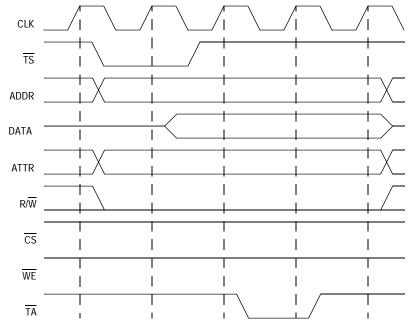

| 9.3.3.3             | Nonburst Transfer With Address Setup and Hold      | 9-11           |

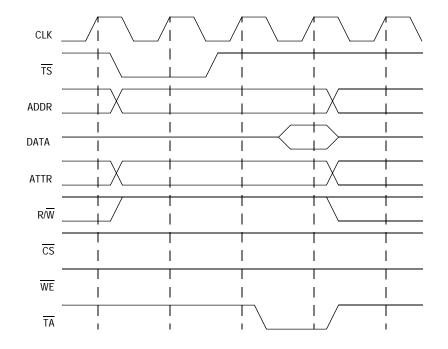

| 9.3.3.4             | Burst Transfer and Chip Selects                    | 9-13           |

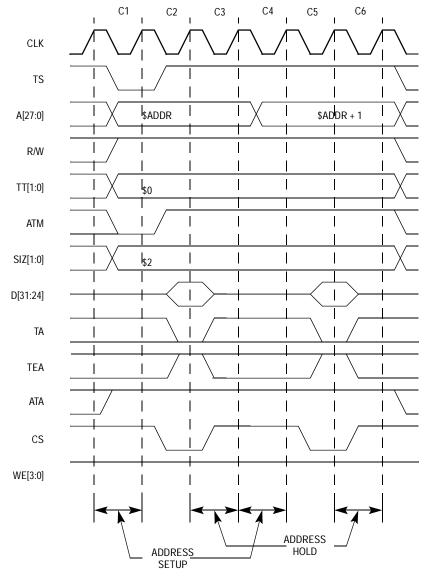

| 9.3.3.5             | Burst Transfer With Address Setup                  | 9-15           |

| 9.3.3.6             | Burst Transfer With Address Setup and Hold         | 9-17           |

| 9.3.4               | External Master Chip Select Operation              | 9-20           |

| 9.3.4.1             | External Master Nonburst Transfer                  | 9-20           |

| 9.3.4.2             | External Master Burst Transfer                     | 9-22           |

| 9.3.4.3             | External Master Burst Transfer with Setup and Hold | 9-24           |

| 9.4                 | Programming Model                                  | 9-26           |

| 9.4.1               | Chip Select Registers Memory Map                   |                |

| 9.4.2               | Chip Select Controller Registers                   |                |

| 9.4.2.1             | Chip Select Address Register (CSAR0 - CSAR7)       | 9-28           |

| 9.4.2.2             | Chip Select Mask Register (CSMR0 - CSMR7)          | 9-29           |

| 9.4.2.3             | Chip Select Control Register (CSCR0 - CSCR7)       | 9-31           |

| 9.4.2.4             | Default Memory Control Register (DMCR)             | 9-38           |

#### Section 10 Parallel Port (General Purpose I/O Module)

| 10.1     | Introduction                           |  |

|----------|----------------------------------------|--|

| 10.2     | Parallel Port Operation                |  |

| 10.3     | Programming Model                      |  |

| 10.3.1   | Parallel Port Registers Memory Map     |  |

| 10.3.2   | Parallel Port Registers                |  |

| 10.3.2.1 | Port A Data Direction Register (PADDR) |  |

| 10.3.2.2 | Port A Data Register (PADAT)           |  |

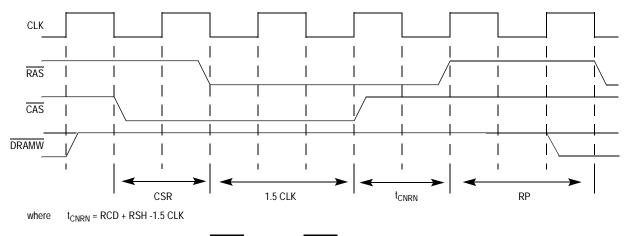

#### Section 11 DRAM Controller

| 11.1     | Introduction                         |      |

|----------|--------------------------------------|------|

| 11.1.1   | Features                             |      |

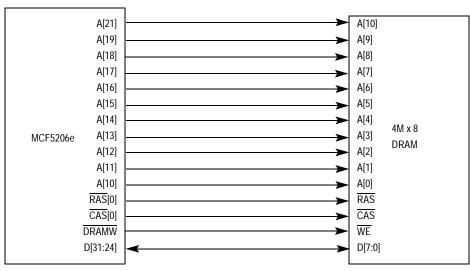

| 11.2     | DRAM Controller I/O                  | 11-1 |

| 11.2.1   | Control Signals                      | 11-1 |

| 11.2.1.1 | Row Address Strobes (RAS[0], RAS[1]) | 11-1 |

| 11.2.1.2 | Column Address Strobes(CAS[0:3])     | 11-2 |

| 11.2.1.3 | DRAM Write (DRAMW)                   | 11-3 |

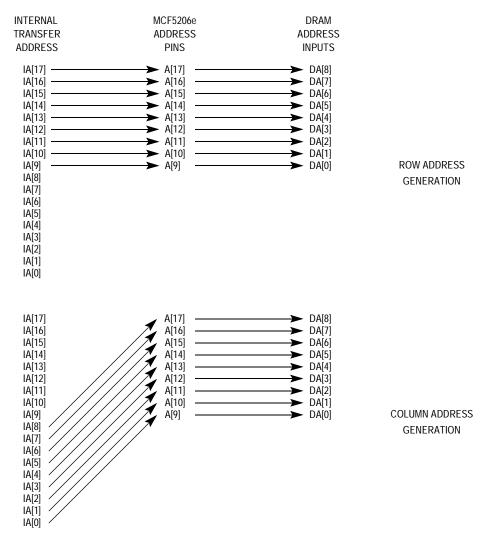

| 11.2.2   | Address Bus                          | 11-3 |

| 11.2.3   | Data Bus                             | 11-4 |

| 11.3     | DRAM Controller Operation            | 11-4 |

|          |                                      |      |

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Page<br>Title Number                                   |  |

|---------------------|--------------------------------------------------------|--|

| 11.3.1              | Reset Operation11-4                                    |  |

| 11.3.1.1            | Master Reset11-5                                       |  |

| 11.3.1.2            | Normal Reset11-5                                       |  |

| 11.3.2              | Definition of DRAM Banks11-5                           |  |

| 11.3.2.1            | Base Address and Address Masking                       |  |

| 11.3.2.2            | Access Permissions11-7                                 |  |

| 11.3.2.3            | Timing11-8                                             |  |

| 11.3.2.4            | Page Mode11-8                                          |  |

| 11.3.2.5            | Port Size/Page Size11-8                                |  |

| 11.3.2.6            | Address Multiplexing11-8                               |  |

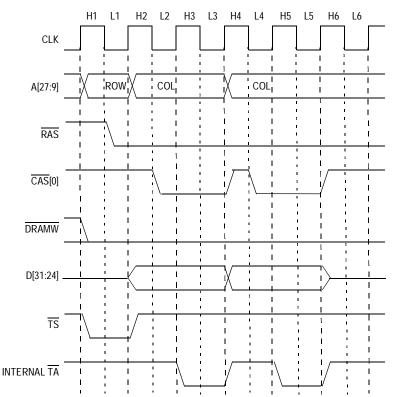

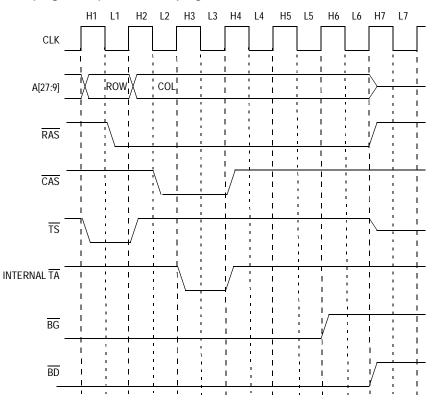

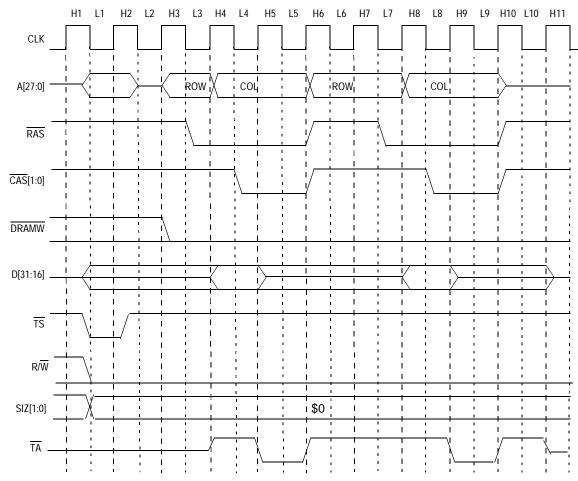

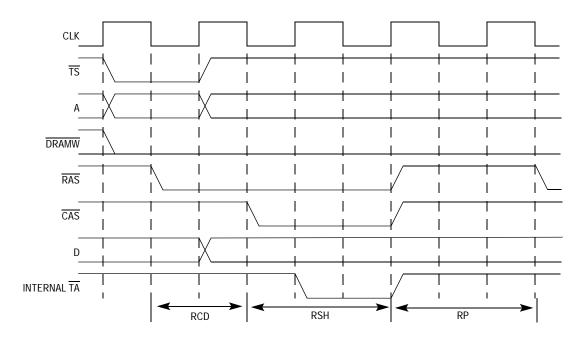

| 11.3.3              | Normal Mode Operation11-15                             |  |

| 11.3.3.1            | Nonburst Transfer In Normal Mode                       |  |

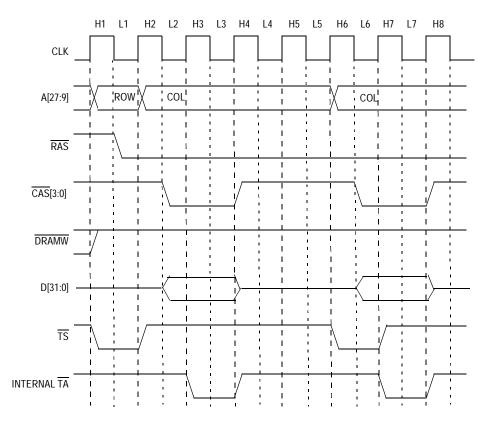

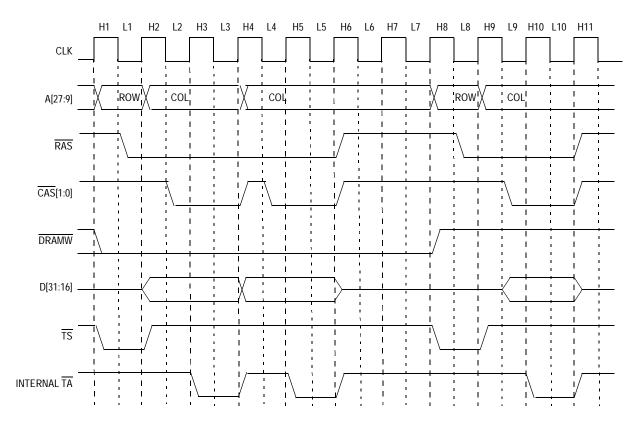

| 11.3.3.2            | Burst Transfer In Normal Mode                          |  |

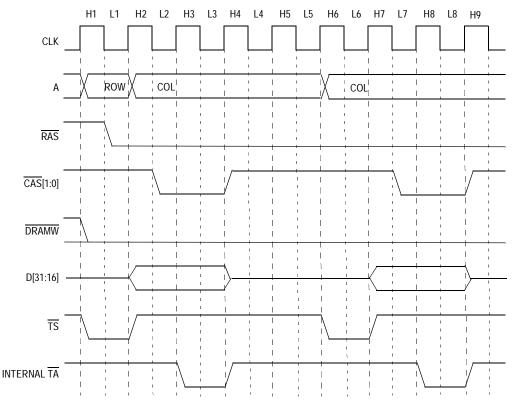

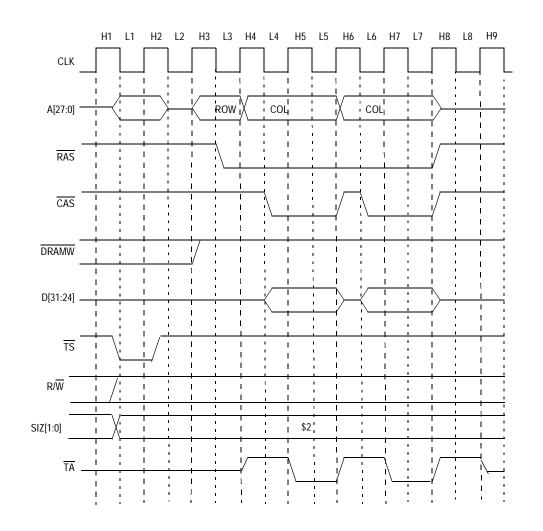

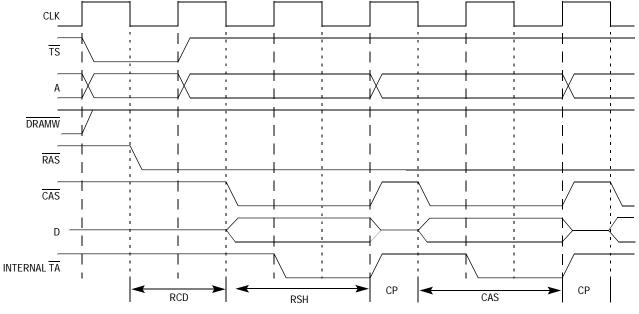

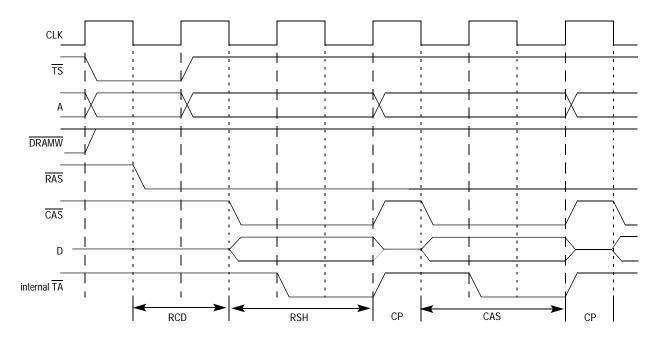

| 11.3.4              | Fast Page Mode Operation11-21                          |  |

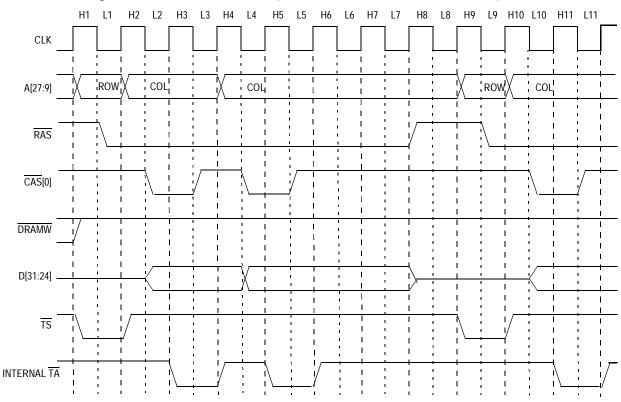

| 11.3.4.1            | Burst Transfer In Fast Page Mode                       |  |

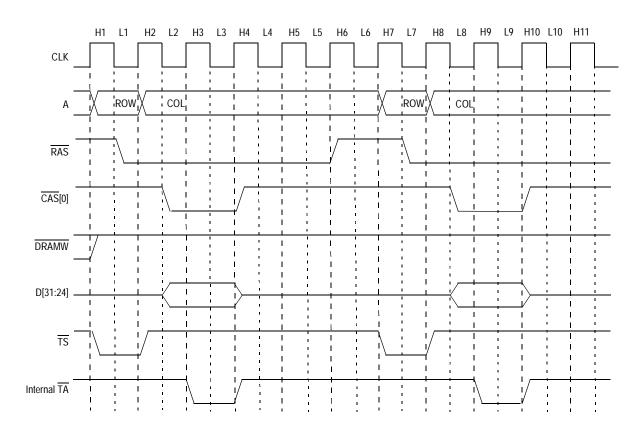

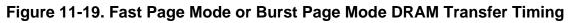

| 11.3.4.2            | Page Hit Read Transfer In Fast Page Mode11-23          |  |

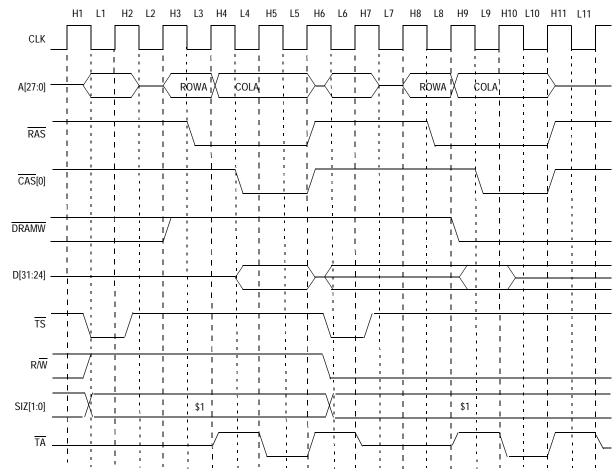

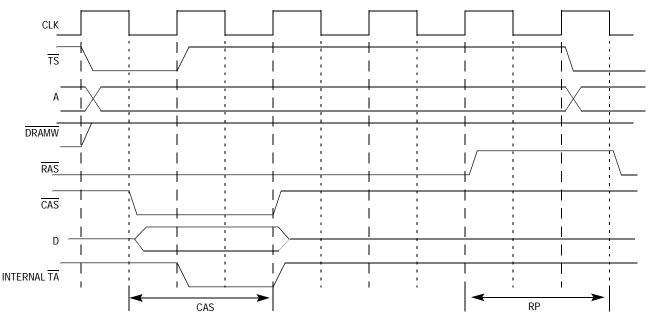

| 11.3.4.3            | Page-Hit Write Transfer in Fast Page Mode11-25         |  |

| 11.3.4.4            | Page Miss Transfer in Fast Page Mode11-27              |  |

| 11.3.4.5            | Bus Arbitration11-30                                   |  |

| 11.3.5              | Burst Page-Mode Operation11-32                         |  |

| 11.3.6              | Extended Data-Out (EDO) DRAM Operation11-35            |  |

| 11.3.7              | Refresh Operation11-38                                 |  |

| 11.3.8              | External Master Use of the DRAM Controller11-40        |  |

| 11.3.8.1            | External Master Nonburst Transfer in Normal Mode11-41  |  |

| 11.3.8.2            | External Master Burst Transfer in Normal Mode11-44     |  |

| 11.3.8.3            | External Master Burst Transfer in Burst Page Mode11-47 |  |

| 11.3.8.4            | Limitations11-50                                       |  |

| 11.4                | Programming Model11-50                                 |  |

| 11.4.1              | DRAM Controller Registers Memory Map11-50              |  |

| 11.4.2              | DRAM Controller Registers11-51                         |  |

| 11.4.2.1            | DRAM Controller Refresh Register (DCRR)11-51           |  |

| 11.4.2.2            | DRAM Controller Timing Register (DCTR)11-52            |  |

| 11.4.2.3            | DRAM Controller Address Reg. (DCAR0 - DCAR1)11-58      |  |

| 11.4.2.4            | DRAM Controller Mask Reg. (DCMR0 - DCMR1)11-59         |  |

| 11.4.2.5            | DRAM Controller Control Reg. (DCCR0 - DCCR1)11-60      |  |

| 11.5                | DRAM Initialization Example11-61                       |  |

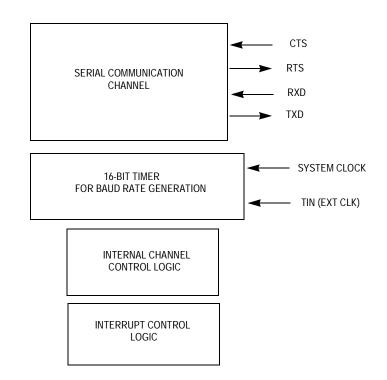

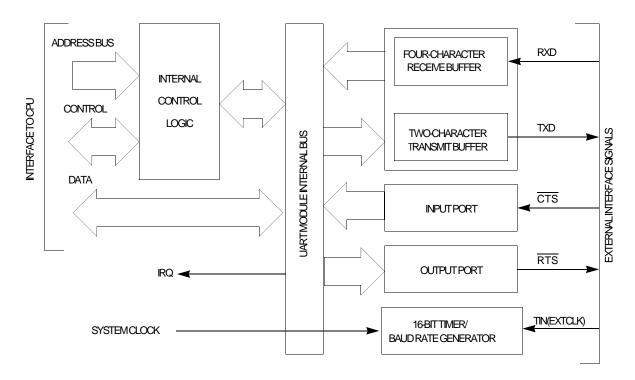

#### Section 12 UART Modules

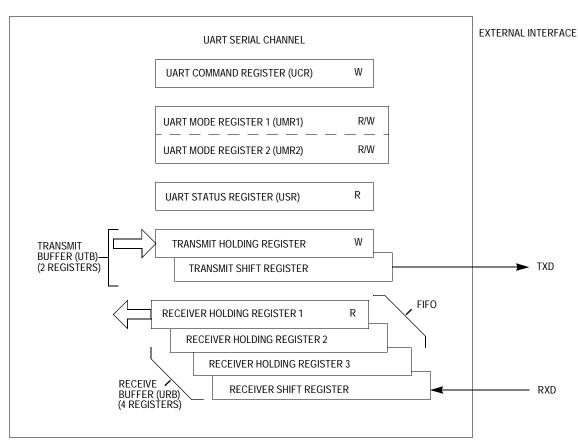

| 12.1   | Module Overview              |  |

|--------|------------------------------|--|

| 12.1.1 | Serial Communication Channel |  |

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                    | Page<br>Number |

|---------------------|------------------------------------------|----------------|

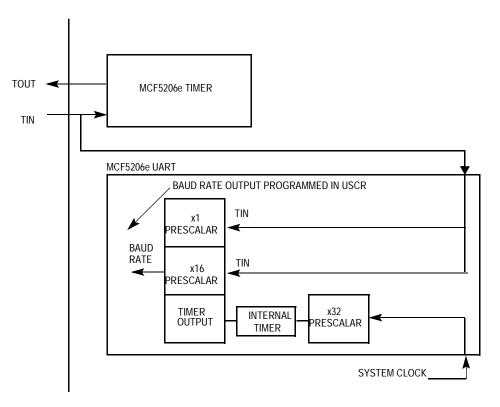

| 12.1.2              | Baud-Rate Generator/Timer                |                |

| 12.1.3              | Interrupt Control Logic                  |                |

| 12.2                | UART Module Signal Definitions           |                |

| 12.2.1              | Transmitter Serial Data Output (TxD)     |                |

| 12.2.2              | Receiver Serial Data Input (RxD)         |                |

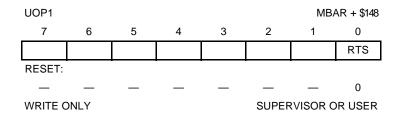

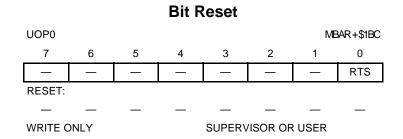

| 12.2.3              | Request-To-Send (RTS)                    |                |

| 12.2.4              | Clear-To-Send (CTS)                      |                |

| 12.3                | Operation                                |                |

| 12.3.1              | Baud-Rate Generator/Timer                |                |

| 12.3.2              | Transmitter and Receiver Operating Modes |                |

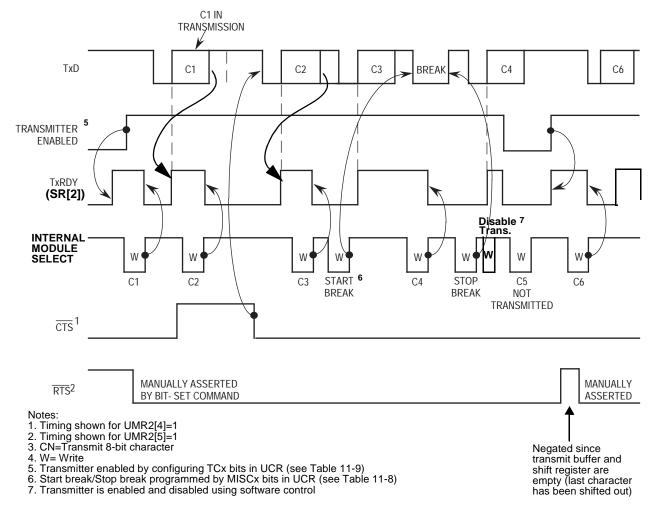

| 12.3.2.1            | Transmitter                              |                |

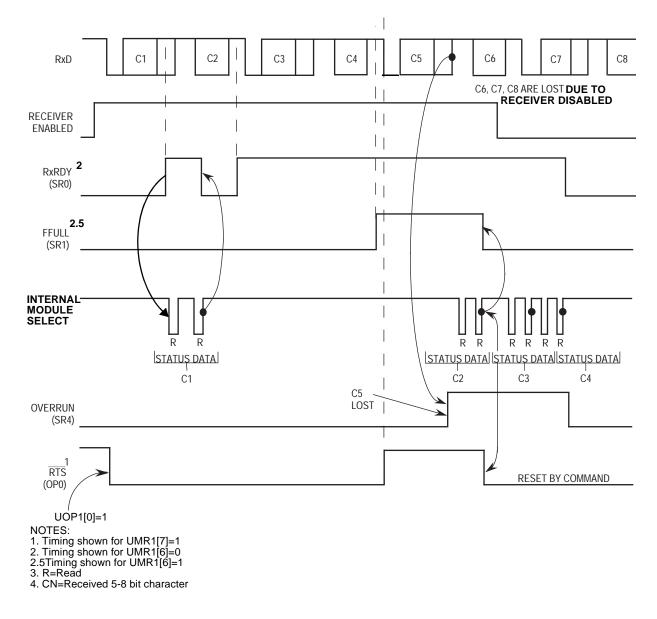

| 12.3.2.2            | Receiver                                 | 12-9           |

| 12.3.2.3            | FIFO Stack                               | 12-11          |

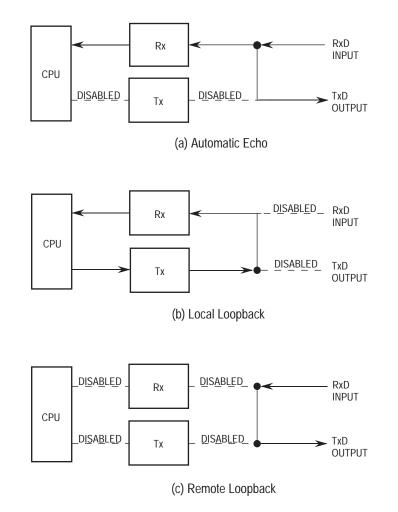

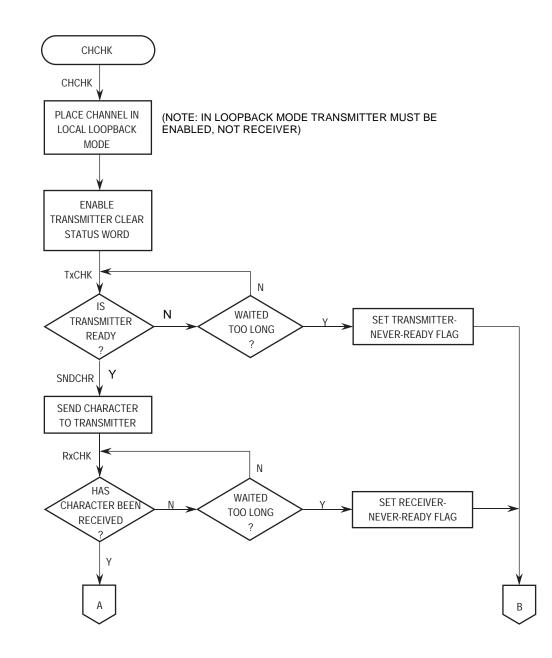

| 12.3.3              | Looping Modes                            | 12-12          |

| 12.3.3.1            | Automatic Echo Mode                      | 12-12          |

| 12.3.3.2            | Local Loopback Mode                      | 12-12          |

| 12.3.3.3            | Remote Loopback Mode                     |                |

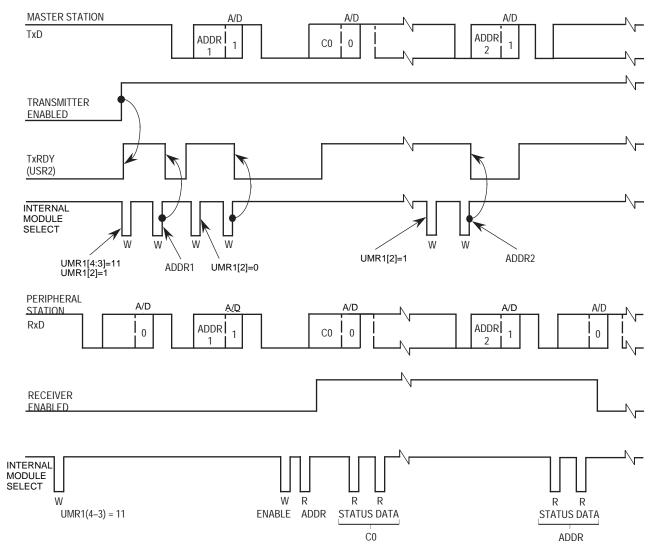

| 12.3.4              | Multidrop Mode                           |                |

| 12.3.5              | Bus Operation                            |                |

| 12.3.5.1            | Read Cycles                              | 12-16          |

| 12.3.5.2            | Write Cycles                             | 12-16          |

| 12.3.5.3            | Interrupt Acknowledge Cycles             | 12-16          |

| 12.4                | Register Description and Programming     | 12-16          |

| 12.4.1              | Register Description                     | 12-16          |

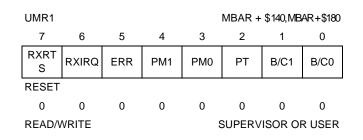

| 12.4.1.1            | Mode Register 1 (UMR1)                   | 12-17          |

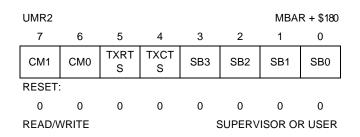

| 12.4.1.2            | Mode Register 2 (UMR2)                   | 12-19          |

| 12.4.1.3            | Status Register (USR)                    | 12-21          |

| 12.4.1.4            | Clock-Select Register (UCSR)             | 12-24          |

| 12.4.1.5            | Command Register (UCR)                   | 12-24          |

| 12.4.1.6            | Receiver Buffer (URB)                    | 12-27          |

| 12.4.1.7            | Transmitter Buffer (UTB)                 | 12-28          |

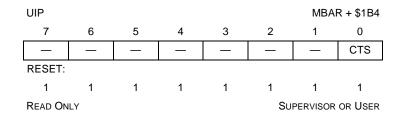

| 12.4.1.8            | Input Port Change Register (UIPCR)       | 12-28          |

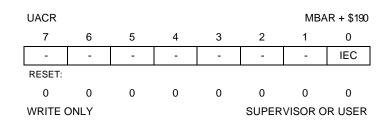

| 12.4.1.9            | Auxiliary Control Register (UACR)        | 12-29          |

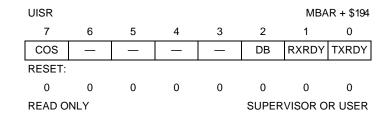

| 12.4.1.10           | Interrupt Status Register (UISR)         |                |

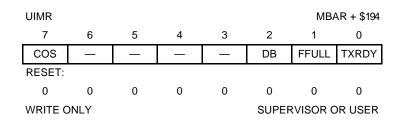

| 12.4.1.11           | Interrupt Mask Register (UIMR)           |                |

| 12.4.1.12           | Timer Upper Preload Register 1 (UBG1)    |                |

| 12.4.1.13           | Timer Upper Preload Register 2 (UBG2)    |                |

| 12.4.1.14           | Interrupt Vector Register (UIVR)         |                |

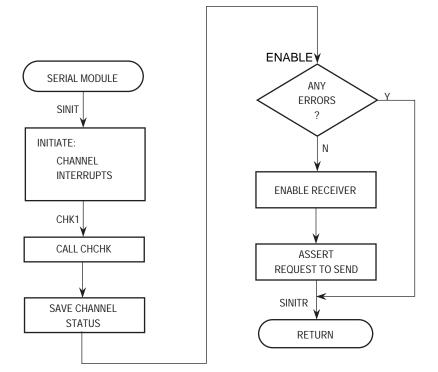

| 12.4.2              | Programming                              | 12-33          |

| 12.4.2.1            | UART Module Initialization               |                |

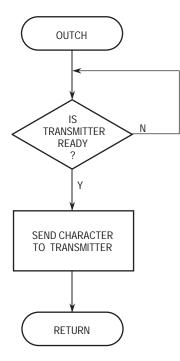

| 12.4.2.2            | I/O Driver Example                       |                |

| 12.4.2.3            | Interrupt Handling                       | 12-33          |

## **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                               | Page<br>Number |

|---------------------|-------------------------------------|----------------|

| 12.5                | UART Module Initialization Sequence | .12-34         |

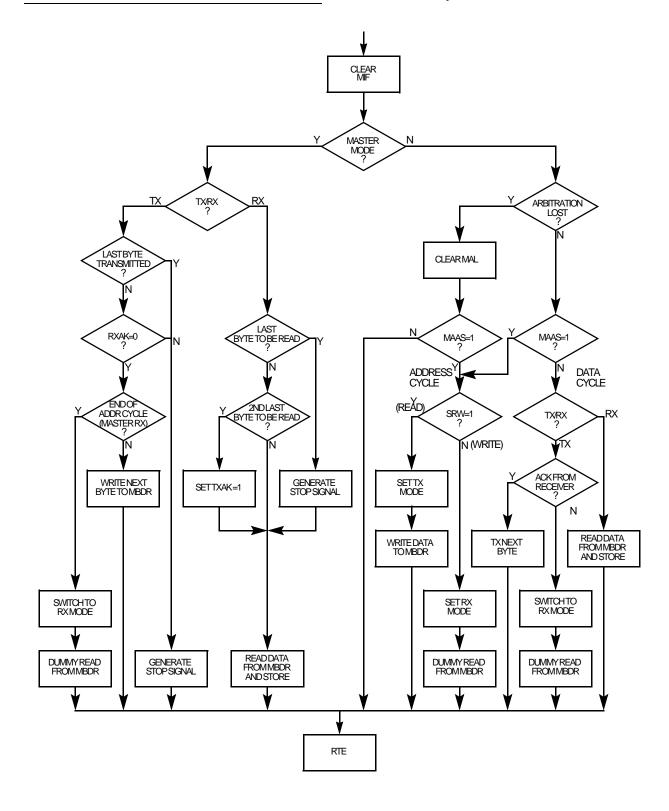

#### Section 13 M-Bus Module

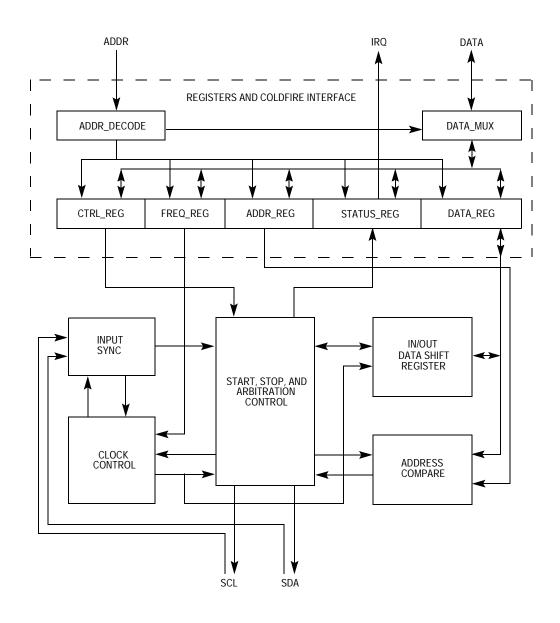

| 13.1   | Overview                                |      |

|--------|-----------------------------------------|------|

| 13.2   | Interface Features                      | 13-1 |

| 13.3   | M-Bus System Configuration              |      |

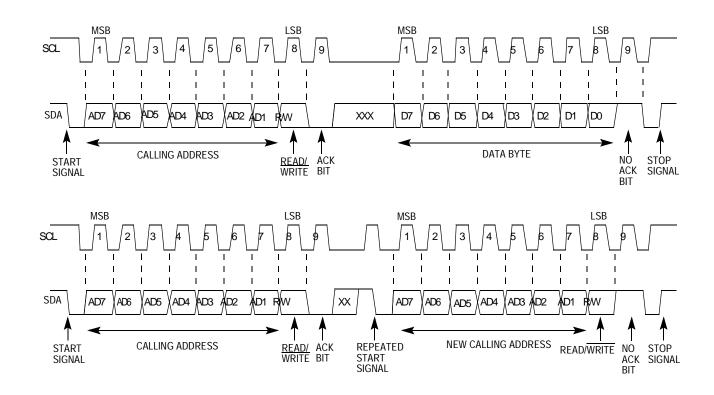

| 13.4   | M-Bus Protocol                          | 13-3 |

| 13.4.1 | START Signal                            |      |

| 13.4.2 | Slave Address Transmission              |      |

| 13.4.3 | Data Transfer                           |      |

| 13.4.4 | Repeated START Signal                   |      |

| 13.4.5 | STOP Signal                             |      |

| 13.4.6 | Arbitration Procedure                   |      |

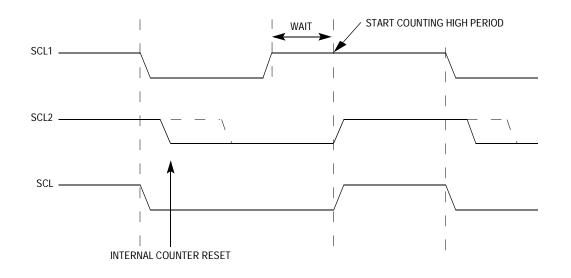

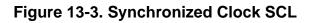

| 13.4.7 | Clock Synchronization                   |      |

| 13.4.8 | Handshaking                             |      |

| 13.4.9 | Clock Stretching                        |      |

| 13.5   | Programming Model                       |      |

| 13.5.1 | M-Bus Address Register (MADR)           |      |

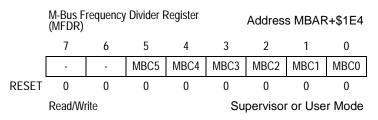

| 13.5.2 | M-Bus Frequency Divider Register (MFDR) |      |

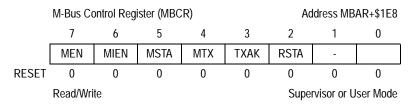

| 13.5.3 | M-Bus Control Register (MBCR)           |      |

| 13.5.4 | M-Bus Status Register (MBSR)            |      |

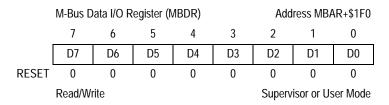

| 13.5.5 | M-Bus Data I/O Register (MBDR)          |      |

| 13.6   | M-Bus Programming Examples              |      |

| 13.6.1 | Initialization Sequence                 |      |

| 13.6.2 | Generation of START                     |      |

| 13.6.3 | Post-Transfer Software Response         |      |

| 13.6.4 | Generation of STOP                      |      |

| 13.6.5 | Generation of Repeated START            |      |

| 13.6.6 | Slave Mode                              |      |

| 13.6.7 | Arbitration Lost                        |      |

|        |                                         |      |

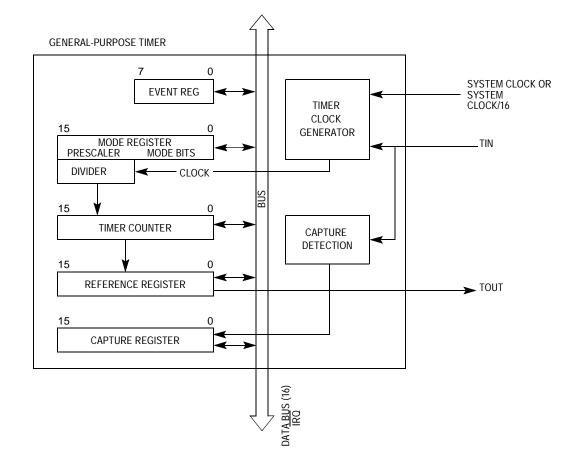

#### Section 14 Timer Module

| Overview of the Timer Module                | 14-1                                                                                               |

|---------------------------------------------|----------------------------------------------------------------------------------------------------|

| Overview of Key Features                    | 14-1                                                                                               |

|                                             |                                                                                                    |

| •                                           |                                                                                                    |

| 5                                           |                                                                                                    |

| Configuring the Timer for Reference Compare |                                                                                                    |

|                                             | Overview of Key Features<br>General-Purpose Timer Units<br>Selecting the Prescaler<br>Capture Mode |

# **TABLE OF CONTENTS (Continued)**

| Title                                             | Page<br>Number                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuring the Timer for Output Mode             | 14-3                                                                                                                                                                                                                                                                                                                 |

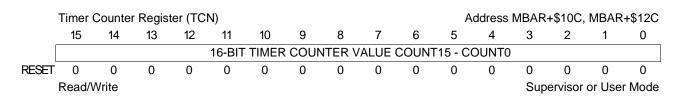

| Programming Model                                 | 14-3                                                                                                                                                                                                                                                                                                                 |

| Understanding the General-Purpose Timer Registers | 14-3                                                                                                                                                                                                                                                                                                                 |

| Timer Mode Register (TMR)                         | 14-4                                                                                                                                                                                                                                                                                                                 |

| Timer Reference Register (TRR)                    | 14-5                                                                                                                                                                                                                                                                                                                 |

| Timer Capture Register (TCR)                      | 14-5                                                                                                                                                                                                                                                                                                                 |

| Timer Counter (TCN)                               | 14-5                                                                                                                                                                                                                                                                                                                 |

| Timer Event Register (TER)                        | 14-6                                                                                                                                                                                                                                                                                                                 |

|                                                   | Title         Configuring the Timer for Output Mode         Programming Model         Understanding the General-Purpose Timer Registers         Timer Mode Register (TMR)         Timer Reference Register (TRR)         Timer Capture Register (TCR)         Timer Counter (TCN)         Timer Event Register (TER) |

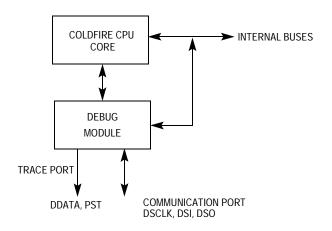

#### Section 15 Debug Support

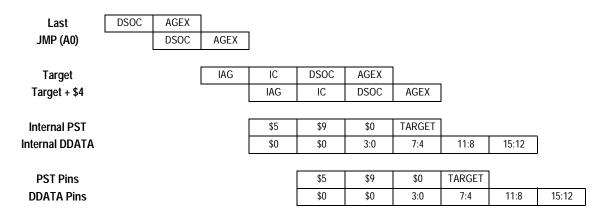

| Real-Time Trace15-1                                      |

|----------------------------------------------------------|

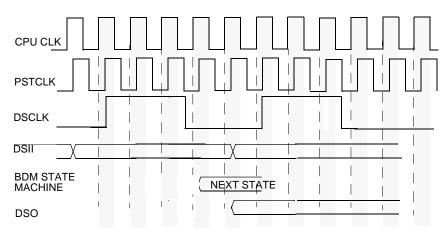

| Background Debug Mode (BDM)15-4                          |

| CPU Halt15-4                                             |

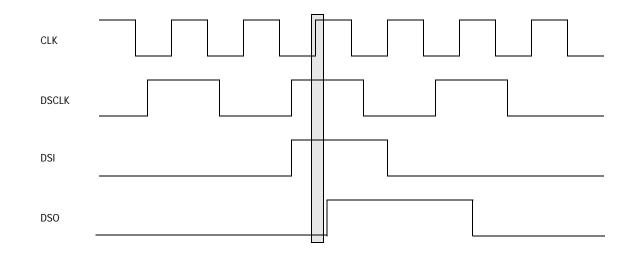

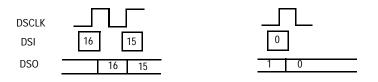

| BDM Serial Interface15-6                                 |

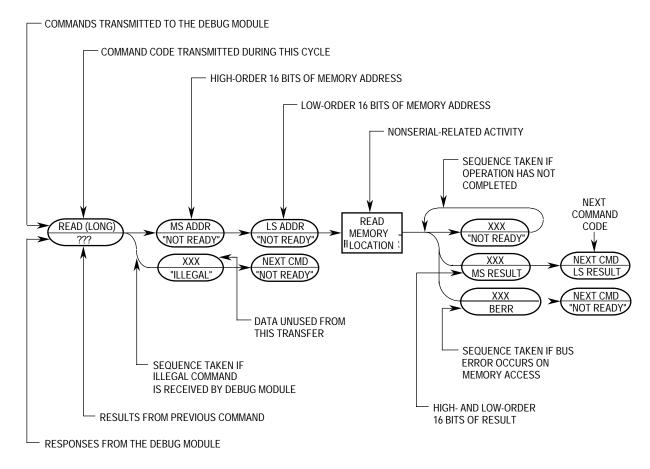

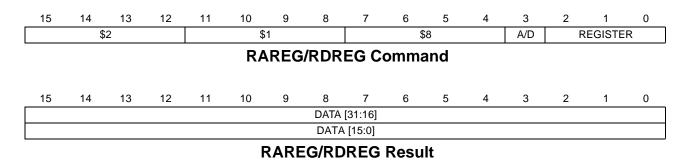

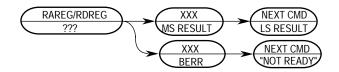

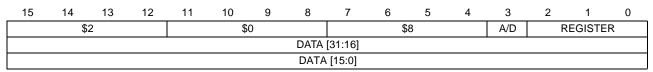

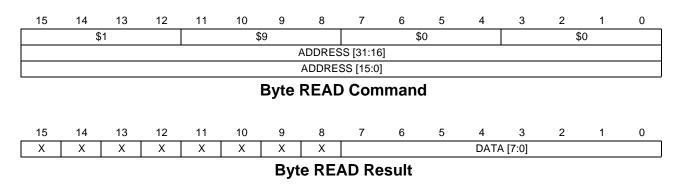

| BDM Command Set15-7                                      |

| BDM Command Set Summary 15-8                             |

| ColdFire BDM Commands15-9                                |

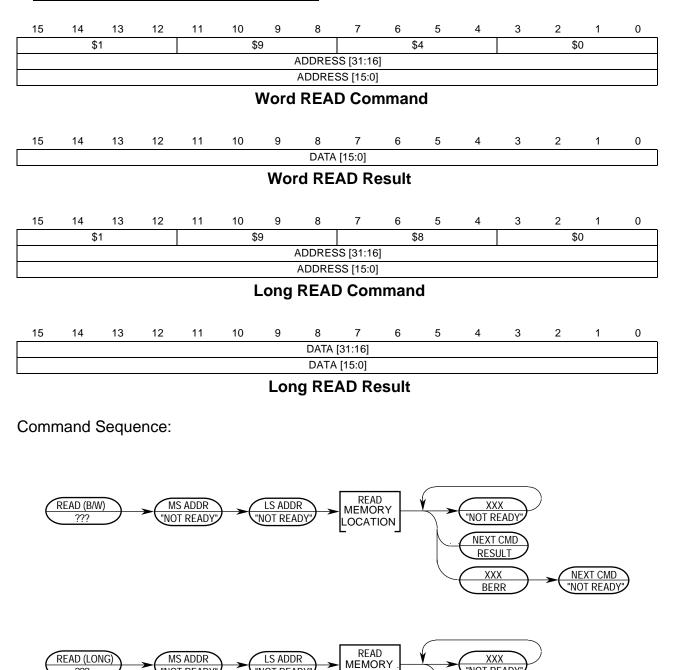

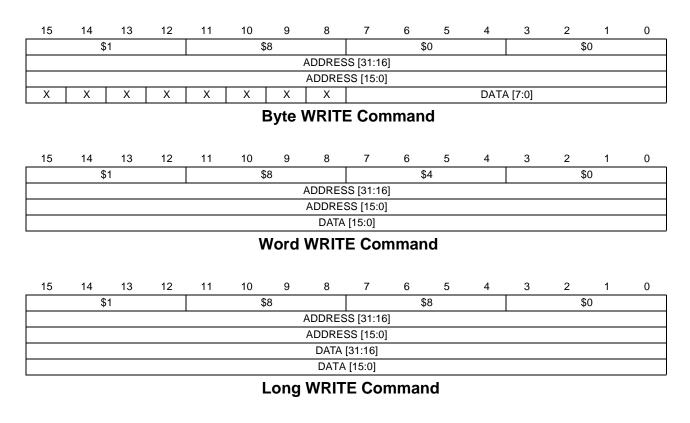

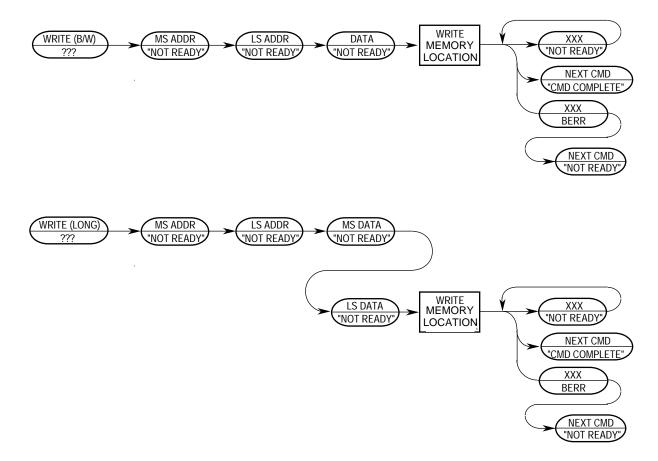

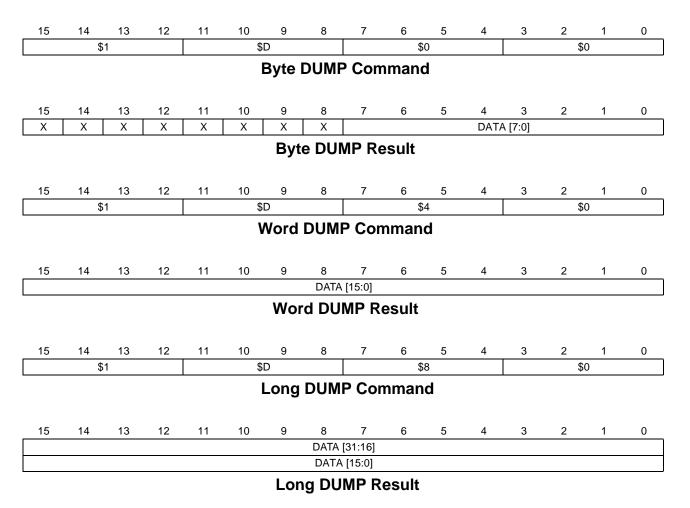

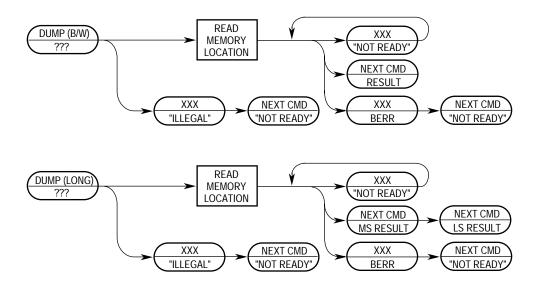

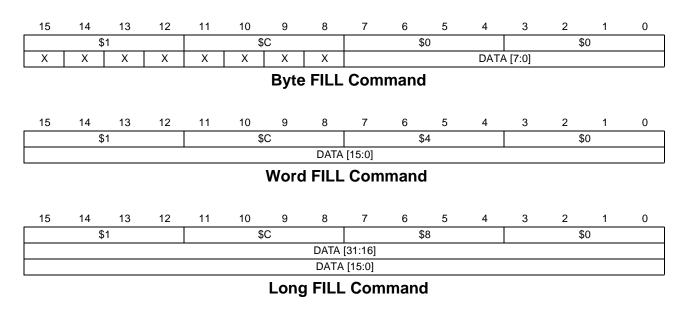

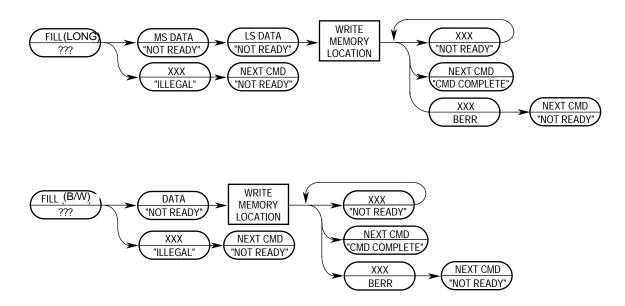

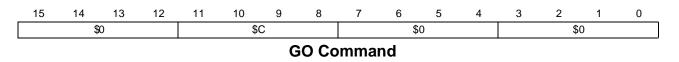

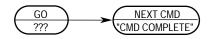

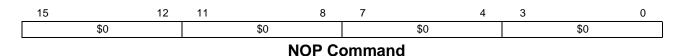

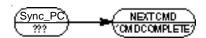

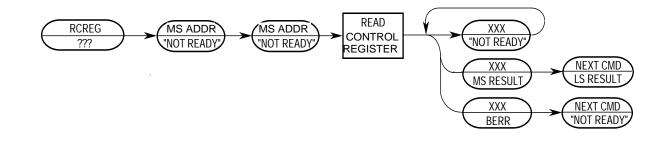

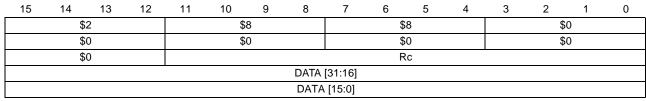

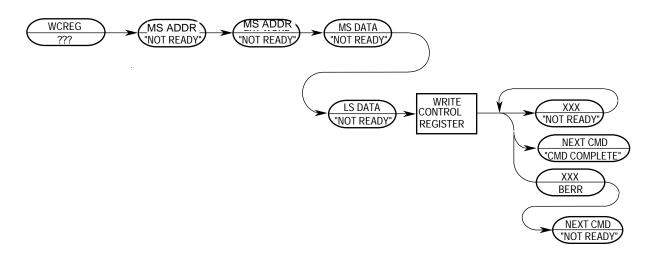

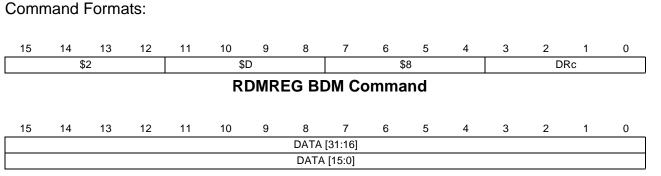

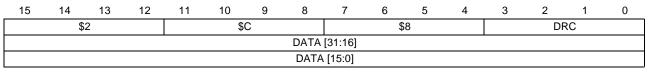

| Command Sequence Diagram                                 |

| Command Set Descriptions                                 |

| Real-Time Debug Support15-26                             |

| Theory of Operation15-26                                 |

| Emulator Mode15-27                                       |

| Debug Module Hardware15-28                               |

| Concurrent BDM and Processor Operation                   |

| Programming Model15-29                                   |

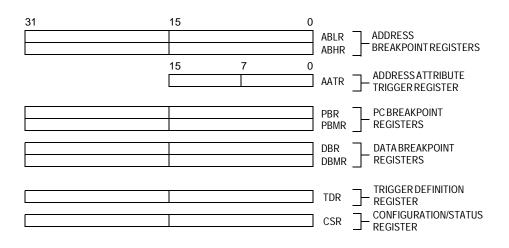

| Address Breakpoint Registers (ABLR, ABHR)                |

| Address Attribute Breakpoint Register (AATR) 15-30       |

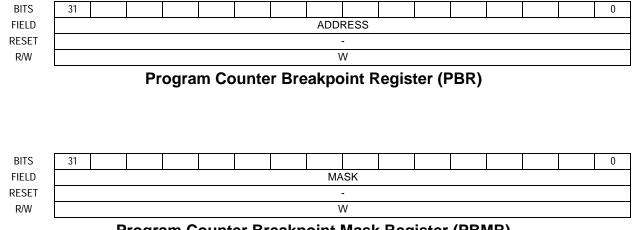

| Program Counter Breakpoint Register (PBR, PBMR) 15-32    |

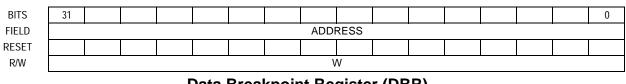

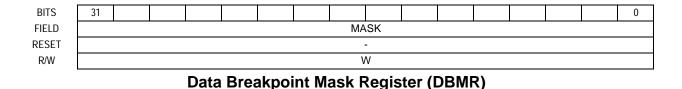

| Data Breakpoint Register (DBR, DBMR)                     |

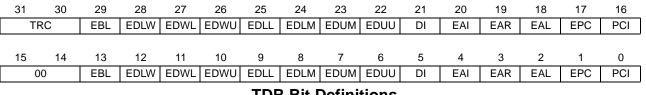

| Trigger Definition Register (TDR)                        |

| Configuration/Status Register (CSR)                      |

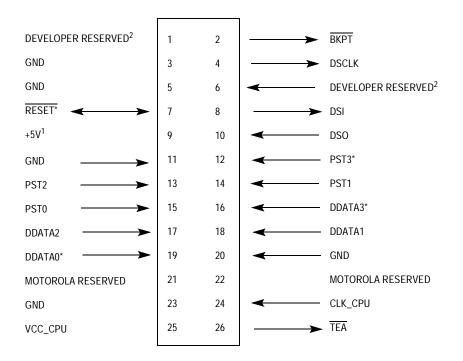

| Motorola Recommended BDM Pinout15-38                     |

| Differences Between the ColdFire BDM and CPU32 BDM 15-38 |

|                                                          |

### Section 16

#### IEEE 1149.1 Test Access Port/JTAG

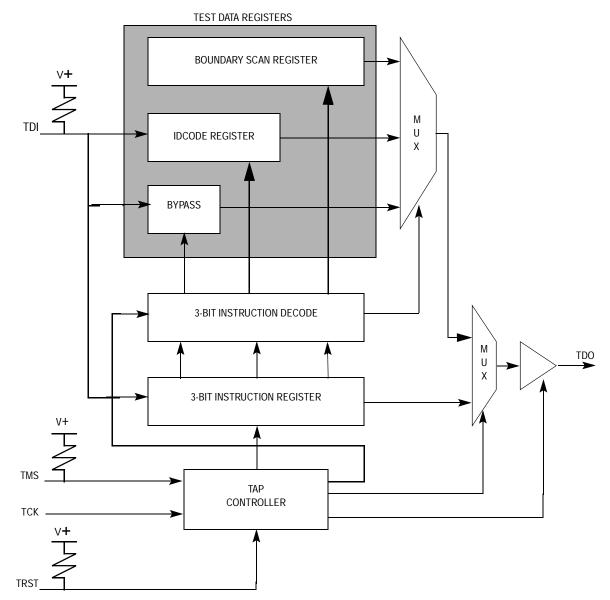

| 16.1 | Overview                   | 16-2 |

|------|----------------------------|------|

| 16.2 | JTAG Pin Descriptions      | 16-2 |

| 16.3 | JTAG Register Descriptions | 16-3 |

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

| 16.3.1              | JTAG Instruction Shift Register              |                |

| 16.3.1.1            | EXTEST Instruction                           | 16-3           |

| 16.3.1.2            | IDCODE                                       | 16-4           |

| 16.3.1.3            | SAMPLE/PRELOAD Instruction                   | 16-4           |

| 16.3.1.4            | HIGHZ Instruction                            |                |

| 16.3.1.5            | CLAMP Instruction                            |                |

| 16.3.1.6            | BYPASS Instruction                           |                |

| 16.3.2              | IDcode Register                              |                |

| 16.3.3              | JTAG Boundary-Scan Register                  |                |

| 16.3.4              | JTAG Bypass Register                         |                |

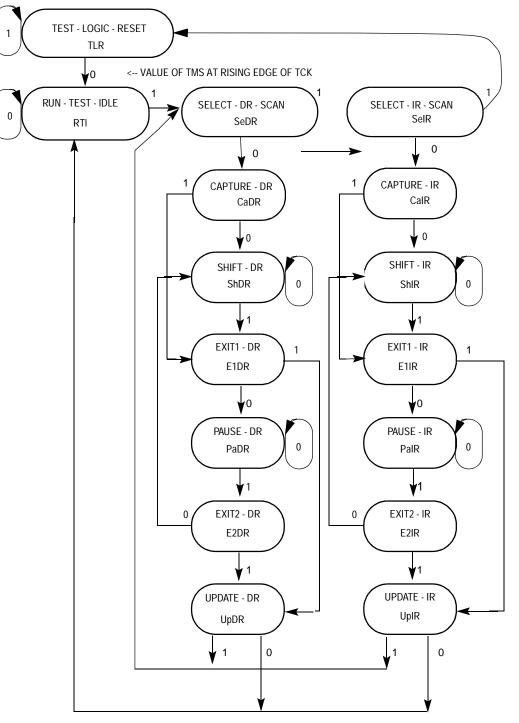

| 16.4                | TAP Controller                               |                |

| 16.5                | Restrictions                                 |                |

| 16.6                | Disabling the IEEE 1149.1 Standard Operation |                |

| 16.7                | Motorola MCF5206e BSDL Description           |                |

| 16.8                | Obtaining the IEEE 1149.1 Standard           |                |

|                     | Section 17<br>Electrical Characteristics     |                |

| 171                 | Maximum Patings                              | 17_1           |

| 17.1      | Maximum Ratings                               |               |

|-----------|-----------------------------------------------|---------------|

| 17.1.1    | Supply, Input Voltage and Storage Temperature | 17-1          |

| 17.1.2    | Operating Temperature                         | 17-2          |

| 17.1.3    | Thermal Resistance                            | 17-2          |

| 17.1.4    | Output Loading                                | 17-2          |

| 17.2      | DC Electrical Specifications                  | 17-3          |

| 17.3      | AC Electrical Specifications                  | 17-4          |

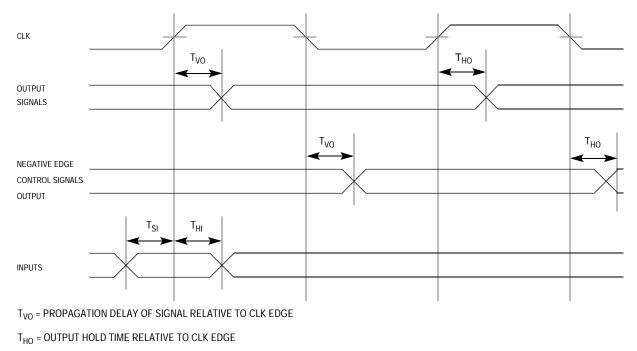

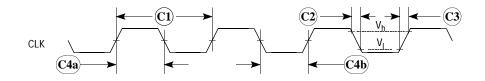

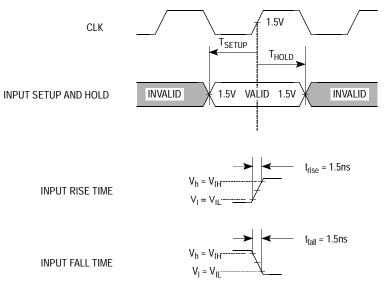

| 17.3.1    | Clock Input Timing Specifications             | 17-4          |

| 17.3.2    | Clock Input Timing Diagram                    | 17-4          |

| 17.3.3    | Processor Bus Input Timing Specifications     | 17-5          |

| 17.3.4    | Input Timing Waveform Diagram                 |               |

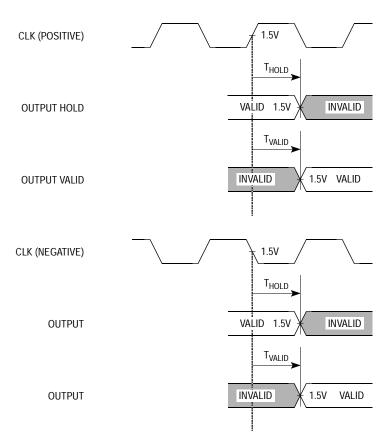

| 17.3.5    | Processor Bus Output Timing Specifications    | 17-7          |

| 17.3.6    | Output Timing Waveform Diagram                | 17-8          |

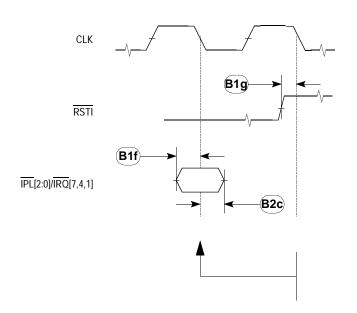

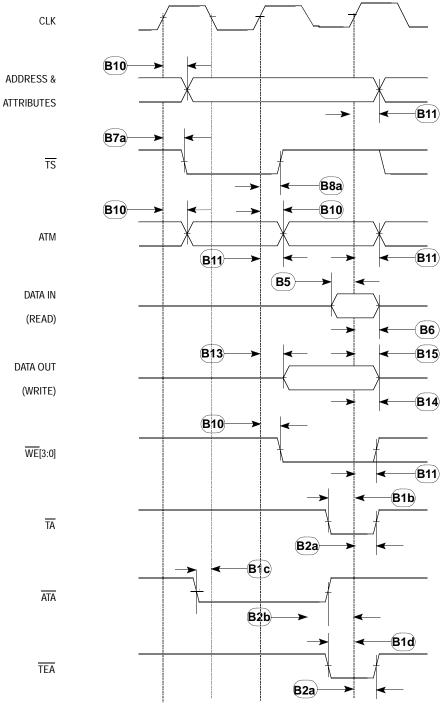

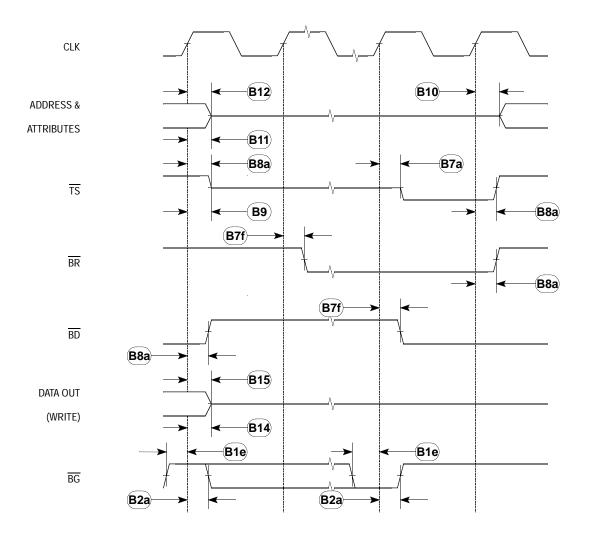

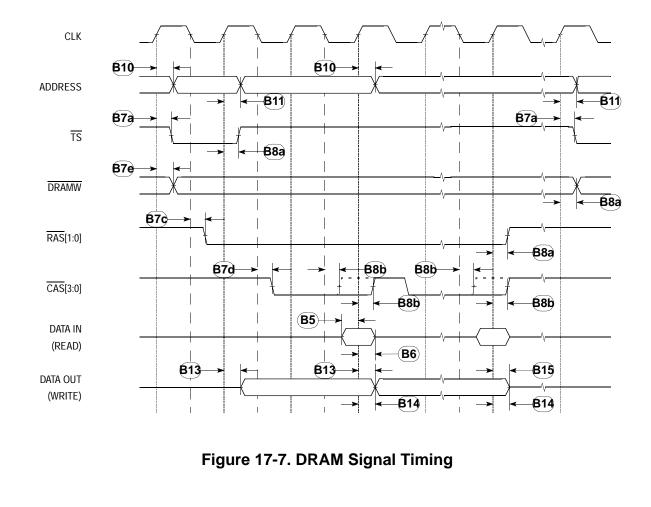

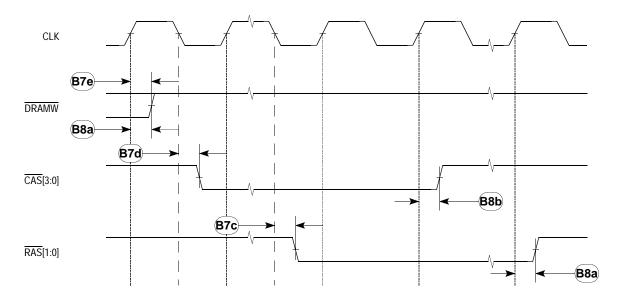

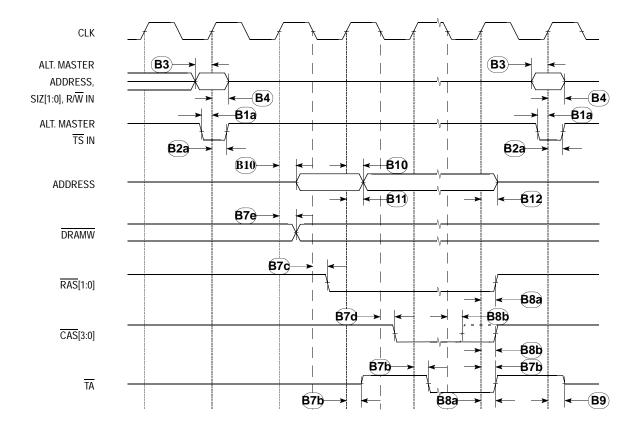

| 17.3.7    | Processor Bus Timing Diagrams                 | 17-9          |

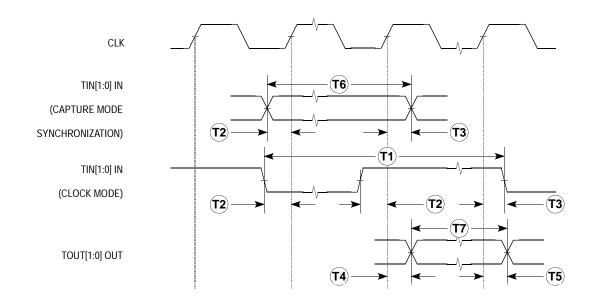

| 17.3.8    | Timer Module AC Timing Specifications         | 17-15         |

| 17.3.9    | Timer Module Timing Diagram                   | 17-15         |

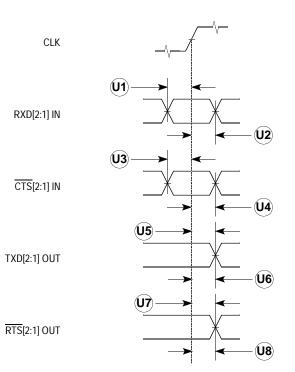

| 17.3.10   | UART Module AC Timing Specifications          | 17-16         |

| 17.3.11   | UART Module Timing Diagram                    | 17-16         |

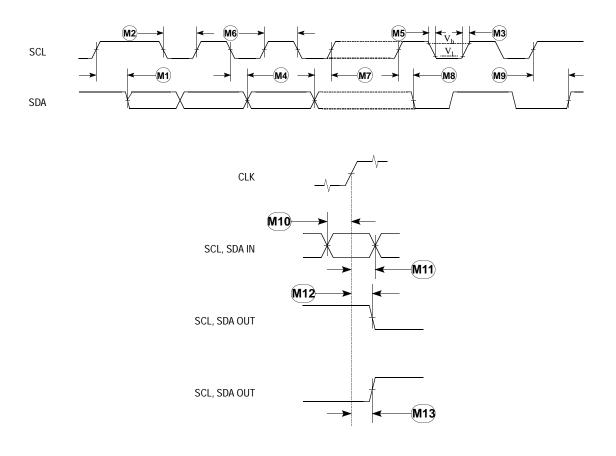

| 17.3.12   | M-Bus Module AC Timing Specifications         | 17-17         |

| 17.3.12.1 | Input Timing Specifications Between SCL an    | d SDA 17-17   |

| 17.3.12.2 | Output Timing Specifications Between SCL a    | and SDA 17-18 |

| 17.3.12.3 | Timing Specifications Between CLK and SCL     | _, SDA 17-18  |

| 17.3.13   | M-Bus Module Timing Diagram                   | 17-19         |

|           |                                               |               |

### **TABLE OF CONTENTS (Continued)**

| Title                                             | Page<br>Number                                                                                                                                                                                                                                |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

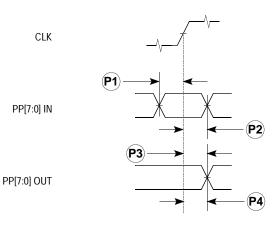

| General-Purpose I/O Port AC Timing Specifications | 17-20                                                                                                                                                                                                                                         |

| General-Purpose I/O Port Timing Diagram           | 17-20                                                                                                                                                                                                                                         |

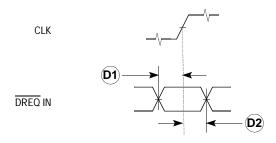

| DMA Controller AC Timing Specifications           | 17-21                                                                                                                                                                                                                                         |

|                                                   |                                                                                                                                                                                                                                               |

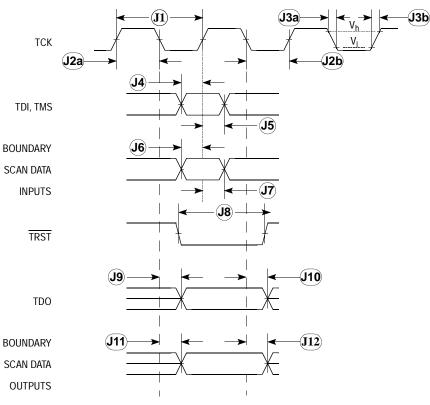

| IEEE 1149.1 (JTAG) AC Timing Specifications       | 17-21                                                                                                                                                                                                                                         |

| IEEE 1149.1 (JTAG) Timing Diagram                 | 17-22                                                                                                                                                                                                                                         |

|                                                   | TitleGeneral-Purpose I/O Port AC Timing SpecificationsGeneral-Purpose I/O Port Timing DiagramDMA Controller AC Timing SpecificationsDMA Controller Timing DiagramIEEE 1149.1 (JTAG) AC Timing SpecificationsIEEE 1149.1 (JTAG) Timing Diagram |

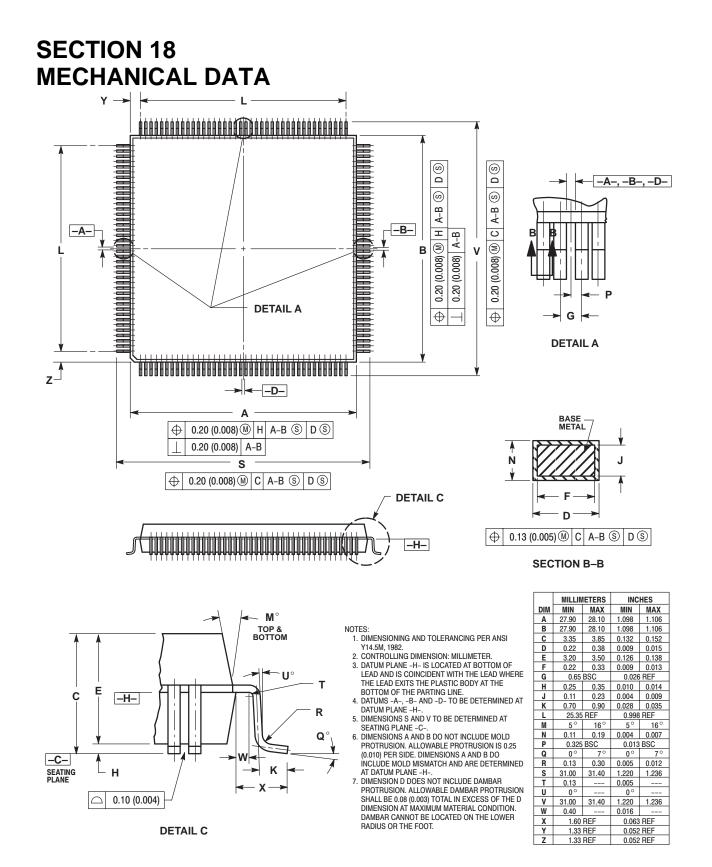

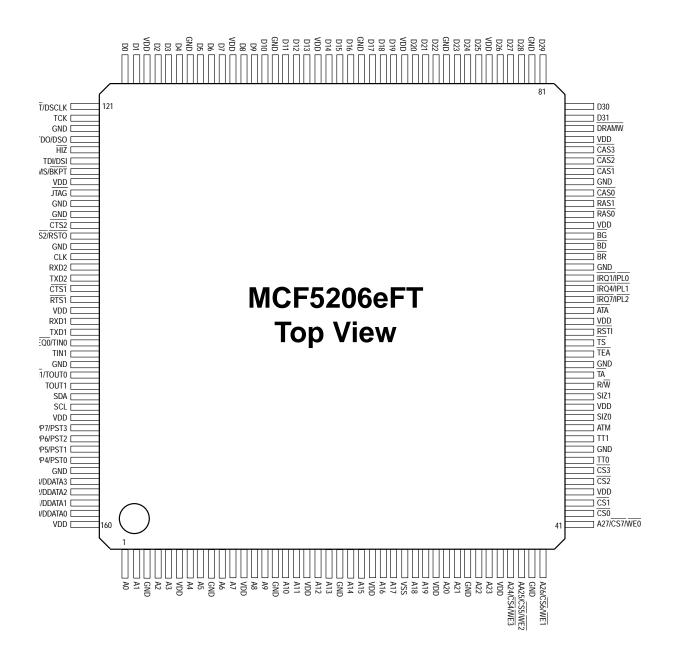

#### Section 18 Mechanical Data

| 18.1   | Package Diagram & Pinout       |  |

|--------|--------------------------------|--|

| 18.1.1 | Package/Frequency Availability |  |

| 18.2   | Documentation                  |  |

| 18.3   | Development Tools              |  |

#### Appendix A MCF5206e Memory Map Summary

#### Appendix B Porting From M68000 Family Devices

| B.1 | C-Compilers and Host Software | B-i  |

|-----|-------------------------------|------|

| B.2 | Target Software Port          | B-i  |

| B.3 | Initialization Code           |      |

| B.4 | Exception Handlers            | В-іі |

| B.5 | Supervisor Registers          |      |

# LIST OF ILLUSTRATIONS

| Figui<br>Numb                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page<br>Numbe                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

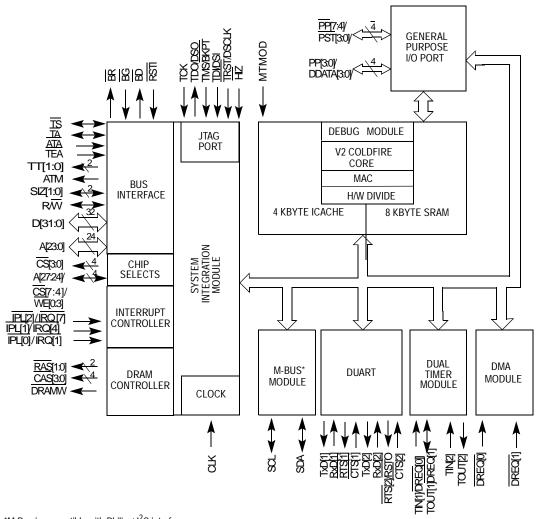

| 1-1.<br>1-2.                                                                                                               | MCF5206e Block Diagram<br>Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                             |

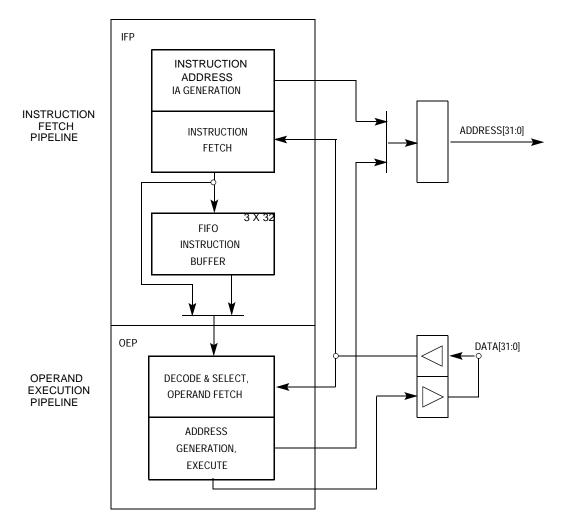

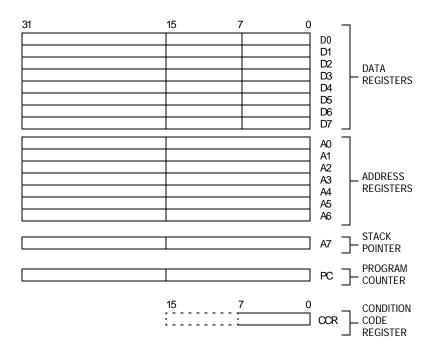

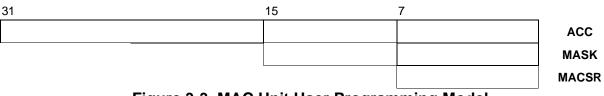

| 3-1.<br>3-2.<br>3-3.<br>3-4.<br>3-5.                                                                                       | ColdFire Processor Core Pipelines<br>User Programming Model<br>MAC Unit User Programming Model<br>Supervisor Programming Model<br>Exception Stack Frame Form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1<br>3-3<br>3-4<br>3-4                                                                                    |

| 4-1.                                                                                                                       | Instruction Cache Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2                                                                                                         |