SLVSBO6B-JANUARY 2013-REVISED JULY 2015

**TPS65090**

# TPS65090 Front-End PMU With Switched-Mode Charger for 2 to 3 Cells In Series

### **Features**

- Wide Input Voltage Charger and Power Path Management:

- V<sub>IN</sub> Range From 6 V to 17 V

- Up to 4-A Output Current on the Power Path

- Switched-Mode Charger; up to 4-A Maximum Charge Current

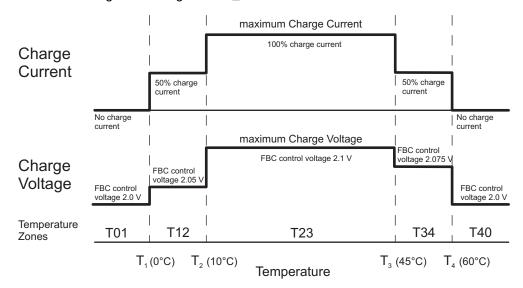

- JEITA Compliant Charging Control

- Thermal Regulation, Safety Timers

- 2 Temperature Sense Inputs

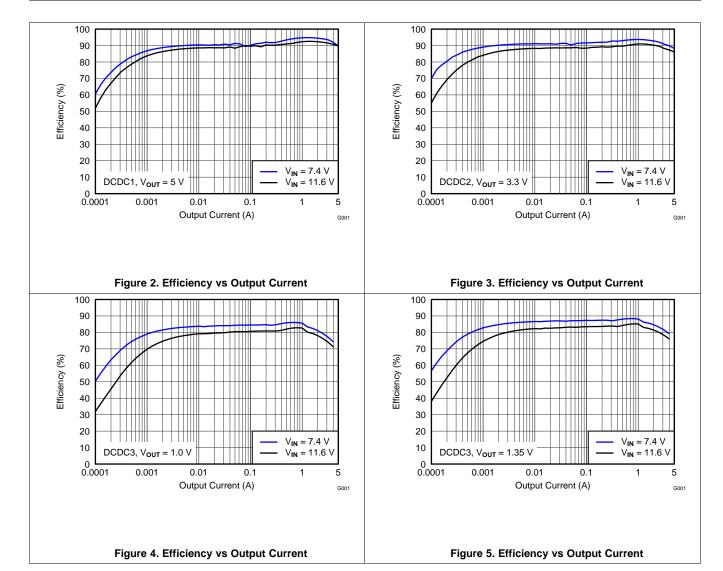

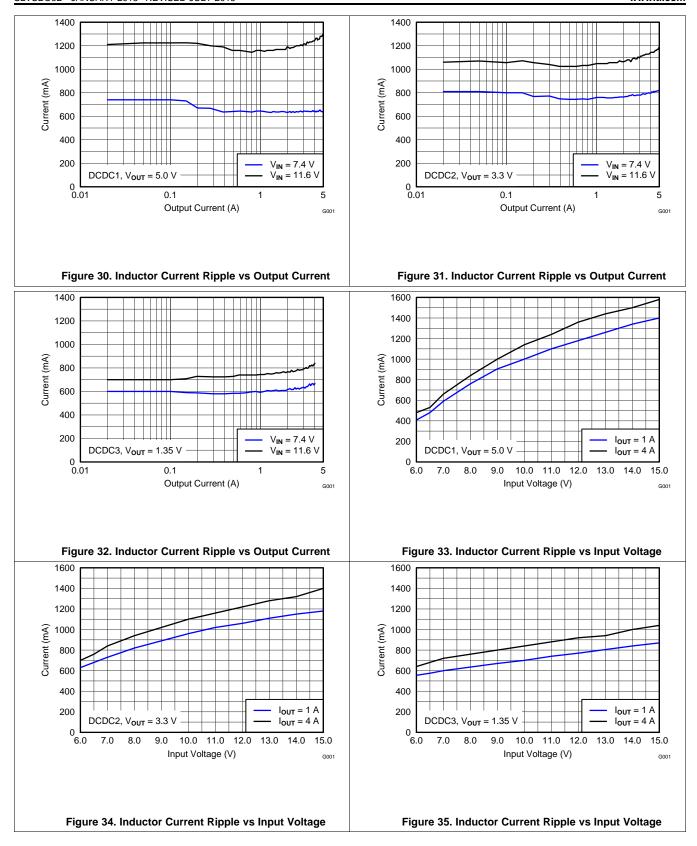

- 3 Step-Down Converters:

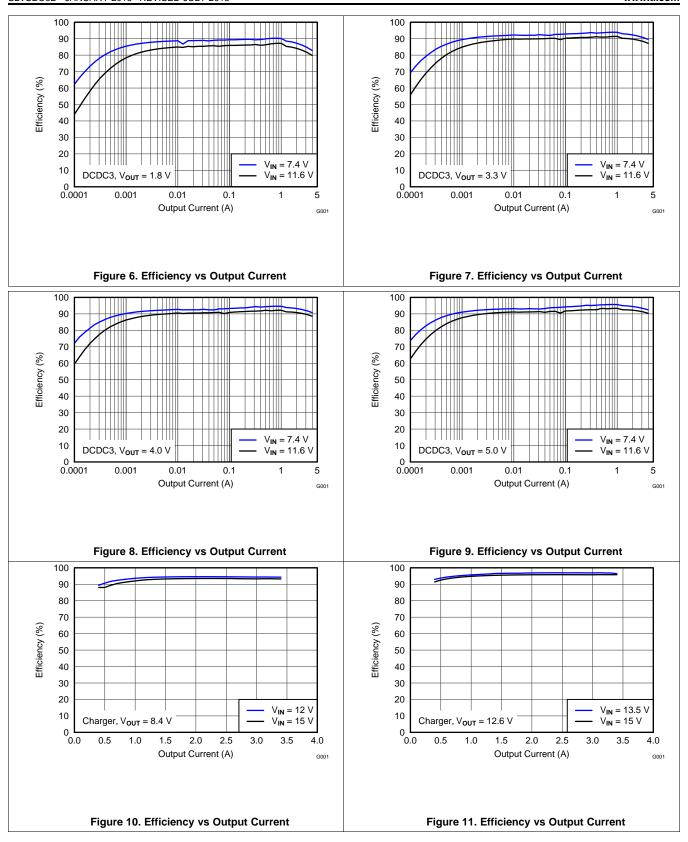

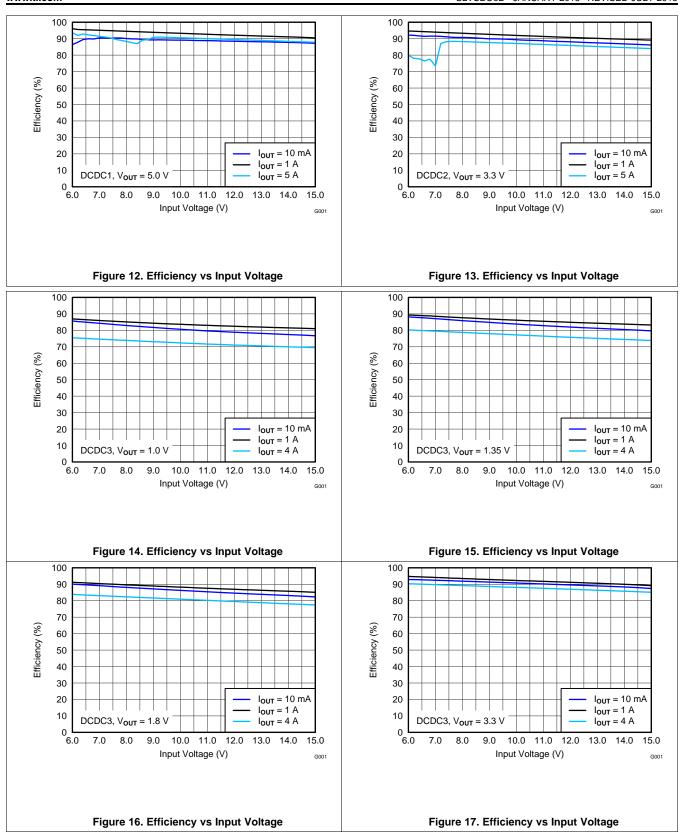

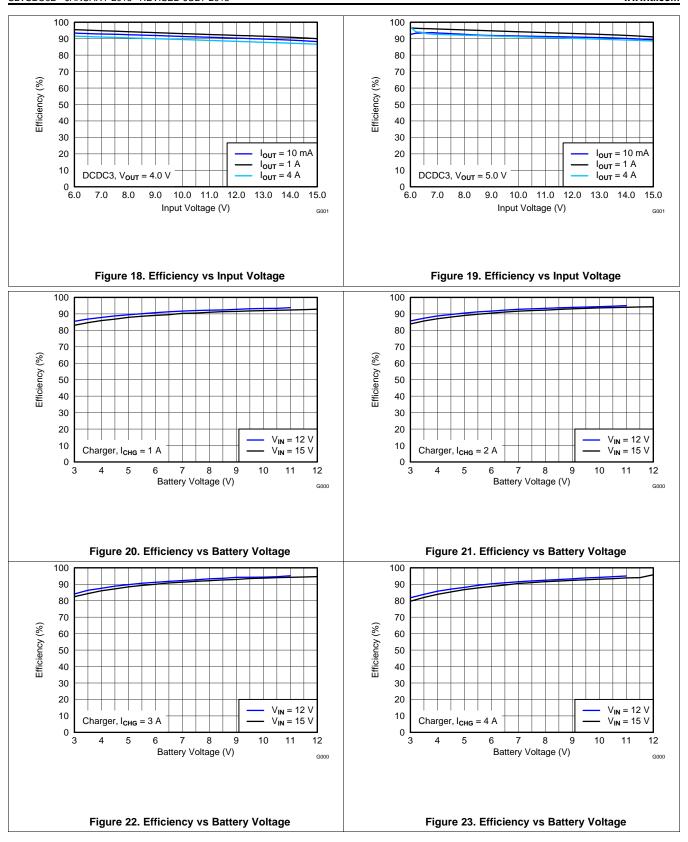

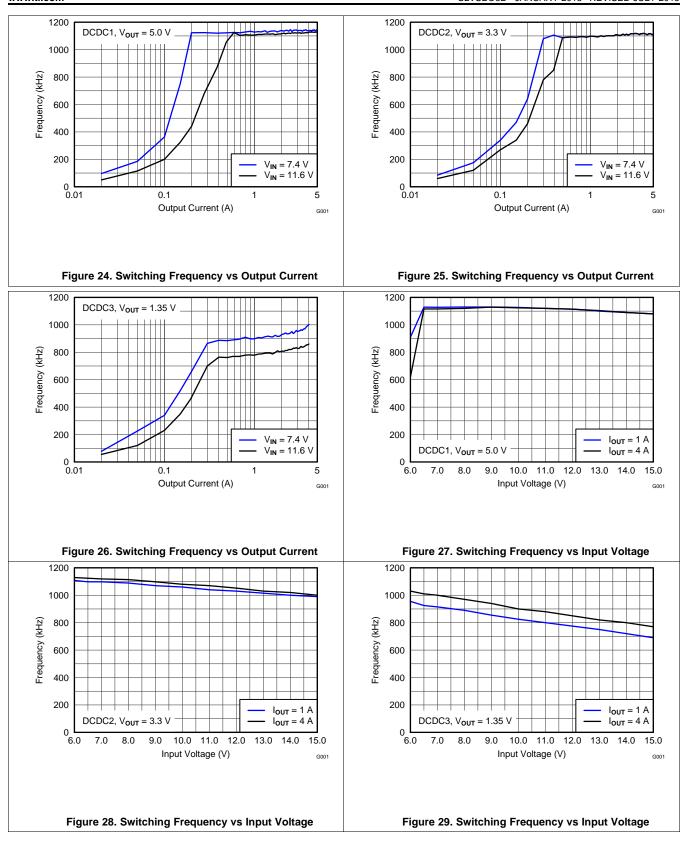

- High Efficiency Over a Wide Output Current Range

- V<sub>IN</sub> Range From 6 V to 17 V

- 2 Fixed Output Voltages (5 V and 3.3 V)

- Up to 5 A of Continuous Output Current

- 1 Adjustable Output Voltage (From 1 V to 5 V)

- Up to 4 A of Continuous Output Current

- Output Voltage Accuracy ±1%

- Typical 30-µA Quiescent Current Per Converter

- 2 Always-On LDOs:

- 2 Fixed Output Voltages (5 V and 3.3 V)

- Output Voltage Accuracy ±1%

- Typical 10-µA Quiescent Current per LDO

- 7 Current-Limited Load Switches:

- One System Voltage Switch With 1-A Current Limit

- One 5-V Switch With 200-mA Current Limit, Reverse-Voltage Protected

- One 3.3-V Switch With 3-A Current Limit

- Four 3.3-V Switches With 1-A Current Limit

- All Switches Controlled by I<sup>2</sup>C Interface

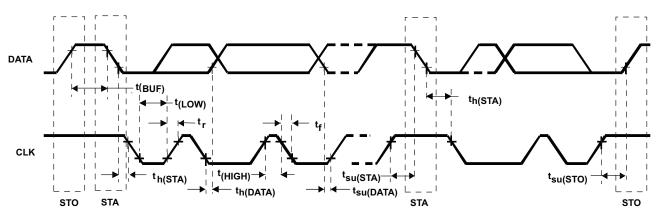

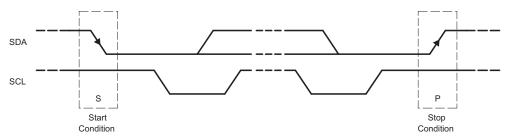

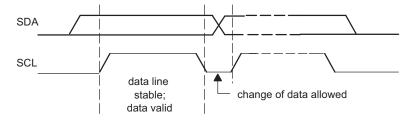

- I<sup>2</sup>C Interface

- Standard-Mode (100 kHz) Supported

- Fast-Mode (400 kHz) Supported

- Fast-Mode Plus (1000 kHz) Supported

- High-Speed (3.4 MHz) Supported

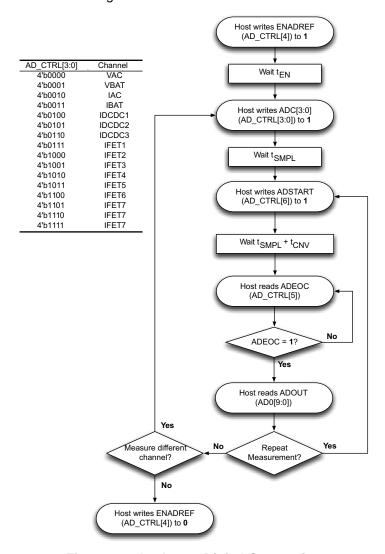

- 16-Channel, 10-Bit Analog-to-Digital Converter (ADC)

- Available in a 9-mm x 9-mm, VQFN-100 Package

## 2 Applications

- Battery-Powered Products Using 2 to 3 Li-Cells in

- **Notebook Computers**

- Mobile PCs and Mobile Internet Devices

- **Industrial Metering Equipment**

- Personal Medical Products

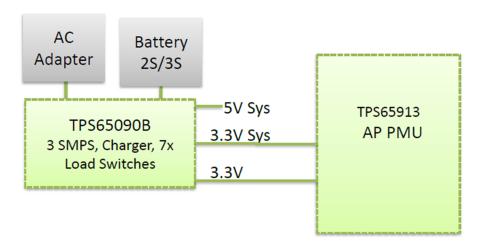

## 3 Description

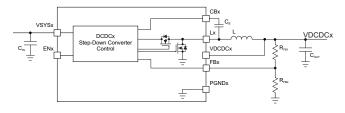

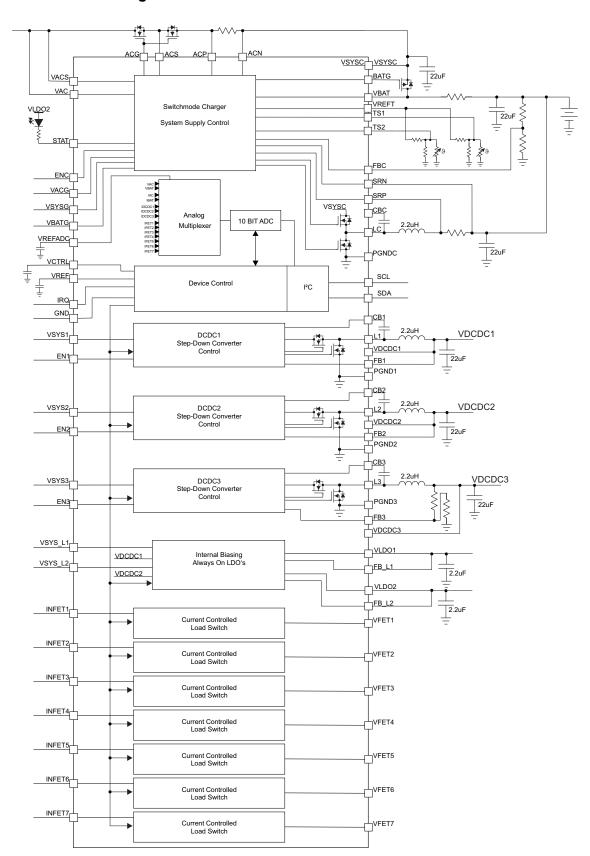

The TPS65090A device is a single-chip power management IC for portable applications consisting of a battery charger with power path management for a dual or triple Li-Ion or Li-Polymer cell battery pack. The charger can be directly connected to an external wall adapter. Three highly efficient step-down converters are targeted for providing a fixed 5-V system voltage, a fixed 3.3-V system voltage, and an adjustable voltage rail. The step-down converters enter a low power mode at light load for maximum efficiency across the widest possible range of load currents. The step-down converters allow the use of small inductors and capacitors to achieve a small solution size. The TPS65090A also integrates two general-purpose always-on LDOs for powering circuit blocks which control the system while shut down. Each LDO operates with an input voltage range from 6 V to 17 V, allowing the LDOs to be supplied from the wall adapter or directly from the main battery pack.

Seven load switches are built into the device. These load switches can be used to control the power supply individually for certain circuit blocks in the application circuit. The current flowing through the load switches, as well as the output current of the step-down converters, the input current from the AC adapter and the charge current is monitored and can be read out using the digital interface.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE       | BODY SIZE (NOM)   |

|-------------|---------------|-------------------|

| TPS65090A   | VQFN-MR (100) | 9.00 mm × 9.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

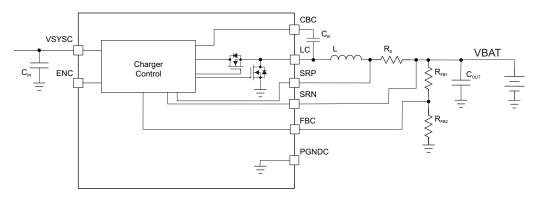

#### DC-DC Block Diagram

### **Table of Contents**

| 1 | Features 1                                            |    | 7.3 Feature Description              | 27 |

|---|-------------------------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                                        |    | 7.4 Device Functional Modes          | 33 |

| 3 | Description 1                                         |    | 7.5 Programming                      | 33 |

| 4 | Revision History2                                     |    | 7.6 Register Maps                    | 37 |

| 5 | Pin Configuration and Functions                       | 8  | Application and Implementation       | 49 |

| 6 |                                                       |    | 8.1 Application Information          |    |

| 0 | Specifications 6 6.1 Absolute Maximum Ratings 6       |    | 8.2 Typical Applications             | 49 |

|   | • • • • • • • • • • • • • • • • • • • •               | 9  | Power Supply Recommendations         |    |

|   | 3                                                     | 10 | Layout                               |    |

|   | 6.3 Recommended Operating Conditions                  |    | 10.1 Layout Guidelines               |    |

|   | 6.5 Electrical Characteristics - Power Path Control 8 |    | 10.2 Layout Example                  |    |

|   |                                                       |    | 10.3 Thermal Considerations          |    |

|   | 6.6 Electrical Characteristics - Charger              | 11 | Device and Documentation Support     |    |

|   | 6.8 Electrical Characteristics - Dc-Dc Converters 11  |    | 11.1 Device Support                  |    |

|   | 6.9 Electrical Characteristics - Load Switches        |    | 11.2 Documentation Support           |    |

|   | 6.10 Electrical Characteristics - Control             |    | 11.3 Community Resources             |    |

|   | 6.11 Timing Requirements - I <sup>2</sup> C Interface |    | 11.4 Trademarks                      |    |

|   |                                                       |    | 11.5 Electrostatic Discharge Caution |    |

| 7 | ,,                                                    |    | 11.6 Glossary                        |    |

| ′ | Detailed Description                                  | 12 | Mechanical, Packaging, and Orderable |    |

|   | 7.1 Overview                                          | 12 | Information                          | 62 |

|   | 7.2 Functional Block Diagram                          |    |                                      |    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision A (July 2013) to Revision B

**Page**

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

## Changes from Original (January 2013) to Revision A

**Page**

| • | Changed text in ALWAYS ON LDOs and POWER PATH CONTROL sections for clarification                | 27 |

|---|-------------------------------------------------------------------------------------------------|----|

| • | Changed text in CHARGER section for clarification                                               | 29 |

| • | Added INTERRUPTS section for clarification                                                      | 33 |

| • | Added text to REVERSE VOLTAGE PROTECTION section for clarification                              | 53 |

| • | Changed graph title from "ADAPTER INPUT POWER UP AND POWER DOWN" to "SUPPLEMENT MODE OPERATION" | 56 |

| • | Added text to THERMAL INFORMATION section for clarification.                                    | 61 |

## 5 Pin Configuration and Functions

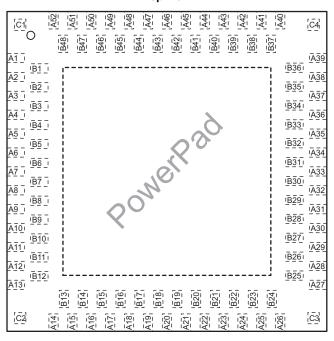

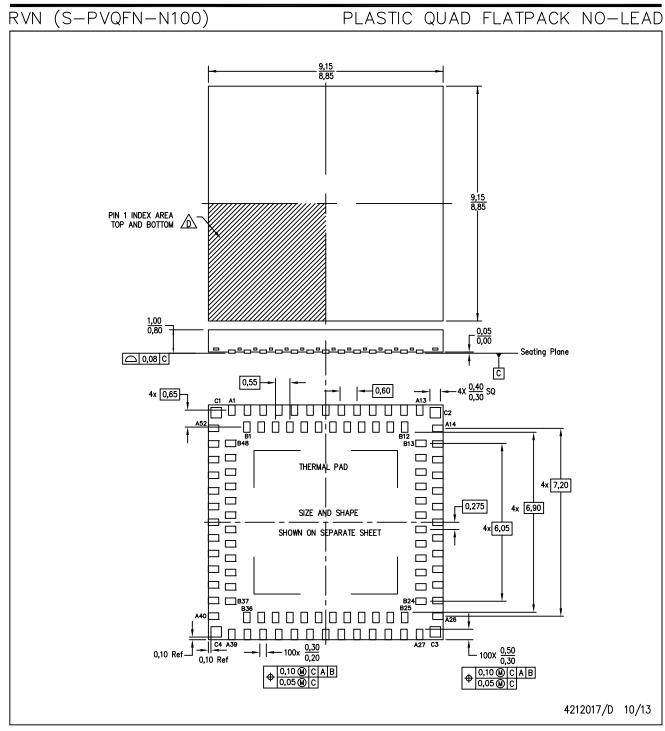

#### RVN Package 100-Pin VQFN-MR Top View

### **Pin Functions**

| Р          | IN                 |     |                                                                                                                                      |  |  |  |

|------------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME       | NO.                | I/O | DESCRIPTION                                                                                                                          |  |  |  |

| POWER PATI | POWER PATH CONTROL |     |                                                                                                                                      |  |  |  |

| ACG        | A51                | 0   | Gate connection for AC adapter input switches                                                                                        |  |  |  |

| ACN        | A50                | I   | Shunt resistor sense connection for input current sensing                                                                            |  |  |  |

| ACP        | B47                | I   | Shunt resistor sense connection for input current sensing                                                                            |  |  |  |

| ACS        | B48                | I   | Source connection for AC adapter input switches                                                                                      |  |  |  |

| BATG       | A2                 | 0   | Gate connection for the battery switch                                                                                               |  |  |  |

| VAC        | A13                | I   | AC adapter supply input for charger control                                                                                          |  |  |  |

| VACS       | A14                | I   | AC adapter sense input for the charger                                                                                               |  |  |  |

| CHARGER    |                    |     |                                                                                                                                      |  |  |  |

| CBC        | B2                 | I   | Bootstrap capacitor connection for charger step-down converter                                                                       |  |  |  |

| ENC        | A41                | I   | Enable input for charger (1: enabled, 0: disabled), must be connected to a valid logic signal                                        |  |  |  |

| FBC        | A52                | I   | Voltage feedback input for charger step-down converter. Must be connected to an external feedback divider to program charge voltage. |  |  |  |

| LC         | A5, B4, B5         | 0   | Inductor connection for switched-mode battery charger step-down converter                                                            |  |  |  |

| PGNDC      | A6, B6             | _   | Power Ground                                                                                                                         |  |  |  |

| SRN        | B1                 | I   | Shunt resistor connection for battery charge current sensing                                                                         |  |  |  |

| SRP        | A1                 | I   | Shunt resistor connection for battery charge current sensing                                                                         |  |  |  |

| STAT       | B13                | 0   | Charge status pin, open-drain (charge in progress, charge complete, sleep mode, fault)                                               |  |  |  |

| TS1        | A24                | I   | Temperature sensor input for temperature sensor 1                                                                                    |  |  |  |

| TS2        | B23                | I   | Temperature sensor input for temperature sensor 2                                                                                    |  |  |  |

| VACG       | A39                | 0   | VAC good pin, open drain (1, high impedance : voltage good; 0 : voltage not available)                                               |  |  |  |

| VBAT       | A15                | I   | Battery sense connection                                                                                                             |  |  |  |

## Pin Functions (continued)

|         | PIN                   |     |                                                                                                                                                        |  |  |

|---------|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO.                   | I/O | DESCRIPTION                                                                                                                                            |  |  |

| VBATG   | A38                   | 0   | VBAT good pin, open drain (1, high impedance : voltage good; 0 : voltage not available), pullup voltage should not be higher than voltage connected to |  |  |

| VREFT   | A25                   | I   | Reference voltage output for temperature measurements                                                                                                  |  |  |

| VSYSC   | A3, A4, B3            | I   | Switched-mode battery charger step-down converter supply voltage                                                                                       |  |  |

| VSYSG   | B36                   | 0   | VSYS good pin, open drain (1, high impedance : voltage good; 0 : voltage not available)                                                                |  |  |

| DCDC1   |                       |     |                                                                                                                                                        |  |  |

| CB1     | B44                   | I   | Bootstrap capacitor connection for DCDC1                                                                                                               |  |  |

| EN1     | B38                   | I   | Enable input for DCDC1 (1: enabled, 0: disabled), must be connected to a valid logic signal                                                            |  |  |

| FB1     | B37                   | I   | Output voltage sense input for DCDC1                                                                                                                   |  |  |

| L1      | A45, B41,<br>B42      | 0   | Inductor connection for DCDC1 step-down converter                                                                                                      |  |  |

| PGND1   | A43, A44,<br>B40      | _   | Power Ground                                                                                                                                           |  |  |

| VDCDC1  | A48                   | I   | Output voltage connection of DCDC1                                                                                                                     |  |  |

| VSYS1   | A46, A47,<br>B43      | I   | Supply voltage input for DCDC1 step-down converter                                                                                                     |  |  |

| DCDC2   | 1                     | T   |                                                                                                                                                        |  |  |

| CB2     | B17                   | I   | Bootstrap capacitor connection for DCDC2                                                                                                               |  |  |

| EN2     | A42                   | I   | Enable input for DCDC2 (1: enabled, 0: disabled), must be connected to a valid logic signal                                                            |  |  |

| FB2     | B24                   | I   | Output voltage sense input for DCDC2                                                                                                                   |  |  |

| L2      | A21, B19,<br>B20      | 0   | Inductor connection for DCDC2 step-down converter                                                                                                      |  |  |

| PGND2   | A22, A23,<br>B21, B22 | _   | Power Ground                                                                                                                                           |  |  |

| VDCDC2  | A18                   | I   | Output voltage connection of DCDC2                                                                                                                     |  |  |

| VSYS2   | A19, A20,<br>B18      | I   | Supply voltage input for DCDC2 step-down converter                                                                                                     |  |  |

| DCDC3   |                       |     |                                                                                                                                                        |  |  |

| CB3     | A12                   | I   | Bootstrap capacitor connection for DCDC3                                                                                                               |  |  |

| EN3     | A26                   | I   | Enable input for DCDC3 (1: enabled, 0: disabled), must be connected to a valid logic signal                                                            |  |  |

| FB3     | B14                   | I   | Output voltage feedback input for DCDC3, a resistive feedback divider must be connected                                                                |  |  |

| L3      | A9, B8, B9            | 0   | Inductor connection for DCDC3 step-down converter                                                                                                      |  |  |

| PGND3   | A7, A8, B7            | _   | Power Ground                                                                                                                                           |  |  |

| VDCDC3  | A16                   | I   | Output voltage sense input for DCDC3                                                                                                                   |  |  |

| VSYS3   | A10, A11,<br>B10, B11 | I   | Supply voltage input for DCDC3 step-down converter                                                                                                     |  |  |

| LDO1    | 1                     | T   |                                                                                                                                                        |  |  |

| FB_L1   | B46                   | I   | Output voltage sense input for LDO1                                                                                                                    |  |  |

| VLDO1   | B45                   | 0   | Output of the LDO1 linear regulator                                                                                                                    |  |  |

| VSYS_L1 | A49                   | I   | Supply voltage input for LDO1 linear regulator                                                                                                         |  |  |

| LDO2    |                       | 1   |                                                                                                                                                        |  |  |

| FB_L2   | B15                   | I   | Output voltage sense input for LDO2                                                                                                                    |  |  |

| VLDO2   | B16                   | 0   | Output of the LDO2 linear regulator                                                                                                                    |  |  |

| VSYS_L2 | A17                   | I   | Supply voltage input for LDO2 linear regulator                                                                                                         |  |  |

| FET1    |                       | ī   | T                                                                                                                                                      |  |  |

| INFET1  | B28                   | I   | Supply voltage input for load switch FET1, connect to GND, if not used                                                                                 |  |  |

| VFET1   | A30                   | 0   | Output of load switch FET1, leave unconnected if not used                                                                                              |  |  |

| FET2    |                       | ī   | T                                                                                                                                                      |  |  |

| INFET2  | B29                   | I   | Supply voltage input for load switch FET2, connect to GND, if not used                                                                                 |  |  |

Submit Documentation Feedback

## Pin Functions (continued)

| PIN          |                   | 1/0 | DECORPORTION                                                                                                                 |

|--------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.               | I/O | DESCRIPTION                                                                                                                  |

| VFET2        | A31               | 0   | Output of load switch FET2, leave unconnected if not used                                                                    |

| FET3         |                   |     |                                                                                                                              |

| INFET3       | A34, B31          | I   | Supply voltage input for load switch FET3, connect to GND, if not used                                                       |

| VFET3        | A32, B30          | 0   | Output of load switch FET3, leave unconnected if not used                                                                    |

| FET4         |                   |     |                                                                                                                              |

| INFET4       | B34               | I   | Supply voltage input for load switch FET4, connect to GND, if not used                                                       |

| VFET4        | A37               | 0   | Output of load switch FET4, leave unconnected if not used                                                                    |

| FET5         |                   |     |                                                                                                                              |

| INFET5       | B33               | I   | Supply voltage input for load switch FET5, connect to GND, if not used                                                       |

| VFET5        | A36               | 0   | Output of load switch FET5, leave unconnected if not used                                                                    |

| FET6         |                   |     |                                                                                                                              |

| INFET6       | B32               | ı   | Supply voltage input for load switch FET6, connect to GND, if not used                                                       |

| VFET6        | A35               | 0   | Output of load switch FET6, leave unconnected if not used                                                                    |

| FET7         |                   |     |                                                                                                                              |

| INFET7       | B27               | I   | Supply voltage input for load switch FET7, connect to GND, if not used                                                       |

| VFET7        | A29               | 0   | Output of load switch FET7, leave unconnected if not used                                                                    |

| DIGITAL INTE | RFACE/CONTI       | ROL |                                                                                                                              |

| AGND         | A33               | _   | Analog ground                                                                                                                |

| GND          | A40               | _   | Logic ground                                                                                                                 |

| IRQ          | B12               | 0   | Interrupt output, open drain, (1, high impedance : no interrupt; $0$ : interrupt) details on events available through $I^2C$ |

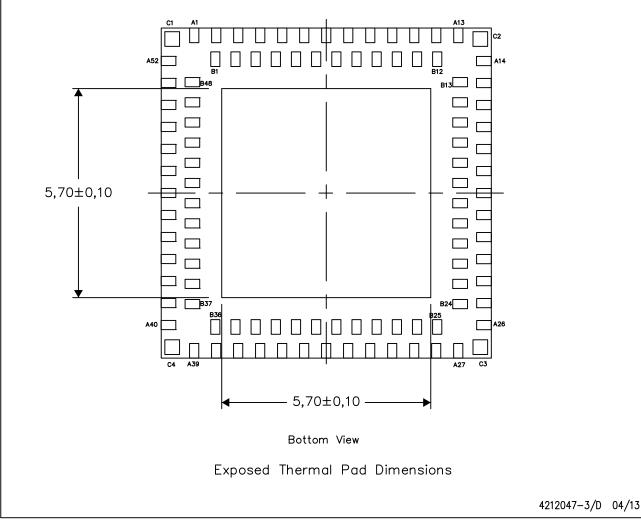

| PGND         | C1, C2, C3,<br>C4 | _   | Internally connected to PowerPAD™                                                                                            |

| PowerPAD     |                   | _   | Must be soldered to achieve appropriate power dissipation. Must be connected to PGND.                                        |

| SCL          | B25               | I/O | Clock input for the I <sup>2</sup> C interface                                                                               |

| SDA          | A27               | I/O | Data line for the I <sup>2</sup> C interface                                                                                 |

| VCTRL        | B39               | 0   | Internal control supply decoupling capacitor connection                                                                      |

| VREF         | B35               | 0   | Reference voltage decoupling capacitor connection                                                                            |

| VREFADC      | B26               | 0   | ADC reference voltage decoupling capacitor connection                                                                        |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                        |                                 | MIN      | MAX | UNIT |  |

|------------------------|---------------------------------|----------|-----|------|--|

| POWER PATH CONT        | ROL                             |          |     |      |  |

| ) / I (2)              | VAC, VACS                       | -0.3     | 30  | .,   |  |

| Voltage <sup>(2)</sup> | ACP, ACN, ACS, BATG             | -0.3     | 20  | V    |  |

| <b>D</b> ''' : 11/ !:  | between ACP and ACN             | -0.5     | 0.5 | .,   |  |

| Differential Voltage   | between ACG and ACS             | -0.3     | 7   | V    |  |

| CHARGER                |                                 | <u> </u> |     | II.  |  |

|                        | VSYSC, VBAT, LC, SRP, SRN, STAT | -0.3     | 20  |      |  |

| Voltage (2)            | FBC, TS1, TS2, VREFT            | -0.3     | 7   | V    |  |

|                        | ENC                             | -0.3     | 3.6 |      |  |

| <b>5</b> //            | between SRP and SRN             | -0.5     | 0.5 | .,   |  |

| Differential Voltage   | between CBC and LC              | -0.3     | 7   | V    |  |

| DCDC1                  |                                 | -        |     |      |  |

|                        | VSYS1, L1                       | -0.3     | 20  |      |  |

| Voltage <sup>(2)</sup> | FB1, VDCDC1                     | -0.3     | 7   | V    |  |

|                        | EN1                             | -0.3     | 3.6 |      |  |

| Differential Voltage   | between CB1 and L1              | -0.3     | 7   | V    |  |

| DCDC2                  |                                 | <u> </u> |     | II.  |  |

|                        | VSYS2, L2                       | -0.3     | 20  |      |  |

| Voltage <sup>(2)</sup> | FB2, VDCDC2                     | -0.3     | 3.6 | V    |  |

|                        | EN2                             | -0.3     | 3.6 |      |  |

| Differential Voltage   | between CB2 and L2              | -0.3     | 7   | V    |  |

| DCDC3                  |                                 | -        |     |      |  |

|                        | VSYS3, L3                       | -0.3     | 20  |      |  |

| Voltage <sup>(2)</sup> | FB3, VDCDC3                     | -0.3     | 7   | V    |  |

|                        | EN3                             | -0.3     | 3.6 |      |  |

| Differential Voltage   | between CB3 and L3              | -0.3     | 7   | V    |  |

| LDO1                   |                                 | <u> </u> |     | II.  |  |

| (2)                    | VSYS_L1                         | -0.3     | 20  | .,   |  |

| Voltage <sup>(2)</sup> | VLDO1, FB_L1                    | -0.3     | 7   | V    |  |

| LDO2                   |                                 |          |     | J.   |  |

| (2)                    | VSYS_L2                         | -0.3     | 20  | .,   |  |

| Voltage <sup>(2)</sup> | VLDO2, FB_L2                    | -0.3     | 3.6 | V    |  |

| FET1                   |                                 | <u> </u> |     | •    |  |

| Voltage <sup>(2)</sup> | INFET1, VFET1                   | -0.3     | 20  | V    |  |

| FET2                   |                                 | <br>     |     | ı    |  |

| Voltage <sup>(2)</sup> | INFET2, VFET2                   | -0.3     | 6   | V    |  |

| FET3                   | -                               |          |     | L    |  |

| Voltage <sup>(2)</sup> | INFET3, VFET3                   | -0.3     | 6   | V    |  |

| FET4                   | <u> </u>                        | <u> </u> |     | l .  |  |

| Voltage <sup>(2)</sup> | INFET4, VFET4                   | -0.3     | 6   | V    |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltages are with respect to network ground terminal.

## **Absolute Maximum Ratings (continued)**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                        |                                                    | MIN  | MAX | UNIT |

|------------------------|----------------------------------------------------|------|-----|------|

| FET5                   |                                                    |      |     |      |

| Voltage <sup>(2)</sup> | INFET5, VFET5                                      | -0.3 | 6   | V    |

| FET6                   |                                                    | *    |     | -    |

| Voltage <sup>(2)</sup> | INFET6, VFET6                                      | -0.3 | 6   | V    |

| FET7                   |                                                    |      |     |      |

| Voltage <sup>(2)</sup> | INFET7, VFET7                                      | -0.3 | 6   | V    |

| DIGITAL INTERFA        | ACE/CONTROL                                        | ·    |     | •    |

| \/alta===(2)           | SDAT, SCLK, IRQ, VCTRL, VCTRL2, VACG, VSYSG, VBATG | -0.3 | 7   |      |

| Voltage <sup>(2)</sup> | VREFADC, VREF                                      | -0.3 | 3.6 | V    |

| GENERAL                |                                                    |      |     |      |

| Temperature            | Operating junction, T <sub>J</sub>                 | -40  | 150 | 00   |

|                        | Storage temperature, T <sub>stq</sub>              | -65  | 150 | °C   |

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

## 6.3 Recommended Operating Conditions

| Treesminended Speraning Containens       | MIN                                   | NOM MAX | UNIT |

|------------------------------------------|---------------------------------------|---------|------|

| POWER PATH CONTROL                       | ,                                     | ,       |      |

| Supply voltage at VAC                    | 6                                     | 17      | V    |

| Differential voltage between ACP and ACN | -0.2                                  | 0.2     | V    |

| CHARGER                                  | ,                                     |         |      |

| Supply voltage at VSYSC, VBAT            | 6                                     | 17      | V    |

| Differential voltage between SRP and SRN | -0.2                                  | 0.2     | V    |

| DCDC1                                    |                                       |         |      |

| Supply voltage at VSYS1                  | 6                                     | 17      | V    |

| DCDC2                                    |                                       |         |      |

| Supply voltage at VSYS2                  | 6                                     | 17      | V    |

| DCDC3                                    |                                       |         |      |

| Supply voltage at VSYS3                  | 6                                     | 17      | V    |

| LD01                                     |                                       | ·       |      |

| Supply voltage at VSYS_L1                | 6                                     | 17      | V    |

| LDO2                                     |                                       |         |      |

| Supply voltage at VSYS_L2                | 6                                     | 17      | V    |

| FET1                                     |                                       |         |      |

| Supply voltage at INFET1                 | 5                                     | 17      | V    |

| FET2                                     |                                       |         |      |

| Supply voltage at INFET2                 | 4.5                                   | 5.5     | V    |

| FET3                                     |                                       |         |      |

| Supply voltage at INFET3                 | 3                                     | 5.5     | V    |

| FET4                                     | · · · · · · · · · · · · · · · · · · · |         |      |

| Supply voltage at INFET4                 | 3                                     | 5.5     | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **Recommended Operating Conditions (continued)**

|                                                | MIN | NOM MA | X  | UNIT |

|------------------------------------------------|-----|--------|----|------|

| FET5                                           |     |        |    |      |

| Supply voltage at INFET5                       | 3   | 5      | .5 | V    |

| FET6                                           |     |        | •  |      |

| Supply voltage at INFET6                       | 3   | 5      | .5 | V    |

| FET7                                           |     |        | •  |      |

| Supply voltage at INFET7                       | 3   | 5      | .5 | V    |

| CONTROL                                        |     |        | •  |      |

| Supply voltage at VCTRL2                       | 3   | 5      | .5 | V    |

| GENERAL                                        |     |        | •  |      |

| Operating free-air temperature, T <sub>A</sub> | -40 |        | 35 | °C   |

| Operating junction temperature, T <sub>J</sub> | -40 | 1:     | 25 | °C   |

### 6.4 Thermal Information

|                      |                                              | TPS65090A     |      |

|----------------------|----------------------------------------------|---------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RVN [VQFN-MR] | UNIT |

|                      |                                              | 100 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 24.8          | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case(top) thermal resistance     | 5.6           | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 3.9           | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.1           | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 3.9           | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case(bottom) thermal resistance  | 0.1           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics - Power Path Control

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

| PARAMETER                                                         | TEST CONDITIONS                                                          | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| VAC overvoltage disconnect                                        |                                                                          | 17   | 17.6 | 18.2 | V    |

| VAC overvoltage hysteresis                                        |                                                                          |      | 550  |      | mV   |

| VAC undervoltage lockout                                          | V <sub>AC</sub> voltage decreasing                                       | 5    | 5.5  | 6    | V    |

| VAC undervoltage lockout hysteresis                               |                                                                          |      | 550  |      | mV   |

| Maximum input DPM current programming range                       |                                                                          | 1000 |      | 4000 | mA   |

| $(V_{ACP}$ - $V_{ACN})$ voltage to maximum input DPM current gain |                                                                          |      | 100  |      | A/V  |

| land DDM compart as sulation                                      | V <sub>ACP</sub> - V <sub>ACN</sub> , IACSET = 0                         | 40   | 44   | 48   | mV   |

| Input DPM current regulation                                      | V <sub>ACP</sub> - V <sub>ACN</sub> , IACSET = 1                         | 36   | 40   | 44   | mV   |

| Maximum battery discharge current                                 | V <sub>BAT</sub> - V <sub>SRN</sub> , IBATSET = 0, T <sub>A</sub> = 25°C | 17.5 | 20   | 21   | mV   |

| comparator threshold                                              | V <sub>BAT</sub> - V <sub>SRN</sub> , IBATSET = 1, T <sub>A</sub> = 25°C | 15   | 17.5 | 18.5 | mV   |

| VACS input impedance                                              |                                                                          |      | 1000 |      | kΩ   |

| VAC input impedance                                               |                                                                          |      | 25   |      | kΩ   |

| Gate drive current on ACG                                         |                                                                          | 12   |      |      | μΑ   |

| Gate drive current on BATG                                        | Turnon                                                                   | 500  |      |      | μΑ   |

| Gate drive current on BATG                                        | Turnoff                                                                  | 25   |      |      | mA   |

| BATG turnoff delay time after adapter is detected                 |                                                                          |      | 30   |      | ms   |

## **Electrical Characteristics - Power Path Control (continued)**

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                             | PARAMETER                                             | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT |

|-----------------------------|-------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

|                             | Quiescent current into VAC                            | Charging enabled, V <sub>AC</sub> = 11.5 V  |     | 2.5 | 5   | mA   |

|                             | Quiescent current into VAC                            | Charging disabled, V <sub>AC</sub> = 11.5 V |     | 1   | 1.5 | mA   |

|                             | Leakage current into ACP and ACN                      | Charging disabled                           |     |     | 80  | μΑ   |

| $V_{SUPPL}$                 | Supplement threshold to turn on battery switch        | V <sub>SRN</sub> - V <sub>ACN</sub> rising  | 13  | 45  | 84  | mV   |

| V <sub>SUPPL</sub><br>HYS   | Supplement mode hysteresis to turn off battery switch | V <sub>SRN</sub> - V <sub>ACN</sub> falling |     | 20  |     | mV   |

| I <sub>ACRC</sub>           | Reverse adapter current threshold                     | V <sub>ACN</sub> - V <sub>ACP</sub> rising  |     | 45  |     | mV   |

| $V_{SLEEP}$                 | SLEEP mode threshold                                  | V <sub>AC</sub> – V <sub>SRN</sub> falling  | 20  | 90  | 150 | mV   |

| V <sub>SLEEP</sub> _<br>HYS | SLEEP mode hysteresis                                 | V <sub>AC</sub> – V <sub>SRN</sub> rising   |     | 200 |     | mV   |

## 6.6 Electrical Characteristics - Charger

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                     | PARAMETER                                                                     | TEST CONDITIONS                                                         | MIN   | TYP                          | MAX   | UNIT |

|---------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------|------------------------------|-------|------|

| CHARG               | ER - POWER                                                                    |                                                                         |       |                              |       |      |

|                     |                                                                               | VSET = 00, default for $T_{01}$ and $T_{40}$                            | 1.98  | 2                            | 2.02  |      |

| \ /                 | Charger foodback valtage                                                      | VSET = 01, default for T <sub>12</sub>                                  | 2.03  | 2.05                         | 2.07  | V    |

| $V_{FBC}$           | Charger feedback voltage                                                      | VSET = 10, default for T <sub>34</sub>                                  | 2.055 | 2.075                        | 2.095 | V    |

|                     |                                                                               | VSET = 11, default for T <sub>23</sub>                                  | 2.08  | 2.1                          | 2.12  |      |

|                     | Leakage current into FBC                                                      |                                                                         |       |                              | 0.1   | μΑ   |

|                     |                                                                               | VSET = 00, ENRECG = 1                                                   | 1.925 | 1.950                        | 1.975 |      |

| V                   | Charger feedback voltage for automatic                                        | VSET = 01, ENRECG = 1                                                   | 1.975 | 2                            | 2.025 | V    |

| $V_{FBCR}$          | charge restart                                                                | VSET = 10, ENRECG = 1                                                   | 2     | 2.025                        | 2.05  | v    |

|                     |                                                                               | VSET = 11, ENRECG = 1                                                   | 2.025 | 2.05                         | 2.075 |      |

| I <sub>CHARGE</sub> | Maximum charge current programming                                            |                                                                         | 1000  |                              | 4000  | mA   |

|                     | (V <sub>SRP</sub> - V <sub>SRN</sub> ) voltage to maximum charge current gain |                                                                         |       | 100                          |       | A/V  |

|                     |                                                                               | ISET = 000                                                              |       | 0%                           |       |      |

|                     |                                                                               | ISET = 001                                                              |       | 25%                          |       |      |

|                     |                                                                               | ISET = 010                                                              |       | 37.5%                        |       |      |

|                     | 12C programmable charge gurrent                                               | ISET = 011, default for $T_{12}$ and $T_{34}$ battery temperature range |       | 50%                          |       |      |

|                     | I <sup>2</sup> C programmable charge current                                  | ISET = 100                                                              |       | 62.5%                        |       |      |

|                     |                                                                               | ISET = 101                                                              |       | 75%                          |       |      |

|                     |                                                                               | ISET = 110                                                              |       | 87.5%                        |       |      |

|                     |                                                                               | ISET = 111, default for T <sub>23</sub> battery temperature range       |       | 100%                         |       |      |

|                     |                                                                               | $V_{SRP}$ - $V_{SRN}$ = 40 mV typical, $T_J$ < 100 °C                   | 38.5  | 40                           | 42.5  |      |

|                     | Charge current sense regulation voltage                                       | $V_{SRP}$ - $V_{SRN}$ = 20 mV typical, $T_J$ < 100 °C                   | 18.5  | 20                           | 22    | mV   |

|                     |                                                                               | $V_{SRP}$ - $V_{SRN}$ = 4 mV typical, $T_J$ < 100 °C                    | 2.3   | 4                            | 5.9   |      |

|                     | Minimum programmable charge current                                           |                                                                         |       | 100                          |       | mA   |

|                     | Precharge current                                                             |                                                                         |       | . 0.1 *                      |       |      |

|                     |                                                                               |                                                                         |       | I <sub>CHARGE</sub>          |       |      |

|                     | Termination current                                                           |                                                                         |       |                              |       |      |

|                     | Leakage current into SRN and SPP                                              | Vo. = < 12 V                                                            |       | CHARGE                       | 45    | μA   |

|                     | Termination current  Leakage current into SRN and SRP                         | V <sub>BAT</sub> < 12 V                                                 |       | 0.1 *<br>I <sub>CHARGE</sub> |       | 45   |

## **Electrical Characteristics - Charger (continued)**

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                   | PARAMETER                                                                                                                                                 | TEST CONDITIONS                                                             | MIN   | TYP   | MAX   | UNIT      |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-------|-------|-----------|

|                   | Switching frequency                                                                                                                                       |                                                                             | 1360  | 1600  | 1840  | kHz       |

| R <sub>DSON</sub> | High-side switch ON-resistance                                                                                                                            |                                                                             |       | 25    |       | $m\Omega$ |

| R <sub>DSON</sub> | Low-side switch ON-resistance                                                                                                                             |                                                                             |       | 60    |       | mΩ        |

| CHARG             | ER - CONTROL                                                                                                                                              |                                                                             |       |       |       |           |

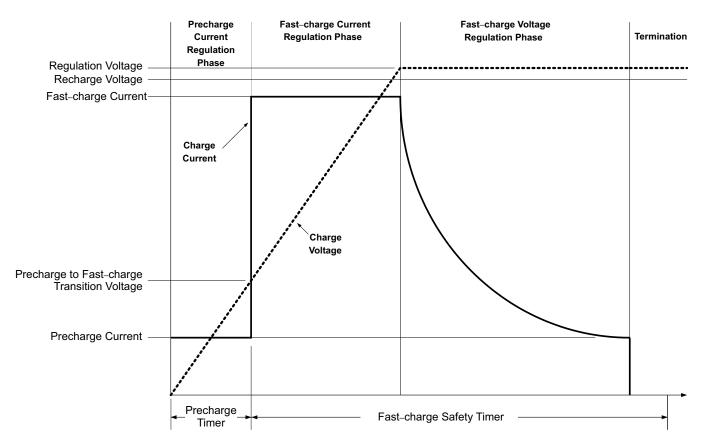

|                   | Precharge timer                                                                                                                                           |                                                                             | 1600  | 1800  | 2000  | s         |

|                   | Fast-charge safety timer programming                                                                                                                      |                                                                             | 2     |       | 10    | h         |

|                   | Fast-charge safety timer accuracy                                                                                                                         |                                                                             |       |       | 10%   |           |

|                   |                                                                                                                                                           | FASTTIME = 000, default setting                                             |       | 2     |       |           |

|                   |                                                                                                                                                           | FASTTIME = 001                                                              |       | 3     |       |           |

|                   |                                                                                                                                                           | FASTTIME = 010                                                              |       | 4     |       |           |

|                   | I <sup>2</sup> C programmable values for fast-charge                                                                                                      | FASTTIME = 011                                                              |       | 5     |       | h         |

|                   | safety timer                                                                                                                                              | FASTTIME = 100                                                              |       | 6     |       | 11        |

|                   |                                                                                                                                                           | FASTTIME = 101                                                              |       | 7     |       |           |

|                   |                                                                                                                                                           | FASTTIME = 110                                                              |       | 8     |       |           |

|                   |                                                                                                                                                           | FASTTIME = 111                                                              |       | 10    |       |           |

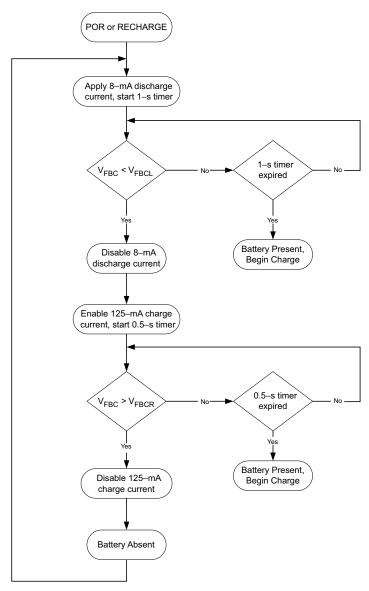

|                   | Battery detection discharge timer                                                                                                                         |                                                                             |       | 1     |       | S         |

|                   | Battery detection discharge current                                                                                                                       |                                                                             | 5     |       | 20    | mA        |

|                   | Battery detection discharge current after timer fault                                                                                                     |                                                                             |       | 2     |       | mA        |

| V <sub>FBCL</sub> | Battery detection discharge feedback voltage threshold for battery OK                                                                                     |                                                                             | 1.43  | 1.45  | 1.47  | V         |

|                   | Battery feedback voltage threshold for precharge to fast-charge transition                                                                                |                                                                             | 1.43  | 1.45  | 1.47  | V         |

|                   | Battery detection charge timer                                                                                                                            |                                                                             |       | 0.5   |       | s         |

|                   | Battery detection charge current sense regulation voltage                                                                                                 | V <sub>SRP</sub> - V <sub>SRN</sub> = 2 mV typical, T <sub>J</sub> < 100 °C | 0.5   | 2     | 3.8   | mV        |

|                   |                                                                                                                                                           | VSET = 00                                                                   | 1.925 | 1.95  | 1.975 |           |

|                   | Battery detection charge feedback voltage                                                                                                                 | VSET = 01                                                                   | 1.975 | 2     | 2.025 |           |

|                   | threshold for battery OK                                                                                                                                  | VSET = 10                                                                   | 2     | 2.025 | 2.05  | V         |

|                   |                                                                                                                                                           | VSET = 11                                                                   | 2.025 | 2.05  | 2.075 |           |

|                   | Minimum battery feedback voltage for battery good detection                                                                                               | Voltage at FBC increasing                                                   | 1.44  | 1.5   | 1.54  | V         |

|                   | Maximum battery feedback voltage for battery good detection                                                                                               | Voltage at FBC increasing                                                   | 2.18  | 2.25  | 2.28  | V         |

|                   | Battery cell temperature measurement, ratio of $V_{TS1,2}$ compared to $V_{REFTS}$ , $I^2C$ programming option for $T_1$                                  | Sensor temperature is -10°C, T_SET = 000                                    | 71.9% | 72.4% | 72.9% |           |

|                   | Voltage ratio threshold hysteresis                                                                                                                        | Sensor temperature is -10°C, voltage decreasing                             |       | 0.2%  |       |           |

| T <sub>1</sub>    | Battery cell temperature measurement, ratio of $V_{TS1,2}$ compared to $V_{REFTS}$                                                                        | Default value, Sensor temperature is 0°C, T_SET = 001                       | 70.4% | 71%   | 71.5% |           |

|                   | Voltage ratio threshold hysteresis                                                                                                                        | Sensor temperature is 0°C, voltage decreasing                               |       | 0.2%  |       |           |

| T <sub>2</sub>    | Battery cell temperature measurement, ratio of V <sub>TS1,2</sub> compared to V <sub>REFTS</sub>                                                          | Default value, Sensor temperature is 10°C, T_SET = 010                      | 68.1% | 68.7% | 69.2% |           |

|                   | Voltage ratio threshold hysteresis                                                                                                                        | Sensor temperature is 10°C, voltage decreasing                              |       | 0.4%  |       |           |

|                   | Battery cell temperature measurement, ratio of V <sub>TS1,2</sub> compared to V <sub>REFTS</sub> , I <sup>2</sup> C programming option for T <sub>2</sub> | Sensor temperature is 15°C, T_SET = 011                                     | 67%   | 67.4% | 67.9% |           |

## **Electrical Characteristics - Charger (continued)**

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                | PARAMETER                                                                                                                         | TEST CONDITIONS                                        | MIN   | TYP   | MAX   | UNIT |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|------|

|                | Voltage ratio threshold hysteresis                                                                                                | Sensor temperature is 15°C, voltage decreasing         |       | 0.4%  |       |      |

|                | Battery cell temperature measurement, ratio of $V_{TS1,2}$ compared to $V_{REFTS}$ , $I^2C$ programming option for $T_3$          | Sensor temperature is 40°C, T_SET = 100                | 59.3% | 59.7% | 60.1% |      |

|                | Voltage ratio threshold hysteresis                                                                                                | Sensor temperature is 40°C, voltage increasing         |       | 0.9%  |       |      |

| T <sub>3</sub> | Battery cell temperature measurement, ratio of $V_{TS1,2}$ compared to $V_{REFTS}$                                                | Default value, Sensor temperature is 45°C, T_SET = 101 | 57.1% | 57.6% | 57.9% |      |

|                | Voltage ratio threshold hysteresis                                                                                                | Sensor temperature is 45°C, voltage increasing         |       | 0.9%  |       |      |

|                | Battery cell temperature measurement, ratio of $V_{TS1,2}$ compared to $V_{REFTS}$ , $I^2C$ programming option for $T_3$ or $T_4$ | Sensor temperature is 50°C, T_SET = 110                | 54.7% | 55.2% | 55.8% |      |

|                | Voltage ratio threshold hysteresis                                                                                                | Sensor temperature is 50°C, voltage increasing         |       | 1.1%  |       |      |

| T <sub>4</sub> | Battery cell temperature measurement, ratio of $V_{\text{TS1,2}}$ compared to $V_{\text{REFTS}}$                                  | Default value, Sensor temperature is 60°C, T_SET = 111 | 49.6% | 50.1% | 50.5% |      |

|                | Voltage ratio threshold hysteresis                                                                                                | Sensor temperature is 60°C, voltage increasing         |       | 1.1%  |       |      |

|                | Output voltage at VREFT                                                                                                           | Internally connected to VLDO2                          |       | 3.3   |       | V    |

|                | Output impedance of VREFT                                                                                                         |                                                        |       | 4     |       | kΩ   |

|                | Quiescent current into VBAT                                                                                                       | Charging active                                        |       |       | 25    | μA   |

|                | Quiescent current into VBAT                                                                                                       | Charging suspended                                     |       |       | 150   | μA   |

| $V_{IL}$       | ENC input low voltage                                                                                                             |                                                        |       |       | 0.4   | V    |

| $V_{IH}$       | ENC input high voltage                                                                                                            |                                                        | 1.2   |       |       | V    |

|                | ENC input current                                                                                                                 | Clamped on GND or 3.3V                                 |       | 0.01  | 0.1   | μA   |

|                | Charge current derating starting temperature                                                                                      | Junction temperature increasing                        |       | 100   |       | °C   |

|                | Charge current derating starting voltage                                                                                          | V <sub>SYSC</sub> decreasing                           | 6.7   | 7.3   | 7.6   | V    |

|                | Overtemperature protection                                                                                                        |                                                        | 125   | 140   | 150   | °C   |

|                | Overtemperature hysteresis                                                                                                        |                                                        |       | 20    |       | °C   |

## 6.7 Electrical Characteristics - DC-DC Converters

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                           | PARAMETER                | TEST CONDITIONS                    | MIN  | TYP  | MAX   | UNIT      |

|---------------------------|--------------------------|------------------------------------|------|------|-------|-----------|

| DCDC1 - POWER             |                          | •                                  | •    |      | •     |           |

| Output vo                 | oltage                   | Power save mode disabled           | 5    | 5.05 | 5.125 | V         |

| Switch va                 | Illey current limit      | T <sub>A</sub> = 25°C              | 5500 |      |       | mA        |

| High-side                 | switch ON-resistance     |                                    |      | 20   |       | mΩ        |

| Low-side                  | switch ON-resistance     |                                    |      | 20   |       | $m\Omega$ |

| Maximum                   | line regulation          |                                    |      | 0.5% |       |           |

| Maximum                   | load regulation          |                                    |      | 0.5% |       |           |

| Output au                 | uto-discharge resistance |                                    |      | 300  | 400   | Ω         |

| FB1 input                 | timpedance               | V <sub>EN1</sub> = 1               |      | 1    |       | ΜΩ        |

| Shutdown                  | current into VSYS1       | V <sub>SYS1</sub> = 7.2 V, EN1 = 0 |      |      | 1     | μΑ        |

| DCDC1 - CONTR             | OL                       | •                                  | ·    |      |       |           |

| V <sub>IL</sub> EN1 input | t low voltage            |                                    |      |      | 0.4   | V         |

| V <sub>IH</sub> EN1 input | t high voltage           |                                    | 1.2  |      |       | V         |

## **Electrical Characteristics - DC-DC Converters (continued)**

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|          | PARAMETER                        | TEST CONDITIONS                    | MIN TYP   | MAX   | UNIT |

|----------|----------------------------------|------------------------------------|-----------|-------|------|

|          | EN1 input current                | Clamped on GND or 3.3 V            | 0.01      | 0.1   | μΑ   |

|          | Overtemperature protection       |                                    | 140       |       | °C   |

|          | Overtemperature hysteresis       |                                    | 20        |       | °C   |

| DCDC     | C2 - POWER                       |                                    |           |       |      |

|          | Output voltage                   | Power save mode disabled           | 3.3 3.333 | 3.383 | V    |

|          | Switch valley current limit      | T <sub>A</sub> = 25°C              | 5500      |       | mA   |

|          | High-side switch ON-resistance   |                                    | 20        |       | mΩ   |

|          | Low-side switch ON-resistance    |                                    | 20        |       | mΩ   |

|          | Maximum line regulation          |                                    | 0.5%      |       |      |

|          | Maximum load regulation          |                                    | 0.5%      |       |      |

|          | Output auto-discharge resistance |                                    | 300       | 400   | Ω    |

|          | FB2 input impedance              | V <sub>EN2</sub> = 1               | 1         |       | МΩ   |

|          | Shutdown current into VSYS2      | V <sub>SYS2</sub> = 7.2 V, EN2 = 0 |           | 1     | μA   |

| DCDC     | C2 - CONTROL                     | ,                                  | -         | '     |      |

| $V_{IL}$ | EN2 input low voltage            |                                    |           | 0.4   | V    |

| $V_{IH}$ | EN2 input high voltage           |                                    | 1.2       |       | V    |

|          | EN2 input current                | Clamped on GND or 3.3 V            | 0.01      | 0.1   | μA   |

|          | Overtemperature protection       |                                    | 140       |       | °C   |

|          | Overtemperature hysteresis       |                                    | 20        |       | °C   |

| DCDC     | C3 - POWER                       |                                    |           |       |      |

|          | Feedback voltage                 |                                    | 792 800   | 808   | mV   |

|          | Switch valley current limit      | T <sub>A</sub> = 25°C              | 4200      |       | mA   |

|          | High-side switch ON-resistance   |                                    | 20        |       | mΩ   |

|          | Low-side switch ON-resistance    |                                    | 20        |       | mΩ   |

|          | Maximum line regulation          |                                    | 0.5%      |       |      |

|          | Maximum load regulation          |                                    | 0.5%      |       |      |

|          | Output auto-discharge resistance |                                    | 300       | 400   | Ω    |

|          | Leakage current into FB3         |                                    |           | 0.1   | μΑ   |

|          | Shutdown current into VSYS3      | V <sub>SYS3</sub> = 7.2 V, EN3 = 0 |           | 1     | μΑ   |

| DCDC     | C3 - CONTROL                     |                                    |           | 1     |      |

| $V_{IL}$ | EN3 input low voltage            |                                    |           | 0.4   | V    |

| $V_{IH}$ | EN3 input high voltage           |                                    | 1.2       |       | V    |

|          | EN3 input current                | Clamped on GND or 3.3 V            | 0.01      | 0.1   | μΑ   |

|          | Overtemperature protection       |                                    | 140       |       | °C   |

|          | Overtemperature hysteresis       |                                    | 20        |       | °C   |

### 6.8 Electrical Characteristics - Linear Regulators

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

| PARAMETER                                  | TEST CONDITIONS                                                   | MIN   | TYP   | MAX | UNIT |

|--------------------------------------------|-------------------------------------------------------------------|-------|-------|-----|------|

| LD01                                       |                                                                   |       |       |     |      |

| Output voltage                             | I <sub>OUTLDO1</sub> = 1 mA                                       | 4.90  | 4.95  | 5   | V    |

| LDO1 current limit                         | $T_A = 25$ °C                                                     | 30    | 50    | 120 | mA   |

| LDO1 maximum output current                | DCDC1 active (bypass switch turned on), $V_{SYS} = 7.5 \text{ V}$ |       | 120   |     | mA   |

| Maximum line regulation                    |                                                                   |       | 0.5%  |     |      |

| Maximum load regulation                    |                                                                   |       | 0.5%  |     |      |

| FB_L1 input impedance                      |                                                                   |       | 1     |     | МΩ   |

| Quiescent current into VSYS_L1 and VSYS_L2 | DCDC1 and DCDC2 are enabled                                       |       |       | 35  | μΑ   |

| Overtemperature protection                 |                                                                   |       | 140   |     | °C   |

| Overtemperature hysteresis                 |                                                                   |       | 20    |     | °C   |

| LDO2                                       |                                                                   |       |       |     |      |

| Output voltage                             | I <sub>OUTLDO2</sub> = 1 mA                                       | 3.233 | 3.267 | 3.3 | V    |

| LDO2 current limit                         | T <sub>A</sub> = 25°C                                             | 30    | 50    | 120 | mA   |

| LDO2 maximum output current                | DCDC2 active (bypass switch turned on), V <sub>SYS</sub> = 7.5 V  |       | 120   |     | mA   |

| Maximum line regulation                    |                                                                   |       | 0.5%  |     |      |

| Maximum load regulation                    |                                                                   |       | 0.5%  |     |      |

| FB_L2 input impedance                      |                                                                   |       | 1     |     | МΩ   |

| Quiescent current into VSYS_L2 and VSYS_L1 | DCDC1 and DCDC2 are enabled                                       |       |       | 35  | μΑ   |

| Overtemperature protection                 |                                                                   |       | 140   |     | °C   |

| Overtemperature hysteresis                 |                                                                   |       | 20    |     | °C   |

### 6.9 Electrical Characteristics - Load Switches

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

| PARAMETER                                     | TEST CONDITIONS                        | MIN  | TYP | MAX  | UNIT   |

|-----------------------------------------------|----------------------------------------|------|-----|------|--------|

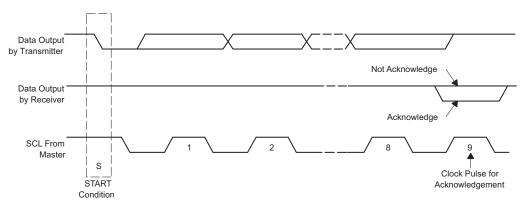

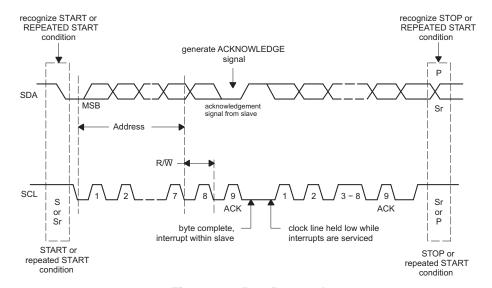

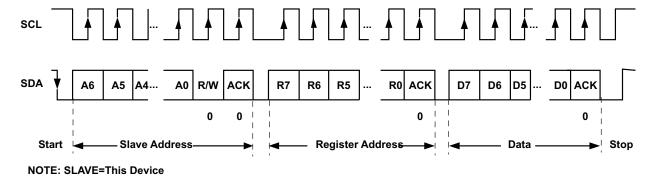

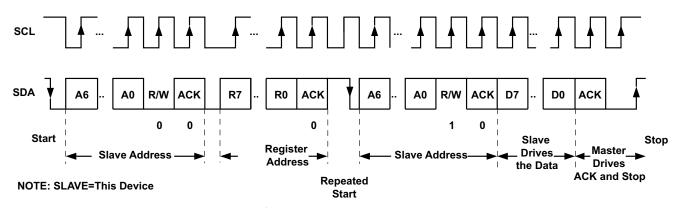

| FET1                                          |                                        |      |     |      |        |