### **Features and Benefits**

- Chopper stabilization for stable switchpoints throughout operating temperature range

- User-programmable:

- Magnetic operate point through the VCC pin:9 programming bits provide 4-gauss resolution

- Output polarity

- Output fall time for reduced EMI in automotive applications

- On-board voltage regulator for 3 to 24 V operation

- On-chip protection against:

- Supply transients

- Output short-circuits

- Reverse battery condition

- True Zero-Speed Operation

- True Power-On State

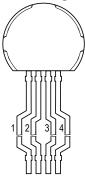

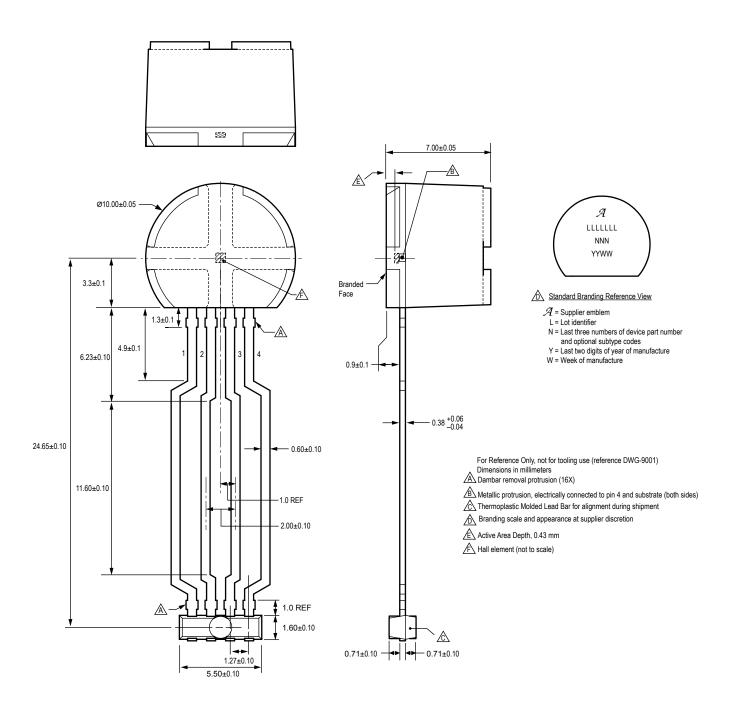

## Package: 4-pin SIP (suffix SE)

## **Description**

The ATS128LSE programmable, true power-on state (TPOS), sensor IC is an optimized combination of Hall-effect IC and rare-earth pellet that switches in response to magnetic signals created by ferromagnetic targets in gear-tooth sensing and proximity sensing applications.

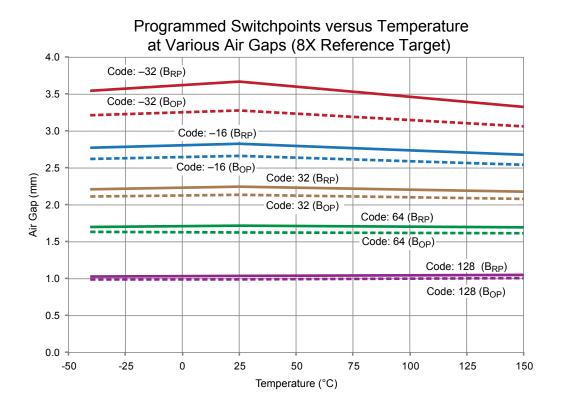

These devices offer a wide programming range for the magnetic operate point,  $B_{OP}$ . A fixed hysteresis then sets the magnetic release point,  $B_{RP}$ , based on the selected  $B_{OP}$ .

The devices are externally programmable. A wide range of programmability is available on the magnetic operate point,  $B_{OP}$ , while the hysteresis remains fixed. This advanced feature allows optimization of the sensor IC switchpoint and can drastically reduce the effects of mechanical placement tolerances found in production environments.

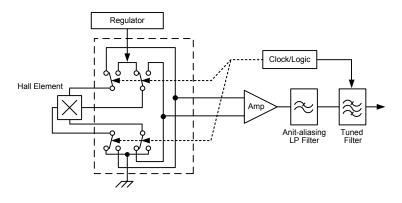

A proprietary dynamic offset cancellation technique, with an internal high-frequency clock, reduces the residual offset voltage, which is normally caused by device overmolding, temperature dependencies, and thermal stress. Having the Hall element and amplifier in a single chip minimizes many problems normally associated with low-level analog signals.

This device is ideal for use in gathering speed or position information using gear-tooth-based configurations, or for proximity sensing with ferromagnetic targets.

The ATS128 is provided in a 4-pin SIP. It is lead (Pb) free, with 100% matte tin leadframe plating.

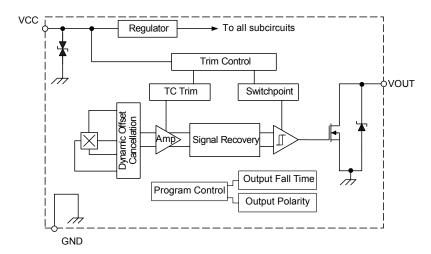

## **Functional Block Diagram**

# Highly Programmable, Back-Biased, Hall-Effect Switch with TPOS Functionality

## **Selection Guide**

| Part Number   | Packing*                   |

|---------------|----------------------------|

| ATS128LSETN-T | 450 pieces per 13-in. reel |

| ma r          |                            |

<sup>\*</sup>Contact Allegro<sup>TM</sup> for additional packing options

### **Absolute Maximum Ratings**

| Characteristic                | Symbol                 | Notes                                                                                                                                 | Rating     | Unit |

|-------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------|------|

| Forward Supply Voltage        | V <sub>CC</sub>        |                                                                                                                                       | 28         | V    |

| Reverse Supply Voltage        | V <sub>RCC</sub>       |                                                                                                                                       | -18        | V    |

| Forward Output Voltage        | V <sub>OUT</sub>       |                                                                                                                                       | 28         | V    |

| Reverse Output Voltage        | V <sub>ROUT</sub>      |                                                                                                                                       | -0.7       | V    |

| Output Current Sink           | I <sub>OUT(SINK)</sub> | Internal current limiting is intended to protect the device from output short circuits, but is not intended for continuous operation. | 20         | mA   |

| Operating Ambient Temperature | T <sub>A</sub>         | L temperature range                                                                                                                   | -40 to 150 | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max)   |                                                                                                                                       | 165        | °C   |

| Storage Temperature           | T <sub>stg</sub>       |                                                                                                                                       | -65 to 170 | °C   |

## **Pin-out Diagram**

### **Terminal List Table**

| Number | Name | Function           |  |  |  |

|--------|------|--------------------|--|--|--|

| 1      | VCC  | Input power supply |  |  |  |

| 2      | VOUT | Output signal      |  |  |  |

| 3      | NC   | No connect         |  |  |  |

| 4      | GND  | Ground             |  |  |  |

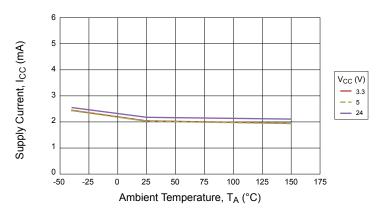

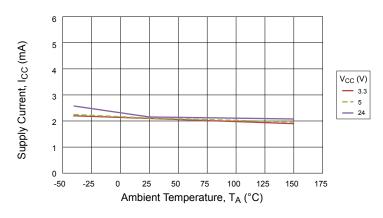

**OPERATING CHARACTERISTICS** Valid with  $T_A = -40$ °C to 150°C,  $C_{BYPASS} = 0.1 \mu F$ ,  $V_{CC} = 12 \text{ V}$ , unless otherwise noted

| Characteristics               | Symbol                |                                                                                         | Min.                                                                                                                 | Тур. | Max. | Unit |     |

|-------------------------------|-----------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|------|------|-----|

| Electrical Characteristics    |                       |                                                                                         |                                                                                                                      |      |      |      |     |

| Supply Voltage                | V <sub>CC</sub>       |                                                                                         |                                                                                                                      |      |      | 24   | V   |

| Supply Current                | I <sub>cc</sub>       | No load on VC                                                                           | DUT                                                                                                                  | _    | _    | 5.5  | mA  |

| Supply Zener Clamp Voltage    | V <sub>ZSUPPLY</sub>  | T <sub>A</sub> = 25°C, I <sub>CC</sub>                                                  | = I <sub>CC</sub> (max) + 3 mA                                                                                       | 28   | _    | _    | V   |

| Supply Zener Current          | I <sub>ZSUPPLY</sub>  | V <sub>CC</sub> = 28 V                                                                  |                                                                                                                      | _    | _    | 8.5  | mA  |

| Output Zener Clamp Voltage    | V <sub>ZOUTPUT</sub>  | I <sub>OUT</sub> = 3 mA                                                                 |                                                                                                                      | 28   | _    | _    | V   |

| Reverse Battery Current       | I <sub>RCC</sub>      | V <sub>CC</sub> = -18 V                                                                 |                                                                                                                      | -5   | _    | _    | mA  |

| Chopping Frequency            | f <sub>C</sub>        |                                                                                         |                                                                                                                      | _    | 400  | _    | kHz |

| Power-On Characteristics      |                       |                                                                                         |                                                                                                                      |      |      |      |     |

| Power-On Time <sup>1</sup>    | t <sub>PO</sub>       | T <sub>A</sub> = 25°C; C <sub>LC</sub>                                                  | DAD (PROBE) = 10 pF                                                                                                  | _    | _    | 30   | μs  |

| Daniel On Otate?              | DOO                   | POL = 0                                                                                 | $B < B_{RP}, t > t_{on}$                                                                                             | _    | High | _    | _   |

| Power-On State <sup>2</sup>   | POS                   | POL = 1                                                                                 | $B < B_{RP}$ , $t > t_{on}$                                                                                          | _    | Low  | _    | _   |

| Output Stage Characteristics  | ·                     |                                                                                         |                                                                                                                      |      |      |      |     |

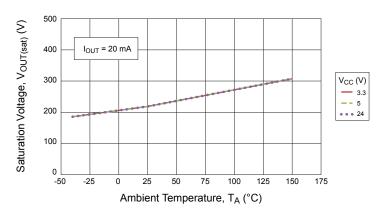

| Output Saturation Voltage     | V <sub>OUT(sat)</sub> | Output = On, I <sub>OUT</sub> = 20 mA                                                   |                                                                                                                      | _    | 175  | 400  | mV  |

| Output Leakage Current        | I <sub>OFF</sub>      | V <sub>OUT</sub> = 24 V; (                                                              | Output = Off                                                                                                         | _    | _    | 10   | μΑ  |

| Output Current Limit          | I <sub>OUT(lim)</sub> | Short-Circuit F                                                                         | Protection, Output = On                                                                                              | 30   | _    | 90   | mA  |

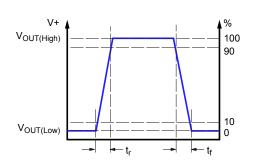

| Outrot Disa Tima 3            |                       | V <sub>CC</sub> = 12 V, R <sub>F</sub><br>see figure 1                                  | $_{PU}$ = 820 $\Omega$ , $C_{LOAD}$ = 10 pF,                                                                         | _    | _    | 2    | μs  |

| Output Rise Time <sup>3</sup> | t <sub>r</sub>        | V <sub>CC</sub> = 12 V, R <sub>F</sub><br>see figure 1                                  | $P_U = 2 \text{ k}\Omega$ , $C_{LOAD} = 4.7 \text{ nF}$ ,                                                            | _    | 21   | _    | μs  |

|                               |                       | FALL = 0                                                                                | $V_{CC}$ = 12 V, $R_{LOAD}$ = 820 Ω, $C_{LOAD}$ = 10 pF, see figure 1                                                | _    | _    | 2    | μs  |

| Output Fall Time <sup>4</sup> |                       | FALL = 1                                                                                | FALL = 1 $V_{CC} = 12 \text{ V}, R_{LOAD} = 2 \text{ k}\Omega,$<br>$C_{LOAD} = 4.7 \text{ nF}, \text{ see figure 1}$ |      | _    | 10   | μs  |

|                               | t <sub>f</sub>        | FALL = 3 $V_{CC}$ = 12 V, $R_{LOAD}$ = 2 k $\Omega$ , $C_{LOAD}$ = 4.7 nF, see figure 1 |                                                                                                                      | 8    | _    | 13   | μs  |

|                               |                       | FALL = 4                                                                                | V12 V B 2 kO                                                                                                         |      |      | 16   | μs  |

Continued on the next page...

Figure 1. Rise Time and Fall Time Definitions

# Highly Programmable, Back-Biased, Hall-Effect Switch with TPOS Functionality

## **OPERATING CHARACTERISTICS** (continued) Valid with $T_A = -40^{\circ}\text{C}$ to 150°C, $C_{BYPASS} = 0.1 \, \mu\text{F}$ , $V_{CC} = 12 \, \text{V}$ ,

unless otherwise noted

| Characteristics                                      | Symbol                   |                                                                   | Min.                                  | Тур.        | Max. | Unit |     |

|------------------------------------------------------|--------------------------|-------------------------------------------------------------------|---------------------------------------|-------------|------|------|-----|

| Output Stage Characteristics (continue               | d)                       |                                                                   |                                       |             |      |      |     |

|                                                      |                          | POL = 0                                                           | B > B <sub>OP</sub> , opposite tooth  | _           | Low  | _    | -   |

| Output Polarity <sup>2</sup>                         | POL                      | POL - U                                                           | B < B <sub>RP</sub> , opposite valley | _           | High | -    | _   |

| Output Folanty-                                      | POL                      | POL = 1                                                           | B > B <sub>OP</sub> , opposite tooth  | _           | High | -    | _   |

|                                                      |                          | POL - I                                                           | B < B <sub>RP</sub> , opposite valley | _           | Low  | -    | _   |

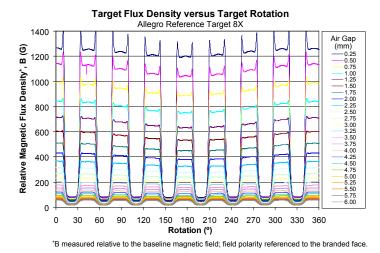

| Magnetic Characteristics valid $V_{CC} = 3 t$        | o 24 V, T <sub>J</sub> ≤ | T <sub>J</sub> (max), using                                       | Allegro 8X reference target, unless   | otherwise n | oted |      |     |

| Air Gap Setpoint Drift Over Temperature <sup>5</sup> | AG <sub>Drift</sub>      | Device progra                                                     | ammed with air gap of 2.5 mm          | _           | ±0.2 | _    | mm  |

| <b>Programming Characteristics</b>                   |                          |                                                                   |                                       |             |      |      |     |

| Switchpoint Magnitude Selection Bits                 | Bit <sub>BOPSEL</sub>    |                                                                   |                                       | _           | 8    | _    | Bit |

| Switchpoint Polarity Bits                            | Bit <sub>BOPPOL</sub>    |                                                                   |                                       | _           | 1    | _    | Bit |

| Output Polarity Bits                                 | Bit <sub>POL</sub>       |                                                                   |                                       | _           | 1    | _    | Bit |

| Fall Time Bits                                       | Bit <sub>FALL</sub>      |                                                                   |                                       | _           | 2    | -    | Bit |

| Device Lock Bits                                     | Bit <sub>LOCK</sub>      |                                                                   |                                       | _           | 1    | -    | Bit |

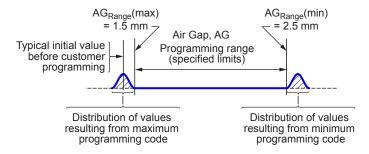

|                                                      |                          | T <sub>A</sub> = 25°C, Minimum code (BOPPOL = 1,<br>BOPSEL = 255) |                                       | 2.5         | _    | _    | mm  |

| Programmable Air Gap Range <sup>6,7</sup>            | AG <sub>Range</sub>      | T <sub>A</sub> = 25°C, M<br>BOPSEL = 25                           | aximum code (BOPPOL = 0,<br>55)       | _           | _    | 1.5  | mm  |

| AG <sub>Range</sub> Programming Resolution           | Res <sub>AG</sub>        | T <sub>A</sub> = 25°C, de<br>2.5 mm                               | evice programmed with air gap of      | _           | 0.05 | -    | mm  |

<sup>&</sup>lt;sup>1</sup>Determined by design and device characterization.

<sup>&</sup>lt;sup>2</sup>Output state when device configured as shown in figure 4.

<sup>&</sup>lt;sup>3</sup>Output Rise Time is governed by external circuit tied to VOUT. Measured from 10% to 90% of steady state output.

<sup>&</sup>lt;sup>4</sup>Measured from 90% to 10% of steady state output.

<sup>&</sup>lt;sup>5</sup>Switchpoint varies with temperature, proportionally to the programmed air gap. This parameter is based on characterization data and is not a tested parameter in production. The AG<sub>Drift</sub> value trends smaller as temperature increases.

<sup>&</sup>lt;sup>6</sup>Switchpoint varies with temperature. A sufficient margin, obtained through customer testing, is recommended to ensure functionality across the operating temperature range. Programming at larger air gaps leaves less margin for switchpoint drift.

<sup>7</sup>At the minimum code setpoint (BOPSEL = 255, BOPPOL = 1), the switchpoint can correspond to an air gap greater than 2.5 mm, and at maximum code setpoint (BOPSEL = 255, BOPPOL = 0), the switchpoint can correspond to an air gap smaller than 1.5 mm.

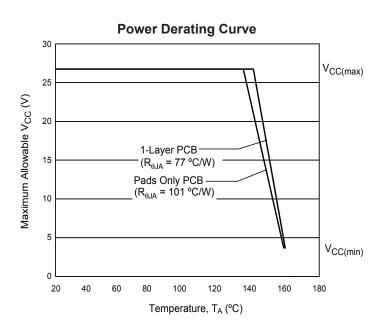

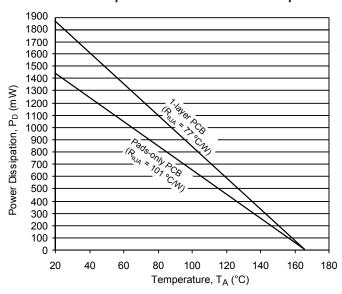

THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

| Characteristic             | Symbol              | Symbol Test Conditions*                                                                                                    |     |      |

|----------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------|-----|------|

|                            | _                   | 1-layer PCB with copper limited to solder pads                                                                             | 101 | °C/W |

| Package Thermal Resistance | ance $R_{	heta JA}$ | 1-layer PCB with copper limited to solder pads and 3.57 in. <sup>2</sup> (23.03 cm <sup>2</sup> ) of copper area each side | 77  | °C/W |

<sup>\*</sup>Additional information is available on the Allegro Web site.

## **Power Dissipation versus Ambient Temperature**

## **Characteristic Performance**

## Supply Current (On) versus Ambient Temperature

## **Supply Current (Off) versus Ambient Temperature**

## **Saturation Voltage versus Ambient Temperature**

## **Functional Description**

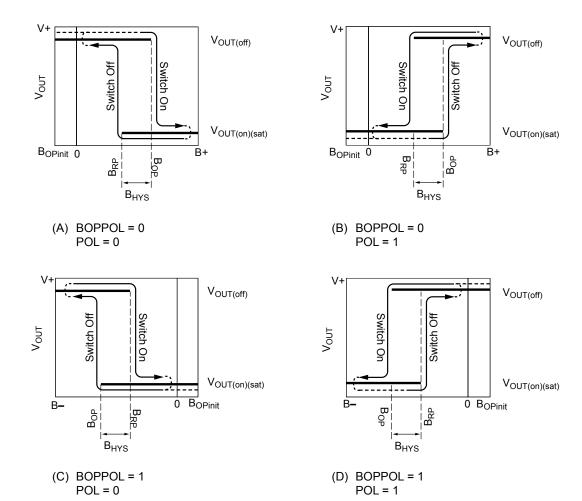

When the Output Polarity bit is not set (POL = 0), the ATS128 output switches on after the magnetic field at the Hall sensor IC exceeds the operate point threshold,  $B_{OP}.$  When the magnetic field is reduced to below the release point threshold,  $B_{RP}$ , the device output switches off. The difference between the magnetic operate and release points is called the hysteresis of the device,  $B_{HYS}.$

In the alternative case, in which the Output Polarity bit is set (POL = 1), the ATS128 output switches off when the magnetic field at the Hall sensor IC exceeds the operate point threshold,  $B_{OP}$ . When the magnetic field is reduced to below the release point threshold,  $B_{RP}$ , the device output switches on.

Figure 2. Hysteresis Diagrams. These plots demonstrate the behavior of the ATS128 with the applied magnetic field impinging on the branded face of the device case (refer to Package Outline Drawings section). On the horizontal axis, the B+ direction indicates increasing south or decreasing north magnetic flux density, and the B- direction indicates increasing north or decreasing south magnetic flux density.

# Highly Programmable, Back-Biased, Hall-Effect Switch with TPOS Functionality

### Air Gap Operating Range

The Programmable Air Gap Range,  $AG_{Range}$ , can be programmed around the zero crossing point, within the range limits:  $AG_{Range}(min)$  and  $AG_{Range}(max)$ . The available programming range for  $AG_{Range}$  falls within the distributions of the initial, minimum code setpoint (BOPSEL = 255, BOPPOL = 1), and the maximum code setpoint (BOPSEL = 255, BOPPOL = 0). The switchpoint can correspond to an air gap smaller than 1.5 mm or larger than 2.5 mm, as shown in figure 3.

Figure 3. On the horizontal axis, the operating air gap may exceed the recommended range for switching. The maximum and minimum values for the actual operating air gap range are described by distributions of the maximum and minimum code setpoints.

## **Application Information**

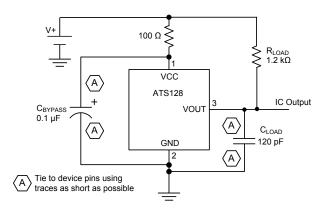

Figure 4. Typical Application Circuit

## **Chopper Stabilization Technique**

When using Hall-effect technology, a limiting factor for switchpoint accuracy is the small signal voltage developed across the Hall element. This voltage is disproportionally small relative to the offset that can be produced at the output of the Hall sensor IC. This makes it difficult to process the signal while maintaining an accurate, reliable output over the specified operating temperature and voltage ranges. Chopper stabilization is a unique approach used to minimize Hall offset on the chip. Allegro employs a technique to remove key sources of the output drift induced by thermal and mechanical stresses. This offset reduction technique is based on a signal modulation-demodulation process. The undesired offset signal is separated from the magnetic fieldinduced signal in the frequency domain, through modulation. The subsequent demodulation acts as a modulation process for the offset, causing the magnetic field-induced signal to recover its original spectrum at base band, while the DC offset becomes a high-frequency signal. The magnetic-sourced signal then can

pass through a low-pass filter, while the modulated DC offset is suppressed. In addition to the removal of the thermal and stress related offset, this novel technique also reduces the amount of thermal noise in the Hall sensor IC while completely removing the modulated residue resulting from the chopper operation. The chopper stabilization technique uses a high frequency sampling clock. For demodulation process, a sample and hold technique is used. This high-frequency operation allows a greater sampling rate, which results in higher accuracy and faster signal-processing capability. This approach desensitizes the chip to the effects of thermal and mechanical stresses, and produces devices that have extremely stable quiescent Hall output voltages and precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process, which allows the use of low-offset, low-noise amplifiers in combination with highdensity logic integration and sample-and-hold circuits.

Figure 5. Concept of Chopper Stabilization Technique

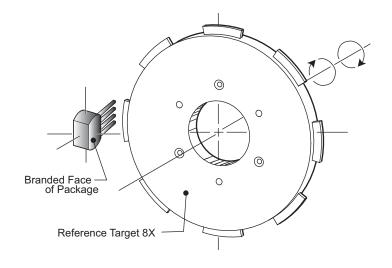

## **Reference Target Characteristics**

#### **REFERENCE TARGET 8X**

| Characteristic         | Symbol         | Test Conditions                                                            | Тур. | Units | Symbol Key              |

|------------------------|----------------|----------------------------------------------------------------------------|------|-------|-------------------------|

| Outside Diameter       | D <sub>o</sub> | Outside diameter of target                                                 | 120  | mm    | an h <sub>ta</sub>      |

| Face Width             | F              | Breadth of tooth, with respect to branded face                             | 6    | mm    | Branded Face of Package |

| Circular Tooth Length  | t              | Length of tooth, with respect to branded face; measured at D <sub>o</sub>  | 23.6 | mm    |                         |

| Circular Valley Length | t <sub>v</sub> | Length of valley, with respect to branded face; measured at D <sub>o</sub> | 23.6 | mm    |                         |

| Tooth Whole Depth      | h <sub>t</sub> |                                                                            | 5    | mm    |                         |

| Material               |                | CRS 1018                                                                   | _    | _     | Air Gap                 |

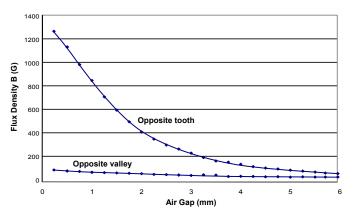

## Target/Gear Parameters for Correct Operation

For correct operation, TPOS or continuous, the target must generate a minimum difference between the applied flux density over a tooth and the applied flux density over a valley, at the maximum installation air gap.

The following recommendations should be followed in the design and specification of targets:

- Face Width,  $F \ge 5 \text{ mm}$

- Circular Tooth Length,  $t \ge 5$  mm

- Circular Valley Length, t<sub>v</sub> > 13 mm

- Whole Tooth Depth,  $h_t > 5 \text{ mm}$

Reference Gear Magnetic Gradient Amplitude versus Air Gap

## **Programming Guidelines**

#### Overview

Programming is accomplished by sending a series of input voltage pulses serially through the VCC (supply) pin of the device. A unique combination of different voltage level pulses controls the internal programming logic of the device to select a desired programmable parameter and change its value. There are three voltage levels that must be taken into account when programming. These levels are referred to as  $high\ (V_{PH}), mid\ (V_{PM}),$  and low  $(V_{PL})$ .

The ATS128 features three programmable modes, Try mode, Blow mode, and Read mode:

- In Try mode, programmable parameter values are set and measured simultaneously. A parameter value is stored temporarily, and reset after cycling the supply voltage.

- In Blow mode, the value of a programmable parameter may be permanently set by blowing solid-state fuses internal to the device. Device locking is also accomplished in this mode.

- In Read mode, each bit may be verified as blown or not blown.

The programming sequence is designed to help prevent the device from being programmed accidentally; for example, as a result of noise on the supply line. Note that, for all programming modes, no parameter programming registers are accessible after the device-level LOCK bit is set. The only function that remains accessible is the overall Fuse Checking feature.

Although any programmable variable power supply can be used to generate the pulse waveforms, for design evaluations, Allegro

highly recommends using the Allegro Sensor IC Evaluation Kit, available on the Allegro website On-line Store. The manual for that kit is available for download free of charge, and provides additional information on programming these devices. (Note: This kit is not recommended for production purposes.)

#### **Definition of Terms**

**Register** The section of the programming logic that controls the choice of programmable modes and parameters.

**Bit Field** The internal fuses unique to each register, represented as a binary number. Changing the bit field settings of a particular

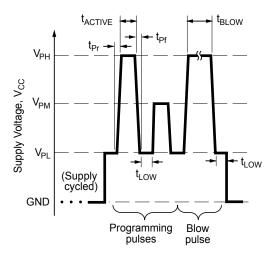

Figure 6. Programming pulse definitions (see table 1)

Table 1. Programming Pulse Requirements, Protocol at  $T_A = 25^{\circ}C$

| Characteristics                 | Symbol             | Notes                                                                                                                           | Min.  | Тур. | Max. | Unit |

|---------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

|                                 | V <sub>PL</sub>    |                                                                                                                                 | 4.5   | 5    | 5.5  | V    |

| Programming Voltage             | $V_{PM}$           | Measured at the VCC pin                                                                                                         | 12.5  | _    | 14   | V    |

|                                 | $V_{PH}$           |                                                                                                                                 | 21    | _    | 27   | V    |

| Programming Current             | I <sub>PP</sub>    | $V_{CC}$ = 5 $\rightarrow$ 26 V, $C_{BLOW}$ = 0.1 $\mu F$ (min); minimum supply current required to ensure proper fuse blowing. | 175   | ı    | -    | mA   |

|                                 | t <sub>LOW</sub>   | Duration of $V_{PL}$ separating pulses at $V_{PM}$ or $V_{PH}$                                                                  | 20    | ı    | _    | μs   |

| Pulse Width t <sub>ACTIVE</sub> |                    | Duration of pulses at V <sub>PM</sub> or V <sub>PH</sub> for key/code selection                                                 | 20    | _    | _    | μs   |

|                                 | t <sub>BLOW</sub>  | Duration of pulse at V <sub>PH</sub> for fuse blowing                                                                           | 90    | 100  | _    | μs   |

| Pulse Rise Time                 | t <sub>Pr</sub>    | $V_{PL}$ to $V_{PM}$ or $V_{PL}$ to $V_{PH}$                                                                                    | 5     | _    | 100  | μs   |

| Pulse Fall Time                 | t <sub>Pf</sub>    | V <sub>PM</sub> to V <sub>PL</sub> or V <sub>PH</sub> to V <sub>PL</sub>                                                        | 5     | _    | 100  | μs   |

| Blow Pulse Slew Rate            | SR <sub>BLOW</sub> |                                                                                                                                 | 0.375 | _    | _    | V/µs |

# Highly Programmable, Back-Biased, Hall-Effect Switch with TPOS Functionality

register causes its programmable parameter to change, based on the internal programming logic.

**Key** A series of voltage pulses used to select a register or mode.

**Code** The number used to identify the combination of fuses activated in a bit field, expressed as the decimal equivalent of the binary value. The LSB of a bit field is denoted as code 1, or bit 0.

**Addressing** Increasing the bit field code of a selected register by serially applying a pulse train through the VCC pin of the device. Each parameter can be measured during the addressing process, but the internal fuses must be blown before the programming code (and parameter value) becomes permanent.

**Fuse Blowing** Applying a high voltage pulse of sufficient duration to permanently set an addressed bit by blowing a fuse internal to the device. Once a bit (fuse) has been blown, it cannot be reset.

**Blow Pulse** A high voltage pulse of sufficient duration to blow the addressed fuse.

**Cycling the Supply** Powering-down, and then powering-up the supply voltage. Cycling the supply is used to clear the programming settings in Try mode.

## **Programming Procedure**

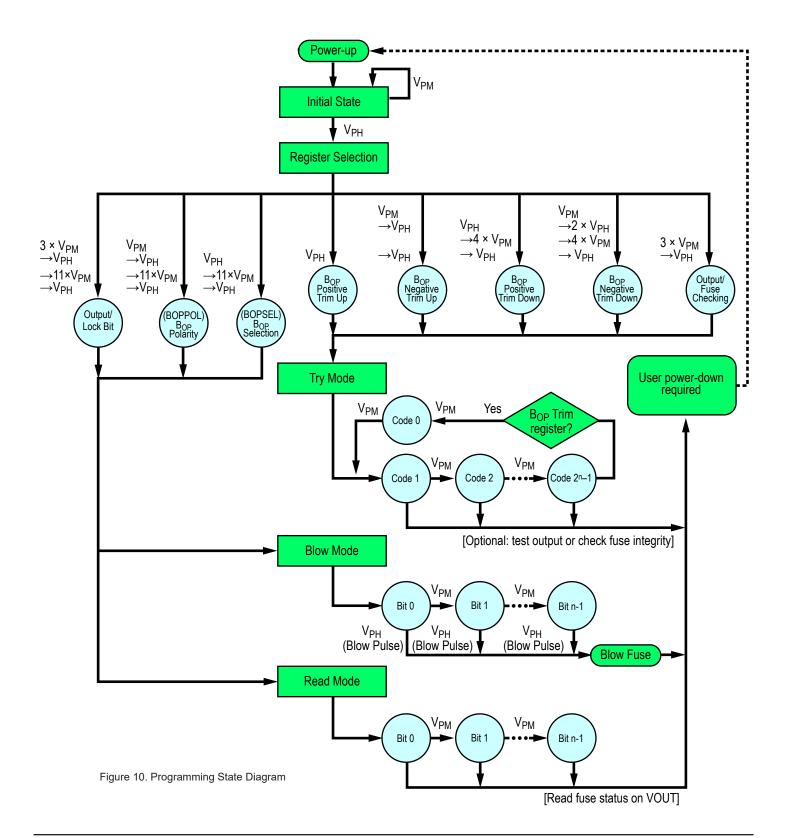

Programming involves selection of a register and mode, and then setting values for parameters in the register for evaluation or fuse blowing. Figure 10 provides an overview state diagram.

### **Register Selection**

Each programmable parameter can be accessed through a specific register. To select a register, from the Initial state, a sequence of voltage pulses consisting of one  $V_{PH}$  pulse, one  $V_{PM}$  pulse, and then a unique combination of  $V_{PH}$  and  $V_{PM}$  pulses, is applied serially to the VCC pin (with no  $V_{CC}$  supply interruptions). This sequence of pulses is called the key, and uniquely identifies each register. An example register selection key is shown in figure 7.

Figure 7. Example of Try mode register selection pulses, for the  $B_{\text{OP}}$  Negative Trim, Up-Counting register.

To simplify Try mode, the ATS128 provides a set of four virtual registers, one for each combination of:  $B_{OP}$  selection (BOPSEL),  $B_{OP}$  polarity (BOPPOL), and a facility for transiting  $B_{OP}$  magnitude values in an increasing or decreasing sequence. These registers also allow wrapping back to the beginning of the register after transiting the register.

#### **Mode Selection**

The same physical registers are used for all programming modes. To distinguish the Blow mode and Read mode, when selecting the registers an additional pulse sequence consisting of eleven  $V_{PM}$  pulses followed by one  $V_{PH}$  pulse is added to the key. The combined register and mode keys are shown in table 3.

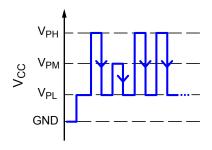

### **Try Mode**

In Try mode, the bit field addressing is accomplished by applying a series of V<sub>PM</sub> pulses to the VCC pin of the device, as shown in figure 7. Each pulse increases the total bit field value of the selected parameter, increasing by one on the falling edge of each additional V<sub>PM</sub> pulse. When addressing a bit field in Try mode, the number of V<sub>PM</sub> pulses is represented by a decimal number called a code. Addressing activates the corresponding fuse locations in the given bit field by increasing the binary value of an internal DAC, up to the maximum possible code. As the value of the bit field code increases, the value of the programmable parameter changes. Measurements can be taken after each V<sub>PM</sub> pulse to determine if the desired result for the programmable parameter has been reached. Cycling the supply voltage resets all the locations in the bit field that have un-blown fuses to their initial states. This should also be done before selection of a different register in Try mode.

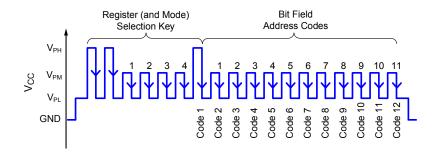

When addressing a parameter in Try mode, the bit field address (code) defaults to the value 1, on the falling edge of the final register selection key  $V_{PH}$  pulse (see figure 8). A complete example is shown figure 12. Note that, in the four  $B_{OP}$  selection virtual registers, after the maximum code is entered, the next  $V_{PM}$  pulse wraps back to the beginning of the register, and selects code 0.

Figure 8. Try mode bit field addressing pulses.

# Highly Programmable, Back-Biased, Hall-Effect Switch with TPOS Functionality

The four  $B_{OP}$  selecting virtual registers allow the programmer to adjust the  $B_{OP}$  parameter for use with a wide magnetic field range. In addition, values can be traversed from low to high, or from high to low. Figure 12 shows the relationship between the  $B_{OP}$  parameter and the different Try mode registers. Note: See the Output Polarity section for information about setting the POL bit before using Try mode.

The FALL and POL fields are in the same register (FALL is bits 1:0, and POL is bit 2). Therefore, in Try mode both can be programmed simultaneously by adding the codes for the two parameters, and send the sum as the code. For example, sending code 7 (111) sets FALL to 3 (x11) and sets POL (1xx).

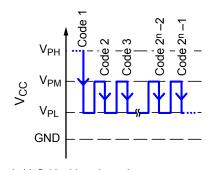

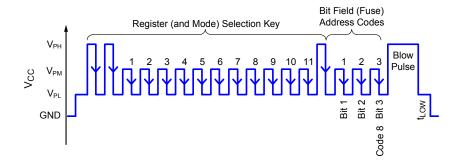

#### **Blow Mode**

After the required code is determined for a given parameter, its value can be set permanently by blowing individual fuses in the appropriate register bit field. Blowing is accomplished by selecting the register and mode selection key, followed by the appropriate bit field address, and ending the sequence with a Blow pulse. The Blow mode selection key is a sequence of eleven  $V_{PM}$  pulses followed by one  $V_{PH}$  pulse. The Blow pulse consists of a  $V_{PH}$  pulse of sufficient duration,  $t_{BLOW}$ , to permanently set an addressed bit by blowing a fuse internal to the device. The device power must be cycled after each individual fuse is blown.

A 0.1  $\mu$ F blowing capacitor,  $C_{BLOW}$ , must be mounted between the VCC pin and the GND pin during programming, to ensure enough current is available to blow fuses. If programming in the application,  $C_{BYPASS}$  (see figure 4) can serve the same purpose.

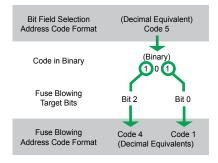

Due to power requirements, the fuse for each bit in the bit field must be blown individually. The ATS128 built-in circuitry allows only one fuse at a time to be blown. During Blow mode, the bit field can be considered a one-hot shift register. Table 2 illustrates how to relate the number of  $V_{PM}$  pulses to the binary and decimal value for Blow mode bit field addressing. It should be noted that the simple relationship between the number of  $V_{PM}$  pulses and the required code is:

$$2^n = \text{Code},$$

where n is the number of  $V_{PM}$  pulses, and the bit field has an initial state of decimal code 1 (binary 00000001). To correctly blow the required fuses, the code representing the required parameter value must be translated to a binary number. For example, as shown in figure 9, decimal code 5 is equivalent to the binary number 101. Therefore bit 2 must be addressed and blown, the device power supply cycled, and then bit 0 must be addressed and blown. The order of blowing bits, however, is not important. Blowing bit 0 first, and then bit 2 is acceptable. A complete example is shown in figure 13.

Note: After blowing, the programming is not reversible, even after cycling the supply power. Although a register bit field fuse cannot be reset after it is blown, additional bits within the same register can be blown at any time until the device is locked. For example, if bit 1 (binary 10) has been blown, it is still possible to blow bit 0. The end result would be binary 11 (decimal code 3).

### **Locking the Device**

After the required code for each parameter is programmed, the device can be locked to prevent further programming of any parameters. To do so, perform the following steps:

- 1. Ensure that the  $C_{\mbox{\footnotesize BLOW}}$  capacitor is mounted.

- 2. Select the Output/Lock Bit register key.

- 3. Select Blow mode selection key.

- 4. Address bit 4 (10000) by sending four V<sub>PM</sub> pulses.

- 5. Send one Blow pulse, at  $\rm I_{PP}$  and  $\rm SR_{BLOW}$ , and sustain it for  $\rm t_{BLOW}$

- 6. Delay for a t<sub>LOW</sub> interval, then power-down.

- 7. Optionally check all fuses.

Table 2. Blow Mode Bit Field Addressing

| Quantity of V <sub>PM</sub> Pulses | Binary<br>Register Bit Field | Decimal Equivalent<br>Code |

|------------------------------------|------------------------------|----------------------------|

| 0                                  | 0000001                      | 1                          |

| 1                                  | 0000010                      | 2                          |

| 2                                  | 00000100                     | 4                          |

| 3                                  | 00001000                     | 8                          |

| 4                                  | 00010000                     | 16                         |

| 5                                  | 00100000                     | 32                         |

| 6                                  | 01000000                     | 64                         |

| 7                                  | 10000000                     | 128                        |

Figure 9. Example of code 5 broken into its binary components.

# Highly Programmable, Back-Biased, Hall-Effect Switch with TPOS Functionality

**Table 3. Programming Logic Table**

| Pogistor Nama                                                                                                                         | Bit Field Add       | ress (Code)           |                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Name<br>[Selection Key]                                                                                                      | Binary<br>(MSB→LSB) | Decimal<br>Equivalent | Notes                                                                                                                                                           |

| Try Mode Register Selections <sup>1</sup>                                                                                             |                     |                       |                                                                                                                                                                 |

| B <sub>OP</sub> Positive, Trim Up-Counting                                                                                            | 00000000            | 0                     | Increase B <sub>OP</sub> (South field), wraps back to code 0.                                                                                                   |

| [ 2×V <sub>PH</sub> ]                                                                                                                 | 11111111            | 255                   | B <sub>OP</sub> selection is at maximum value.                                                                                                                  |

| B <sub>OP</sub> Negative, Trim Up-Counting                                                                                            | 00000000            | 0                     | Increase B <sub>OP</sub> (North field), wraps back to code 0.                                                                                                   |

| $[V_{PH} \rightarrow V_{PM} \rightarrow 2 \times V_{PH}]$                                                                             | 11111111            | 255                   | B <sub>OP</sub> selection is at maximum value.                                                                                                                  |

| B <sub>OP</sub> Positive, Trim Down-Counting                                                                                          | 11111111            | 0                     | Decrease $B_{OP}$ (South field), wraps back to code 0. Code is automatically inverted (code 1 selects $B_{OP}$ selection maximum value minus 1.)                |

| $[2 \times V_{PH} \rightarrow 4 \times V_{PM} \rightarrow V_{PH}]$                                                                    | 00000000            | 255                   | B <sub>OP</sub> selection is at minimum value.                                                                                                                  |

| $B_{OP}$ Negative, Trim Down-Counting $[V_{PH} \rightarrow V_{PM} \rightarrow 2 \times V_{PH}]$                                       | 11111111            | 0                     | Decrease $B_{OP}$ (North field), wraps back to code 0. Code is automatically inverted (code 1 selects $B_{OP}$ selection maximum value minus 1.)                |

| $\rightarrow$ 4 × $V_{PM} \rightarrow V_{PH}$ ]                                                                                       | 00000000            | 255                   | B <sub>OP</sub> selection is at minimum value.                                                                                                                  |

|                                                                                                                                       | x01                 | 1                     | Output Fall Time (FALL). Least significant bit.                                                                                                                 |

|                                                                                                                                       | x11                 | 3                     | Output Fall Time (FALL). Most significant bit.                                                                                                                  |

| Outrout / Fires Objection                                                                                                             | 0xx                 | 0                     | Output Polarity Bit (POL). Default, no fuse blowing required. POL = 0, V <sub>OUT</sub> = Low opposite target tooth.                                            |

| Output / Fuse Checking [ $V_{PH} \rightarrow 3 \times V_{PM} \rightarrow V_{PH}$ ]                                                    | 1xx                 | 4                     | Output Polarity Bit (POL). POL = 1, V <sub>OUT</sub> = High opposite target tooth. Code references a single bit only.                                           |

|                                                                                                                                       | 1000                | 8                     | Fuse Threshold Low Register. Checks un-blown fuses. Code references a single bit only.                                                                          |

|                                                                                                                                       | 1001                | 9                     | Fuse Threshold High Register. Checks blown fuses.                                                                                                               |

| Blow or Read Mode Register Selec                                                                                                      | tions <sup>2</sup>  |                       |                                                                                                                                                                 |

| B <sub>OP</sub> Selection<br>(BOPSEL)                                                                                                 | 00000000            | 0                     | B <sub>OP</sub> magnitude selection. Default, no fuse blowing required. Minimum value, corresponding to AG <sub>Range</sub> (max).                              |

| $[2 \times V_{PH} \rightarrow 11 \times V_{PM} \rightarrow V_{PH}]$                                                                   | 11111111            | 255                   | B <sub>OP</sub> magnitude selection. Maximum value, corresponding to AG <sub>Range</sub> (min).                                                                 |

| B <sub>OP</sub> Polarity<br>(BOPPOL)                                                                                                  | 0                   | 0                     | South field polarity. Default, no fuse blowing required.                                                                                                        |

| $ \begin{array}{l} [\ V_{PH} \rightarrow V_{PM} \rightarrow V_{PH} \\ \rightarrow 11 \times V_{PM} \rightarrow V_{PH} \end{array} ] $ | 1                   | 1                     | North field polarity.                                                                                                                                           |

|                                                                                                                                       | 00                  | 0                     | Output Fall Time (FALL). Default, no fuse blowing required.                                                                                                     |

|                                                                                                                                       | 11                  | 3                     | Output Fall Time (FALL) selection is at maximum value.                                                                                                          |

| Output / Lock Bit<br>[ V <sub>PH</sub> → 3×V <sub>PM</sub> → V <sub>PH</sub><br>→ 11×V <sub>PM</sub> → V <sub>PH</sub> ]              | 000                 | 0                     | Output Polarity Bit (POL). Default, no fuse blowing required. POL = 0, V <sub>OUT</sub> = Low opposite target tooth.                                            |

|                                                                                                                                       | 100                 | 4                     | Output Polarity Bit (POL). Code refers to bit 2 only. POL = 1, V <sub>OUT</sub> = High opposite target tooth.                                                   |

| · ···                                                                                                                                 | 10000               | 16                    | Lock bit (LOCK). Locks access to all registers with exception of Fuse Threshold registers. Code refers to bit 5 only.                                           |

|                                                                                                                                       | 0 to 1111111        | _                     | Read mode bit values. Sequentially selects each bit in selected Blow mode register for reading bit status as blown or not blown. Monitor VOUT after each pulse. |

<sup>&</sup>lt;sup>1</sup>Code 1 is automatically selected after the falling edge of the final V<sub>PH</sub> in the register key. Each subsequent V<sub>PM</sub> in the bit field addresses the next decimal code.

$<sup>^2</sup>$ Bit 0, or code 1, is automatically selected after the falling edge of the final  $V_{PH}$  in the register key. Each subsequent  $V_{PM}$  in the bit field addresses the next bit.

### **Fuse Checking**

Incorporated in the ATS128 is circuitry to simultaneously check the integrity of the fuse bits. The fuse checking feature is enabled by using the Fuse Checking registers, and while in Try mode, applying the codes shown in table 3. The register is only valid in Try mode and is available before or after the programming LOCK bit is set.

Selecting the Fuse Threshold High register checks that all blown fuses are properly blown. Selecting the Fuse Threshold Low register checks all un-blown fuses are properly intact. The supply current,  $I_{\rm CC}$ , increases by 250  $\mu A$  if a marginal fuse is detected. If all fuses are correctly blown or fully intact, there will be no change in supply current.

### **Output Polarity**

When selecting the  $B_{OP}$  registers in Try mode, the output polarity is determined by the value of the Output Polarity bit (POL). The default value is POL = 0 (fuse un-blown). For applications that require the output states defined by POL = 1 (see Operating Characteristics table), it is recommended to first permanently blow the POL bit by selecting the Output / Lock bit register, and code 4. The output is then defined by POL = 1 when selecting the  $B_{OP}$  Try mode registers. See table 3 for parameter details.

#### **Additional Guidelines**

The additional guidelines in this section should be followed to ensure the proper behavior of these devices:

- The power supply used for programming must be capable of delivering at least V<sub>PH</sub> and I<sub>PP</sub>.

- Be careful to observe the t<sub>LOW</sub> delay time before powering down the device after blowing each bit.

- Set the LOCK bit (only after all other parameters have been programmed and validated) to prevent any further programming of the device.

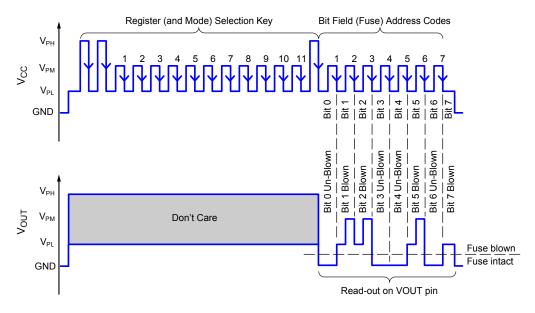

#### **Read Mode**

The ATS128 features a Read mode that allows the status of each programmable fuse to be read back individually. The status, blown or not blown, of the addressed fuse is determined by monitoring the state of the VOUT pin. A complete example is shown in figure 11.

Read mode uses the same register selection keys as Blow mode (see table 3), allowing direct addressing of the individual fuses in the BOPPOL and BOPSEL registers (do not inadvertently send a Blow pulse while in Read mode). After sending the register and mode selection keys, that is, after the falling edge of the final  $V_{PH}$  pulse in the key, the first bit (the LSB) is selected. Each addi-

Figure 11. Read mode example. Pulse sequence for accessing the  $B_{OP}$  Selection register (BOPSEL) and reading back the status of each of the eight bit fields. In this example, the code (blown fuses) is  $2 + 2^2 + 2^5 + 2^7 = 166$  (10100110). After each address pulse is sent, the voltage on the VOUT pin will be at GND for un-blown fuses and at  $V_{CC}$  (at  $V_{PL}$  or  $V_{PM}$ ) for blown fuses.

tional  $V_{PM}$  pulse addresses the next bit in the selected register, up to the MSB. Read mode is available only before the LOCK bit has been set.

After the final  $V_{PH}$  key pulse, and after each  $V_{PM}$  address pulse, if  $V_{OUT}$  is high, the corresponding fuse can be considered blown

(the status of the Output Polarity bit, POL, does not affect Read mode output values, allowing POL to be tested also). If the output state is low, the fuse can be considered un-blown. During Read mode VOUT must be pulled high using a pull-up resistor (see  $R_{LOAD}$  in the Typical Application Circuit diagram).

Figure 12. Example of Try mode programming pulses applied to the VCC pin. In this example,  $B_{OP}$  Positive Trim, Down-Counting register is addressed to code 12 by the eleven  $V_{PM}$  pulses (code 1 is selected automatically at the falling edge of the register-mode selection key).

Figure 13. Example of Blow mode programming pulses applied to the VCC pin. In this example, the  $B_{OP}$  Magnitude Selection register (BOPSEL) is addressed to code 8 (bit 3, or 3  $V_{PM}$  pulses) and its value is permanently blown.

## **BOP** Selection

The ATS128 allows accurate trimming of the magnetic operate point,  $B_{OP}$ , within the application. This programmable feature reduces effects due to mechanical placement tolerances and improves performance when used in proximity or gear tooth sensing applications.

B<sub>OP</sub> can be set to any value within the range allowed by the BOPSEL registers. This includes switchpoints of south or north polarity, and switchpoints at or near the zero crossing point for B. However, switching is recommended only within the air gap limits specified in the Operating Characteristics table.

Trimming of  $B_{OP}$  is typically done in two stages. In the first stage,  $B_{OP}$  is adjusted temporarily using the Try mode programming features, to find the fuse value that corresponds to the optimum  $B_{OP}$ . After a value is determined, then it can be permanently set using the Blow mode features.

As an aid to programming the ATS128 has several options available in Try Mode for adjusting the  $B_{OP}$  parameter. As shown in figure 14, these allow trimming of  $B_{OP}$  for operation in north or south polarity magnetic fields. In addition the  $B_{OP}$  parameter can either trim-up, start at the  $B_{OP}$  minimum value and increase to the maximum value, or trim-down, starting at the  $B_{OP}$  maximum value and decreasing to the minimum value.

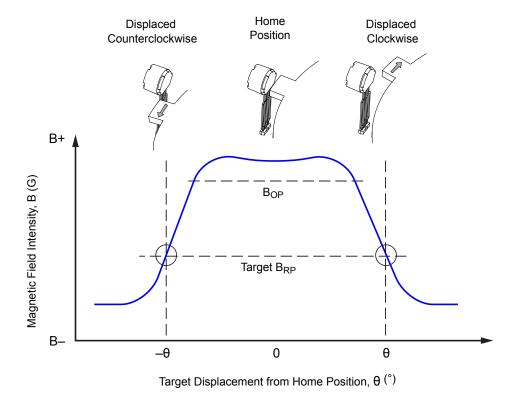

The Trim Up-Counting and Trim Down-Counting features can simplify switchpoint calibration by allowing the user to find the codes for both the magnetic operation point,  $B_{OP}$ , and the magnetic release point,  $B_{RP}$ . As an example, consider using the ATS128 as a proximity sensor to detect rotational displacement of a ferromagnetic target (see figure 15). When the ferromagnetic target is centered opposite the device branded face, its location is considered homed (0 mm displacement). If the target rotates a certain distance,  $\pm \theta_{\rm v}$  in either direction, the sensor IC output should change state.

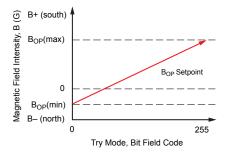

(A) BOP Positive, Trim Up-Counting Register

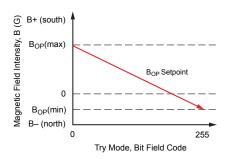

(B) B<sub>OP</sub> Positive, Trim Down-Counting Register

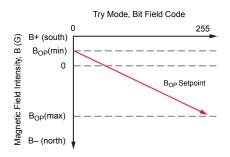

(C)  $B_{OP}$  Negative, Trim Up-Counting Register

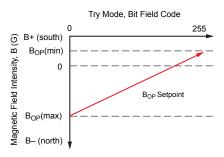

(D) B<sub>OP</sub> Negative, Trim Down-Counting Register

Figure 14. B<sub>OP</sub> profiles for each of the four B<sub>OP</sub> Selection virtual registers available in Try mode.

Figure 15 shows a plot of the example, indicating magnetic field density versus displacement, at a fixed air gap. For the example, the magnetic field is assumed to be positive (south). At the Home position the device output will be in a state defined by  $B > B_{OP}$ , low (assuming POL = 0). In a position at a displacement greater than  $\pm \theta$ , the output will be in the state defined by  $B < B_{RP}$ , high. To achieve the required result,  $B_{OP}$  is programmed to a level such that the sensor IC changes state from low to high at  $\pm \theta$ .

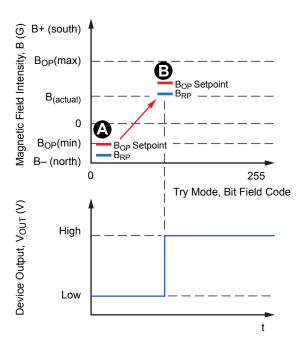

First, the target is located at the corresponding switchpoint location, the  $-\theta^{\circ}$  or  $+\theta^{\circ}$  position. Next, the device Positive Trim, Up-Counting register is selected and the output is monitored while the addressed code is increased. When the register is entered, the default magnitude (code 1) of  $B_{OP}$  is lower than the magnetic flux

density, Bactual, and output is low. (See A in figure 16.)

As the code is increased,  $B_{OP}$  is increased. When  $B_{OP}$  is increased to a level where  $B_{OP}$  point is greater than  $B_{actual}$ , the output changes state from low to high. The code value when the device switched from low to high corresponds to the  $B_{RP}$  point (record this for later reference). (See B in figure 16.)

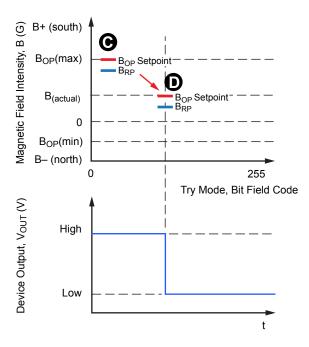

To find the code that corresponds to  $B_{OP}$ , the device Positive Trim, Down-Counting register is selected, and the output is monitored while the addressed code is increased. When the register is entered, the default magnitude (code 1)  $B_{OP}$  is higher than the ambient field flux density,  $B_{actual}$ , (because the codes are inverted for down-counting) and output is high. (See C in figure 17.)

Figure 15. Example of magnetic flux density versus target displacement. In an application, an increasing B value could indicate either an increasing intensity of a south field or a decreasing intensity of a north field.

As the code is increased,  $B_{OP}$  is decreased. When  $B_{OP}$  is less than  $B_{actual}$  the output changes state from high to low. (See D in figure 17.) Record the  $B_{OP}$  selection for later use. Because when using the Down-Counting register the  $B_{OP}$  selection is automatically inverted, therefore the recorded value is equal to the maximum value minus the addressed code.

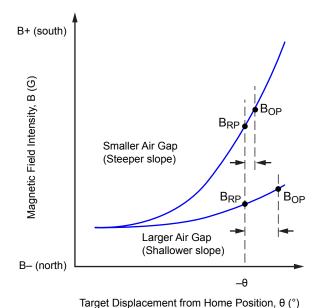

The air gap mechanical position is also a factor in determining the magnetic switchpoints. As seen in figure 18, at smaller air gaps the change in flux density versus change in displacement is large, represented by a steeply sloped function, and there is relatively little difference between the target displacements at  $B_{\rm OP}$  and  $B_{\rm RP}$ . At larger air gaps, however, the change function is shal-

## BOP Positive, Trim Up-Counting Register

Figure 16. Positive Trim, Up-Counting to find  $B_{RP}$ .

## B<sub>OP</sub> Positive, Trim Down-Counting Register

Figure 17. Positive Trim, Down-Counting to find B<sub>OP</sub>.

lower, and therefore the difference between  $B_{OP}$  and  $B_{RP}$  must be considered. If  $B_{RP}$  is more appropriate as the actual device switchpoint, the code determined using the Up-Counting register in the example can be programmed and set. If  $B_{OP}$  is more appropriate as the switchpoint, the code determined using the Down-Counting register can be programmed and set.

It should be noted that in the proximity sensor example given above, the magnetic field was defined as positive (south) and the  $B_{OP}$  Positive, Trim Up- and Trim Down-Counting registers were used. If in the application the magnetic field is negative, the  $B_{OP}$  Negative, Trim Up- and Trim Down-Counting registers should be used as shown in figures 14C and 14D. The procedure for programming these registers is the same as discussed in the proximity sensor example. Note the purpose of the example is to show how to use some of the ATS128  $B_{OP}$  programming options and is not based on any reference design.

.

Figure 18. Example switchpoints versus mechanical location.

## **Power Derating**

The device must be operated below the maximum junction temperature of the device,  $T_J(max)$ . Under certain combinations of peak conditions, reliable operation may require derating supplied power or improving the heat dissipation properties of the application. This section presents a procedure for correlating factors affecting operating  $T_J$ . (Thermal data is also available on the Allegro MicroSystems website.)

The Package Thermal Resistance,  $R_{\theta JA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to the ambient air. Its primary component is the Effective Thermal Conductivity, K, of the printed circuit board, including adjacent devices and traces. Radiation from the die through the device case,  $R_{\theta JC}$ , is relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors, damped by overmolding.

The effect of varying power levels (Power Dissipation,  $P_D$ ), can be estimated. The following formulas represent the fundamental relationships used to estimate  $T_J$ , at  $P_D$ .

$$P_D = V_{IN} \times I_{IN} \tag{1}$$

$$\Delta T = P_D \times R_{\Theta I \Delta} \tag{2}$$

$$T_{J} = T_{A} + \Delta T \tag{3}$$

For example, given common conditions such as:  $T_A$ = 25°C,  $V_{IN}$  = 12 V,  $I_{IN}$  = 4 mA, and  $R_{\theta JA}$  = 140 °C/W, then:

$$P_D = V_{IN} \times I_{IN} = 12 \text{ V} \times 4 \text{ mA} = 48 \text{ mW}$$

$\Delta T = P_D \times R_{\theta JA} = 48 \text{ mW} \times 140 \text{ °C/W} = 7 \text{ °C}$

$T_1 = T_\Delta + \Delta T = 25 \text{ °C} + 7 \text{ °C} = 32 \text{ °C}$

A worst-case estimate,  $P_D(max)$ , represents the maximum allowable power level, without exceeding  $T_J(max)$ , at a selected  $R_{\theta JA}$  and  $T_A.$

*Example*: Reliability for  $V_{CC}$  at  $T_A$ =150°C, package SE, using a single-layer PCB.

Observe the worst-case ratings for the device, specifically:  $R_{\theta JA} = 101$  °C/W,  $T_J(max) = 165$ °C,  $V_{CC}(max) = 24$ V, and  $I_{CC}(max) = 5.5$  mA.

Calculate the maximum allowable power level,  $P_D(\text{max})$ . First, invert equation 3:

$$\Delta T_{max} = T_{J}(max) - T_{A} = 165 \,^{\circ}C - 150 \,^{\circ}C = 15 \,^{\circ}C$$

This provides the allowable increase to  $T_J$  resulting from internal power dissipation. Then, invert equation 2:

$$P_D(max) = \Delta T_{max} \div R_{\theta JA} = 15^{\circ}C \div 101^{\circ}C/W = 149 \text{ mW}$$

Finally, invert equation 1 with respect to voltage:

$$\begin{split} V_{CC}(est) &= P_D(max) \div I_{CC}(max) = 149 \text{ mW} \div 5.5 \text{ mA} = 27 \text{ V} \\ \text{The result indicates that, at $T_A$, the application and device can dissipate adequate amounts of heat at voltages $\le V_{CC}(est)$.} \end{split}$$

Compare  $V_{CC}(est)$  to  $V_{CC}(max)$ . If  $V_{CC}(est) \leq V_{CC}(max)$ , then reliable operation between  $V_{CC}(est)$  and  $V_{CC}(max)$  requires enhanced  $R_{\theta JA}.$  If  $V_{CC}(est) \geq V_{CC}(max)$ , then operation between  $V_{CC}(est)$  and  $V_{CC}(max)$  is reliable under these conditions.

## Package SE 4-Pin SIP

# Highly Programmable, Back-Biased, Hall-Effect Switch with TPOS Functionality

## **Revision History**

| Number | Date              | Description             |  |

|--------|-------------------|-------------------------|--|

| _      | May 4, 2013       | Initial release         |  |

| 1      | February 14, 2019 | Minor editorial updates |  |

Copyright ©2019, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com