## Industrial Analog Current/ **Voltage-Output Conditioners**

### **General Description**

The MAX15500/MAX15501 analog output conditioners provide a programmable current up to ±24mA, or a voltage up to ±12V proportional to a control voltage signal. The control voltage is typically supplied by an external DAC with an output voltage range of 0 to 4.096V for the MAX15500 and 0 to 2.5V for the MAX15501. The output current and voltage are selectable as either unipolar or bipolar. In the unipolar configuration, a control voltage of 5% full-scale (FS) produces a nominal output of 0A or 0V to achieve underrange capability. A control voltage of 100%FS produces one of two programmable levels (105%FS or 120%FS) to achieve overrange capability. The outputs of the MAX15500/MAX15501 are protected against overcurrent conditions and a short to ground or supply voltages up to ±35V. The devices also monitor for overtemperature and supply brownout conditions. The supply brownout threshold is programmable.

The MAX15500/MAX15501 are programmed through an SPI™ interface capable of daisy-chained operation. The MAX15500/MAX15501 provide extensive error reporting through the SPI interface and an additional open-drain interrupt output. The devices include an analog output to monitor load conditions.

The MAX15500/MAX15501 operate over the -40°C to +105°C temperature range. The devices are available in a 32-pin, 5mm x 5mm TQFN package.

### **Applications**

Programmable Logic Controllers (PLCs) Distributed I/Os **Embedded Systems** Industrial Control and Automation

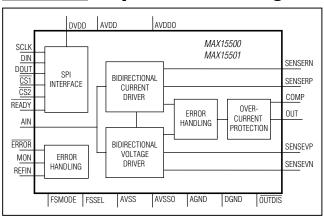

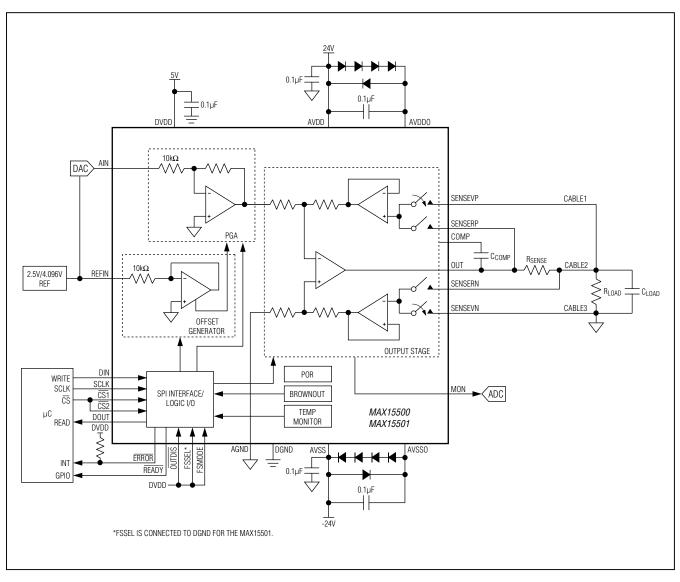

### Simplified Block Diagram

#### **Features**

- Supply Voltage Up to ±32.5V

- Output Protected Up to ±35V

- **Programmable Output (Plus Overrange)**

- ±10V

- 0 to 10V

- 0 to 5V ±20mA

- 0 to 20mA

- 4 to 20mA

- Current Output Drives 0 to  $1k\Omega$

- Voltage Output Drives Loads Down to  $1k\Omega$

- **HART Compliant**

- 2ppm Gain Error Drift Over Temperature

- SPI Interface, with Daisy-Chain Capability

- Supports +4.096V (MAX15500) or +2.5V (MAX15501) Full-Scale Input Signals

- **Extensive Érror Reporting** Short-Circuit and Overcurrent Protection **Open-Circuit Detection Brownout Detection Overtemperature Protection**

- ♦ Fast, 40us Settling Time

### **Ordering Information**

| PART          | PIN-PACKAGE | REFERENCE |

|---------------|-------------|-----------|

| MAX15500GTJ+  | 32 TQFN-EP* | +4.096V   |

| MAX15500KGTJ+ | 32 TQFN-EP* | +4.096V   |

| MAX15501GTJ+  | 32 TQFN-EP* | +2.5V     |

| MAX15501KGTJ+ | 32 TQFN-EP* | +2.5V     |

**Note:** All devices are specified over the -40°C to +105°C operating temperature range.

- +Denotes a lead(Pb)-free/RoHS-compliant package.

- \*EP = Exposed pad.

SPI is a trademark of Motorola, Inc.

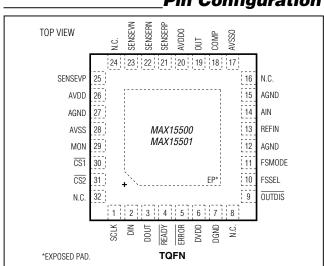

### Pin Configuration

## Industrial Analog Current/ Voltage-Output Conditioners

### **ABSOLUTE MAXIMUM RATINGS**

| AVIDD : AONID                   | 0.01/         |

|---------------------------------|---------------|

| AVDD to AGND                    | 0.3V to +35V  |

| AVSS to AGND                    | 35V to +0.3V  |

| AVDD to AVSS                    | 0 to +70V     |

| AVDD to AVDDO                   | 0 to +4V      |

| AVSS to AVSSO                   | 4V to 0V      |

| DGND to AGND                    | 0.3V to +0.3V |

| AVDD to DVDD                    | 6V to +35V    |

| DVDD to DGND                    | 0.3V to +6.0V |

| CS1, CS2, SCLK, DIN, DOUT, READ | , - , ,       |

| MON, OUTDIS, FSSEL to DGND      | 0.3V to +6.0V |

| AIN, REFIN to AGND              | 0.3V to +6.0V |

|                                 |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VAVDD = +24V, VAVSS = -24V, VDVDD = 5.0V, CLOAD = 1nF, CCOMP = 0nF, VREFIN = 4.096V for the MAX15500, VREFIN = 2.5V for the MAX15501. All specifications for TA = -40°C to +105°C. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER                           | SYMBOL             | CONDITIONS                                                      | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------|--------------------|-----------------------------------------------------------------|-------|-------|-------|-------|

| POWER SUPPLY (Note 1)               |                    |                                                                 |       |       |       |       |

| Analog Positive Supply Voltage      | V4.455             | 5% overrange (FSMODE = DVDD)                                    | 15    | 24    | 32.5  | V     |

| Analog Positive Supply Voltage      | Vavdd              | 20% overrange (FSMODE = DGND)                                   | 18.5  | 24    | 32.5  | V     |

| Analog Negative Supply              | 1/41/00            | 5% overrange (FSMODE = DVDD)                                    | -32.5 | -24   | -15   | V     |

| Voltage                             | Vavss              | 20% overrange (FSMODE = DGND)                                   | -32.5 | -24   | -18.5 | V     |

| AVDD to AVDDO Voltage<br>Difference | Vavddo             | (Note 1)                                                        |       | 2.5   |       | V     |

| AVSS to AVSSO Voltage<br>Difference | Vavsso             | (Note 1)                                                        |       | 2.5   |       | V     |

| Digital Supply Voltage              | V <sub>D</sub> VDD |                                                                 | 2.7   |       | 5.25  | V     |

| Analog Positive Supply Current      | IAP                | IAP = IAVDD + IAVDDO, ILOAD = OA                                |       | 5     | 7     | mA    |

| Analog Negative Supply Current      | I <sub>AN</sub>    | IAN = IAVSS + IAVSSO, ILOAD = 0A                                | -7    | -4.5  |       | mA    |

| Digital Supply Current              | IDVDD              | $V_{DVDD} = 5V$                                                 |       | 0.1   | 0.4   | mA    |

| Analog Positive Standby Current     | ISTBYP             | ISTBYP = IAVDD + IAVDDO, OUTDIS = DGND or software standby mode |       | 1     |       | mA    |

| Analog Negative Standby Current     | ISTBYN             | ISTBYN = IAVSS + IAVSSO, OUTDIS = DGND or software standby mode |       | -0.5  |       | mA    |

| ANALOG INPUT (AIN, REFIN)           |                    |                                                                 |       |       |       |       |

| Input Impedance                     | RIN                |                                                                 |       | 10    |       | kΩ    |

| Input Capacitance                   | CIN                |                                                                 |       | 10    |       | рF    |

| Analog Input Full Scale             | VAIN               | FSSEL = DVDD, MAX15500                                          | 4.0   | 4.096 | 4.2   | V     |

| Analog Input i uli ocale            | VAIN               | FSSEL = DGND, MAX15501                                          | 2.4   | 2.5   | 2.6   | V     |

| REFIN Full-Scale Input              | Voccivi            | FSSEL = DVDD, MAX15500                                          | 4.0   | 4.096 | 4.2   | V     |

| TET IN TUIT-Scale Input             | VREFIN             | FSSEL = DGND, MAX15501                                          | 2.4   | 2.5   | 2.6   | 1 V   |

# Industrial Analog Current/ Voltage-Output Conditioners

### **ELECTRICAL CHARACTERISTICS (continued)**

(VAVDD = +24V, VAVSS = -24V, VDVDD = 5.0V, CLOAD = 1nF, CCOMP = 0nF, VREFIN = 4.096V for the MAX15500, VREFIN = 2.5V for the MAX15501. All specifications for T<sub>A</sub> = -40°C to +105°C. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                 | SYMBOL | CONDITIONS                                                                           |                                                       | MIN | TYP  | MAX | UNITS |

|---------------------------|--------|--------------------------------------------------------------------------------------|-------------------------------------------------------|-----|------|-----|-------|

| CURRENT OUTPUT (Note 2)   |        |                                                                                      |                                                       |     |      |     |       |

| Maximum Load Resistance   | RLOAD  | $V_{AVDD} = +24V, V_{AV}$                                                            | /SS = -24V                                            |     | 750  |     | Ω     |

| Waximum Load Nesistance   | TILUAD | VAVDD = +32.5V, VAVSS = -32.5V                                                       |                                                       |     | 1000 |     | 52    |

| Maximum Load Inductance   | LLOAD  | CCOMP = 100nF (N                                                                     | ote 3)                                                |     | 15   |     | mH    |

| Maximum Load Capacitance  | CLOAD  | CCOMP = 4.7nF                                                                        |                                                       |     | 100  |     | μF    |

|                           |        |                                                                                      | To 0.1% accuracy,<br>LLOAD = 20µH,<br>CCOMP = 0nF     |     | 40   |     |       |

|                           |        |                                                                                      | To 0.1% accuracy,<br>LLOAD = 1mH,<br>CCOMP = 0.15nF   |     | 500  |     |       |

|                           |        | Full-scale step<br>from 0 to 20mA or<br>-20mA to + 20mA,<br>R <sub>LOAD</sub> = 750Ω | To 0.1% accuracy,<br>LLOAD = 10mH,<br>CCOMP = 0.15nF  |     | 500  |     |       |

| Maximum Settling Time     |        |                                                                                      | To 0.01% accuracy,<br>LLOAD = 20µH,<br>CCOMP = 0nF    |     | 60   |     | μs    |

|                           |        |                                                                                      | To 0.01% accuracy,<br>LLOAD = 10mH,<br>CCOMP = 0.15nF |     | 600  |     |       |

|                           |        | 1% full-scale step, RLOAD = $750\Omega$                                              | To 0.1% accuracy,<br>LLOAD = 20µH,<br>CCOMP = 0nF     |     | 20   |     | μο    |

|                           |        |                                                                                      | To 0.1% accuracy,<br>LLOAD = 1mH,<br>CCOMP = 0.15nF   |     | 100  |     |       |

|                           |        |                                                                                      | To 0.1% accuracy,<br>LLOAD = 10mH,<br>CCOMP = 0.15nF  |     | 100  |     |       |

|                           |        |                                                                                      | To 0.01% accuracy,<br>LLOAD = 20µH,<br>CCOMP = 0nF    |     | 40   |     |       |

|                           |        |                                                                                      | To 0.01% accuracy,<br>LLOAD = 10mH,<br>CCOMP = 0.15nF |     | 200  |     |       |

| Full-Scale Output Current | lout   | VFSMODE = VDVDD                                                                      |                                                       |     | ±21  |     | mA    |

| - an ocale Output Outrent | 1001   | VFSMODE = VDGND                                                                      |                                                       |     | ±24  |     | 111/7 |

# Industrial Analog Current/ Voltage-Output Conditioners

### **ELECTRICAL CHARACTERISTICS (continued)**

(VAVDD = +24V, VAVSS = -24V, VDVDD = 5.0V, CLOAD = 1nF, CCOMP = 0nF, VREFIN = 4.096V for the MAX15500, VREFIN = 2.5V for the MAX15501. All specifications for TA = -40°C to +105°C. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER                        | SYMBOL      | CONDITIONS                                                                             |                                      | MIN | TYP  | MAX   | UNITS             |

|----------------------------------|-------------|----------------------------------------------------------------------------------------|--------------------------------------|-----|------|-------|-------------------|

| Offset Error                     |             | VAIN = 5% of VREFIN<br>VAIN = 50% of VREFI                                             |                                      |     | ±0.1 | ±0.5  | %FS               |

| Offset-Error Drift               |             |                                                                                        |                                      |     | ±5   |       | ppm/°C            |

| Gain Error                       | GE          | 0.01% precision RSENSE, tested according to the ideal transfer                         | MAX15500                             |     | ±0.1 | ±0.51 | %FS               |

|                                  |             | functions shown in<br>Table 8                                                          | MAX15501                             |     | ±0.1 | ±0.5  |                   |

| Gain-Error Drift                 |             | No RSENSE drift                                                                        |                                      |     | ±2   |       | ppm/°C            |

| Integral Nonlinearity Error      | INL         |                                                                                        |                                      |     | 0.05 |       | %FS               |

| Output Conductance               |             | (dlout/dVout), lout 750 $\Omega$ to 0 $\Omega$ , FSMOD mode                            |                                      |     | 1.0  |       | μΑ/V              |

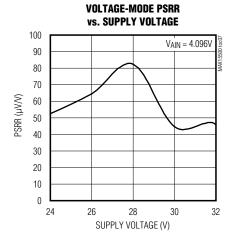

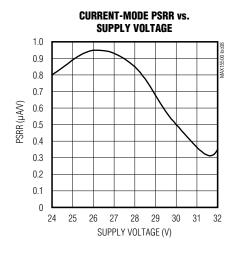

| Power-Supply Rejection Ratio     | PSRR        | At DC, V <sub>AVDD</sub> = +24<br>= -24V to -32.5V, V <sub>A</sub><br>mode, FSMODE = D | IN = VREFIN, unipolar                |     | 1.6  |       | μΑ/V              |

| Overcurrent Limit                |             | RSENSE shorted                                                                         |                                      | 25  | 30   | 40    | mA                |

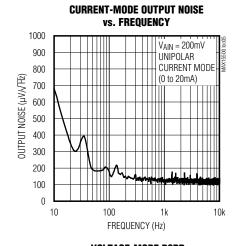

| Output Current Noise             |             | 0.1Hz to 10Hz                                                                          |                                      |     | 20   |       | nA <sub>RMS</sub> |

| Output Guirent Noise             |             | At 1kHz                                                                                |                                      |     | 2.6  |       | nA/√Hz            |

| Output Slew Rate                 |             |                                                                                        |                                      |     | 1.5  |       | mA/µs             |

| Small-Signal Bandwidth           |             |                                                                                        |                                      |     | 30   |       | kHz               |

| Maximum OUT Voltage to AVDDO     |             | Vavddo - Vout                                                                          |                                      |     | 2.0  |       | V                 |

| Minimum OUT Voltage to AVSSO     |             | Vout - Vavsso                                                                          |                                      |     | 2.0  |       | V                 |

| <b>VOLTAGE OUTPUT (RLOAD = 1</b> | <b>k</b> Ω) |                                                                                        |                                      |     |      |       |                   |

| Minimum Resistive Load           | RLOAD       |                                                                                        |                                      |     | 1    |       | kΩ                |

| Maximum Capacitive Load          | CLOAD       | CCOMP = 4.7nF                                                                          |                                      |     | 100  |       | μF                |

|                                  |             | To 0.1% accuracy, lowith 1nF, CCOMP = 0                                                | pad = 1k $\Omega$ in parallel<br>OnF |     | 20   |       |                   |

| Maximum Settling Time (Full-     |             | To 0.1% accuracy, keep with 1µF, CCOMP = 4                                             | oad = $1k\Omega$ in parallel 4.7nF   |     | 1000 |       |                   |

| Scale Step)                      |             | To 0.01% accuracy, with 1nF, CCOMP = 0                                                 | load = $1k\Omega$ in parallel<br>OnF |     | 30   |       | μs                |

|                                  |             | To 0.01% accuracy, lewith 1µF, CCOMP = 4.                                              |                                      |     | 1300 |       |                   |

# Industrial Analog Current/ Voltage-Output Conditioners

### **ELECTRICAL CHARACTERISTICS (continued)**

(VAVDD = +24V, VAVSS = -24V, VDVDD = 5.0V, CLOAD = 1nF, CCOMP = 0nF, VREFIN = 4.096V for the MAX15500, VREFIN = 2.5V for the MAX15501. All specifications for TA = -40°C to +105°C. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER                    | SYMBOL     | COND                                        | DITIONS                               | MIN | TYP  | MAX  | UNITS  |  |

|------------------------------|------------|---------------------------------------------|---------------------------------------|-----|------|------|--------|--|

|                              |            | To 0.1% accuracy, lowith 1nF, CCOMP = 0     |                                       |     | 10   |      |        |  |

| Maximum Settling Time        |            | To 0.1% accuracy, lowith 1µF, CCOMP = 4     |                                       |     | 300  |      |        |  |

| (1% Full-Scale Step)         |            | To 0.01% accuracy, with 1nF, CCOMP = 0      | load = 1k $\Omega$ in parallel<br>)nF |     | 20   |      | μs     |  |

|                              |            | To 0.01% accuracy, with 1µF, CCOMP = 4      | load = $1k\Omega$ in parallel 1.7nF   |     | 600  |      |        |  |

| Gain Error                   |            | Tested according to functions shown in T    |                                       |     | ±0.1 | ±0.5 | %FS    |  |

| Gain-Error Drift             |            |                                             |                                       |     | ±2   |      | ppm/°C |  |

|                              |            | FSMODE = DVDD                               | 5V range                              |     | 5.25 |      | V      |  |

| Full Cools Outsut Valtages   | \/ - · · - | FSWODE = DVDD                               | 10V range                             |     | 10.5 |      |        |  |

| Full-Scale Output Voltage    | Vout -     | FSMODE = DGND                               | 5V range                              |     | 6    |      |        |  |

|                              |            |                                             | 10V range                             |     | 12   |      |        |  |

| Offset Error                 |            | VAIN = 5% of VREFIN<br>VAIN = 50% of VREFI  |                                       |     | ±0.1 | ±0.5 | %FS    |  |

| Offset-Error Drift           |            |                                             |                                       |     | ±2   |      | ppm/°C |  |

| Integral Nonlinearity Error  | INL        |                                             |                                       |     | 0.05 |      | %FS    |  |

| Power-Supply Rejection       | PSRR       | At DC, VAVDD = +18<br>= -18.5V to -32.5V, V | 5.5V to +32.5V, VAVSS<br>AIN = VREFIN |     | 30   |      | μV/V   |  |

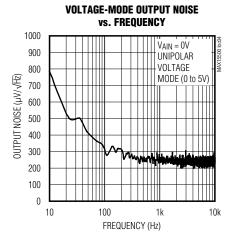

| Output-Voltage Noise         |            | 0.1Hz to 10Hz                               |                                       |     | 16.3 |      | μVRMS  |  |

| Output-voltage Noise         |            | 1kHz                                        |                                       |     | 250  |      | nV/√Hz |  |

| Output-Voltage Slew Rate     |            |                                             |                                       |     | 1.5  |      | V/µs   |  |

| Short-Circuit Current        |            |                                             |                                       | 20  | 30   | 45   | mA     |  |

| Maximum OUT Voltage to AVDDO |            | Vavddo - Vout                               |                                       |     | 2.0  |      | V      |  |

| Minimum OUT Voltage to AVSSO |            | Vout - Vavsso                               |                                       |     | 2.0  |      | V      |  |

# Industrial Analog Current/ Voltage-Output Conditioners

### **ELECTRICAL CHARACTERISTICS (continued)**

(VAVDD = +24V, VAVSS = -24V, VDVDD = 5.0V, CLOAD = 1nF, CCOMP = 0nF, VREFIN = 4.096V for the MAX15500, VREFIN = 2.5V for the MAX15501. All specifications for  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                               | SYMBOL          | CONDITIONS                                                                         | MIN                     | TYP  | MAX            | UNITS |

|-----------------------------------------|-----------------|------------------------------------------------------------------------------------|-------------------------|------|----------------|-------|

| OUTPUT MONITOR (MON)                    | ,               | ,                                                                                  | ,                       |      |                |       |

| Maximum Output Voltage                  |                 | Current mode, see the <i>Output Monitor</i> section for V <sub>MON</sub> equations |                         | 3    |                | V     |

| Maximum Output Voltage                  |                 | Voltage mode, see the <i>Output Monitor</i> section for V <sub>MON</sub> equations |                         | 3    |                | V     |

| Output Resistance                       |                 |                                                                                    |                         | 35   |                | kΩ    |

| OVERTEMPERATURE DETECT                  | ION             |                                                                                    |                         |      |                |       |

| Overtemperature Threshold               |                 |                                                                                    |                         | +150 |                | °C    |

| Overtemperature Threshold<br>Hysteresis |                 |                                                                                    |                         | 10   |                | °C    |

| DIGITAL INPUTS (CS1, CS2, SC            | LK, DIN, OU     | TDIS, FSSEL, FSMODE)                                                               |                         |      |                |       |

| Input High Voltage                      | VIH             |                                                                                    | 0.7 x<br>VDVDD          |      |                | V     |

| Input Low Voltage                       | VIL             |                                                                                    |                         |      | 0.3 x<br>VDVDD | V     |

| Input Hysteresis                        | VIHYST          |                                                                                    |                         | 300  |                | mV    |

| Input Leakage Current                   | I <sub>IN</sub> | VINPUT = 0V or VDVDD                                                               |                         | ±0.1 | ±1.0           | μΑ    |

| Input Capacitance                       | CIN             |                                                                                    |                         | 10   |                | рF    |

| DIGITAL OUTPUT (DOUT, REAL              | OY)             |                                                                                    |                         |      |                |       |

| Output Low Voltage                      | VoL             | ISINK = 4mA                                                                        |                         |      | 0.4            | V     |

| Output High Voltage                     | Voн             | ISOURCE = 4mA                                                                      | V <sub>DVDD</sub> - 0.5 |      |                | V     |

| Output Three-State Leakage              | loz             | DOUT only                                                                          |                         | ±0.1 | ±10            | μΑ    |

| Output Three-State Capacitance          | Coz             | DOUT only                                                                          |                         | 15   |                | рF    |

| Output Short-Circuit Current            | loss            | V <sub>D</sub> V <sub>D</sub> D = 5.25V                                            |                         | ±150 |                | mA    |

| DIGITAL INTERRUPT (ERROR)               |                 |                                                                                    |                         |      |                |       |

| Interrupt Active Voltage                | VINT            | ISINK = 5.0mA                                                                      |                         |      | 0.4            | V     |

| Interrupt Inactive Leakage              | INTZ            |                                                                                    |                         | ±0.1 | ±1.0           | μΑ    |

| Interrupt Inactive Capacitance          | CINTZ           |                                                                                    |                         | 15   |                | pF    |

| Interrupt Short-Circuit Current         | INTSS           | $V_{DVDD} = 2.7V$                                                                  | 5                       | 30   |                | mA    |

## Industrial Analog Current/ Voltage-Output Conditioners

### **ELECTRICAL CHARACTERISTICS (continued)**

(VAVDD = +24V, VAVSS = -24V, VDVDD = 5.0V, CLOAD = 1nF, CCOMP = 0nF, VREFIN = 4.096V for the MAX15500, VREFIN = 2.5V for the MAX15501. All specifications for TA = -40°C to +105°C. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER                        | SYMBOL | CONDITIONS                               | MIN | TYP | MAX | UNITS |

|----------------------------------|--------|------------------------------------------|-----|-----|-----|-------|

| TIMING CHARACTERISTICS           | •      |                                          |     |     |     |       |

| Serial-Clock Frequency           | fSCLK  | (Note 4)                                 | 0   |     | 20  | MHz   |

| SCLK Pulse-Width High            | tCH    | 40% duty cycle                           | 20  |     |     | ns    |

| SCLK Pulse-Width Low             | tCL    | 60% duty cycle                           | 20  |     |     | ns    |

| CS_ Fall to SCLK Fall Setup Time | tcss   | To 1st SCLK falling edge                 | 15  |     |     | ns    |

| SCLK Fall to CS_ Fall Hold Time  | tCSH   | (Note 5)                                 | 0   |     |     | ns    |

| DIN to SCLK Fall Setup Time      | tDS    |                                          | 15  |     |     | ns    |

| DIN to SCLK Fall Hold Time       | tDH    |                                          | 0   |     |     | ns    |

| SCLK Fall to DOUT Settle Time    | tDOT   | CLOAD = 20pF                             |     |     | 30  | ns    |

| SCLK Fall to DOUT Hold Time      | tDOH   | CLOAD = 0pF                              | 2   |     |     | ns    |

| SCLK Fall to DOUT Disable        | tDOZ   | 14th SCLK deassertion (Note 6)           |     |     | 30  | ns    |

| SCLK Fall to READY Fall          | tcr    | 16th SCLK assertion, CLOAD = 0pF or 20pF | 2   |     | 30  | ns    |

| CS_ Fall to DOUT Enable          | tDOE   | Asynchronous assertion                   | 1   |     | 35  | ns    |

| CS_ Rise to DOUT Disable         | tcsdoz | Asynchronous deassertion                 |     |     | 35  | ns    |

| CS_ Rise to READY Rise           | tcsr   | Asynchronous deassertion, CLOAD = 20pF   |     |     | 35  | ns    |

| CS_ Pulse-Width High             | tcsw   |                                          | 15  |     |     | ns    |

- **Note 1:** Use diodes as shown in the *Typical Operating Circuit/Functional Diagram* to ensure a voltage difference of 2V to 3.5V from AVDD to AVDDO and from AVSS to AVSSO.

- Note 2:  $R_{LOAD} = 750\Omega$ . For the MAX15500, RSENSE =  $48.7\Omega$  for FSMODE = DVDD and RSENSE =  $42.2\Omega$  for FSMODE = DGND. For the MAX15501, RSENSE =  $47.3\Omega$  for FSMODE = DVDD and RSENSE =  $41.2\Omega$  for FSMODE = DGND. See the *Typical Operating Circuit/Functional Diagram*.

- Note 3: Condition at which part is stable.

- Note 4: The maximum clock speed for daisy-chain applications is 10MHz.

- Note 5: t<sub>CSH</sub> is applied to  $\overline{CS}$  falling to determine the 1st SCLK falling edge in a free-running SCLK application. It is also applied to  $\overline{CS}$  rising with respect to the 15th SCLK falling edge to determine the end of the frame.

- Note 6: After the 14th SCLK falling edge, the MAX15500/MAX15501 outputs are high impedance and DOUT data is ignored.

# Industrial Analog Current/ Voltage-Output Conditioners

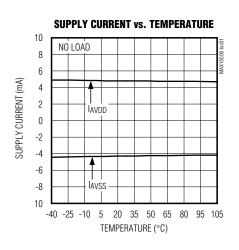

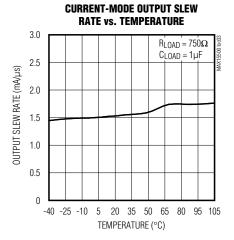

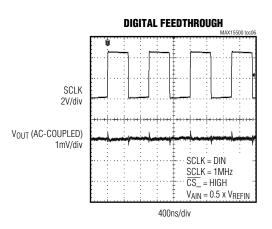

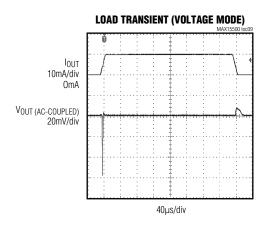

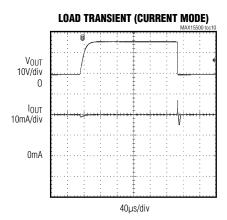

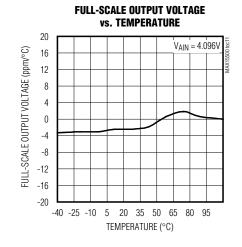

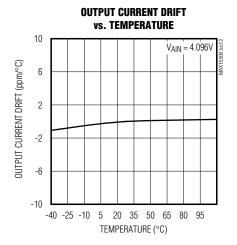

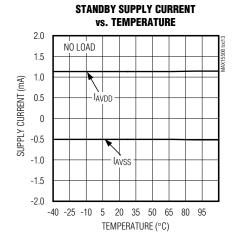

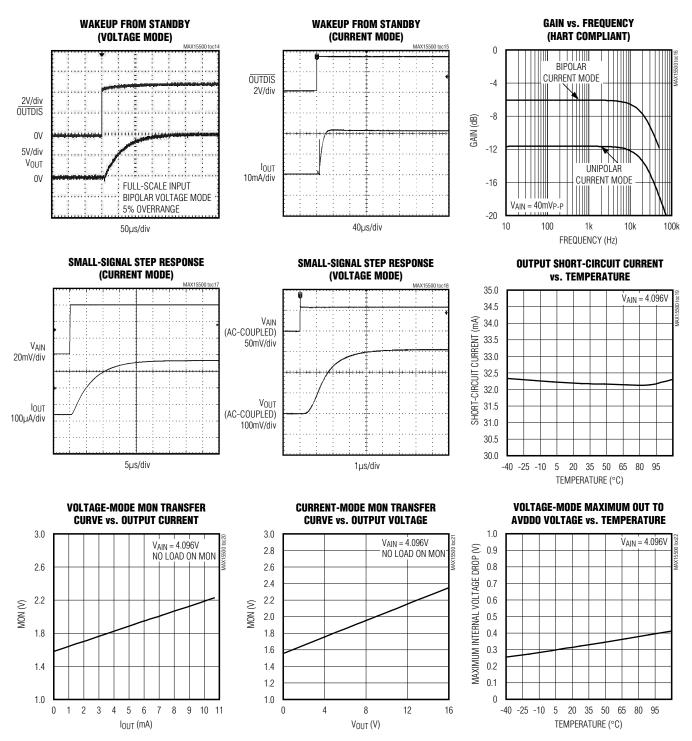

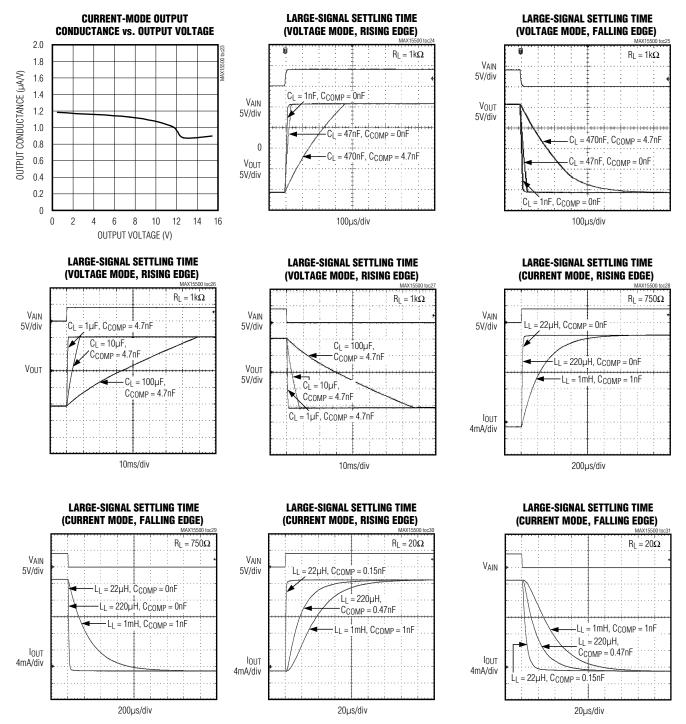

### **Typical Operating Characteristics**

$(V_{AVDD} = +24V, V_{DVDD} = +5V, V_{AVSS} = -24V, C_{LOAD} = 1nF, 5\%$  overrange mode, unipolar current output or bipolar voltage-output mode,  $V_{REFIN} = +4.096V, T_A = +25$ °C, unless otherwise specified.)

# Industrial Analog Current/ Voltage-Output Conditioners

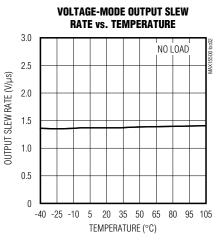

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = +24V, V_{DVDD} = +5V, V_{AVSS} = -24V, C_{LOAD} = 1nF, 5\%$  overrange mode, unipolar current output or bipolar voltage-output mode,  $V_{REFIN} = +4.096V, T_A = +25$ °C, unless otherwise specified.)

# Industrial Analog Current/ Voltage-Output Conditioners

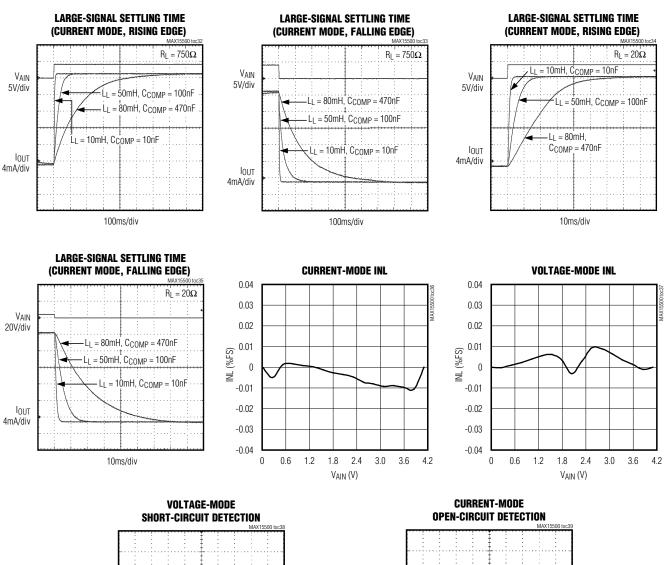

### Typical Operating Characteristics (continued)

$(V_{AVDD} = +24V, V_{DVDD} = +5V, V_{AVSS} = -24V, C_{LOAD} = 1nF, 5\%$  overrange mode, unipolar current output or bipolar voltage-output mode,  $V_{REFIN} = +4.096V, T_A = +25$ °C, unless otherwise specified.)

# Industrial Analog Current/ Voltage-Output Conditioners

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = +24V, V_{DVDD} = +5V, V_{AVSS} = -24V, C_{LOAD} = 1nF, 5\%$  overrange mode, unipolar current output or bipolar voltage-output mode,  $V_{REFIN} = +4.096V, T_A = +25$ °C, unless otherwise specified.)

# Industrial Analog Current/ Voltage-Output Conditioners

### Typical Operating Characteristics (continued)

(V<sub>AVDD</sub> = +24V, V<sub>DVDD</sub> = +5V, V<sub>AVSS</sub> = -24V, C<sub>LOAD</sub> = 1nF, 5% overrange mode, unipolar current output or bipolar voltage-output mode, V<sub>REFIN</sub> = +4.096V, T<sub>A</sub> = +25°C, unless otherwise specified.)

# Industrial Analog Current/ Voltage-Output Conditioners

### Pin Description

| PIN              | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | SCLK   | SPI Clock Input. Activate SCLK only when $\overline{\text{CS}}$ is low to minimize noise coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2                | DIN    | SPI Data Input. Data is clocked into the serial interface on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                | DOUT   | SPI Data Output. Data transitions at DOUT on the falling edge of SCLK. DOUT is high impedance when either CS1 or CS2 is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4                | READY  | Active-Low Device Ready Output. READY is an active-low output that goes low when the device successfully completes processing an SPI data frame. READY returns high at the next rising edge of CS In daisy-chain applications, the READY output typically drives the CS_ input of the next device in the chain or a GPIO of a microcontroller.                                                                                                                                                                                                                                                                    |

| 5                | ERROR  | Active-Low Flag Output. $\overline{\text{ERROR}}$ is an open-drain output that pulls low when output short circuit, output open circuit, overtemperature, or brownout conditions occur. $\overline{\text{ERROR}}$ typically drives an interrupt input of a microcontroller. The $\overline{\text{ERROR}}$ output is cleared after the internal error register is read through the SPI interface. Connect a 10k $\Omega$ pullup resistor from $\overline{\text{ERROR}}$ to DVDD. The MAX15500K/MAX15501K offer enhanced error mode logic. See the Error Handling section and Figures 11a and 11b for more details. |

| 6                | DVDD   | Digital Power-Supply Voltage Input. Apply either a 3V or 5V nominal voltage supply to DVDD. DVDD powers the digital portion of the MAX15500/MAX15501. Bypass DVDD to DGND with a 0.1µF capacitor as close as possible to the device.                                                                                                                                                                                                                                                                                                                                                                              |

| 7                | DGND   | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8, 16,<br>24, 32 | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9                | OUTDIS | Active-Low Output Disable Input. OUTDIS is an active-low logic input that forces the analog output to 0A or 0V and puts the device in standby mode when connected to DGND. Connect OUTDIS to DVDD for normal operation.                                                                                                                                                                                                                                                                                                                                                                                           |

| 10               | FSSEL  | Full-Scale Select Input. Connect FSSEL to DVDD for the MAX15500 when applying a +4.096V reference at REFIN. Connect FSSEL to DGND for the MAX15501 when applying a +2.50V reference at REFIN.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11               | FSMODE | Overrange Mode Select Input. Connect FSMODE to DVDD to set the output voltage to 105%FS when the input voltage is equal to the full-scale value. Connect FSMODE to DGND to set the output voltage to 120%FS when the input voltage is equal to the full-scale value. FSMODE has no effect in current mode.                                                                                                                                                                                                                                                                                                        |

| 12, 15, 27       | AGND   | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13               | REFIN  | Reference Voltage Input. Connect REFIN to an external +4.096V reference for the MAX15500 or +2.5V reference for the MAX15501. REFIN is used to set the offset for unipolar and bipolar modes.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14               | AIN    | Analog Signal Input. The analog input signal range at AIN is from 0V to the nominal full scale of +4.096V for the MAX15500 and +2.5V for the MAX15501.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17               | AVSSO  | Negative Output Driver Supply Voltage Input. AVSSO provides power to the driver output stage. Bypass AVSSO to AVSS with a 0.1µF capacitor. Use diodes as shown in the <i>Typical Operating Circuit/Functional Diagram</i> to ensure a voltage difference of 2V to 3.5V between AVSS and AVSSO.                                                                                                                                                                                                                                                                                                                    |

| 18               | COMP   | Output Amplifier Compensation Feedback Node. Connect a compensation capacitor from COMP to OUT. See Table 10 for the recommended compensation capacitor values.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# Industrial Analog Current/ Voltage-Output Conditioners

### Pin Description (continued)

| PIN | NAME                                                                                                             | FUNCTION                                                                                                                                                                                                                                                                                       |

|-----|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | OUT                                                                                                              | Analog Output. The analog voltage or current output range at OUT is programmable. See Tables 1 to 4 for possible output range settings.                                                                                                                                                        |

| 20  | AVDDO                                                                                                            | Positive Output Driver Supply Voltage Input. AVDDO provides power to the driver output stage. Bypass AVDDO to AVDD with a 0.1µF capacitor. Use diodes as shown in the <i>Typical Operating Circuit/Functional Diagram</i> to ensure a voltage difference of 2V to 3.5V between AVDD and AVDDO. |

| 21  | Sense Resistor Positive Connection. See the <i>Typical Operating Circuit/Functional Diag</i> typical connection. |                                                                                                                                                                                                                                                                                                |

| 22  | SENSERN                                                                                                          | Sense Resistor Negative Connection. See the <i>Typical Operating Circuit/Functional Diagram</i> for the typical connection.                                                                                                                                                                    |

| 23  | SENSEVN                                                                                                          | Kelvin Sense Voltage Negative Input. See the <i>Typical Operating Circuit/Functional Diagram</i> for the typical connection.                                                                                                                                                                   |

| 25  | SENSEVP                                                                                                          | Kelvin Sense Voltage Positive Input. See the <i>Typical Operating Circuit/Functional Diagram</i> for the typical connection.                                                                                                                                                                   |

| 26  | AVDD                                                                                                             | Positive Analog Supply Voltage Input. Bypass AVDD to AGND with a 0.1µF capacitor.                                                                                                                                                                                                              |

| 28  | AVSS                                                                                                             | Negative Analog Supply Voltage Input. Bypass AVSS to AGND with a 0.1µF capacitor.                                                                                                                                                                                                              |

| 29  | MON                                                                                                              | Load Monitoring Output. MON provides an analog 0 to 3V output. See the <i>Output Monitor</i> section.                                                                                                                                                                                          |

| 30  | CS1                                                                                                              | Active-Low SPI Chip-Select Input 1. See the SPI Interface section.                                                                                                                                                                                                                             |

| 31  | CS2                                                                                                              | Active-Low SPI Chip-Select Input 2. See the SPI Interface section.                                                                                                                                                                                                                             |

|     |                                                                                                                  | Exposed Pad. Internally connected to AVSS. Connect to AVSS. Connect to a large copper area to maximize thermal performance. Do not connect ground or signal lines through EP.                                                                                                                  |

# Industrial Analog Current/ Voltage-Output Conditioners

### Typical Operating Circuit/Functional Diagram

## Industrial Analog Current/ Voltage-Output Conditioners

### **Detailed Description**

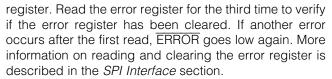

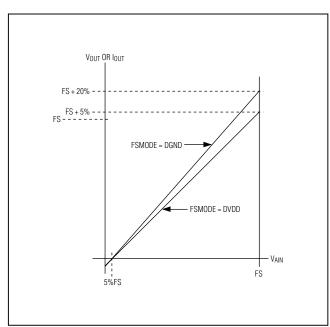

The MAX15500/MAX15501 output a programmable current up to ±24mA or a voltage up to ±12V proportional to a control signal at AIN. The devices operate from a dual 15V to 32.5V supply. The control voltage applied at AIN is typically supplied by an external DAC with an output voltage range of 0 to 4.096V for the MAX15500 and 0 to 2.5V for the MAX15501. The MAX15500/MAX15501 are capable of both unipolar and bipolar current and voltage outputs. In current mode, the devices produce currents of -1.2mA to +24mA or -24mA to +24mA. In voltage mode, the devices produce voltages of -0.3V to +6V. -0.6V to +12V. or  $\pm 12V$ . To allow for overrange and underrange capability in unipolar mode, the transfer function of the MAX15500/MAX15501 is offset such that when the voltage at AIN is 5% of full scale. IOUT is 0mA and Vout is 0V. Once VAIN attains full scale, Vout or IOUT becomes full scale +5% or +20% depending on the state of FSMODE. The devices are protected against overcurrent and short-circuit conditions when OUT goes to ground or a voltage up to ±32.5V. The devices also monitor for overtemperature and supply brownout conditions. The supply brownout threshold is programmable between ±10V and ±24V in 2V increments.

The MAX15500/MAX15501 are programmed through an SPI interface with daisy-chain capability. A device ready logic output (READY) and two device select inputs (CS1 and CS2) facilitate a daisy-chain arrangement for multiple device applications. The MAX15500/MAX15501 provide

Table 1. Output Values for FSMODE = DVDD, Unipolar 5% Overrange

| OUTPUT RANGE               | OUTPUT VALUES           |                       |  |  |  |

|----------------------------|-------------------------|-----------------------|--|--|--|

| OUTPUT RANGE               | V <sub>AIN</sub> = 5%FS | V <sub>AIN</sub> = FS |  |  |  |

| 0 to 20mA<br>(4mA to 20mA) | 0mA                     | 21mA                  |  |  |  |

| 0 to 5V                    | OV                      | 5.25V                 |  |  |  |

| 0 to 10V                   | OV                      | 10.5V                 |  |  |  |

Table 2. Output Values for FSMODE = DGND, Unipolar 20% Overrange

| OUTPUT RANGE               | OUTPUT VALUES |           |  |  |  |

|----------------------------|---------------|-----------|--|--|--|

| OUTPUT RANGE               | VAIN = 5%FS   | VAIN = FS |  |  |  |

| 0 to 20mA<br>(4mA to 20mA) | 0mA           | 24mA      |  |  |  |

| 0 to 5V                    | OV            | 6V        |  |  |  |

| 0 to 10V                   | OV            | 12V       |  |  |  |

extensive error reporting of short-circuit, open-circuit, brownout, and overtemperature conditions through the SPI interface and an additional open-drain interrupt output (ERROR). The MAX15500/MAX15501 include an analog 0 to 3V output (MON) to monitor the load condition at OUT.

### **Analog Section**

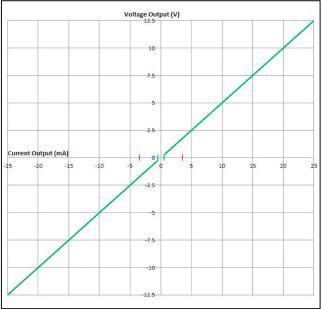

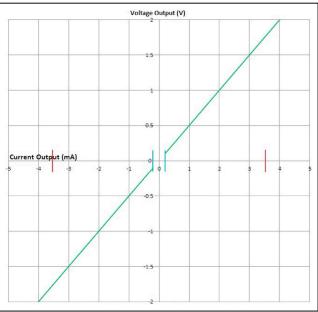

The MAX15500/MAX15501 support two output modes: current and voltage. Each mode has different full-scale output values depending on the state of FSMODE as detailed in Table 1 through Table 4 and Figures 1 and 2. Use the device configuration register in Table 6 to select the desired voltage or current output range.

### Startup

During startup, the MAX15500/MAX15501 output is set to zero and all register bits are set to zero. The devices remain in standby mode until they are configured through the SPI interface.

#### Input Voltage Range

The input voltage full-scale level is selectable between 2.5V and 4.096V using logic input FSSEL. The MAX15500 is specified for a 0 to 4.096V input voltage range, while the MAX15501 is specified for a 0 to 2.500V input voltage range. Connect FSSEL to DVDD to set the input range to 0 to 4.096V for the MAX15500. Connect FSSEL to DGND to set the input range to 0 to 2.500V for the MAX15501.

Table 3. Output Values for FSMODE = DVDD, Bipolar 5% Overrange

| OUTPUT RANGE | VAIN = 0V         VAIN = FS           -21mA         +21mA |                       |  |  |

|--------------|-----------------------------------------------------------|-----------------------|--|--|

| OUTPUT HANGE | V <sub>AIN</sub> = 0V                                     | V <sub>AIN</sub> = FS |  |  |

| ±20mA        | -21mA                                                     | +21mA                 |  |  |

| ±10V         | -10.5V                                                    | +10.5V                |  |  |

Table 4. Output Values for FSMODE = DGND, Bipolar 20% Overrange

| OUTPUT RANGE | OUTPUT                | VALUES                |

|--------------|-----------------------|-----------------------|

| OUTPUT RANGE | V <sub>AIN</sub> = 0V | V <sub>AIN</sub> = FS |

| ±20mA        | -24mA                 | +24mA                 |

| ±10V         | -12V                  | +12V                  |

## Industrial Analog Current/ Voltage-Output Conditioners

#### **Output Monitor**

The MON output provides an analog voltage signal proportional to the output voltage in current mode and proportional to the output current in voltage mode. Use this signal to measure the system load presented to the output. The full-scale signal on MON is 3V with a typical accuracy of 10%. The signal range is typically 1.5V to 3V in unipolar mode and 0 to 3V in bipolar mode.

In current mode, the MAX15500/MAX15501 program IOUT and monitor the voltage at SENSERN.

VMON = 1.425V + (VSENSERN/20)

$R_{LOAD} = ((V_{MON} - 1.425V) \times 20)/I_{OUT}(P_{ROGRAMMED})$  In voltage mode, the MAX15500/MAX15501 program V\_OUT and monitor I\_OUT.

$VMON = 1.521V + 62.4 \times ILOAD$

RLOAD = VOUT(PROGRAMMED)/((VMON - 1.521V)/62.4)

### **Error Handling**

Many industrial control systems require error detection and handling. The devices provide extensive error status reporting. An open-drain interrupt flag output,  $\overline{\text{ERROR}}$ , pulls low when an error condition is detected. An error register stores the error source. Reading the error register once resets the  $\overline{\text{ERROR}}$  pin but not the error register itself, allowing the system to determine the source of the error and take steps to fix the error condition. After the error condition has been fixed, read the error register for the second time to allow the device to clear the error

When an output short-circuit or output open-load error occurs and disappears before the error register is read, the intermittent bit is set in the error register. The intermittent bit does not assert for brownout and overtemperature error conditions. The MAX15500/MAX15501 and MAX15500K/MAX15501K offer different error handling for open circuits and short circuits. See the individual sections, Figure 11a, and Figure 11b for more details.

#### **Error Conditions**

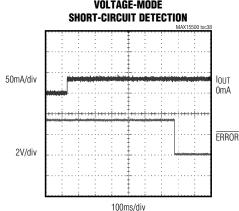

#### **Output Short Circuit**

The output short-circuit error bit asserts when the output current exceeds 30mA (typ) for longer than 260ms. In current mode, this error occurs when the sense resistor is shorted and the sense voltage is not equal to 0V. In voltage mode, this error occurs when the load is shorted to the supply or ground. The short-circuit error activates the intermittent bit in the error register if the error goes away before the error register is read.

The MAX15500/MAX15501 only asserts the short-circuit flag when a short is detected and an open circuit is not detected.

Figure 1. Unipolar Transfer Function

Figure 2. Bipolar Transfer Function

## Industrial Analog Current/ Voltage-Output Conditioners

# Output Short-Circuit: Voltage Mode Only (MAX15500K/MAX15501K)

The output short-circuit error bit asserts when the output current exceeds 30mA (typ) for longer than 260ms in voltage mode only. This error occurs when the load is shorted to the supply or ground. The short-circuit error activates the intermittent bit in the error register if the error goes away before the error register is read.

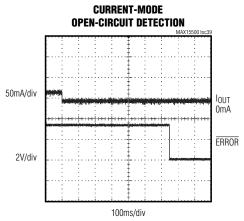

#### Output Open Load (MAX15500/MAX15501)

The open-circuit error bit activates when VOUT is within 30mV of AVDDO or AVSSO and there is no short-circuit current in current mode for longer than 260ms. This error activates the intermittent bit in the error register if the error goes away before the error register is read.

The MAX15500/MAX15501 open-circuit flag is active when both a short circuit and open circuit are detected. The MAX15500/MAX15501 does not flag open circuit when the load current is between -3.5mA (typ) to +3.5mA (typ). Figure 11a shows the full range of the open circuit detection range and Figure 11b offers a zoomed in view. The MAX15500/MAX15501 are shown in the red lines.

#### Output Open Load (MAX15500K/MAX15501K)

The open-circuit error bit activates when VOUT is within 30mV of AVDDO or AVSSO for longer than 260ms. This error activates the intermittent bit in the error register if the error goes away before the error register is read.

The MAX15500K/MAX15501K does not flag open circuit when the load current is between -0.5mA (typ) to +0.5mA (typ). Figure 11a shows the full range of the open circuit detection range and Figure 11b offers a zoomed in view. The MAX15500K/MAX15501K are shown in the green lines.

#### **Internal Overtemperature**

The MAX15500/MAX15501 enter standby mode if the die temperature exceeds +150°C and the overtemperature protection is enabled as shown in Table 6. When the die temperature cools down below +140°C, the error register must be read back twice to resume normal operation. The devices provide a 10°C hysteresis. The MAX15500/MAX15501 and MAX15500K/MAX15501K all trigger the overtemperature ERROR flag in the same manner.

#### **Brownout**

The brownout-error bit activates when the supply voltage (VAVDD or VAVSS) falls below the brownout threshold. The threshold is programmable between ±10V to ±24V in 2V steps. See Table 6 for details. The MAX15500/MAX15501 provide a 2% hysteresis for the brownout threshold. The accuracy of the threshold is typically within 10%. During power-up, ERROR can go low and the brownout register is set. Users need to read out the error register twice to clear all the error register bits and reset ERROR to high. The MAX15500/MAX15501 and MAX15500K/MAX15501K all trigger the overtemperature ERROR flag in the same manner.

#### **Output Protection**

The MAX15500/MAX15501 supply inputs (AVDD, AVDDO, AVSS, and AVSSO) and sense inputs (SENSERN, SENSERP, SENSEVN, and SENSEVP) are protected against voltages up to ±35V with respect to AGND. See the *Typical Operating Circuit/Functional Diagram* for the recommended supply-voltage connection.

#### SPI Interface

#### **Standard SPI Implementation**

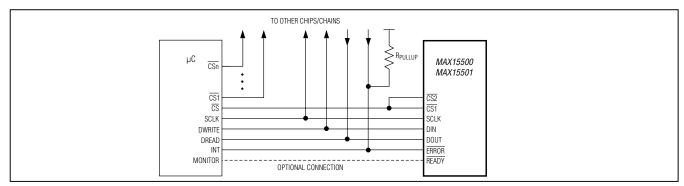

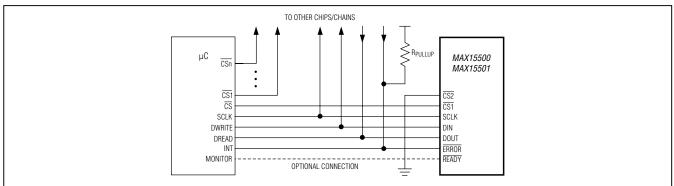

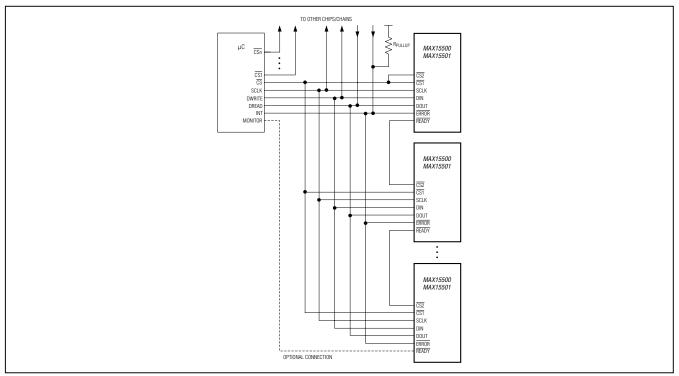

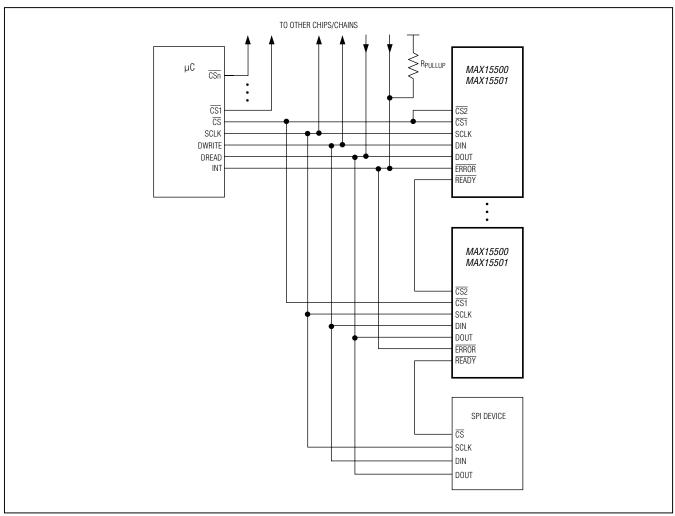

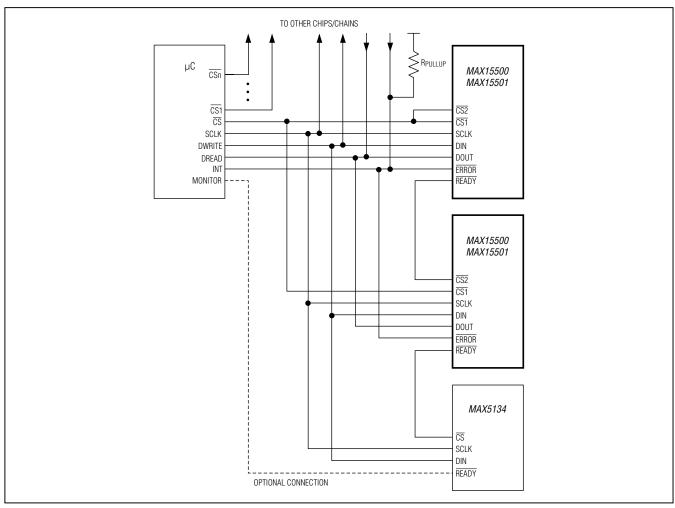

The MAX15500/MAX15501 SPI interface supports daisychaining. Multiple MAX15500/MAX15501 devices can be controlled from a single 4-wire SPI interface. The MAX15500/MAX15501 feature dual CS\_ inputs and an added digital output, READY, that signals when the devices finish processing the SPI frame. CS1 and  $\overline{\text{CS2}}$  are internally OR-ed. Pull both  $\overline{\text{CS1}}$  and  $\overline{\text{CS2}}$  to logic-low to activate the MAX15500/MAX15501. For a daisy-chained application, connect the CS1 input of all of the devices in the chain to the  $\overline{\text{CS}}$  driver of the microcontroller. Connect the CS2 input of the first device to ground or to the  $\overline{\text{CS}}$  driver of the microcontroller. Connect CS2 of the remaining devices to the READY output of the preceding device in the chain. The READY output of the last device in the chain indicates when all slave devices in the chain are configured. Connect the READY output of the last device in the chain to the microcontroller. Use the open-drain ERROR output as a wired-OR interrupt. See Figures 3 to 6.

# Industrial Analog Current/ Voltage-Output Conditioners

Figure 3. Single Connection (Compatible with Standard SPI)

Figure 4. Alternate Single Connection (Compatible with Standard SPI)

Figure 5. Daisy-Chain Connection (Compatible with Standard SPI)

# Industrial Analog Current/ Voltage-Output Conditioners

Figure 6. Daisy-Chain Terminating (Compatible with Standard SPI)

#### **Modified SPI Interface Description**

The SCLK, DIN, and DOUT of the MAX15500/MAX15501 assume standard SPI functionality. While the basic function of the MAX15500/MAX15501  $\overline{CS}_{-}$  inputs is similar to the standard SPI interface protocol, the management of the  $\overline{CS}_{-}$  input within the chain is modified. When both  $\overline{CS}_{-}$  inputs are low, the MAX15500/MAX15501 assume control of the DOUT line and continue to control the line until the data frame is finished and  $\overline{READY}$  goes low (Figure 9). Once a complete frame is processed and the  $\overline{READY}$  signal is issued, the devices do not accept any data from DIN, until either  $\overline{CS1}$  or  $\overline{CS2}$  rises and returns

low. A new communication cycle is initiated by a subsequent falling edge on  $\overline{CS1}$  or  $\overline{CS2}$ . When either  $\overline{CS1}$  or  $\overline{CS2}$  is high, the MAX15500/MAX15501 SPI interface deactivates, DOUT returns to a high-impedance mode,  $\overline{READY}$  (if active) clears, and any partial frames not yet processed are ignored.

READY asserts once a valid frame is processed allowing the next device in the chain to begin processing the subsequent frame. A valid frame consists of 16 SCLK cycles following the falling edge of  $\overline{CS}$ . Once  $\overline{READY}$  asserts, it remains asserted until either  $\overline{CS}$  rises, completing the programming of the chain.

## Industrial Analog Current/ Voltage-Output Conditioners

The MAX15500/MAX15501 relinquish control of DOUT once the devices process the frame(s). DOUT remains high impedance when the SPI interface continues to hold  $\overline{\text{CS}}_{-}$  low beyond the required frame(s). Install a pullup/puldown resistor at the DOUT line to maintain the desired state when DOUT goes high impedance.

#### **Single Device SPI Connection**

For applications using a single MAX15500 or MAX15501, connect both  $\overline{CS1}$  and  $\overline{CS2}$  inputs to the device-select driver of the host microcontroller. Alternatively, connect one of the  $\overline{CS}$  inputs to the device-select driver of the host microcontroller and the other  $\overline{CS}$  to DGND. Both methods allow standard SPI interface operation. See Figures 3 and 4.

#### **Daisy-Chain SPI Connection**

The MAX15500/MAX15501-modified SPI interface allows a single SPI master to drive multiple devices in a daisy-chained configuration, saving additional SPI channels for other devices and saving cost in isolated applications.

Figure 5 shows multiple MAX15500/MAX15501 devices connected in a daisy chain. The chain behaves as a single device to the microcontroller in terms of timing with an expanded instruction frame requiring 16 SCLK cycles per device for complete programming. No timing parameters are affected by the READY propagation as all devices connect to the microcontroller chip-select through the CS1 inputs.

A chain of MAX15500/MAX15501 devices can be terminated with any standard SPI-compatible single device without a READY output. The MAX15500/MAX15501 portion of the chain continues to display timing parameters comparable to a single device. See Figure 6.

When using the MAX15500/MAX15501 with mixed chains, the connections could require some modification to accommodate the interfaces of the additional devices in the chain. Construct the daisy chain as shown in Figure 7 when using devices with similar READY outputs but without dual  $\overline{CS}$  inputs such as the MAX5134 quad 16-bit DAC. The chain is subject to timing relaxation for parameters given with respect to  $\overline{CS}$  rising edges to accommodate  $\overline{READY}$  propagation to and through consecutive MAX5134 devices.

The chain can begin and terminate with either device type. Each MAX5134 or MAX15500/MAX15501 device in the chain could be replaced by a subchain of similar devices. If the chain is terminated with a standard SPI device, omit the optional connection from READY to the

monitor input on the microcontroller. The MAX15500/MAX15501 portion of the chain continues to display timing parameters comparable to a single device.

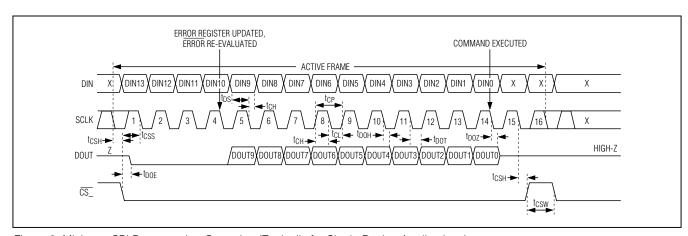

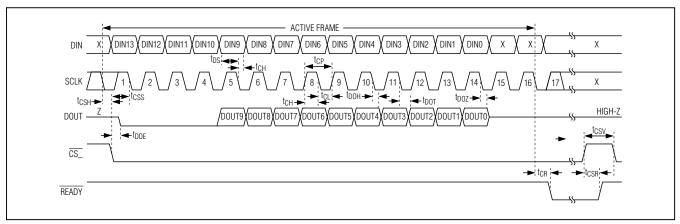

### SPI Digital Specifications and Waveforms

Figures 8, 9, and 10 show the operation of the modified SPI interface. The minimum programming operation typically used in single device applications is 16 SCLK periods, the minimum for a valid frame. This cycle can also represent the operation of the final device in a chain.

The extended programming operation is typically used for devices in daisy-chained applications. In this case, READY drives the chip-select input of the subsequent device in the chain. The next device in the chain begins its active frame on the 16th SCLK falling edge in response to READY falling (latching DIN[13] on the 17th SCLK falling edge, if present).

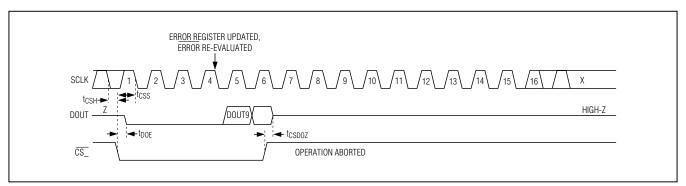

### **Aborted SPI Operations**

Driving a  $\overline{\text{CS}_-}$  input high before a valid SPI frame is transmitted to the device can cause an erroneous command. Avoid driving  $\overline{\text{CS}_-}$  high before a valid SPI frame is transmitted to the device. See Figures 9 and 10 for valid SPI operation timing.

#### SPI Operation Definitions

Input data bits DIN[13:11] represent the SPI command address while DIN[9:0] represent the data written to or read from the command address. The command address directs subsequent input data to the proper internal register for setting up the behavior of the device and selects the correct status data for readback through DOUT. Command address 0h points to a no-op command and does not impact the operation of the device. DOUT is active during this operation and reads back 00h. Command address 1h points to the configuration register used to program the MAX15500/MAX15501. Device configuration takes effect following the 14th SCLK falling edge. DOUT activates and remains low during this operation. Command addresses 4h and 5h point to readback commands of the MAX15500/MAX15501. Readback commands provide configuration and error register status through DOUT[9:0] and do not affect the internal operation of the device. Command addresses 2h, 3h, 6h, and 7h are reserved for future use. Table 5 shows the list of commands.

#### **Device Configuration Operation**

Table 6 shows the function of each bit written to the configuration register 1h. Table 7 shows the data readback registers.

# Industrial Analog Current/ Voltage-Output Conditioners

Figure 7. Mixed MAX15500/MAX15501 and MAX5134 Daisy-Chain Connections

Figure 8. Minimum SPI Programming Operation (Typically for Single Device Applications)

# Industrial Analog Current/ Voltage-Output Conditioners

Figure 9. Extended SPI Programming Operation (Daisy-Chained Applications)

Figure 10. Aborted SPI Programming Operation (Invalid, Showing t<sub>CSDOZ</sub> and Internal Activity)

### Readback Operations

Write to the command addresses 4h or 5h to read back the configuration register data or the internal error information through DOUT[9:0]. For error readback operations, each bit corresponds to a specific error condition, with multiple bits indicating multiple error conditions present.

### Intermittent Errors

An intermittent error is defined as an error that is detected and is resolved before the error register is read back. When the error is resolved without intervention, the intermittent bit (bit 9) is set. The output short-circuit and output open-load errors trigger the intermittent bit. Internal over-

temperature and supply voltage brownout do not trigger the intermittent bit.

### **Error Reporting Applications**

The ERROR output is typically connected to an interrupt input of the system microcontroller. The MAX15500/MAX15501 only issue an interrupt when a new error condition is detected. The devices do not issue interrupts when errors (either individual or multiple) are resolved or when already reported errors persist. The system microcontroller resets ERROR when the system microcontroller reads back the error register. ERROR does not assert again unless a different error occurs.

# Industrial Analog Current/ Voltage-Output Conditioners

Figure 11a. Diagram Showing the MAX15500/MAX15501 "Plain" (Red) and the MAX15500K/MAX15501K (Teal) Open-Circuit Detection Windows

Figure 11b. Zoomed In Diagram Showing the MAX15500/ MAX15501 "Plain" (Red) and the MAX15500K/MAX15501K (Teal) Open-Circuit Detection Windows

# Industrial Analog Current/ Voltage-Output Conditioners

**Table 5. SPI Commands**

| COMMAND<br>ADDRESS<br>DIN[13:11] | NAME                | DESCRIPTION                                                   |

|----------------------------------|---------------------|---------------------------------------------------------------|

| 000                              | No-op               | No operation.                                                 |

| 001                              | Write configuration | Write device configuration register. See Table 6 for details. |

| 010                              | Reserved            | Reserved, no operation.                                       |

| 011                              | Reserved            | Reserved, no operation.                                       |

| 100                              | Read error          | Read error register status. See Table 7 for details.          |

| 101                              | Read configuration  | Read device configuration register. See Table 6 for details.  |

| 110                              | Reserved            | Reserved, no operation.                                       |

| 111                              | Reserved            | Reserved, no operation.                                       |

## **Table 6. Configuration Register**

| LOCATION             | FUNCTION         | DESCRIPTION                                                                                                                                                                  |                                                                                                                                                 |  |  |  |

|----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DIN[9:7]             | Mode[2:0]        | Sets device operating mode.  000 Mode[0]: Standby  001 Mode[1]: Bipolar current: ±20mA  010 Mode[2]: Unipolar current: 0 to 20mA  011 Mode[3]: Unipolar current: 4mA to 20mA | 100 Mode[4]: Standby<br>101 Mode[5]: Bipolar voltage: ±10V<br>110 Mode[6]: Unipolar voltage: 0 to 10V<br>111 Mode[7]: Unipolar voltage: 0 to 5V |  |  |  |

| DIN[6:4]             | VBOTH[2:0]       | Sets supply voltage brownout threshold for error 000: ±10V 100: ±18V 001: ±12V 101: ±20V 010: ±14V 110: ±22V 011: ±16V 111: ±24V                                             | or reporting.                                                                                                                                   |  |  |  |

| DIN[3]               | Thermal shutdown | 0 = thermal protection off. 1 = thermal protection                                                                                                                           | on on.                                                                                                                                          |  |  |  |

| DIN[10],<br>DIN[2:0] | _                | Reserved                                                                                                                                                                     |                                                                                                                                                 |  |  |  |

Note: Modes 2h and 3h are functionally identical.

### **Table 7. Readback Operations and Formatting**

| DOUT BITS          | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| COMMAND ADD        | DRESS DIN[13:11] = 101. READBACK DEVICE CONFIGURATION REGISTER                                                                                                                                                                                                                                                                            |  |

| DOUT[9:0]          | See configuration register details in Table 6.                                                                                                                                                                                                                                                                                            |  |

| COMMAND ADD        | DRESS DIN[13:11] = 100. READBACK ERROR REGISTER                                                                                                                                                                                                                                                                                           |  |

| DOUT[9]            | Output Intermittent Fault. For details, see the Error Handling section.                                                                                                                                                                                                                                                                   |  |

| DOUT[8]            | Output Short Circuit. Output short circuit. In the MAX15500/MAX15501, this bit asserts when IOUT > 30mA in voltage and current modes for longer than 260ms. In the MAX15500K/MAX15501K, this bit asserts when lout > 30mA for longer than 260ms (in voltage mode only).                                                                   |  |

| DOUT[7]            | Output Open Load. In the MAX15500/MAX15501, this bit asserts when VOUT is within 30mV of AVDDO or AVSSO and there is no short-circuit condition for longer than 260ms. In the MAX15500K/MAX15501K, the output open load bit asserts when V <sub>OUT</sub> is within 30mV of AV <sub>DDO</sub> or AV <sub>SSO</sub> for longer than 260ms. |  |

| DOUT[6]            | Internal Overtemperature. This bit asserts when the die temperature exceeds +150°C.                                                                                                                                                                                                                                                       |  |

| DOUT[5]            | Supply Brownout. This bit asserts when either supply has entered the brownout limits. See Table 6 for details.                                                                                                                                                                                                                            |  |