## **General Description**

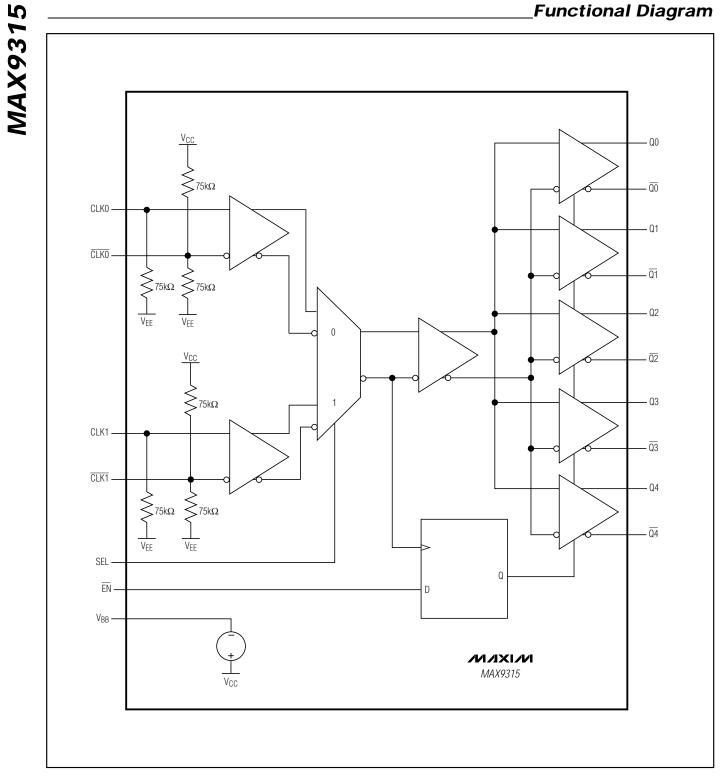

The MAX9315 low-skew, 1-to-5 differential driver is designed for clock and data distribution. This device allows selection between two inputs. The selected input is reproduced at five differential outputs. The differential inputs can be adapted to accept a single-ended input by connecting the on-chip V<sub>BB</sub> supply to one input as a reference voltage.

The MAX9315 features low output-to-output skew (20ps), making it ideal for clock and data distribution across a backplane or a board. For interfacing to differential HSTL and LVPECL signals, this device operates over a +2.375V to +3.8V supply range, allowing high-performance clock or data distribution in systems with a nominal +2.5V or +3.3V supply. For differential LVECL operation, this device operates with a -2.375V to -3.8V supply.

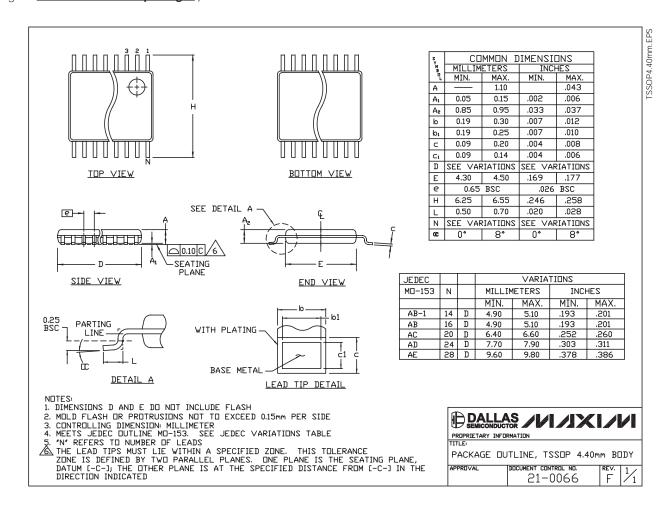

The MAX9315 is offered in a space-saving 20-pin TSSOP package.

### **Applications**

Precision Clock Distribution Low-Jitter Data Repeater Data and Clock Driver and Buffer Central Office Backplane Clock Distribution DSLAM Backplane

Base Station

ATE

19-2220; Rev 1; 11/04

EVALUATION KIT AVAILABLE

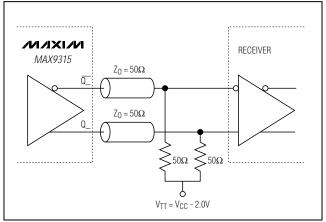

## \_Typical Application Circuit

#### Functional Diagram appears at end of data sheet.

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### \_Features

- +2.375V to +3.8V Supply for Differential HSTL/LVPECL Operation

- -2.375V to -3.8V Supply for Differential LVECL Operation

- Two Selectable Differential Inputs

- Synchronous Output Enable/Disable

- ♦ 20ps Output-to-Output Skew

- ♦ 360ps Propagation Delay

- Guaranteed 400mV Differential Output at 1.5GHz

- On-Chip Reference for Single-Ended Inputs

- Input Biased Low when Left Open

- Pin Compatible with MC100LVEP14

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |  |  |  |  |

|------------|----------------|-------------|--|--|--|--|

| MAX9315EUP | -40°C to +85°C | 20 TSSOP    |  |  |  |  |

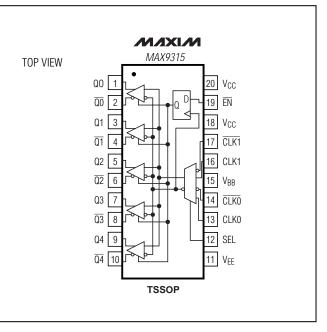

## Pin Configuration

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> - V <sub>EE</sub>                                     | 1V  |

|-----------------------------------------------------------------------|-----|

| Inputs (CLK_, CLK_, SEL, EN)                                          |     |

| to V <sub>EE</sub> (V <sub>EE</sub> - 0.3V) to (V <sub>CC</sub> + 0.3 | 3V) |

| CLK_ to CLK±3                                                         | VO  |

| Continuous Output Current                                             | nΑ  |

| Surge Output Current                                                  | nΑ  |

| VBB Sink/Source Current±0.65r                                         | nΑ  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                 |     |

| Single-Layer PC Board                                                 |     |

| 20-Pin TSSOP (derate 7.69mW/°C above +70°C)615n                       | nW  |

| Multilayer PC Board                                                   |     |

| 20-Pin TSSOP (derate 10.9mW/°C above +70°C)879n                       | nW  |

| Junction-to-Ambient Thermal Resistance in Still Air                   |     |

| Single-Layer PC Board                                                 |     |

| 20-Pin TSSOP+130°C                                                    | /W  |

|                                                                       |     |

| Multilayer PC Board                                 |

|-----------------------------------------------------|

| 20-Pin TSSOP+91°C/W                                 |

| Junction-to-Ambient Thermal Resistance with 500LFPM |

| Airflow Single-Layer PC Board                       |

| 20-Pin TSSOP+9.6°C/W                                |

| Junction-to-Case Thermal Resistance                 |

| 20-Pin TSSOP+20°C/W                                 |

| Operating Temperature Range40°C to +85°C            |

| Junction Temperature+150°C                          |

| Storage Temperature Range65°C to +150°C             |

| ESD Protection                                      |

| Human Body Model (Inputs and Outputs)≥2kV           |

| Soldering Temperature (10s)+300°C                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

$(V_{CC} - V_{EE} = 2.375V \text{ to } 3.8V, \text{ outputs loaded with } 50\Omega \pm 1\% \text{ to } V_{CC} - 2V, \text{ SEL} = \text{high or low}, \overline{EN} = \text{low}, \text{ unless otherwise noted}. Typical values are at V_{CC} - V_{EE} = +3.3V, V_{IHD} = V_{CC} - 1V, V_{ILD} = V_{CC} - 1.5V.) (Notes 1, 2, 3)$

| PARAMETER                                      | SYMBOL CONDITIONS |                                             |                            | -40°C |                            | +25°C                      |     |                            | +85°C                      |     |                            |       |

|------------------------------------------------|-------------------|---------------------------------------------|----------------------------|-------|----------------------------|----------------------------|-----|----------------------------|----------------------------|-----|----------------------------|-------|

| PARAMETER                                      | STIVIBUL          | CONDITIONS                                  | MIN                        | TYP   | MAX                        | MIN                        | ΤΥΡ | MAX                        | MIN                        | TYP | MAX                        | UNITS |

| SINGLE-ENDED INPUTS (SEL, EN)                  |                   |                                             |                            |       |                            |                            |     |                            |                            |     |                            |       |

| Input High Voltage                             | VIH               |                                             | V <sub>CC</sub> -<br>1.225 |       | V <sub>CC</sub>            | V <sub>CC</sub> -<br>1.225 |     | V <sub>CC</sub>            | V <sub>CC</sub> -<br>1.225 |     | V <sub>CC</sub>            | V     |

| Input Low Voltage                              | VIL               |                                             | VEE                        |       | V <sub>CC</sub> -<br>1.625 | V <sub>EE</sub>            |     | V <sub>CC</sub> -<br>1.625 | VEE                        |     | V <sub>CC</sub> -<br>1.625 | V     |

| Input Current                                  | lin               | VIH(MAX), VIL(MIN)                          | -500                       |       | 500                        | -500                       |     | 500                        | -500                       |     | 500                        | μA    |

| DIFFERENTIAL INP                               | JTS (CLK_         | , <u>CLK_</u> )                             |                            |       |                            |                            |     |                            |                            |     |                            |       |

| Single-Ended Input<br>High Voltage<br>(Note 4) | VIH               | V <sub>BB</sub> connected to CLK_, Figure 1 | V <sub>CC</sub> -<br>1.225 |       | V <sub>CC</sub>            | V <sub>CC</sub> -<br>1.225 |     | Vcc                        | V <sub>CC</sub> -<br>1.225 |     | V <sub>CC</sub>            | V     |

| Single-Ended Input<br>Low Voltage<br>(Note 4)  | VIL               | V <sub>BB</sub> connected to CLK_, Figure 1 | V <sub>EE</sub>            |       | V <sub>CC</sub> -<br>1.625 | VEE                        |     | V <sub>CC</sub> -<br>1.625 | VEE                        |     | V <sub>CC</sub> -<br>1.625 | V     |

| High Voltage of<br>Differential Input          | VIHD              |                                             | V <sub>EE</sub> + 1.2      |       | V <sub>CC</sub>            | V <sub>EE</sub> + 1.2      |     | V <sub>CC</sub>            | V <sub>EE</sub> +<br>1.2   |     | V <sub>CC</sub>            | V     |

| Low Voltage of<br>Differential Input           | VILD              |                                             | VEE                        |       | V <sub>CC</sub> -<br>0.1   | V <sub>EE</sub>            |     | V <sub>CC</sub> -<br>0.1   | VEE                        |     | V <sub>CC</sub> -<br>0.1   | V     |

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} - V_{EE} = 2.375V \text{ to } 3.8V, \text{ outputs loaded with } 50\Omega \pm 1\% \text{ to } V_{CC} - 2V, \text{ SEL} = \text{high or low, } \overline{EN} = \text{low, unless otherwise noted. Typical values are at } V_{CC} - V_{EE} = +3.3V, V_{IHD} = V_{CC} - 1V, V_{ILD} = V_{CC} - 1.5V.$  (Notes 1, 2, 3)

| PARAMETER                              | SYMBOL                               | CONDITIONS                                                              | -40°C                      |     |                                      | +25°C                      |     |                                      | +85°C                      |     |                                      |    |

|----------------------------------------|--------------------------------------|-------------------------------------------------------------------------|----------------------------|-----|--------------------------------------|----------------------------|-----|--------------------------------------|----------------------------|-----|--------------------------------------|----|

|                                        | SYMBOL                               |                                                                         | MIN                        | TYP | MAX                                  | MIN                        | TYP | MAX                                  | MIN                        | TYP | MAX                                  |    |

| Differential Input                     | Vihd -                               | For (V <sub>CC</sub> - V <sub>EE</sub> ) <<br>+3.0V                     | 0.1                        |     | V <sub>CC</sub> -<br>V <sub>EE</sub> | 0.1                        |     | V <sub>CC</sub> -<br>V <sub>EE</sub> | 0.1                        |     | V <sub>CC</sub> -<br>V <sub>EE</sub> | V  |

| Voltage                                | Vild                                 | For (V <sub>CC</sub> - V <sub>EE</sub> ) ≥ $+3.0V$                      | 0.1                        |     | 3.0                                  | 0.1                        |     | 3.0                                  | 0.1                        |     | 3.0                                  | >  |

| Input Current                          | lin                                  | V <sub>IH</sub> , V <sub>IL</sub> , V <sub>IHD</sub> , V <sub>ILD</sub> | -150                       |     | 150                                  | -150                       |     | 150                                  | -150                       |     | 150                                  | μA |

| OUTPUTS ( $Q_{,} \overline{Q}_{)$      |                                      |                                                                         |                            |     |                                      |                            |     |                                      | -                          |     |                                      |    |

| Single-Ended<br>Output High<br>Voltage | Voh                                  | Figure 1                                                                | V <sub>CC</sub> -<br>1.145 |     | V <sub>CC</sub> -<br>0.865           | V <sub>CC</sub> -<br>1.145 |     | V <sub>CC</sub> -<br>0.865           | V <sub>CC</sub> -<br>1.145 |     | V <sub>CC</sub> -<br>0.865           | V  |

| Single-Ended<br>Output Low<br>Voltage  | V <sub>OL</sub>                      | Figure 1                                                                | V <sub>CC</sub> -<br>1.945 |     | V <sub>CC</sub> -<br>1.695           | V <sub>CC</sub> -<br>1.945 |     | V <sub>CC</sub> -<br>1.695           | V <sub>CC</sub> -<br>1.945 |     | V <sub>CC</sub> -<br>1.695           | V  |

| Differential Output<br>Voltage         | V <sub>OH</sub> -<br>V <sub>OL</sub> | Figure 1                                                                | 550                        |     | 910                                  | 550                        |     | 910                                  | 550                        |     | 910                                  | mV |

| REFERENCE                              | REFERENCE                            |                                                                         |                            |     |                                      |                            |     |                                      |                            |     |                                      |    |

| Reference Voltage<br>Output (Note 5)   | V <sub>BB</sub>                      | $I_{BB} = \pm 0.5 \text{mA}$                                            | V <sub>CC</sub> -<br>1.525 |     | V <sub>CC</sub> -<br>1.325           | V <sub>CC</sub> -<br>1.525 |     | V <sub>CC</sub> -<br>1.325           | 00                         |     | V <sub>CC</sub> -<br>1.325           | V  |

| SUPPLY                                 |                                      |                                                                         |                            |     |                                      |                            |     |                                      |                            |     |                                      |    |

| Supply Current<br>(Note 6)             | IEE                                  |                                                                         |                            | 41  | 48                                   |                            | 45  | 55                                   |                            | 49  | 65                                   | mA |

### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} - V_{EE} = 2.375V \text{ to } 3.8V, \text{ outputs loaded with } 50\Omega \pm 1\% \text{ to } V_{CC} - 2V, \text{ input frequency} = 1.5GHz, \text{ input transition time} = 125ps (20\% \text{ to } 80\%), \text{ SEL} = \text{ high or low}, \overline{EN} = \text{ low}, \text{ V}_{IHD} = \text{ V}_{EE} + 1.2V \text{ to } \text{ V}_{CC}, \text{ V}_{ILD} = \text{ V}_{EE} \text{ to } \text{ V}_{CC} - 0.15V, \text{ V}_{IHD} - \text{ V}_{ILD} = 0.15V \text{ to the smaller of } 3V \text{ or } \text{ V}_{CC} - \text{ V}_{EE}, \text{ unless otherwise noted}. \text{ Typical values are at } \text{ V}_{CC} - \text{ V}_{EE} = +3.3V, \text{ V}_{IHD} = \text{ V}_{CC} - 1V, \text{ V}_{ILD} = \text{ V}_{CC} - 1.5V.$  (Notes 1, 7)

|                                            |                                         |                                                              |     | -40°C |     | +25°C |     |     | +85°C |     |     | UNITS    |

|--------------------------------------------|-----------------------------------------|--------------------------------------------------------------|-----|-------|-----|-------|-----|-----|-------|-----|-----|----------|

| PARAMETER                                  | SYMBOL                                  | CONDITIONS                                                   | ΜΙΝ | ТҮР   | MAX | MIN   | ТҮР | MAX | MIN   | ТҮР | МАХ | ps       |

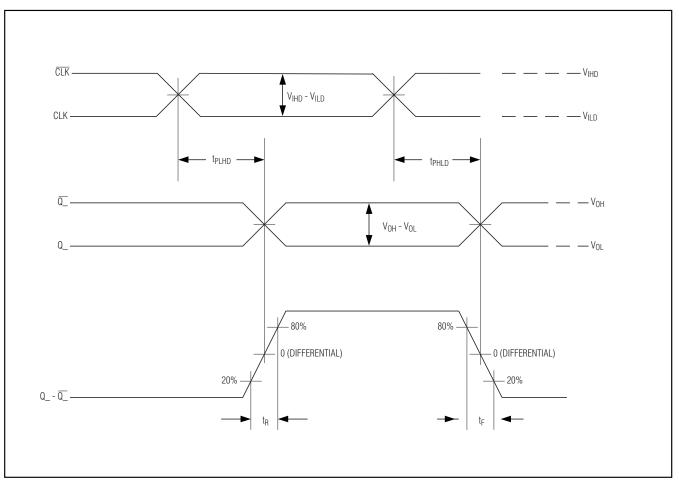

| Differential Input-<br>to-Output Delay     | <sup>t</sup> PLHD,<br><sup>t</sup> PHLD | Figure 2                                                     | 290 |       | 400 | 310   |     | 440 | 300   |     | 520 | ps       |

| Output-to-Output<br>Skew (Note 8)          | tskoo                                   |                                                              |     | 5     | 30  |       | 20  | 40  |       | 20  | 50  | ps       |

| Part-to-Part Skew<br>(Note 9)              | t <sub>SKPP</sub>                       |                                                              |     |       | 110 |       |     | 130 |       |     | 220 | ps       |

| Added Random<br>Jitter (Note 10)           | t <sub>RJ</sub>                         | $f_{IN} = 1.5 GHz clock$                                     |     | 0.8   | 1.2 |       | 0.8 | 1.2 |       | 0.8 | 1.2 | ps (RMS) |

| Added<br>Deterministic Jitter<br>(Note 10) | t <sub>DJ</sub>                         | 1.5Gbps 2E <sup>23</sup> -1<br>PRBS pattern                  |     | 50    | 70  |       | 50  | 70  |       | 50  | 70  | ps (p-p) |

| Switching<br>Frequency                     | fMAX                                    | (V <sub>OH</sub> - V <sub>OL</sub> ) ≥<br>400mV,<br>Figure 2 | 1.5 |       |     | 1.5   |     |     | 1.5   |     |     | GHz      |

| Output Rise/Fall<br>Time (20% to 80%)      | t <sub>R</sub> , t <sub>F</sub>         | Figure 2                                                     | 80  |       | 120 | 90    |     | 130 | 90    |     | 145 | ps       |

Note 1: Measurements are made with the device in thermal equilibrium.

**Note 2:** Current into a pin is defined as positive. Current out of a pin is defined as negative.

**Note 3:** DC parameters production tested at  $T_A = +25^{\circ}C$  and guaranteed by design over the full operating temperature range.

Note 4: Single-ended input operation using  $V_{BB}$  is limited to  $V_{CC}$  -  $V_{EE}$  = 3.0V to 3.8V.

Note 5: Use  $V_{BB}$  only for inputs that are on the same device as the  $V_{BB}$  reference.

**Note 6:** All pins open except  $V_{CC}$  and  $V_{EE}$ .

**Note 7:** Guaranteed by design and characterization. Limits are set at ±6 sigma.

Note 8: Measured between outputs of the same part at the signal crossing points for a same-edge transition.

Note 9: Measured between outputs of different parts at the signal crossing points under identical conditions for a same-edge transition.

Note 10: Device jitter added to the input signal.

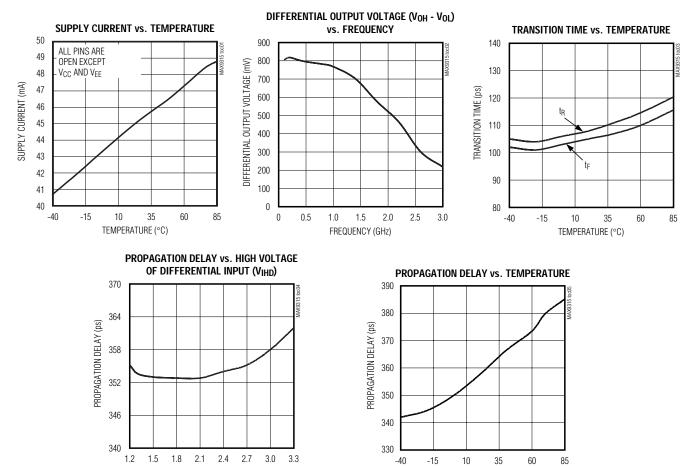

### \_Typical Operating Characteristics

TEMPERATURE (°C)

$(V_{CC} = +3.3V, V_{EE} = 0, V_{IHD} = V_{CC} - 1V, V_{ILD} = V_{CC} - 1.15V$ , input transition time = 125ps (20% to 80%), f<sub>IN</sub> = 2GHz, outputs loaded with 50 $\Omega$  to V<sub>CC</sub> - 2V, T<sub>A</sub> = +25°C, unless otherwise noted.)

V<sub>IHD</sub> (V)

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                             |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Q0              | Noninverting Q0 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                       |

| 2      | QO              | Inverting Q0 Output. Typically terminate with $50\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                           |

| 3      | Q1              | Noninverting Q1 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                       |

| 4      | Q1              | Inverting Q1 Output. Typically terminate with $50\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                           |

| 5      | Q2              | Noninverting Q2 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                       |

| 6      | Q2              | Inverting Q2 Output. Typically terminate with $50\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                           |

| 7      | Q3              | Noninverting Q3 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                       |

| 8      | $\overline{Q3}$ | Inverting Q3 Output. Typically terminate with $50\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                           |

| 9      | Q4              | Noninverting Q4 Output. Typically terminate with 50 $\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                       |

| 10     | $\overline{Q4}$ | Inverting Q4 Output. Typically terminate with $50\Omega$ resistor to V <sub>CC</sub> - 2V.                                                                                                                                           |

| 11     | VEE             | Negative Supply Voltage                                                                                                                                                                                                              |

| 12     | SEL             | Clock Select Input (Single Ended). Drive low to select the CLK0, $\overline{CLK0}$ input. Drive high to select the CLK1, $\overline{CLK1}$ input. The SEL threshold is equal to V <sub>BB</sub> .                                    |

| 13     | CLK0            | Noninverting Differential Clock Input 0. Internal 75k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                                                         |

| 14     | CLKO            | Inverting Differential Clock Input 0. Internal 75k $\Omega$ pullup to V <sub>CC</sub> and 75k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                 |

| 15     | V <sub>BB</sub> | Reference Output Voltage. Connect to the inverting or noninverting clock input to provide a reference for single-ended operation. When used, bypass with a $0.01\mu$ F ceramic capacitor to V <sub>CC</sub> ; otherwise, leave open. |

| 16     | CLK1            | Noninverting Differential Clock Input 1. Internal 75k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                                                         |

| 17     | CLK1            | Inverting Differential Clock Input 1. Internal 75k $\Omega$ pullup to V <sub>CC</sub> and 75k $\Omega$ pulldown to V <sub>EE</sub> .                                                                                                 |

| 18, 20 | V <sub>CC</sub> | Positive Supply Voltage. Bypass $V_{CC}$ to $V_{EE}$ with $0.1\mu$ F and $0.01\mu$ F ceramic capacitors. Place the capacitors as close to the device as possible with the smaller value capacitor closest to the device.             |

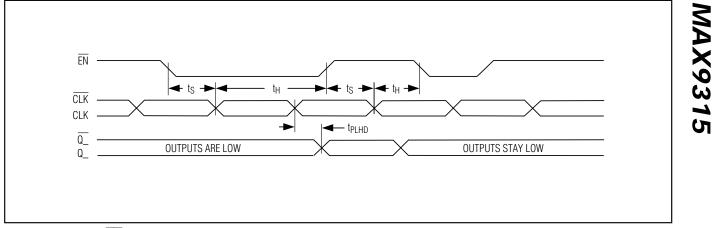

| 19     | ĒN              | Output Enable Input. Outputs are synchronously enabled on the falling edge of the selected clock input when EN is low. Outputs are synchronously driven low on the falling edge of the selected clock input when EN is high.         |

### Detailed Description

The MAX9315 is a low-skew, 1-to-5 differential driver designed for clock or data distribution. A 2-to-1 MUX selects one of the two differential clock inputs, CLK0,  $\overline{CLK0}$  or CLK1,  $\overline{CLK1}$ . The MUX is switched by the single-ended SEL input. A logic low selects the CLK0,  $\overline{CLK0}$  input and a logic high selects the  $\overline{CLK1}$ , CLK1 input. The SEL logic threshold is set by the internal voltage reference V<sub>BB</sub>. SEL can be driven to V<sub>CC</sub> and V<sub>EE</sub> or by a single-ended LVPECL/LVECL signal. The selected input is reproduced at five differential outputs.

#### Synchronous Enable

The MAX9315 is synchronously enabled and disabled with outputs in the low state to eliminate shortened clock pulses. EN is connected to the input of an edge-triggered D flip-flop. After power-up, drive EN low and

toggle the selected clock input to enable the outputs. The outputs are enabled on the falling edge of the selected clock input after  $\overline{\text{EN}}$  goes low. The outputs are set to a low state on the falling edge of the selected clock input after  $\overline{\text{EN}}$  goes high. The threshold for  $\overline{\text{EN}}$  is equal to V<sub>BB</sub>.

#### Supply

For interfacing to differential HSTL and LVPECL signals, the V<sub>CC</sub> range is from +2.375V to +3.8V (with V<sub>EE</sub> grounded), allowing high-performance clock or data distribution in systems with a nominal +2.5V or +3.3V supply. For interfacing to differential LVECL, the V<sub>EE</sub> range is -2.375V to -3.8V (with V<sub>CC</sub> grounded). Output levels are referenced to V<sub>CC</sub> and are considered LVPECL or LVECL, depending on the level of the V<sub>CC</sub> supply. With V<sub>CC</sub> connected to a positive supply and

$V_{EE}$  connected to ground, the outputs are LVPECL. The outputs are LVECL when  $V_{CC}$  is connected to ground and  $V_{EE}$  is connected to a negative supply.

#### **Input Bias Resistors**

When the inputs are open, the internal bias resistors set the inputs to low state. The inverting inputs (CLK0 and CLK1) are each biased with a 75k $\Omega$  pullup to V<sub>CC</sub> and a 75k $\Omega$  pulldown to V<sub>EE</sub>. The noninverting inputs (CLK0 and CLK1) are each biased with a 75k $\Omega$  pulldown to V<sub>EE</sub>.

#### **Differential Clock Input Limits**

The maximum magnitude of the differential signal applied to the clock input is 3.0V or  $V_{CC}$  -  $V_{EE}$ , whichever is less. This limit also applies to the difference between any reference voltage input and a single-ended input. Specifications for the high and low voltages of a differential input ( $V_{IHD}$  and  $V_{ILD}$ ) and the differential input voltage ( $V_{IHD}$  -  $V_{ILD}$ ) apply simultaneously.

#### Single-Ended Clock Input and VBB

The differential clock inputs can be configured to accept single-ended inputs. This is accomplished by connecting the on-chip reference voltage, V<sub>BB</sub>, to the inverting or noninverting input of a differential input as a reference. For example, the differential CLK0, CLK0 input is converted to a noninverting, single-ended input by connecting V<sub>BB</sub> to CLKO and connecting the singleended input signal to CLK0. Similarly, an inverting configuration is obtained by connecting  $V_{BB}$  to CLK0 and connecting the single-ended input to CLKO. With a differential input configured as single ended (using  $V_{BB}$ ), the single-ended input can be driven to V<sub>CC</sub> and V<sub>FF</sub> or with a single-ended LVPECL/LVECL signal. Note that single-ended input must be at least VBB ±100mV or a differential input of at least 100mV to switch the outputs to the VOH and VOL levels specified in the DC Electrical Characteristics table.

If V<sub>BB</sub> is used, the supply must be in the V<sub>CC</sub> - V<sub>EE</sub> = +2.725V to +3.8V range because one of the inputs must be V<sub>EE</sub> + 1.2V or higher for proper input stage operation. V<sub>BB</sub> must be at least V<sub>EE</sub> + 1.2V because it becomes the high-level input when the other (single-ended) input swings below it. Therefore, minimum V<sub>BB</sub> = V<sub>EE</sub> + 1.2V. The minimum V<sub>BB</sub> output of the MAX9315 is V<sub>CC</sub> - 1.525V. Substituting the minimum V<sub>BB</sub> output into V<sub>BB</sub> = V<sub>EE</sub> + 1.2V results in a minimum supply of +2.725V. Rounding up to standard supplies gives the single-ended operating supply range of V<sub>CC</sub> - V<sub>EE</sub> = +3.0V to +3.8V.

When using the V<sub>BB</sub> reference output, bypass it with a  $0.01\mu$ F ceramic capacitor to V<sub>CC</sub>. If the V<sub>BB</sub> reference is not used, leave it open. The V<sub>BB</sub> reference can source or sink 0.5mA, which is sufficient to drive two inputs. Use V<sub>BB</sub> only for inputs that are on the same device as the V<sub>BB</sub> reference.

### Applications Information

#### Supply Bypassing

Bypass V<sub>CC</sub> to V<sub>EE</sub> with high-frequency surface-mount ceramic 0.1µF and 0.01µF capacitors in parallel as close to the device as possible, with the 0.01µF capacitor closest to the device. Use multiple parallel vias to minimize parasitic inductance. When using the V<sub>BB</sub> reference output, bypass it with a 0.01µF ceramic capacitor to V<sub>CC</sub> (if the V<sub>BB</sub> reference is not used, it can be left open).

#### **Controlled-Impedance Traces**

Input and output trace characteristics affect the performance of the MAX9315. Connect high-frequency input and output signals with 50 $\Omega$  characteristic impedance traces. Minimize the number of vias to prevent impedance discontinuities. Reduce reflections by maintaining the 50 $\Omega$  characteristic impedance through cables and connectors. Reduce skew within a differential pair by matching the electrical length of the traces.

#### **Output Termination**

Terminate outputs with  $50\Omega$  to  $V_{CC}$  - 2V or use an equivalent Thevenin termination. When a single-ended signal is taken from a differential output, terminate both outputs. For example, if Q0 is used as a single-ended output, terminate both Q0 and  $\overline{Q0}$ .

### Chip Information

TRANSISTOR COUNT: 616 PROCESS: Bipolar

###

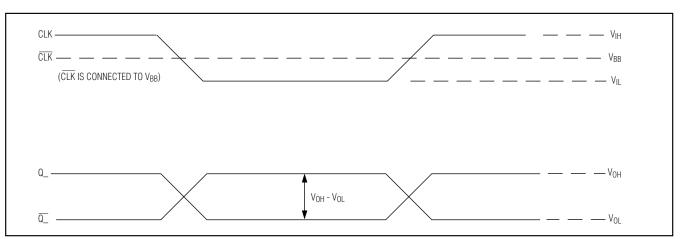

Figure 1. MAX9315 Switching Characteristics with Single-Ended Input

Figure 2. MAX9315 Timing Diagram

Figure 3. MAX9315 EN Timing Diagram

Functional Diagram

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/packages</u>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_

© 2004 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.

\_ 11

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: MAX9315EUP+ MAX9315EUP+T