# L6374

### Industrial quad line driver

#### Features

- Four independent line drivers with 100 mA up to 35 V outputs

- Input signals between 7 V and + 35 V, with pre-setting threshold

- Push-pull outputs with three state control and true zero current between Vs and ground

- Current limiting on each output effective in the full "ground to Vs" output voltage range

- Output voltage clamp to Vs and to ground

- Overtemperature and undervoltage protections

- Diagnostic for overtemperature, undervoltage and overcurrent

- Pre-setting delay for overcurrent diagnostic

- High speed operation: up to 300 kHz with 35 V swing

#### Description

The L6374 is especially designed to be used as a line driver in industrial control systems based on the 24 V signal levels (IEC 61131, 24VDC).

#### Table 1. Device summary

| Order codes | Package | Packaging     |

|-------------|---------|---------------|

| L6374FP     | SO-20   | Tube          |

| L6374FPT    | SO-20   | Tape and reel |

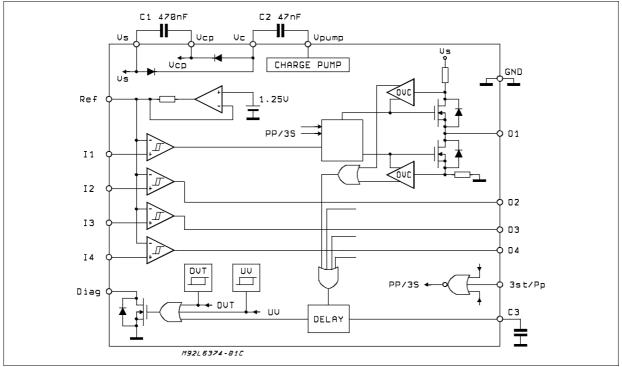

#### Figure 1. Block diagram

## Contents

| 1  | Maximum ratings                      | 3 |  |  |  |  |

|----|--------------------------------------|---|--|--|--|--|

| 2  | Pin connections                      | 3 |  |  |  |  |

| 3  | Electrical characteristics4          | 4 |  |  |  |  |

| 4  | Thermal characteristics6             | 6 |  |  |  |  |

|    | 4.1 RthJP                            | 6 |  |  |  |  |

|    | 4.2 RthJA1 6                         | 6 |  |  |  |  |

|    | 4.3 RthJA2 6                         | 6 |  |  |  |  |

| 5  | Overtemperature protection (OVT)     | B |  |  |  |  |

| 6  | Undervoltage protection (UV)         | 8 |  |  |  |  |

| 7  | Diagnostic logic                     | 9 |  |  |  |  |

| 8  | Programmable delay                   | 9 |  |  |  |  |

| 9  | Analog inputs (I1,I2,I3,I4)          | 9 |  |  |  |  |

| 10 | State / push-pull input              | 0 |  |  |  |  |

| 11 | The switching of the output stage 11 | 1 |  |  |  |  |

| 12 | Application note                     | 5 |  |  |  |  |

| 13 | Package mechanical data 16           |   |  |  |  |  |

| 14 | Revision history                     | B |  |  |  |  |

#### L6374

# 1 Maximum ratings

| Table 2.          | Absolute maximum ratings |                                                                                  |                             |      |

|-------------------|--------------------------|----------------------------------------------------------------------------------|-----------------------------|------|

| Symbol            | Pin                      | Parameter                                                                        | Value                       | Unit |

| M                 | 4                        | Supply voltage ( $t_W \le 10 \text{ ms}$ )                                       | 50                          | V    |

| V <sub>S</sub>    | 1                        | Supply voltage (DC)                                                              | 40                          | V    |

| V <sub>ilog</sub> | 12,                      | Logic input voltage (DC)                                                         | -0.3 to 7                   | V    |

| I <sub>ilog</sub> | 13                       | Logic input forced current, per pin                                              | ±1                          | mA   |

| li                | 7, 8,                    | Channel input current (forced)                                                   | ±2                          | mA   |

| Vi                | 9, 10                    | Channel input voltage                                                            | - 7 to 35                   | V    |

|                   |                          | Output current (forced, apart from inductive load)                               | ±100                        | mA   |

| I <sub>out</sub>  | 3, 4,<br>17,             | Output current (forced, apart from inductive load) same $t_W \leq 10 \mbox{ ms}$ | ±1                          | А    |

| V <sub>out</sub>  | 18                       | Output Voltage (forced, not resulting from an inductive kick)                    | -0.3 to V <sub>S</sub> +0.3 | V    |

| I <sub>set</sub>  | 11                       | Setting pin forced current                                                       | ±1                          | mA   |

| V <sub>set</sub>  |                          | Setting pin forced voltage                                                       | -0.3 to 5                   | V    |

| V <sub>diag</sub> | 14                       | External voltage                                                                 | -0.3 to 35                  | V    |

| I <sub>diag</sub> | 14                       | Externally forced current                                                        | -10 to 10                   | mA   |

| $V_{C3}$          | 13                       | Voltage on the delay capacitor, externally forced                                | -0.3 to 4.5                 | V    |

| Т <sub>ор</sub>   |                          | Ambient temperature, operating range                                             | -25 to 85                   | °C   |

| Τ <sub>J</sub>    |                          | Junction temperature, operating range (see overtemperature protection)           | -25 to 125                  | °C   |

| T <sub>stg</sub>  |                          | Storage temperature                                                              | -55 to 150                  | °C   |

#### Table 2. Absolute maximum ratings

# 2 Pin connections

| Figure 2. | Pins connection | (top view) |

|-----------|-----------------|------------|

|-----------|-----------------|------------|

| -     |       | _        |

|-------|-------|----------|

| Vs 🗆  | 1 20  |          |

| νερ 🗖 | 2 19  | D Vpump  |

| 02 🗆  | 3 18  | 03       |

| 01 🗆  | 4 17  | 04       |

| GND 🗆 | 5 16  | GND      |

| GND 🗆 | 6 15  | GND      |

| I1 🗆  | 7 14  | 🗆 Diag   |

| 12 🗆  | 8 13  | 🗆 СЗ     |

| 13 🗖  | 9 12  | ] 3st/Pp |

| I4 🗆  | 10 11 | 🗆 Ref    |

| 1     |       |          |

# 3 Electrical characteristics

| Symbol            | Pin                  | Parameter                                                 | Test condition                                                                                 | Min                           | Тур  | Max                      | Unit |

|-------------------|----------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------|------|--------------------------|------|

| DC opera          | tion (V <sub>s</sub> | <sub>;</sub> = 24 V; T <sub>J</sub> = -25 to 125 °C; unle | ss otherwise specified)                                                                        |                               |      |                          |      |

| Vs                |                      | Supply voltage                                            |                                                                                                | 10.8                          |      | 35                       | V    |

| V <sub>sh</sub>   |                      | UV upperthreshold                                         |                                                                                                | 9                             |      | 10.8                     | V    |

| H <sub>ys1</sub>  | 1                    | UV hysteresis                                             |                                                                                                | 250                           | 450  | 650                      | mV   |

| I <sub>qsc</sub>  |                      | Quiescent current                                         | Outputs open                                                                                   |                               | 3    | 5                        | mA   |

| V <sub>ref</sub>  |                      | Input comparators reference voltage                       | Reference pin floating                                                                         | 1.05                          | 1.25 | 1.35                     | V    |

|                   | 11                   | Sink/source current on                                    | V <sub>ref</sub> = 0 V                                                                         | -30                           | -20  | -10                      | μA   |

| I <sub>ref</sub>  |                      | reference pin                                             | V <sub>ref</sub> = 5 V                                                                         | 10                            | 20   | 30                       | μA   |

| V                 |                      | Comparator threshold with                                 | V <sub>S</sub> = 9 to 12 V                                                                     | -0.2                          |      | 2.0                      | V    |

| V <sub>th</sub>   |                      | external bias                                             | V <sub>S</sub> = 12 to 35 V                                                                    | -0.2                          |      | 5.0                      | V    |

| V <sub>il</sub>   |                      | Input low level                                           | V <sub>REF</sub> externally biased                                                             | -7                            |      | V <sub>REF</sub><br>-0.2 | V    |

|                   |                      |                                                           | Pin V <sub>REF</sub> floating                                                                  | -7                            |      | 0.8                      | V    |

| V <sub>ih</sub>   | 7, 8,<br>9, 10       | Input high level                                          | V <sub>REF</sub> externally biased                                                             | V <sub>REF</sub><br>+0.2      |      | 35                       | V    |

|                   |                      |                                                           |                                                                                                | Pin V <sub>REF</sub> floating | 2    |                          | 35   |

| Vi                |                      | Input voltage (operative range)                           |                                                                                                | -7                            |      | 35                       | V    |

| 1                 |                      | Input bice current                                        | $0 < V_i < V_S$                                                                                | -1                            |      | 1                        | μA   |

| Ibias             |                      | Input bias current                                        | V <sub>i</sub> = -7 V                                                                          | -1                            | -0.5 | -0.1                     | mA   |

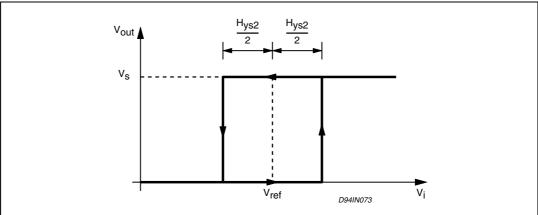

| Hys <sub>2</sub>  |                      | Input comparators hysteresis                              | See analog inputs sections                                                                     | 100                           | 200  | 350                      | mV   |

| T <sub>h</sub>    |                      | OVT upper threshold                                       |                                                                                                |                               | 170  |                          | °C   |

| Η <sub>T</sub>    |                      | OVT hysteresis                                            |                                                                                                |                               | 20   |                          | °C   |

| I <sub>sc</sub>   |                      | Current limit                                             | $V_i = -7$ to $V_S$ ; $V_{out} = 0$ to $V_S$ ;                                                 | 110                           | 200  | 300                      | mA   |

| V <sub>on</sub>   | 3, 4,<br>17,<br>18   | Internal voltage drop @ rated current                     | $I_{out} = \pm 100$ mA; sourced @ high<br>output, sunk @<br>low output T <sub>J</sub> = 125 °C |                               | 400  | 600                      | mV   |

|                   |                      |                                                           | Same, T <sub>J</sub> = 25 °C                                                                   |                               | 250  | 400                      | mV   |

| I <sub>lkg</sub>  |                      | Output 3-state leakage current                            | $V_{out} = 0$ to $V_{S}$                                                                       | -25                           |      | 25                       | μA   |

| V                 |                      | Push-pull mode request                                    |                                                                                                | -0.2                          |      | 0.8                      | V    |

| V <sub>in</sub>   | 12                   | 3-state mode request                                      |                                                                                                | 2                             |      | 5.5                      | V    |

| l <sub>in</sub>   |                      | Input current                                             | V <sub>i</sub> = 0 V                                                                           | Ī                             | 10   | 25                       | μA   |

| I <sub>dlkg</sub> | 14                   | Diagnostic output leakage                                 | Diagnostic OFF; V <sub>diag</sub> = 24 V                                                       |                               |      | 5                        | μA   |

| V <sub>diag</sub> |                      | Diagnostic output voltage drop                            | I <sub>diag</sub> = 5 mA                                                                       |                               | 200  | 500                      | mV   |

Table 3.

Electrical characteristics

| Symbol          | Pin                                                                                                                                                  | Parameter                        | Test condition                   | Min | Тур  | Max  | Unit |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|-----|------|------|------|--|

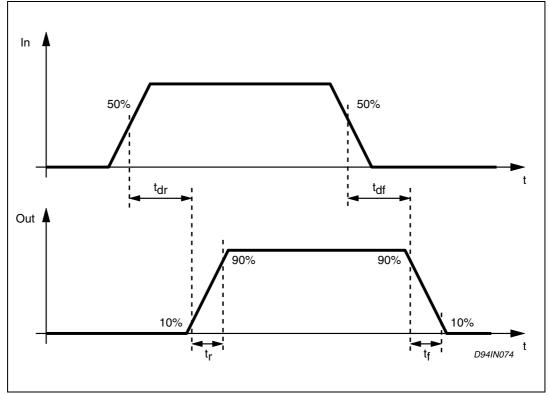

| -               | <b>AC operation</b> ( $V_S = 10.8$ to 35 V; $T_J = -25$ to 125 °C; $I_{out} = 100$ mA; unless otherwise specified; see switching waveforms diagrams) |                                  |                                  |     |      |      |      |  |

| +               | 7 to 4                                                                                                                                               | Delou time on riging edge        | R <sub>I</sub> to ground         |     | 1000 | 1500 | ns   |  |

| t <sub>dr</sub> | 8 to 3<br>9                                                                                                                                          | Delay time on rising edge        | R <sub>I</sub> to V <sub>S</sub> |     | 500  | 1000 | ns   |  |

|                 | to181                                                                                                                                                |                                  | R <sub>I</sub> to ground         |     | 500  | 1000 | ns   |  |

| t <sub>df</sub> | 0 to<br>17                                                                                                                                           |                                  | R <sub>I</sub> to V <sub>S</sub> |     | 1000 | 1500 | ns   |  |

| +               |                                                                                                                                                      | Rise time                        | R <sub>I</sub> to ground         |     | 120  | 250  | ns   |  |

| t <sub>r</sub>  | 3, 4,                                                                                                                                                |                                  | R <sub>I</sub> to V <sub>S</sub> |     | 120  | 250  | ns   |  |

| +               | 17,18                                                                                                                                                | Fall time                        | R <sub>I</sub> to ground         |     | 150  | 300  | ns   |  |

| t <sub>f</sub>  |                                                                                                                                                      | R <sub>I</sub> to V <sub>S</sub> |                                  | 150 | 300  | ns   |      |  |

Table 3.

Electrical characteristics (continued)

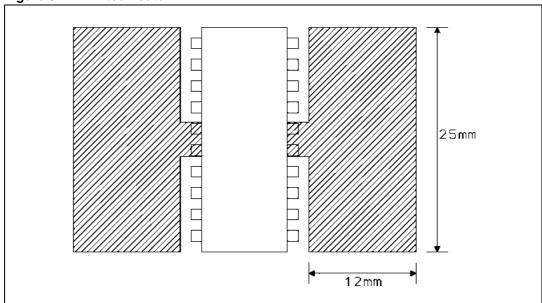

## 4 Thermal characteristics

| Table 4. | Thermal data |

|----------|--------------|

|          | invinui autu |

| Symbol             | Parameter                                                             | Value | Unit |

|--------------------|-----------------------------------------------------------------------|-------|------|

| R <sub>thJP</sub>  | Thermal resistance, junction to pin                                   | 17    | °C/W |

| R <sub>thJA1</sub> | Thermal resistance, junction to ambient (see thermal characteristics) | 65    | °C/W |

| R <sub>thJA2</sub> | Thermal resistance, junction to ambient (see thermal characteristics) | 80    | °C/W |

#### 4.1 R<sub>thJP</sub>

The reference point is the knee on the four central pins, where the pins are upwardly bent and the soldering joint with the PCB footprint can be made.

### 4.2 R<sub>thJA1</sub>

If a dissipating surface, thick at least 35  $\mu$ m, and with a surface similar or bigger than the one shown, is created making use of the printed circuit. Such heatsinking surface is considered on the bottom side of an horizontal PCB (worst case).

### 4.3 R<sub>thJA2</sub>

If the power dissipating pins (the four central ones), as well as the others, have a minimum thermal connection with the external world (very thin strips only) so that the dissipation takes place through still air and through the PCB itself.

It is the same situation of point above, without any heatsinking surface created on purpose on the board.

### 5 **Overtemperature protection (OVT)**

If the chip temperature exceeds  ${\rm T}_{\rm h}$  (measured in a central position in the chip) the chip deactivates itself.

The following actions are taken:

- all the output stages are forced in the "three state" condition, i.e. are disconnected from the output pins; only the clamping diodes at the outputs remain active;

- the signal Diag is activated (active low).

Normal operation is resumed as soon as (typically after some seconds) the chip temperature monitored goes back below  $T_h$  - $H_T$ .

The different upper and lower thresholds with hysteretic behavior, assure that no intermittent conditions can be generated.

### 6 Undervoltage protection (UV)

The supply voltage is expected to range from 11 V to 35 V, even if its reference value is considered to be 24 V.

In this range the L6374 operates correctly. Below 10.8 V the overall system has to be considered not reliable.

Consequently the supply voltage is monitored continuously and a signal, called UV, is internally generated and used.

The signal is "on" as long as the supply voltage does not reach the upper internal threshold of the V<sub>s</sub> comparator (called V<sub>sh</sub>). The UV signal disappears above V<sub>sh</sub>.

Once the UV signal has been removed, the supply voltage must decrease below the lower threshold (i.e. below  $V_{sh}$  -H<sub>vs1</sub>) before it is turned on again.

The hysteresis  $H_{ys1}$  is provided to prevent intermittent operation of the device at low supply voltages that may have a superimposed ripple around the average value.

The UV signal inhibits the outputs, putting them in three-state, but has no effect on the creation of the reference voltages for the internal comparators, nor on the continuous operation of the charge-pump circuits.

#### 7 Diagnostic logic

The situations that are monitored and signalled with the Diag output pin are:

- current limit (OVC) in action; there are 8 individual current limiting circuits, two per each

output, i.e. one per every output transistor; they limit the current that can be either sourced or sunk from each output, to a typical value of 150 mA, equal for all of them;

- undervoltage protection (UV);

- overtemperature protection (OVP); The diagnostic signal is transmitted via an open drain output (for ease of wired-or connection of several such signals) and a low level represents the presence of at least one of the monitored conditions, mentioned above.

#### 8 Programmable delay

The current limiting circuits can be requested to perform even in absence of a real fault condition, for a short period, if the load is of capacitive nature or if it is a filament lamp (that exhibits a very low resistance during the initial heating phase). To avoid the forwarding of misleading, short diagnostic pulses in coincidence with the intervention of the current limiting circuits when operating on capacitive loads, a delay of about 5  $\mu$ s is inserted on the signal path, between the "OR" of the current limit signals and its use as external diagnostic. It takes about 1 $\mu$ s to charge (or discharge) by 24 V a capacitor of 5 nF with a current of 120 mA . To implement longer delays (from the intervention of one of the current limiting circuits to the activation of the diagnostic) an external capacitor can be connected between pin C3 and ground (pin C3 is otherwise left open).

The delay shall then be determined by the ratio of about 10 pF/ $\mu$ s, using the value of the capacitance connected to the pin.

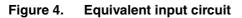

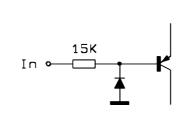

### 9 Analog inputs (11,12,13,14)

The input stage of each channel is a high im-pedence comparator with built-in hysteresis (200 mV) for high noise immunity. Each comparator has one input connected to all the others and tied to a common pin Ref (Pin 11). If this pin is left floating an internal precise band gap voltage reference (1.25 V) is applied, otherwise these inputs can be externally programmed by connecting an external voltage source (from 0 to 5 V) and the current on this pin is internally limited to  $\pm 20$  mA. The other input pin of each comparator can swing from -7 to 35 V.

For this reason it has been implemented the structure shown in *Figure 4 on page 10* and the device can also be used as line receiver.

When the input voltage is negative, the current is internally limited by a 15 k $\Omega$  resistor as shown in *Figure 4 on page 10*. High and low input thresholds can be obtained by adding and subtracting half of the hysteresis to the voltage of pin Ref (see *Figure 5 on page 10*).

## 10 State / push-pull input

The input 3st/Pp is instead intended for a digital incoming signal. It has an internal threshold set at 1.26 V; an internal bias circuit (10 mA typical) simulates a high level (three-state) if the pin is disconnected.

#### Figure 5. Input comparator threshold

### 11 The switching of the output stage

The cross conduction of the two transistors of an output stage of the L6374 would be significantly noisy, because the transistors here can carry peak currents in excess of 100 mA, and even more in the few nanoseconds before the current limiting circuits are really effective.

Consequently the device has been designed so as to avoid such cross conduction. At every switching transition, first of all the transistor in conduction is turned OFF. Then, after a safe interval of around 200 ns, the other transistor is turned on.

When analyzing the switching cycle, and the associated switching times, it is useful to identify some subsequent phases:

- delay from the input pin to the output reaction;

- OFF transition in the output stage;

- dead time

- on transition in the output stage.

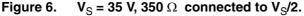

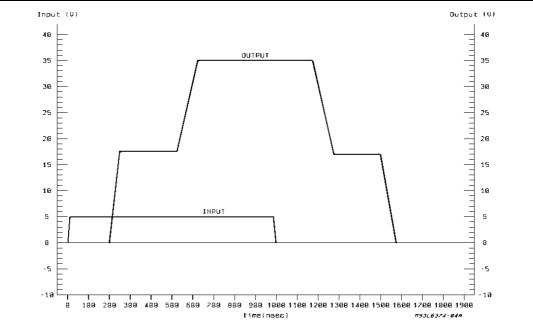

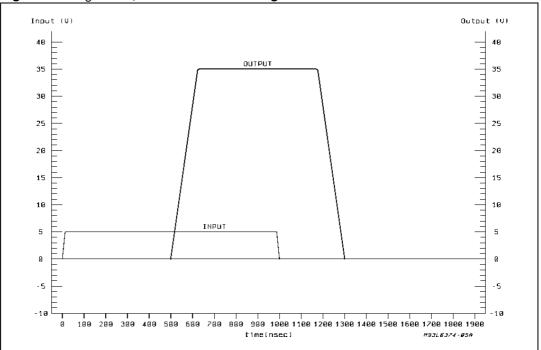

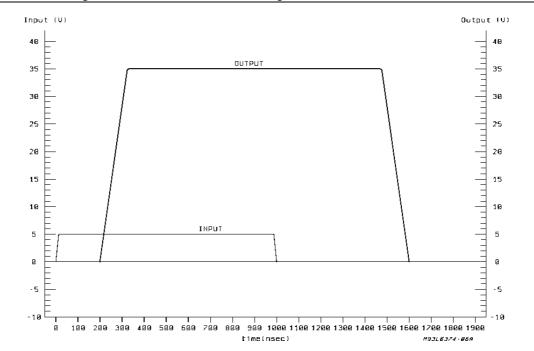

*Figure 6* helps understand such sequence. In fact, with a purely resistive load connected to  $V_s/2$  no parasitic elements interfere significantly. The waveform can be significantly less easy to in terpret if the load has not the perfect symmetry of that case, as showed below. For instance, it is enough to connect the resistive load to ground, or to  $V_s$  – as *Figure 7* and *Figure 8* – show to hide some of the switching phases described.

If the load is connected to ground, the waveform stays stuck to ground as long as the output stage is in high impedance; viceversa when the load is connected to Vs the waveform will linger close to the supply voltage as long as possible.

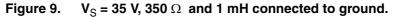

If an output load made of an inductor and a resistor in series is used, the inductive kick at the beginning of every output transition generates the equivalent effect of an "anticipated"

switching when the inductor can discharge; while the switching looks "delayed" if the output transition tends to initiate a charging phase (see *Figure 9*). With a load almost free from parasitic elements, the waveforms resemble the ones of the purely resistive cases.

With a real, more composite load, the effect of the inductive kick in comparison to the resistive load, would be more apparent.

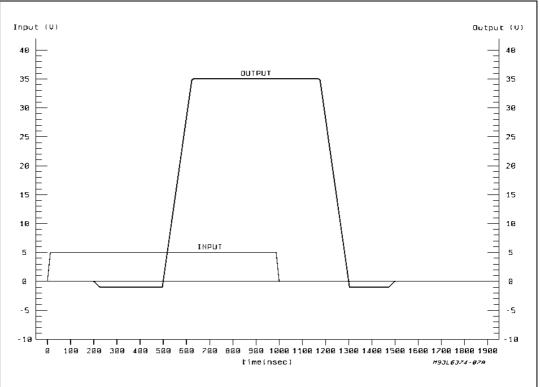

With a capacitor and a resistor in parallel as a load, another type of waveform can be seen (reported in *Figure 10*).

As long as the output stage stays in the transient high impedance state, the output voltage will follow the classic exponential law of an RC relaxation.

As soon as the other transistor is switched on and takes charge, the waveform is quickly forcibly brought to its steady state value.

From the above it is possible to see how the switching times, inherently very fast, of the output stages, may be difficult to identify in a waveform if the output load is not accurately taken into consideration.

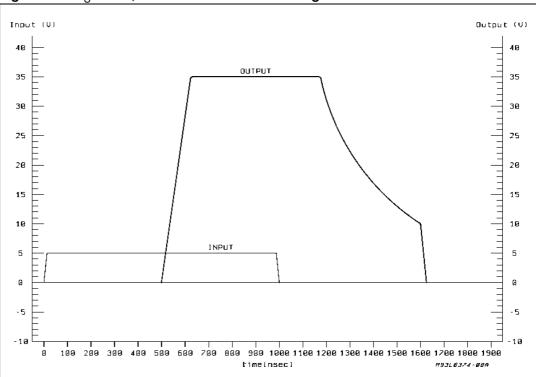

*Figure 11* show typical switching waveform for inputs and outputs.

Figure 7.  $V_S = 35 V, 350 \Omega$  connected to ground

Figure 8.  $V_{\rm S}$  = 35 V, 350  $\Omega$  connected to  $V_{\rm S}$

Figure 10. V<sub>S</sub> = 35 V, 350  $\Omega$  || 1 nF connected to ground.

57

## 12 Application note

It is recommended not to leave the Ref pin (pin 11) floating: if not used with an external voltage reference, it is better to connect an external capacitor (of at least 10 nF) between this pin and ground.

This capacitor filters the voltage reference against voltage spikes that can be generated by the commutation of the output stages.

This is very common using capacitive loads: in fact, the initial transient of such loads behaves like a short circuit, so the current flowing through the outputs presents very high spikes.

Moreover, if the device is used as a line receiver. (i.e. the input signals can go below ground) it is required not to leave the Ref pin (pin 11) floating: in this case, the pin can be connected to ground or to a fixed external voltage reference.

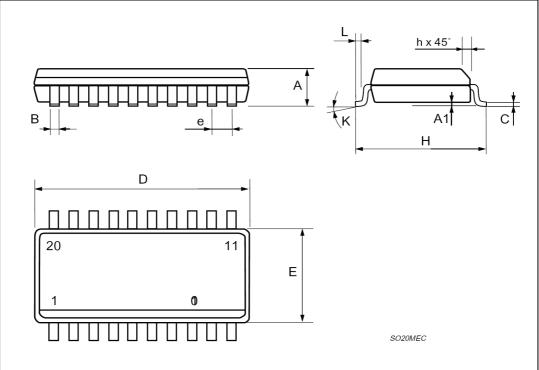

## 13 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com

| Table 5. | SO-20 mechanical data |      |           |           |       |       |  |

|----------|-----------------------|------|-----------|-----------|-------|-------|--|

| Dim      |                       | mm   |           |           | inch  | ch    |  |

| Dim.     | Min                   | Тур  | Max       | Min       | Тур   | Max   |  |

| А        | 2.35                  |      | 2.65      | 0.093     |       | 0.104 |  |

| A1       | 0.1                   |      | 0.3       | 0.004     |       | 0.012 |  |

| В        | 0.33                  |      | 0.51      | 0.013     |       | 0.020 |  |

| С        | 0.23                  |      | 0.32      | 0.009     |       | 0.013 |  |

| D        | 12.6                  |      | 13        | 0.496     |       | 0.512 |  |

| E        | 7.4                   |      | 7.6       | 0.291     |       | 0.299 |  |

| е        |                       | 1.27 |           |           | 0.050 |       |  |

| Н        | 10                    |      | 10.65     | 0.394     |       | 0.419 |  |

| h        | 0.25                  |      | 0.75      | 0.010     |       | 0.030 |  |

| L        | 0.4                   |      | 1.27      | 0.016     |       | 0.050 |  |

| К        |                       |      | 0° (min.) | 8° (max.) |       |       |  |

Table 5.SO-20 mechanical data

# 14 Revision history

| Table 6. | Document revision | on history |

|----------|-------------------|------------|

|----------|-------------------|------------|

| Date        | Revision | Changes                                     |

|-------------|----------|---------------------------------------------|

| August 2003 | 1        | First Issue                                 |

| June 2004   | 2        | Technical migration from ST-PRESS to EDOCS. |

| 03-Mar-2008 | 3        | Modified: Removed obsolete package DIP-20   |

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: <u>L6374FP</u> <u>L6374FP013TR</u> <u>L6374DP</u>