**DAC161S997**

SNAS621A - JUNE 2013-REVISED DECEMBER 2014

# DAC161S997 16-Bit SPI-Programmable DAC for 4-20 mA Loops

#### **Features**

- 16-Bit Resolution

- Very-Low Supply Current of 100 µA

- 5 ppmFS/°C Gain Error

- Pin-Programmable Power-Up Condition

- Loop-Error Detection and Reporting

- Programmable Output-Current Error Levels

- Simple HART Modulator Interfacing

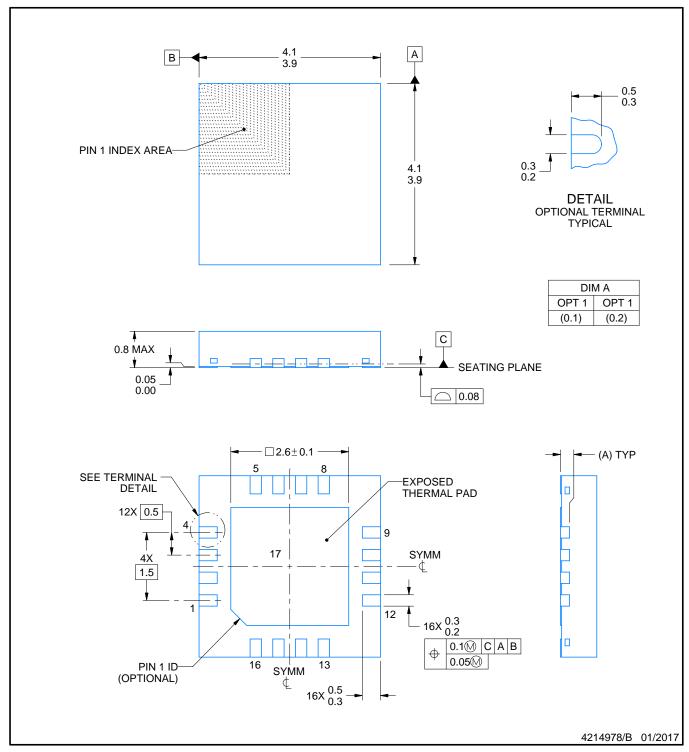

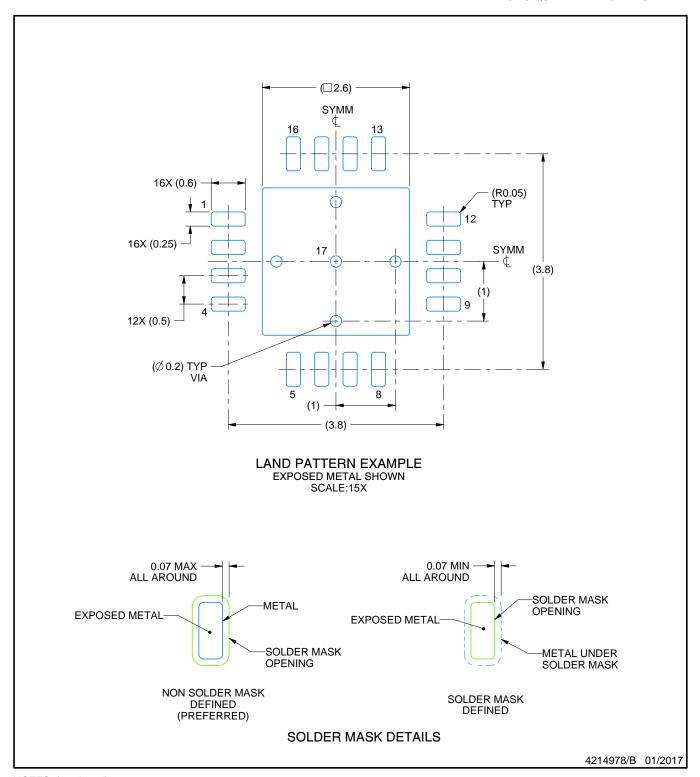

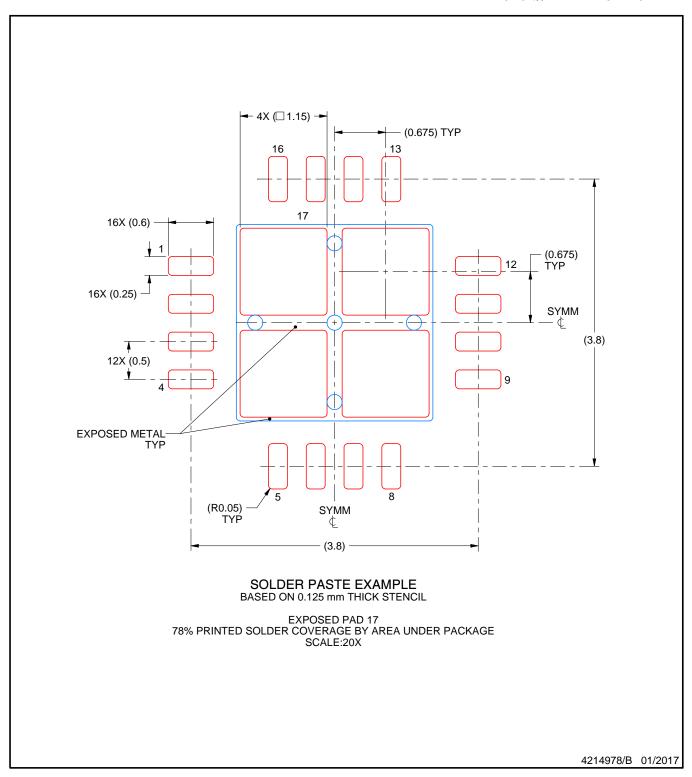

- Highly Integrated Feature Set in Small Footprint WQFN-16 (4- x 4-mm, 0.5-mm Pitch)

# 2 Applications

- Two-Wire 4- to 20-mA Current-Loop Transmitter

- **Loop-Power Transmitters**

- **Industrial Process Control**

- **Actuator Control**

# 3 Description

The DAC161S997 is a very low power 16-bit  $\Sigma\Delta$ digital-to-analog converter (DAC) for transmitting an analog output current over an industry standard 4-20 mA current loop. The DAC161S997 has a simple 4wire SPI for data transfer and configuration of the DAC functions. To reduce power and component count in compact loop-powered applications, the DAC161S997 contains an internal ultra-low power voltage reference and an internal oscillator. The low power consumption of the DAC161S997 results in additional current being available for the remaining portion of the system. The loop drive of the DAC161S997 interfaces to a Highway Addressable Remote Transducer (HART) modulator, allowing injection of FSK modulated digital data into the 4-20 mA current loop. This combination of specifications and features makes the DAC161S997 ideal for 2- and 4-wire industrial transmitters. The DAC161S997 is available in a 16-pin 4-mm × 4-mm WQFN package and is specified over the extended industrial temperature range of -40°C to +105°C.

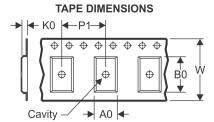

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| DAC161S997  | WQFN (16) | 4.00 mm x 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

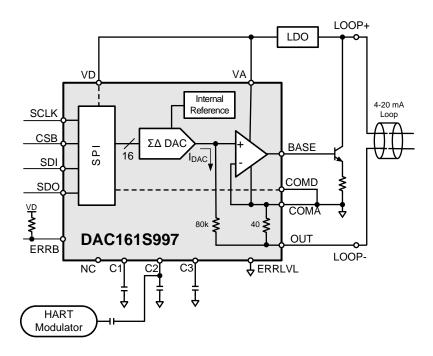

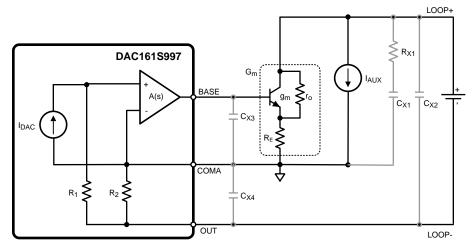

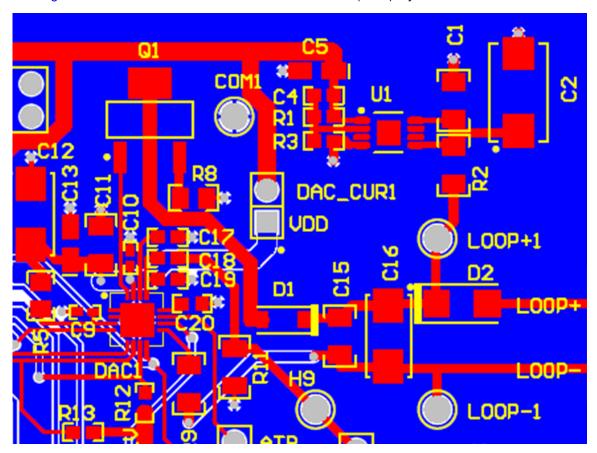

# 4 Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                               |    | 8.3 Feature Description              |                |

|---|----------------------------------------------------------|----|--------------------------------------|----------------|

| 2 | Applications 1                                           |    | 8.4 Device Functional Modes          |                |

| 3 | Description 1                                            |    | 8.5 Programming                      | 10             |

| 4 | Simplified Schematic 1                                   |    | 8.6 Register Maps                    | 1              |

| 5 | Revision History                                         | 9  | Application and Implementation       | 1              |

| 6 | Pin Configuration and Functions                          |    | 9.1 Application Information          |                |

| - | _                                                        |    | 9.2 Typical Application              | 2              |

| 7 | Specifications 4                                         | 10 | Power Supply Recommendations         | 29             |

|   | 7.1 Absolute Maximum Ratings                             | 11 | Layout                               |                |

|   | 7.2 ESD Ratings 4 7.3 Recommended Operating Conditions 4 |    | 11.1 Layout Guidelines               |                |

|   | 7.3 Recommended Operating Conditions                     |    | 11.2 Layout Example                  |                |

|   | 7.5 Electrical Characteristics 5                         | 12 | Device and Documentation Support     |                |

|   | 7.6 Timing Requirements                                  |    | 12.1 Trademarks                      |                |

|   | 7.7 Typical Characteristics                              |    | 12.2 Electrostatic Discharge Caution | 3 <sup>1</sup> |

| 8 | Detailed Description 8                                   |    | 12.3 Glossary                        | 3 <sup>1</sup> |

| 0 | 8.1 Overview                                             | 13 | Mechanical, Packaging, and Orderable |                |

|   | 8.2 Functional Block Diagram 8                           |    | Information                          | 3 <sup>.</sup> |

|   | 0.2 I ullottolial block blagfail 0                       |    |                                      |                |

# 5 Revision History

# Changes from Original (June 2013) to Revision A

Page

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

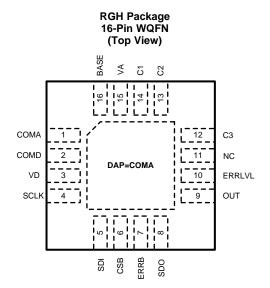

# 6 Pin Configuration and Functions

**Pin Functions**

| Р      | IN  | (1)                 |                                                                   |  |

|--------|-----|---------------------|-------------------------------------------------------------------|--|

| NAME   | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                       |  |

| BASE   | 16  | А                   | External NPN base drive                                           |  |

| COMA   | 1   | Р                   | Analog-block negative supply rail (local COMMON)                  |  |

| COMD   | 2   | Р                   | Digital-block negative supply rail (local COMMON)                 |  |

| CSB    | 6   | I                   | SPI chip select                                                   |  |

| C1     | 14  | Α                   | External capacitor                                                |  |

| C2     | 13  | Α                   | External capacitor, HART input                                    |  |

| C3     | 12  | Α                   | External capacitor                                                |  |

| EERB   | 7   | 0                   | Error flag output, open drain, active LOW                         |  |

| ERRLVL | 10  | I                   | Sets output-current level at power up and under-error conditions. |  |

| NC     | 11  | _                   | Do not connect to this pin.                                       |  |

| OUT    | 9   | Α                   | Loop output current source output                                 |  |

| SCLK   | 4   | I                   | SPI clock input                                                   |  |

| SDI    | 5   | I                   | SPI data input                                                    |  |

| SDO    | 8   | 0                   | SPI data output                                                   |  |

| VA     | 15  | Р                   | Analog-block positive supply rail                                 |  |

| VD     | 3   | Р                   | Digital-block positive supply rail.                               |  |

| DAP    | DAP | Р                   | Die attach pad. Connect directly to local COMMON (COMA, COMD).    |  |

(1) G = Ground, I = Digital Input, O = Digital Output, P = Power, A = Analog

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

|                                                   | MIN  | MAX | UNIT |

|---------------------------------------------------|------|-----|------|

| Supply voltage (VA, VD to COMA, COMD)             | -0.3 | 6   | V    |

| Voltage between any two pins (2)                  |      | 6   | V    |

| Current IN or OUT of any pin — except OUT pin (3) |      | 5   | mA   |

| Output current at OUT                             |      | 50  | mA   |

| Junction Temperature                              |      | 150 | °C   |

| Operating Temperature                             | -40  | 105 | °C   |

| Storage temperature, T <sub>stg</sub>             | -65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are measured with respect to COMA = COMD = 0 V, unless otherwise specified.

(3) When the input voltage (VIN) at any pin exceeds power supplies (VIN < COMA or VIN > VA), the current at that pin must not exceed 5 mA, and the voltage (VIN) at that pin relative to any other pin must not exceed 6 V. See for Pin Descriptions for additional details of input structures.

### 7.2 ESD Ratings

|                    |                         |                                                           | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)(2) | 2000  | ٧    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) The Human Body Model (HBM) is a 100 pF capacitor charged to the specified voltage then discharged through a 1.5 kΩ resistor into each pin.

# 7.3 Recommended Operating Conditions

|                |                   | MIN | MAX  | UNIT |

|----------------|-------------------|-----|------|------|

|                | BASE load to COMA | 0   | 15   | pF   |

|                | (COMA - COMD)     |     | 0    | V    |

|                | OUT load to COMA  |     | none |      |

|                | (VA - VD)         |     | 0    | V    |

| VA, VDD        | Supply voltage    | 2.7 | 3.6  | V    |

| T <sub>A</sub> | Temperature       | -40 | 105  | °C   |

#### 7.4 Thermal Information

|                 |                                          | DAC161S997 |      |

|-----------------|------------------------------------------|------------|------|

|                 |                                          | WQFN       | UNIT |

|                 |                                          | 16 PINS    |      |

| $R_{\theta JA}$ | Package thermal impedance <sup>(1)</sup> | 35         | °C/W |

Product Folder Links: DAC161S997

(1) The package thermal impedance is calculated in accordance with JESD 51-7.

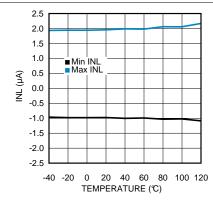

#### 7.5 Electrical Characteristics

Unless otherwise noted, these specifications apply for VA = VD = 3.3 V, COMA = COMD = 0 V,  $T_A$ = 25°C, external bipolar transistor: 2N3904, RE = 22  $\Omega$ , C1 = C2 = C3 = 2.2 nF.

|                     | PARAMETER                                                                      | TEST CONDITIONS                                                 | MIN <sup>(1)</sup> | TYP   | MAX <sup>(1)</sup> | UNIT              |

|---------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-------|--------------------|-------------------|

| POWER S             | SUPPLY                                                                         |                                                                 |                    |       |                    |                   |

| VA, VD              | Supply voltage                                                                 | VA = VD<br>-40°C ≤ T <sub>A</sub> ≤ 105°C                       | 2.7                |       | 3.6                | V                 |

|                     | VA supply current                                                              | DACCODE = 0x0200 <sup>(2)</sup>                                 |                    | 43    |                    | μA                |

|                     | VD supply current                                                              |                                                                 |                    | 57    |                    | μA                |

| ICC                 | Total supply current                                                           |                                                                 |                    | 100   | 125                | μA                |

| DC ACCU             | IRACY                                                                          |                                                                 |                    |       |                    |                   |

| N                   | Resolution                                                                     |                                                                 |                    | 16    |                    | bits              |

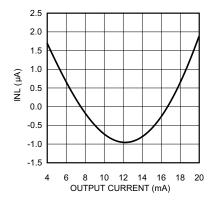

| INL                 | Integral non-linearity <sup>(3)</sup>                                          | 0x2AAA < DACCODE < 0xD555<br>(4 mA < I <sub>LOOP</sub> < 20 mA) | -1.5               |       | 2.6                | μΑ                |

| DNL                 | Differential non-linearity                                                     | see (4)                                                         | -0.2               |       | 0.2                | μA                |

| TUE                 | Total unadjusted error                                                         | 0x2AAA < DACCODE < 0xD555                                       |                    | 0.01  |                    | %FS               |

| OE                  | Offset error                                                                   | see (5)                                                         | -7.86              | 0.84  | 7.86               | μA                |

| ΔΟΕ                 | Offset error temperature coefficient                                           | -40°C ≤ T <sub>A</sub> ≤ 105°C                                  |                    | 0.48  |                    | ppmFS/°C          |

| GE                  | Gain error                                                                     | see <sup>(6)</sup>                                              |                    | 0.007 |                    | %FS               |

| ΔGE                 | Gain error temperature coefficient                                             | -40°C ≤ T <sub>A</sub> ≤ 105°C                                  |                    | 5     |                    | ppmFS/°C          |

| IERRL               | LOW ERROR current                                                              | ERR_LOW = default                                               | 3.36               | 3.375 | 3.39               | mA                |

| IERRH               | HIGH ERROR current                                                             | ERR_HIGH = default                                              | 21.70              | 21.75 | 21.82              | mA                |

| LTD                 | Long term drift — mean shift of 12 mA output current after 1000 hours at 150°C |                                                                 |                    | 90    |                    | ppmFS             |

| LOOP CU             | RRENT OUTPUT (OUT)                                                             |                                                                 |                    |       |                    |                   |

| I <sub>OUTMIN</sub> | Minimum output current                                                         | Tested at DACCODE = 0x01C2 <sup>(7)</sup>                       |                    |       | 0.19               | mA                |

| I <sub>OUTMAX</sub> | Maximum output current                                                         | Tested at DACCODE = 0xFFFF                                      | 23.95              |       |                    | mA                |

| R <sub>OUT</sub>    | Output impedance                                                               |                                                                 |                    | 200   |                    | МΩ                |

|                     | COMA to OUT voltage drop                                                       | I <sub>OUT</sub> = 24 mA                                        |                    | 960   |                    | mV                |

| BASE OU             | TPUT                                                                           |                                                                 |                    |       |                    |                   |

| I <sub>OUTSC</sub>  | BASE short circuit output current                                              | BASE forced to COMA potential                                   |                    | 10    |                    | mA                |

| DYNAMIC             | CHARACTERISTICS                                                                |                                                                 |                    |       |                    |                   |

|                     | Output noise density                                                           | 1 kHz                                                           |                    | 20    |                    | nA/rtHz           |

|                     | Integrated output noise                                                        | 1 Hz to 1 kHz band                                              |                    | 300   |                    | nA <sub>RMS</sub> |

| INTERNA             | L TIMER                                                                        |                                                                 | 1                  |       |                    |                   |

| TM                  | Timeout period                                                                 | Default setting of TIMEOUT in CONFIG register                   |                    | 100   |                    | ms                |

| DIGITAL I           | INPUT CHARACTERISTICS                                                          |                                                                 |                    |       |                    |                   |

| I <sub>IN</sub>     | Digital input leakage current                                                  |                                                                 | -10                |       | 10                 | μΑ                |

| V <sub>IL</sub>     | Input low voltage                                                              |                                                                 |                    |       | 0.2 × VD           | V                 |

| V <sub>IH</sub>     | Input high voltage                                                             |                                                                 | 0.7 × VD           |       |                    | V                 |

| C <sub>IN</sub>     | Input capacitance                                                              |                                                                 |                    | 5     |                    | pF                |

- (1) Limits are ensured by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (2) At code 0x0200 the BASE current is minimal, for example, device current contribution to power consumption is minimized. SPI is inactive, for example, after transmitting code 0x200 to the DAC161S997, there are no more transitions in the channel during the supply current measurement.

- (3) INL is measured using the best-fit method in the output current range of 4 mA to 20 mA.

- (4) Specified by design.

- (5) Offset is the y-intercept of the straight line defined by 4 mA and 20 mA points of the measured transfer characteristic.

- (6) Gain Error is the difference in slope of the straight line defined by measured 4 mA and 20 mA points of transfer characteristic, and that of the ideal characteristic.

- 7) This must be treated as the minimum LOOP current ensured in self-powered mode.

# **Electrical Characteristics (continued)**

Unless otherwise noted, these specifications apply for VA = VD = 3.3 V, COMA = COMD = 0 V,  $T_A$ = 25°C, external bipolar transistor: 2N3904, RE = 22  $\Omega$ , C1 = C2 = C3 = 2.2 nF.

| PARAMETER                           |                               | TEST CONDITIONS            | MIN <sup>(1)</sup> | TYP | MAX <sup>(1)</sup> | UNIT |

|-------------------------------------|-------------------------------|----------------------------|--------------------|-----|--------------------|------|

| DIGITAL O                           | IGITAL OUTPUT CHARACTERISTICS |                            |                    |     |                    |      |

| $V_{OL}$                            | Output Low voltage            | I <sub>sink</sub> = 200 μA |                    |     | 0.4                | V    |

| V <sub>OH</sub>                     | Output HIGH voltage           | I <sub>sink</sub> = 200 μA | 2.6                |     |                    | V    |

| I <sub>OZH</sub> , I <sub>OZL</sub> | TRI-STATE leakage current     |                            | -10                |     | 10                 | μΑ   |

| C <sub>OUT</sub>                    | TRI-STATE output capacitance  |                            |                    | 5   |                    | pF   |

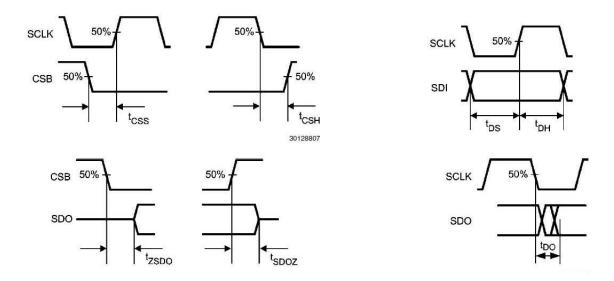

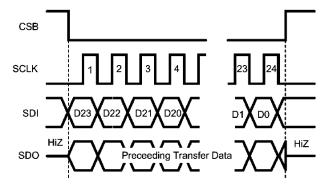

# 7.6 Timing Requirements

|                   |                                                   | MIN                    | NOM | MAX | UNIT |

|-------------------|---------------------------------------------------|------------------------|-----|-----|------|

| f <sub>CLK</sub>  | SCLK frequency                                    | 0                      |     | 10  | MHz  |

| t <sub>H</sub>    | SCLK high time                                    | 0.4 / F <sub>CLK</sub> | 50  |     | ns   |

| tL                | SCLK low time                                     | 0.4 / F <sub>CLK</sub> | 50  |     | ns   |

| t <sub>CSB</sub>  | CSB pulse width                                   | 5                      | 40  |     | ns   |

| t <sub>CSS</sub>  | CSB set-up time prior to SCLK rising edge         | 5                      |     |     | ns   |

| t <sub>SCH</sub>  | 24th rising edge of SCLK to CSB rising edge       | 15                     |     |     | ns   |

| t <sub>CSH</sub>  | CSB hold time after the 24th falling edge of SCLK | 6                      | 10  |     | ns   |

| t <sub>ZSDO</sub> | CSB falling edge to SDO valid                     |                        | 10  | 35  | ns   |

| t <sub>SDOZ</sub> | CSB rising edge to SDO HiZ                        |                        | 10  |     | ns   |

| t <sub>DS</sub>   | SDI data set-up time prior to SCLK rising edge    | 10                     |     |     | ns   |

| t <sub>DH</sub>   | SDI data hold time after SCLK rising edge         | 6                      | 10  |     | ns   |

| t <sub>DO</sub>   | SDO output data valid                             |                        |     | 30  | ns   |

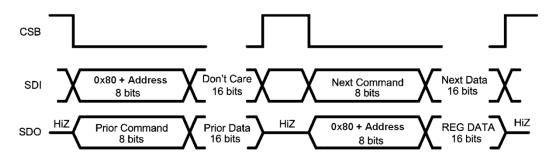

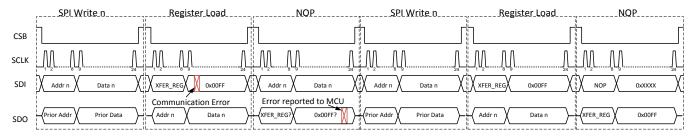

Figure 1. SPI Timing Diagrams

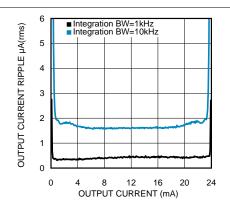

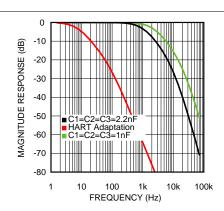

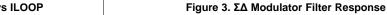

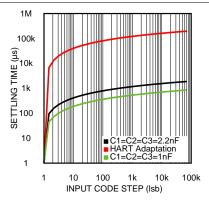

# 7.7 Typical Characteristics

Unless otherwise noted, data presented here was collected under these conditions VA = VD = 3.3 V,  $T_A = 25^{\circ}\text{C}$ , external bipolar transistor: 2N3904,  $RE = 22 \Omega$ , C1 = C2 = C3 = 2.2 nF.

Figure 2. Intergrated Noise vs ILOOP

Figure 4. Settling Time vs Input Step Size

Figure 5. Output Linearity vs Temperature

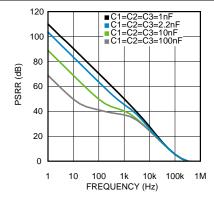

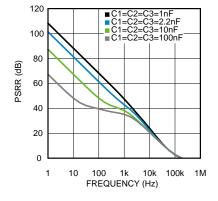

Figure 6. PSRR: I<sub>LOOP</sub> = 4 mA

Figure 7. PSRR: I<sub>LOOP</sub> = 20 mA

# 8 Detailed Description

#### 8.1 Overview

The DAC161S997 is a 16-bit DAC realized as a  $\Sigma\Delta$  modulator. The DAC's output is a current pulse train that is filtered by the on-board low pass RC filter. The final output current is a multiplied copy of the filtered modulator output. This architecture ensures an excellent linearity performance, while minimizing power consumption of the device.

The DAC161S997 eases the design of robust, precise, long-term stable industrial systems by integrating all precision elements on-chip. Only a few external components are needed to realize a low-power, high-precision industrial 4 - 20 mA transmitter.

In case of a fault, or during initial power-up the DAC161S997 will output current in either upper or lower error current band. The choice of band is user selectable via a device pin. The error current value is user programmable via SPI.

### 8.2 Functional Block Diagram

LOOP+ LDO VD VA Internal Reference LOOP SCLK 0-24 mA Loop IN SDI Sensor ΣΔ DAC SP IDAC SDC μC COMD CSE СОМА RECEIVER 80k **≤** 40 € ERRE **DAC161S997** INT OUT LOOP ERRLVL ¥ HART Modulator

Industrial 4-20mA Transmitter

#### 8.3 Feature Description

#### 8.3.1 Error Detection And Reporting

By default, the DAC161S997 detects and reports several types of errors.

#### 8.3.1.1 Loop Error

A loop error occurs when the device is unable to sustain the required output current at OUT pin, typically caused by a drop in loop supply, or an increase in load impedance.

When a loop error occurs, the DAC161S997 changes the OUT-pin current to the value in the ERROR\_LOW register, unless the MASK\_LOOP\_ERR is set to 1. If the MASK\_LOOP\_ERR is not set, then the device also periodically attempts to reassert the OUT current set in DACCODE by default. If the DACCODE-current output is set, the DAC161S997 then stops reporting a loop error. The interval between reasserts is controlled by the L\_RETRY\_TIME field in the ERROR\_CONFIG register. If the DIS\_RETRY\_LOOP field in the ERROR\_CONFIG register is changed to 1, the device does not periodically check the loop and, instead, only checks the loop after a read of the ERR\_STATUS (0x09) register. If the loop error is not resolved, then the loop-error current persists.

Submit Documentation Feedback

Copyright © 2013–2014, Texas Instruments Incorporated

### **Feature Description (continued)**

When a loop error occurs, the DAC161S997 sets the CURR\_LOOP\_STATUS and LOOP\_STATUS fields in the STATUS register to 1. The LOOP\_STATUS field remains set to 1 until the STATUS register is read or the device is reset. If the loop error is cleared, either by the device reasserting the loop current or by changing the OUT current, then the CURR\_LOOP\_STATUS field clears.

#### 8.3.1.2 SPI Timeout Error (Channel Error)

The DAC161S997 expects to receive periodic SPI write commands to ensure that the SPI connection is functioning normally. If no SPI write command occurs within the time indicated by the SPI\_TIMEOUT field in the ERROR\_CONFIG register, the device reports a SPI timeout error. Note that the SPI write command must be properly formatted to avoid SPI Timeout errors (such as a write command that generates a frame error does not prevent an imminent SPI Timeout error).

SPI Timeout error reporting is inhibited by MASK\_SPI\_TOUT. SPI Timeout errors are not reported on the loop if MASK\_SPI\_ERR is set to 1.

Note that a write command to address 0 is not considered a valid write command and will not prevent a SPI Timeout error.

### 8.3.1.3 Frame Error

If a SPI write command has an incorrect number of SCLK pulses, the device reports a frame error. The number of SCLK pulses must be an integer and a multiple of 24. A frame error is always reported by ERRB being pulled low. A frame error does not affect the loop current.

#### 8.3.1.4 Alarm Current

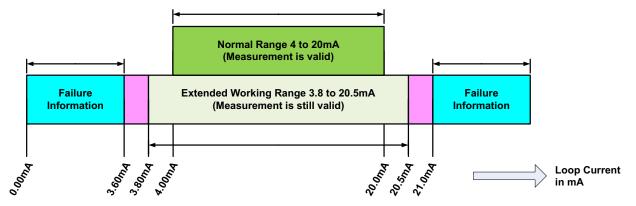

By default, the DAC161S997 reports faults to the plant controller by forcing the OUT current into one of two error bands. The error current bands are defined as either greater than 20 mA, or less than 4 mA. Loop errors are reported by setting current of ERR LOW.

If SPI Timeout Errors are reported on the loop (this is the default; it can be changed by setting the register ERR\_CONFIG:MASK\_LOOP\_ERR), the error band is controlled by the ERRLVL pin. When ERRLVL is tied to the COMD voltage, the ERR\_LOW current is the reporting current. If ERRLVL is tied to VD then the ERR\_HIGH current is the current-on pin, OUT, if a SPI timeout error occurs.

The exact value of the output current used to indicate fault is dictated by the contents of ERR\_HIGH and ERR\_LOW registers.

In the case of a conflicting alarm-current setting (such as a loop error and SPI timeout error occurring simultaneously and ERRLVL is tied high), the current-on pin, OUT, is determined by ERR\_LOW current.

#### 8.4 Device Functional Modes

The DAC161S997 reports errors in 3 different ways, by changing the OUT pin current, pulling the ERRB pin low, and by updating the read-only register STATUS. The reporting on ERRB and OUT pin is customized by setting the ERROR\_CONFIG register.

The ERRB pin connects to a GPIO pin on the microcontroller to function as an interrupt if an error occurs.

If a Loop error and a SPI Timeout error occur simultaneously and the device is configured with conflicting error output currents, the OUT pin current reports the Loop Error.

|                   | STATUS Register                        | Loop Reporting                                                                                                  | ERRB Reporting                                                            |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Frame Error       | Reported in FERR_STS                   | Not reported                                                                                                    | Always reported                                                           |

| Loop Error        | Reported in LOOP_STS and CURR_LOOP_STS | Reported by default unless<br>ERR_CONFIG:MASK_LOOP_E<br>RR is set to 1                                          | Reported by default unless<br>ERR_CONFIG:DIS_LOOP_ERR_ERRB<br>is set to 1 |

| SPI Timeout Error | Reported in SPI_TIMEOUT_ERR            | Reported by default unless either<br>ERR_CONFIG:MASK_SPI_ERR<br>or<br>ERR_CONFIG:MASK_SPI_TOU<br>T are set to 1 | Reported by default unless<br>ERR_CONFIG:MASK_SPI_TOUT is set<br>to 1     |

Product Folder Links: DAC161S997

### 8.5 Programming

#### 8.5.1 Serial Interface

The 4-wire interface is compatible with SPI, QSPI, and MICROWIRE, as well as most DSPs. See the *Timing Requirements* section for timing information about the read and write sequences. The serial interface is comprised of CSB, SCLK, SDIs and SDO. The DAC161S997 supports both Mode 0 and Mode 3 of the SPI protocol.

A bus transaction is initiated by the falling edge of CSB. When CSB is low, the input data is sampled at the SDI pin by the rising edge of the SCLK. The output data is asserted on the SDO pin at the falling edge of SCLK.

A valid transfer requires an integer multiple of 24 SCLK cycles. If CSB is raised before the 24th rising edge of the SCLK, the transfer aborts and a Frame Error is reported. If CSB is held low after the 24th falling edge of the SCLK and additional SCLK edges occur, the data continues to flow through the FIFO and out the SDO pin. When CSB transitions high, the internal controller decodes the most recent 24 bits that were received before the rising edge of CSB. CSB must transition to high after an integer multiple of 24 clock cycles, otherwise a Frame Error is reported and the transaction is considered invalid. When a valid number of SCLK pulses occur with CSB low, the DAC then performs the requested operation after CSB transitions high.

Figure 8. SPI Data Format

The acquired data is shifted into an internal 24-bit shift register (MSB first) which is configured as a 24-bit deep FIFO. As the data is being shifted into the FIFO via the SDI pin, the prior contents of the register are being shifted out through the SDO output. While CSB is high, SDO is in a high Z-state. At the falling edge of CSB, SDO presents the MSB of the data present in the shift register. SDO is updated on every subsequent falling edge of SCLK.

#### NOTE

The first SDO transition will happen on the first falling edge AFTER the first rising edge of SCLK when CSB is low.

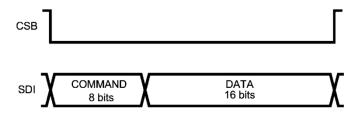

The 24 bits of data contained in the FIFO are interpreted as an 8-bit COMMAND word followed by 16-bits of DATA. The general format of the 24-bit data stream is shown in Figure 9. Complete instruction set is tabulated in the *Detailed Description* section.

Figure 9. SPI Command and Data Words

0 Submit Documentation Feedback

Copyright © 2013–2014, Texas Instruments Incorporated

# **Programming (continued)**

#### 8.5.1.1 SPI Write

SPI write operation is used to change the state of the device. Handshaking does not occur between the master and the slave (DAC161S997), and the master must control the communication on the following inputs: SCLK, CSB, SDI. The format of the data transfer is described in the *Serial Interface* section.

A write is composed of two sections, 8-bits corresponding to a command and 16-bits of data. A command is simply the address of the desired register to update. Note that some registers are read-only; a write to these registers will have no effect on the device operation and the register contents will not change. The user instruction set is shown in the *Detailed Description* section.

During power up or device reset, the register contents of all writable registers are set to the listed values in the *Detailed Description* section.

If the DAC161S997 is used in a highly noisy environment in which SPI errors are potentially an issue, the DAC161S997 supports a more robust protocol (see *Optional Protected SPI Writes*).

#### 8.5.1.2 SPI Read

The read operation requires all 4 wires of the SPI interface, which are SCLK, SCB, SDI, and SDO. The simplest READ operation occurs automatically during any valid transaction on the SPI bus because the SDO pin of DAC161S997 always shifts out the contents of the internal FIFO. Therefore the data being shifted in to the FIFO is verified by initiating another transaction and acquiring data at SDO, allowing only for the verification of FIFO contents.

The internal registers are accessed by the user through a register read command. A register read command is formed by setting bit 7 of the command to 1 (effectively ORing with 0x80) with the address of the desired register to be read and sending the resulting 8 bits as the command (see *Detailed Description*). For example, the register read command of the STATUS register (address 0x05) would be 0x85.

A register read requires two SPI transactions to recover the register data. The first transaction shifts in the register read command; an 8-bits of command byte followed by 16-bits of *dummy* data. The register read command transfers the contents of the internal register into the FIFO. The second transaction shifts out the FIFO contents; an 8-bit command byte (which is a copy of previous transaction) followed by the register data. The Register Read operation is shown in Figure 10.

Figure 10. SPI Register Read Operation

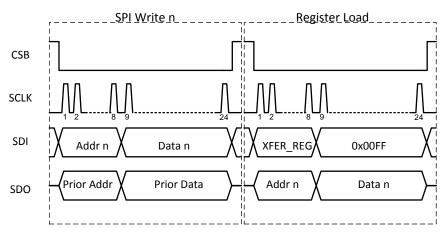

### 8.5.1.3 Optional Protected SPI Writes

The DAC161S997 supports an optional SPI protocol intended to provide robust support against SPI write errors.

When PROTECT\_REG\_WR is set to 1, all register writes require a subsequent XFER\_REG command (a write of 0x00FF to XFER\_REG[0x01]) to load the transferred data into the register address (see Figure 11). This requirement provides protection against write errors in an electrically noisy environment.

Copyright © 2013–2014, Texas Instruments Incorporated

### **Programming (continued)**

Figure 11. Protected SPI writes

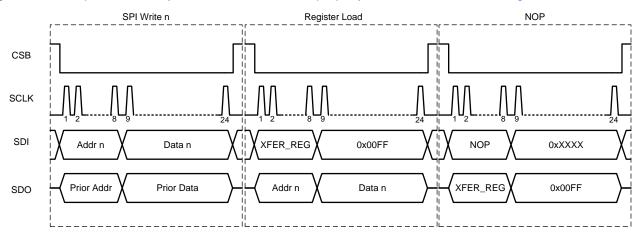

#### 8.5.1.3.1 SPI Write Error Correction

To minimize the chance of a SPI write error, TI recommends to append a NOP command onto the end of every register write sequence to verify that the XFER\_REG is properly executed, as shown in Figure 12.

Figure 12. Protected SPI writes with NOP command

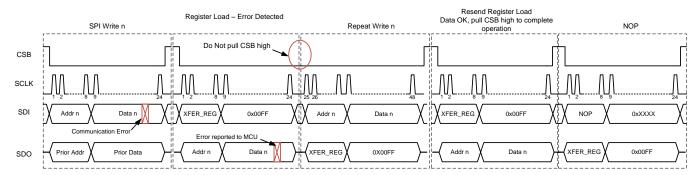

The XFER\_REG command combined with the automatic SDO loopback of the previous SPI write data prevents loading of incorrect data into a register. If the loopback indicates a communication error has occurred (see Figure 13), the CSB pin is held low and the previous write command is repeated. Although the second SPI transaction had 48 SCLK pulses instead of 24 pulses, this is not considered a frame error. A frame error is indicated when the number of SCLK pulses is not an integer multiple of 24.

# **Programming (continued)**

Figure 13. Detection of Error in Register Load

If a communication error occurs in the XFER\_REG command, it is detected during the trailing NOP command (see Figure 14). Although the register load is incomplete, the device has not changed operations. Repeat the original data and XFER\_REG command.

Figure 14. Detection of Error in Register Readback

### 8.6 Register Maps

Unless otherwise indicated, bits outside the register fields listed below are *do not care*, and will not change device configuration. Register read operations on such *do not care* fields will be 0. Registers are read/write unless indicated otherwise.

Table 1. XFER\_REG (Write Only)

|           | Address = 0x01 |                                                                                                                                                                                                             |  |  |

|-----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit Field | Field Name     | Description                                                                                                                                                                                                 |  |  |

| 15:0      |                | When PROTECT_REG_WR is set to 1, then a XFER_REG command is necessary to transfer the previous register write data into the appropriate address. Set this register to 0x00FF to perform a XFER_REG command. |  |  |

Table 2, NOP

| Address = 0x02 |                                  |                                                                                                         |  |  |  |  |  |

|----------------|----------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field      | Bit Field Field Name Description |                                                                                                         |  |  |  |  |  |

| 15:0           |                                  | No Operation. A write to this register will not change any device configuration.                        |  |  |  |  |  |

|                |                                  | This command indicates that the SPI connection is functioning and is used to avoid SPI_INACTIVE errors. |  |  |  |  |  |

Product Folder Links: DAC161S997

# Table 3. WR\_MODE

| Address = 0x03; Default = 0x0000 |                |                                                                                                                                                                                             |  |  |  |  |  |

|----------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field Field Name Description |                |                                                                                                                                                                                             |  |  |  |  |  |

|                                  |                | 0: Register write data transfers to appropriate address immediately after CSB goes high. <b>Default value.</b>                                                                              |  |  |  |  |  |

| 0                                | PROTECT_REG_WR | 1: Enable protected register transfers: all register writes require a subsequent XFER_REG command to finalize the loading of register data. Refer to <i>Optional Protected SPI Writes</i> . |  |  |  |  |  |

### Table 4. DACCODE

| Address = 0x04; Default = 0x2400, 0xE800 |               |                                                                                                           |  |  |  |  |

|------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field                                | Field Name    | Description                                                                                               |  |  |  |  |

| 15:0                                     | DACCODE[45:0] | 16-bit natural binary word, where D15 is the MSB, which indicates the desired DAC output code.            |  |  |  |  |

|                                          | DACCODE[15:0] | Note the default value of this register is based on the state of the ERR_LVL pin during startup or reset. |  |  |  |  |

# Table 5. ERR\_CONFIG

| Address = 0x05; Default = 0x0102 |                   |                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field                        | Field Name        | Description                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 10:8                             | L_RETRY_TIME[2:0] | L_RETRY_TIME sets the time interval between successive attempts to reassert the desired DACCODE output current when a loop error is present. This has no effect if either MASK_LOOP_ERR is set to 1 or if DIS_RETRY_LOOP is set to 1.                                                         |  |  |  |  |

|                                  |                   | LOOP Retry time = (L_RETRY_TIME + 1) × 50 ms                                                                                                                                                                                                                                                  |  |  |  |  |

|                                  |                   | Default value = 1 (100 ms)                                                                                                                                                                                                                                                                    |  |  |  |  |

| 7                                | DIS_RETRY_LOOP    | 0: When a loop error is occurring, periodically attempt to send desired DACCODE output current instead of the set ERR_LOW current. The interval between attempts is set by L_RETRY_TIMER. <b>Default value.</b>                                                                               |  |  |  |  |

|                                  |                   | 1: Do not periodically reassert DACCODE output when a loop error is present; reassert DACCODE after STATUS Register is read out.                                                                                                                                                              |  |  |  |  |

| 6                                | MACK LOOP EDD     | 0: When a LOOP error is detected the DAC161S997 outputs the current indicated by ERR_LOW instead of DACCCODE. <b>Default value.</b>                                                                                                                                                           |  |  |  |  |

| 0                                | MASK_LOOP_ERR     | 1: When a Loop Error is detected the DAC161S997 tries to maintain DACCODE current on pin OUT.                                                                                                                                                                                                 |  |  |  |  |

| 5                                | DIS_LOOP_ERR_ERRB | 0: When a LOOP error is detected the DAC161S997 drives ERRB pin low. <b>Default value.</b>                                                                                                                                                                                                    |  |  |  |  |

|                                  |                   | 1: When a LOOP error is detected the DAC161S997 does not drive ERRB pin low.                                                                                                                                                                                                                  |  |  |  |  |

| 4                                | MASK_SPI_ERR      | 0: SPI timeout errors change the OUT pin current to an error value, which is determined by ERRLVL pin and contents of ERR_LOW or ERR_HIGH. <b>Note:</b> MASK_SPI_TOUT must be set to 0 for this to be reported. <b>Default value.</b>                                                         |  |  |  |  |

|                                  |                   | 1: SPI timeout errors do not change the OUT pin current to an error value.                                                                                                                                                                                                                    |  |  |  |  |

|                                  |                   | SPI_TIMEOUT sets the time interval for SPI timeout error reporting. After each SPI write command, an internal timer is reset; if no subsequent write occurs before the timer reaches SPI timeout, a SPI timeout error is reported. SPI_ERROR reporting is inhibited by setting MASK_SPI_TOUT. |  |  |  |  |

| 3:1                              | SPI_TIMEOUT[2:0]  | A NOP write is considered a valid write and resets the timer without changing the device configuration.                                                                                                                                                                                       |  |  |  |  |

|                                  |                   | SPI Timeout = (SPI_TIMEOUT + 1) x 50 ms                                                                                                                                                                                                                                                       |  |  |  |  |

|                                  |                   | SPI_TIMEOUT default value = 1 (100 ms)                                                                                                                                                                                                                                                        |  |  |  |  |

| 0                                | MASK_SPI_TOUT     | 0: SPI timeout error reporting is enabled. A SPI timeout error drives ERRB low when a SPI Timeout error occurs. <b>Default value.</b>                                                                                                                                                         |  |  |  |  |

|                                  |                   | 1: SPI timeout error reporting is inhibited.                                                                                                                                                                                                                                                  |  |  |  |  |

Product Folder Links: DAC161S997

### Table 6. ERR\_LOW

| Address = 0x06; Default = 0x2400 |              |                                                                                                                                                                                                                                              |  |  |  |  |

|----------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field                        | Field Name   | Description                                                                                                                                                                                                                                  |  |  |  |  |

|                                  |              | Under some error conditions the output current corresponding to this value is the DAC output, regardless of the value of DACCODE. The ERR_LOW value is used as the upper byte of the DACCODE, while the lower byte is forced to 0x00.        |  |  |  |  |

| 15:8                             | ERR_LOW[7:0] | ERR_LOW must be between 0x00(0 mA) and 0x80(12 mA). The DAC161S997 ignores any value outside of that range and retains the previous value in the register. Refer to the <i>Error Detection And Reporting</i> section for additional details. |  |  |  |  |

|                                  |              | The default value is 0x24, which corresponds to approximately 3.37 mA on pin OUT.                                                                                                                                                            |  |  |  |  |

# Table 7. ERR\_HIGH

| Address = 0x07; Default = 0xE800 |               |                                                                                                                                                                                                                                       |  |  |  |  |

|----------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field                        | Field Name    | Description                                                                                                                                                                                                                           |  |  |  |  |

|                                  | ERR_HIGH[7:0] | Under some error conditions the output current corresponding to this value is the Doutput, regardless of the value of DACCODE. The ERR_HIGH value is used as the upper byte of the DACCODE, while the lower byte is forced to 0x00.   |  |  |  |  |

| 15:8                             |               | ERR_HIGH must be greater than or equal to 0x80 (12 mA). The DAC161S997 ignores any value below 0x80 and retains the previous value in the register. Refer to the <i>Error Detection And Reporting</i> section for additional details. |  |  |  |  |

|                                  |               | The default value is 0xE8, which corresponds to approximately 21.8 mA on pin OUT.                                                                                                                                                     |  |  |  |  |

### Table 8. RESET

|           | Address = 0x08               |                                                                                                                                  |  |  |  |  |  |

|-----------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field | Field Field Name Description |                                                                                                                                  |  |  |  |  |  |

| 15:0      |                              | Write 0xC33C to the RESET register followed by a NOP to reset the device. All writable registers are returned to default values. |  |  |  |  |  |

# Table 9. STATUS (Read-Only)

|           | Address = 0x09 or 0x7F |                                                                                                                                                                                                                                   |  |  |  |  |  |

|-----------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field | Field Name             | Description                                                                                                                                                                                                                       |  |  |  |  |  |

| 7:5       | DAC_RES[2:0]           | DAC resolution                                                                                                                                                                                                                    |  |  |  |  |  |

| 7.5       | DAC_RES[2.0]           | On DAC161S997, returns a 111.                                                                                                                                                                                                     |  |  |  |  |  |

|           |                        | Returns the state of the ERRLVL pin:                                                                                                                                                                                              |  |  |  |  |  |

| 4         | ERRLVL_PIN             | 1 = ERRLVL pin is tied HIGH                                                                                                                                                                                                       |  |  |  |  |  |

|           |                        | 0 = ERRLVL pin is tied LOW                                                                                                                                                                                                        |  |  |  |  |  |

|           |                        | Frame-error status sticky bit                                                                                                                                                                                                     |  |  |  |  |  |

|           | FERR STS               | 1 = A frame error has occurred since the last STATUS read.                                                                                                                                                                        |  |  |  |  |  |

| 3         |                        | 0 = No frame error occurred since the last STATUS read.                                                                                                                                                                           |  |  |  |  |  |

|           |                        | This error is cleared by reading the STATUS register. A frame error is caused by an incorrect number of clocks during a register write. A register write without an integer multiple of 24 clock cycles will cause a Frame error. |  |  |  |  |  |

|           |                        | SPI time out error                                                                                                                                                                                                                |  |  |  |  |  |

|           |                        | 1 = The SPI interface has not received a valid command within the interval set by SPI_TIMEOUT.                                                                                                                                    |  |  |  |  |  |

| 2         | SPI_TIMEOUT_ERR        | 0 = The SPI interface has received a valid command within the interval set by SPI_TIMEOUT                                                                                                                                         |  |  |  |  |  |

|           |                        | If this error occurs, it is cleared with a properly formatted write command to a valid address.                                                                                                                                   |  |  |  |  |  |

Product Folder Links: DAC161S997

# Table 9. STATUS (Read-Only) (continued)

| Address = 0x09 or 0x7F |               |                                                                                                                                                                                                                                                |  |  |  |  |

|------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field              | Field Name    | Description                                                                                                                                                                                                                                    |  |  |  |  |

|                        |               | Loop status sticky bit                                                                                                                                                                                                                         |  |  |  |  |

|                        | LOOP_STS      | 1 = A loop error has occurred since last read of STATUS.                                                                                                                                                                                       |  |  |  |  |

| 1                      |               | 0 = No loop error has occurred since last read of STATUS.                                                                                                                                                                                      |  |  |  |  |

|                        |               | Returns the loop error status. When the value in this register is 1, the DAC161S997 is unable to maintain the output current set by DACCODE at some point since the last STATUS read. This indicator clears after reading the STATUS register. |  |  |  |  |

|                        |               | Current loop status                                                                                                                                                                                                                            |  |  |  |  |

|                        |               | 1 = A loop error is occurring.                                                                                                                                                                                                                 |  |  |  |  |

| 0                      | CURR_LOOP_STS | 0 = No loop error is occurring.                                                                                                                                                                                                                |  |  |  |  |

|                        |               | Returns the current Loop error status. When the value in this register is 1, the DAC161S997 is unable to maintain the output current set by DACCODE.                                                                                           |  |  |  |  |

Submit Documentation Feedback

Copyright © 2013–2014, Texas Instruments Incorporated

# 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

#### 9.1.1 16-bit Dac And Loop Drive

#### 9.1.1.1 DC Characteristics

The DAC converts the 16-bit input code in the DACCODE registers to an equivalent current output. The  $\Sigma\Delta$  DAC output is a current pulse which is then filtered by a third-order RC lowpass filter and boosted to produce the loop current ( $I_{LOOP}$ ) at the device OUT pin.

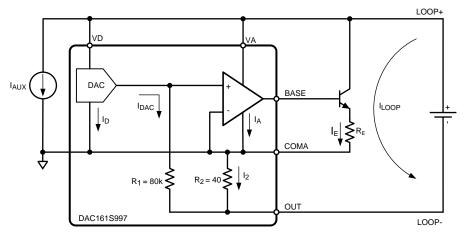

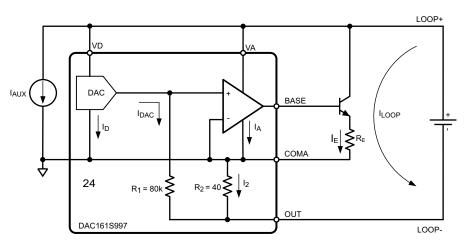

Figure 15. Loop-Powered Transmitter

Figure 15 shows the principle of operation of the DAC161S997 in the Loop-Powered Transmitter (the circuit details are omitted for clarity). In Figure 15,  $I_D$  and  $I_A$  represent supply (quiescent) currents of the internal digital and analog blocks.  $I_{AUX}$  represents supply (quiescent) current of companion devices present in the system, such as the voltage regulator and the digital interface. Because both the control loop formed by the amplifier and the bipolar transistor force the voltage across  $R_1$  and  $R_2$  to be equal, under normal conditions, the  $I_{LOOP}$  is dependent only on  $I_{DAC}$  through the following relationship (see Equation 1).

$$I_{LOOP} = (1 + R1 / R2) I_{DAC}$$

where

•

$$I_{DAC} = f(DACCODE)$$

(1)

Although  $I_{Loop}$  has a number of component currents,  $I_{LOOP} = I_{DAC} + I_D + I_A + I_{AUX} + I_E$ , only  $I_E$  is regulated by the loop to maintain the relationship shown in Equation 1. Because only the magnitude of  $I_E$  is controlled, not the direction, there is a lower limit to  $I_{LOOP}$ . This limit is dependent on the fixed components  $I_A$  and  $I_D$ , and on system implementation through  $I_{AUX}$ .

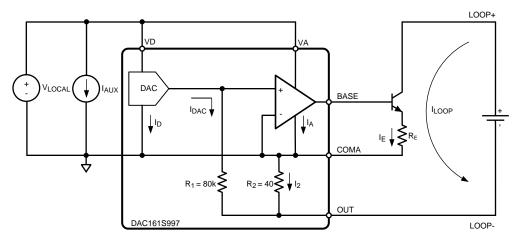

Figure 16. Self-Powered Transmitter

Figure 16 shows the variant of the transmitter where the local supply provides supply currents to the system blocks, and not the 4-20mA loop Self-Powered Transmitter. The ame basic relationship between the  $I_{LOOP}$  and  $I_{DAC}$  continues, but the component currents of  $I_{LOOP}$  are only  $I_{DAC}$  and  $I_{E}$ .

#### 9.1.1.2 DC Input-Output Transfer Function

The output current sourced by the OUT pin of the device is expressed by Equation 2.

$$I_{LOOP} = 24 \text{ mA (DACCODE } / 2^{16})$$

(2)

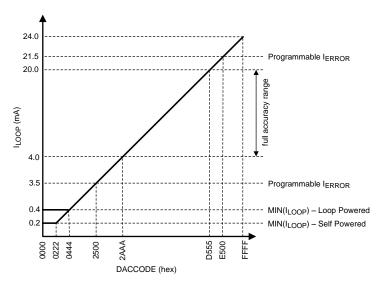

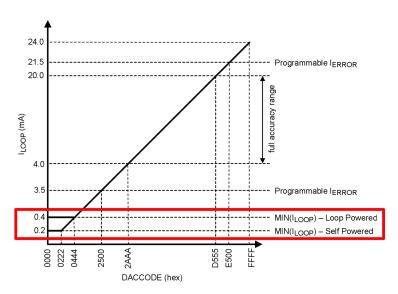

The valid DACCODE range is the full 16-bit code space (0x0000 to 0xFFFF), resulting in the  $I_{DAC}$  range of 0 to approximately 12  $\mu$ A, which, however, does not result in the  $I_{LOOP}$  range of 0 to 24 mA. The maximum output current sourced out of OUT pin,  $I_{LOOP}$ , is 24 mA. The minimum output current is dependent on the system implementation. The minimum output current is the sum of the supply currents of the DAC161S997 internal blocks,  $I_A$ ,  $I_D$ , and companion devices present in the system,  $I_{AUX}$ . The last component current,  $I_E$ , is theoretically controlled down to 0, however, due to the stability considerations of the control loop, not allowing the  $I_E$  to drop below 200  $\mu$ A is advised.

The graph in Figure 17 shows the DC transfer characteristic of the 4-20mA transmitter, including minimum current limits. The minimum current limit for the Loop-Powered Transmitter is typically around 400  $\mu$ A ( $I_D+I_A+I_{AUX}+I_E$ ). The minimum current limit for the Self-Powered Transmitter is typically around 200  $\mu$ A ( $I_E$ ). Typical values for  $I_D$  and  $I_A$  are listed in the *Electrical Characteristics* table.  $I_E$  depends on the BJT device used.

Figure 17. DAC-DC Transfer Function

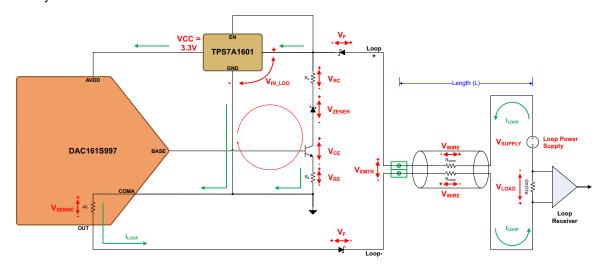

### 9.1.1.3 Loop Interface

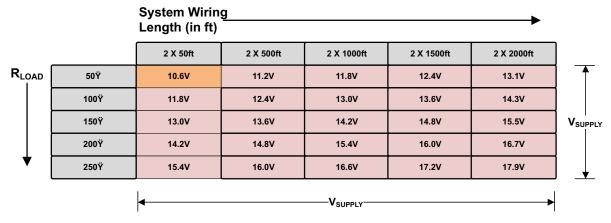

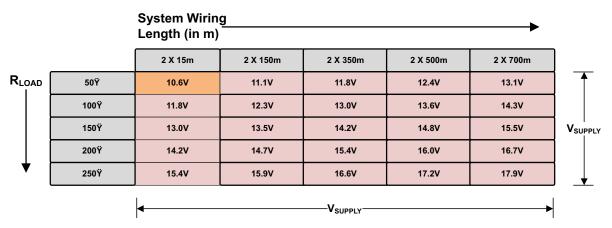

The DAC161S997 cannot directly interface to the typical 4 - 20 mA loop due to the excessive loop supply voltage. The loop interface has to provide the means of stepping down the LOOP Supply to 3.6V. This can be accomplished with either a linear regulator (LDO) or switching regulator while keeping in mind that the regulator's quiescent current will have direct effect on the minimum achievable I<sub>LOOP</sub> (see *DC Input-Output Transfer Function*).

The second component of the loop interface is the external NPN transistor (BJT). This device is part of the control circuit that regulates the transmitter's output current ( $I_{LOOP}$ ). Since the BJT operates over the wide current range, spanning at least 4 - 20 mA, it is necessary to degenerate the emitter in order to stabilize transistor's transconductance ( $g_m$ ). The degeneration resistor of  $22\Omega$  is suggested in typical applications. For circuit details, see Figure 21.

The NPN BJT should not be replaced with an N-channel FET (Field Effect Transistor) for the following reasons: discrete FET's typically have high threshold voltages (VT), in the order of 1.5V to 2V, which is beyond the BASE output maximum range; discrete FET's present higher load capacitance which may degrade system stability margins; and BASE output relies on the BJT's base current for biasing.

### 9.1.1.4 Loop Compliance

The maximum V(LOOP+,LOOP-) potential is limited by the choice of step-down regulator, and the external BJT's Collector Emitter breakdown voltage. For minimum V(LOOP+, LOOP-) potential consider TROUBLE Figure 16. Here, observe that V(LOOP+,LOOP-)  $\cong$  min(V<sub>CE</sub>) + I<sub>LOOP</sub>R<sub>E</sub> + I<sub>LOOP</sub>R<sub>2</sub> = min(V<sub>CE</sub>) + 0.53V + 0.96V = 3.66V, at I<sub>LOOP</sub> = 24mA. The voltage drop across internal R<sub>2</sub> is specified in *Electrical Characteristics*.

#### 9.1.1.5 AC Characteristics

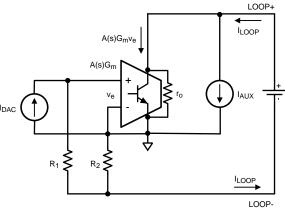

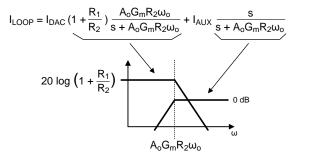

The approximate frequency dependent characteristics of the loop drive circuit can be analyzed using the circuit in Figure 18.

Figure 18. Capacitances Affecting Control Loop

Here it is assumed that the internal amplifier dominates the frequency response of the system, and it has a single pole response. The BJT's response, in the bandwidth of the control loop, is assumed to be frequency independent and is characterized by the transconductance  $g_m$  and the output resistance  $r_o$ .

As in previous sections  $I_{DAC}$  and  $I_{AUX}$  represent the filtered output of the  $\sum \Delta$  modulator and the quiescent current of the companion devices.

The circuit in Figure 18 can be further simplified by omitting the on-board capacitances, whose effect will be discussed in *Stability*, and by combining the amplifier, the external transistor and resistor  $R_E$  into one  $G_m$  block. The resulting circuit is shown in Figure 19.

By assuming that the BJT's output resistance (r<sub>o</sub>) is large, the loop current I<sub>LOOP</sub> can be expressed as:

$$I_{LOOP} = I_{AUX} + A(s)G_m v_e$$

$$(3)$$

Figure 19. AC Analysis Model of a Transmitter

The sum of voltage drops around the path containing R<sub>1</sub>, R<sub>2</sub> and v<sub>e</sub> is:

$$v_{e} = I_{DAC}R_{1} - [I_{AUX} + A(s)G_{m}v_{e} - I_{DAC}]R_{2}$$

(4)

An assumption is made on the response of the internal amplifier:

$$A(s) = \frac{A_0 \omega_0}{s} \tag{5}$$

(6)

### Application Information (continued)

By combining the above the final expression for the I<sub>LOOP</sub> as a function of 2 inputs I<sub>DAC</sub> and I<sub>AUX</sub> is:

The result above reveals that there are 2 distinct paths from the inputs  $I_{DAC}$  and  $I_{AUX}$  to the output  $I_{LOOP}$ .  $I_{DAC}$  follows the low-pass, and the  $I_{AUX}$  follows the high-pass path.

In both cases the corner frequency is dependent on the effective transconductance,  $G_m$ , of the external transistor. This implies that control loop dynamics could vary with the output current  $I_{LOOP}$  if  $G_m$  were allowed to be just native device transconductance  $g_m$ . This undesirable behavior is mitigated by the degenerating resistor  $R_E$  which stabilizes  $G_m$  as follows:

$$G_{m} \cong \frac{1}{1/g_{m}} + R_{E} \cong \frac{1}{R_{E}}$$

$$(7)$$

This results in the frequency response which is largely independent of the output current I<sub>LOOP</sub>:

$$I_{LOOP} = I_{DAC} (1 + \frac{R_1}{R_2}) \frac{A_0 \frac{R_2}{R_E} \omega_0}{s + A_0 \frac{R_2}{R_E} \omega_0} + I_{AUX} \frac{s}{s + A_0 \frac{R_2}{R_E} \omega_0}$$

(8)

While the bandwidth of the  $I_{DAC}$  path may not be of great consequence given the low frequency nature of the 4-20 mA current loop systems, the location of the pole in the  $I_{AUX}$  path directly affects PSRR of the transmitter circuit. This is further discussed in PSRR.

#### 9.1.1.5.1 Step Response

The transient input-output characteristics of the DAC161S997 are dominated by the response of the RC filter at the output of the  $\Sigma\Delta$  DAC. Settling times due to step input are shown in *Typical Characteristics*.

#### 9.1.1.5.2 Output Impedance

The output impedance is described as:

$$R_{OUT} = \frac{\Delta V_{LOOP}}{\Delta I_{LOOP}}$$

(9)

By considering the circuit in Figure 19, and setting  $I_{DAC} = I_{AUX} = 0$ , the following expression can be obtained:

$$R_{OUT}(s) = R_2 + [1 + A(s)G_mR_2]r_o$$

(10)

As in AC Characteristics an assumption can be made on the frequency response of the internal amplifier, and the effective transconductance  $G_m$  should be stabilized with external  $R_E$  leading to:

$$R_{\text{OUT}}(s) \approx \frac{A_{\circ} \left(\frac{R_{2}}{R_{E}}\right) \omega_{\circ} r_{\circ}}{s}$$

(11)

The output impedance of the transmitter is a product of the external BJT's output resistance  $r_o$ , and the frequency characteristics of the internal amplifier. At low frequencies this results in a large impedance that does not significantly affect the output current accuracy.

Copyright © 2013–2014, Texas Instruments Incorporated

#### 9.1.1.5.3 PSRR

Power Supply Rejection Ratio is defined as the ability of the current control loop to reject the variations in the supply current of the companion devices, I<sub>AUX</sub>. Specifically:

$$PSRR = 20 \text{ xlog}_{10} \left( \frac{\Delta I_{LOOP}}{\Delta I_{AUX}} \right)$$

(12)

It was shown in *AC Characteristics* that the  $I_{AUX}$  affects  $I_{LOOP}$  via the high-pass path whose corner frequency is dependent on the effective Gm of the external BJT. If that dependence were not mitigated with the degenerating resistor  $R_E$ , the PSRR would be degraded at low output current  $I_{LOOP}$ .

The typical PSRR performance of the transmitter shown in Figure 6 is shown in Typical Characteristics.

#### 9.1.1.5.4 Stability

The current control loop's stability is affected by the impedances present in the system. Figure 18 shows the simplified diagram of the control loop, formed by the on-board amplifier and an external BJT, and the lumped capacitances  $C_{X1}$  through  $C_{X4}$  that model any other external elements.

$C_{X1}$  typically represents a local step-down regulator, or LDO, and any other companion devices powered from the LOOP+. This capacitance reduces the stability margins of the control loop, and therefore it should be limited. RX1 can be used to isolate  $C_{X1}$  from LOOP+ node and thus remedy the stability margin reduction. If  $R_{X1} = 0$ ,  $C_{X1}$  cannot exceed 10 nF.  $R_{X1} = 200\Omega$  is recommended if it can be tolerated. Minimum  $R_{X1} = 40\Omega$  if  $C_{X1}$  exceeds 10 nF.

$C_{X3}$  also adversely affects stability of the loop and it must be limited to 20 pF.  $C_{X4}$  affects the control loop in the same way as  $C_{X1}$ , and it should be treated in the same way as  $C_{X1}$ .  $C_{X2}$  is the only capacitance that improves stability margins of the control loop. Its maximum size is limited only by the safety requirements.

Stability is a function of  $I_{LOOP}$  as well. Since  $I_{LOOP}$  is approximately equal to the collector current of the external BJT,  $G_m$  of the BJT, and thus loop dynamics, depend on  $I_{LOOP}$ . This dependence can be reduced by degenerating the emitter of the BJT with a small resistance as discussed in *Loop Interface*. Inductance in series with the LOOP+ and LOOP- do not significantly affect the control loop.

### 9.1.1.5.5 Noise and Ripple

The output of the DAC is a current pulse train. The transition density varies throughout the DAC input code range ( $I_{LOOP}$  range). At the extremes of the code range, the transition density is the lowest which results in low frequency components of the DAC output passing through the RC filter. Hence, the magnitude of the ripple present in  $I_{LOOP}$  is the highest at the ends of the transfer characteristic of the device (see *Typical Characteristics*).

It should be noted that at wide noise measurement bandwidth, it is the ripple due to the  $\Sigma\Delta$  modulator that dominates the noise performance of the device throughout the entire code range of the DAC. This results in the "U" shaped noise characteristic as a function of output current. At narrow bandwidths, and particularly at mid-scale output currents, it is the amplifier driving the external BJT that starts to dominate as a noise source.

#### 9.1.1.5.6 Digital Feedthrough

Digital feedthrough is indiscernible from the ripple induced by the  $\Sigma\Delta$  modulator.

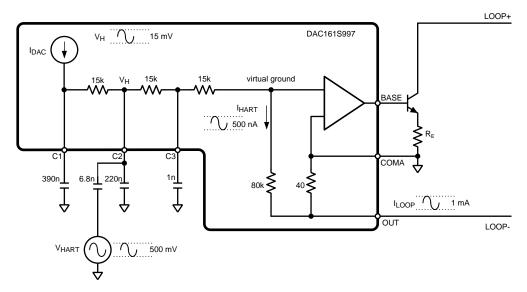

#### 9.1.1.5.7 HART Signal Injection

The HART specification requires minimum suppression of the sensor signal in the HART signal band (1-2 kHz) of about 60 dB. The filter in Figure 20 below meets that requirement.

Product Folder Links: DAC161S997

Figure 20. HART Signal Injection

#### 9.1.1.5.8 RC Filter Limitation

In an effort to speed up the transient response of the device the user can reduce the capacitances associated with the low-pass filter at the output of the  $\Sigma\Delta$  modulator. However, to maintain stability margins of the current control loop it is necessary to have at least  $C_1 = C_2 = C_3 = 1$ nF.

# 9.2 Typical Application

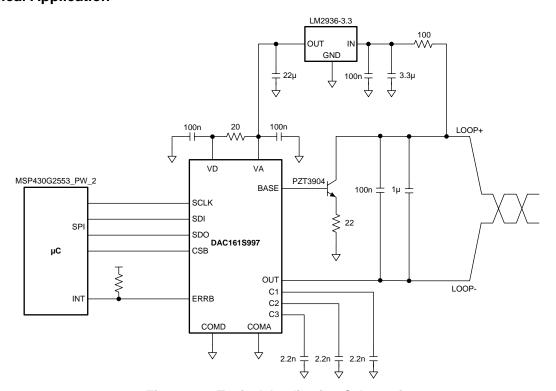

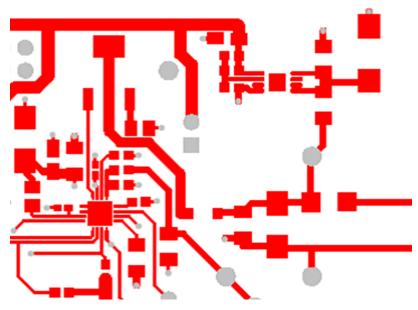

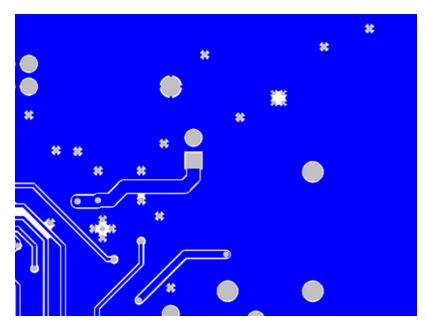

Figure 21. Typical Application Schematic

#### 9.2.1 Design Requirements

The objective of the example below is to focus on the design of a robust, low-power, precise, long- term stable, 2-wire, loop-powered, 4- to 20-mA current-output temperature transmitter by making best use of signal chain, power and computing solutions. This design uses a RTD-temperature sensor with a 4- to 20-mA current-loop transmitter.

### 9.2.2 Detailed Design Procedure

The DAC161S997output is a current pulse which is then filtered by a third-order RC low-pass filter and boosted to produce the loop current ( $I_{LOOP}$ ) at the device OUT pin. Figure 22 shows the principle of operation of the DAC161S997 in the loop-powered transmitter. The  $I_{LOOP}$  has a number of component currents as given in Equation 13.

$$I_{LOOP} = I_{DAC} + I_D + I_A + I_E = 24 \text{ mA} \times \left[ \frac{DAC\_CODE}{2^{16}} \right]$$

#### where

- I<sub>DAC</sub> = f(DAC\_CODE),

- I<sub>D</sub> and I<sub>A</sub> represent the supply currents of internal digital and analog blocks,

- I<sub>AUX</sub> represents the supply current of companion devices present in the system,

- I<sub>E</sub> is the only component which is regulated by the control loop to ensure that the actual loop current corresponds to the DAC input code applied by the MCU.

(13)

Figure 22. Loop Powered Transmitter

#### 9.2.2.1 Reasons for Choosing a 3.9-V Zener Diode

The first and most important requirement for the proper functioning of the entire circuitry is a stable power supply. A good design ensures that the LDO gets the sufficient input voltage ( $V_{IN\_LDO}$ ) to generate a stable 3.3 V under minimum-loop, power-supply voltage and minimum-loop current conditions.

$$V_{IN\_LDO\ (MIN\ REQUIRED\ at\ 3.3\ mA)} = V_{CC} + V_{DO\ (MIN)} = 3.3\ V + 0.1\ V = 3.4\ V$$

(14)

From the circuit implementation, it is evident that the LDO input voltage  $V_{IN\_LDO}$  is function of loop current and collector-emitter drop ( $V_{CE}$ ) of the bipolar junction transistor (BJT). Apply Kirchhoff 's Voltage Law (KVL) in the inner loop:

$$V_{(IN\ LDO)} = [(R_C \times I_{LOOP}) + V_{ZENER} + V_{CF} + (R_F \times I_{LOOP})]$$

(15)

At minimum loop power supply voltage, BJT operation is pushed towards saturation, which means that  $V_{CE}$  is approximately 0 V (minimum). Due to the stability considerations of the current control loop, the minimum output current ( $I_{LOOP(MIN)}$ ) below 200  $\mu$  A is not advised as shown in Figure 23.