# Precision Sample and Hold Amplifier

#### **FEATURES**

- 4μs Typical Acquisition Time

- Guaranteed 0.01% Max. Gain Error

- 2mV Typ. Offset Voltage

- 2.5mV Max. Hold Step

- Very Low Feedthrough 80dB Min.

- High Input Impedance Under All Conditions

- Logic Inputs Compatible with All Logic Families

### **APPLICATIONS**

- 12-Bit Data Acquisition Systems

- Ramp Generators

- Analog Switches

- Staircase Generators

- Sample and Difference Circuits

### DESCRIPTION

The LF398 is a precision sample and hold amplifier which uses a combination of bipolar and junction FET transistors to provide precision, high speed, and long hold times. A typical offset voltage of 2mV and gain error of 0.004% allow this sample and hold amplifier to be used in 12-bit systems. Dynamic performance can be optimized by proper selection of the external hold capacitor. Acquisition times can be as low as  $4\mu$ s for small capacitors while hold step and droop errors can be held below 0.1mV and  $30\mu$ V/sec respectively when using larger capacitors.

The LF398 is fixed at unity gain with  $10^{10}\Omega$  input impedance independent of sample/hold mode. The logic inputs are high impedence differential to allow easy interfacing to any logic family without ground loop problems. A separate offset adjust pin can be used to zero the offset voltage in either the sample or hold mode. Additionally, the hold capacitor can be driven with an external signal to provide precision level shifting or "differencing" operation. The device will operate over a wide supply voltage range from  $\pm 5V$  to  $\pm 18V$  with very little change in performance, and key parameters are specified over this full supply range.

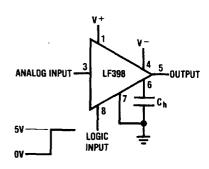

#### **Basic Sample and Hold**

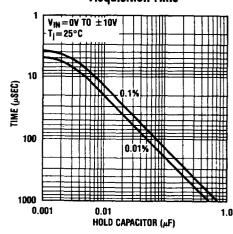

#### **Acquisition Time**

## **ABSOLUTE MAXIMUM RATINGS**

####

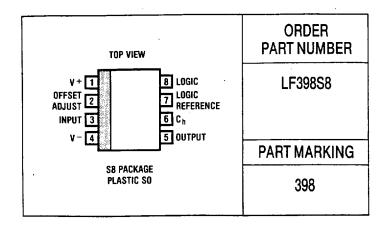

# PACKAGE/ORDER INFORMATION

# **ELECTRICAL CHARACTERISTICS** (Note 3)

| PARAMETER                                    | CONDITIONS                                                   |   | MIN | LF398<br>TYP     | MAX          | UNITS    |

|----------------------------------------------|--------------------------------------------------------------|---|-----|------------------|--------------|----------|

| Input Offset Voltage (Note 6)                |                                                              | • |     | 2                | 7<br>10      | mV<br>mV |

| Input Bias Current (Note 6)                  |                                                              | • |     | 10               | 50<br>100    | nA<br>nA |

| Input Impedance                              |                                                              |   |     | 10 <sup>10</sup> |              | Ω        |

| Gain Error                                   | R <sub>L</sub> = 10k                                         | • |     | 0.004            | 0.01<br>0.02 | %<br>%   |

| Feedthrough Attenuation Ratio at 1kHz        | $C_h = 0.01 \mu F$                                           |   | 80  | 96               |              | dB       |

| Output Impedance                             | "HOLD" Mode                                                  | • |     | 0.5              | 4<br>6       | Ω<br>Ω   |

| "HOLD" Step (Note 4)                         | $C_h = 0.01 \mu F, V_{OUT} = 0$                              |   |     | 0.5              | 2.5          | mV       |

| Supply Current (Note 6)                      | T <sub>i</sub> ≥25°C                                         |   |     | 4.5              | 6.5          | mA       |

| Logic and Logic Reference Input Current      |                                                              |   |     | 2                | 10           | μА       |

| Leakage Current Into Hold Capacitor (Note 6) | "HOLD" Mode (Note 5)                                         |   | •   | 30               | 200          | pA       |

| Acquisition Time to 0.1%                     | $\triangle V_{OUT} = 10V, C_h = 1000pF$<br>$C_h = 0.01\mu F$ |   |     | 4<br>16          |              | μS<br>μS |

| Hold Capacitor Charging Current              | $V_{IN} - V_{OUT} = 2V$                                      |   |     | 5                |              | mA       |

| Supply Voltage Rejection Ratio               | V <sub>OUT</sub> = 0                                         |   | 80  | 110              |              | dB       |

| Differential Logic Threshold                 |                                                              |   | 0.8 | 1.4              | 2.4          | ٧        |

The • denotes the specifications which apply over the full operating temperature range.

Note 1: T<sub>i</sub> max for the LF398S8 is 100°C.

Note 2: The logic inputs are protected to  $\pm$  30V differential as long as the voltage on both pins does not exceed the supply voltage. For proper operation, however, both logic and logic reference pins must be at least 2V below the positive supply and one of these pins must be at least 3V above the negative supply.

**Note 3:** Unless otherwise noted,  $V_S = \pm 15V$ ,  $T_j = 25^{\circ}C$ ,  $-11.5V \le V_{IN} \le = +11.5V$ ,  $C_h = 0.01 \mu F$ ,  $R_L = 10 k \Omega$  and unit is in "sample" mode. Logic reference = 0V and logic voltage = 2.5V.

**Note 4:** The hold step is sensitive to stray capacitance coupling between input logic signals and the hold capacitor. 1pF, for instance, will create an additional 0.5mV step with a 5V logic swing and a 0.01µF hold capacitor. Magnitude of the hold step is inversely proportional to hold capacitor value.

Note 5: Leakage current is measured at a *junction* temperature of 25°C. The effects of junction temperature rise due to power dissipation or elevated ambient can be calculated by doubling the 25°C value for each 11°C increase in chip temperature. Leakage is guaranteed over full input signal range.

**Note 6:** These parameters are guaranteed over a supply voltage range of  $\pm$  5V to  $\pm$  18V.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

LF398S8#TRPBF LF398S8#PBF LF398S8#TR