# **Surface Mount Micromachined Accelerometer**

The MMA2240KEG is a silicon capacitive, micromachined accelerometer featuring signal conditioning, a 2-pole low pass filter and temperature compensation. Zero-g offset full scale span and filter cut-off are factory set and require no external devices. A full system self-test capability verifies system functionality.

#### **Features**

- · Integral Signal Conditioning

- Linear Output

- · Ratiometric Performance

- · 2nd Order Bessel Filter Preserves Pulse Shape Integrity

- · Calibrated Self-test

- · Low Voltage Detect, Clock Monitor, and EPROM Parity Check Status

- Transducer Hermetically Sealed at Wafer Level for Superior Reliability

- · Robust Design, High Shocks Survivability

- Pb-Free Termination

- Environmentally Preferred Package

- Qualified AEC-Q100, Rev. F Grade 2 (-40°C/+105°C)

#### **Typical Applications**

- · Vibration Monitoring and Recording

- Dynamic Suspension Control

| ORDERING INFORMATION |                   |          |                      |  |

|----------------------|-------------------|----------|----------------------|--|

| Device Name          | Temperature Range | Case No. | Package              |  |

| MMA2240EG            | –40° to 85°C      | 475-01   | SOIC-16              |  |

| MMA2240EGR2          | –40° to 85°C      | 475-01   | SOIC-16, Tape & Reel |  |

| MMA2240KEG*          | –40° to 85°C      | 475-01   | SOIC-16              |  |

| MMA2240KEGR2*        | −40° to 85°C      | 475-01   | SOIC-16, Tape & Reel |  |

<sup>\*</sup>Part number sourced from a different facility.

#### $V_{DD}$ Temp G-Cell Integrator Gain Filter $V_{OUT}$ Comp Sensor ST Control Logic & Clock Oscillator Self-test EPROM Trim Circuits Generator $V_{SS}$ **STATUS** Figure 1. Simplified Accelerometer Functional Block Diagram

# MMA2240KEG

MMA2240KEG: X-AXIS SENSITIVITY

MICROMACHINED

ACCELEROMETER

±7g

KEG SUFFIX (Pb-FREE) 16-LEAD SOIC CASE 475-01

The block diagram of the MMA2240EG is shown in Figure 1. The X-axis g-cell is constructed using surface micromachining; and the interface IC is fabricated in a 1.2 micron (60%) silicon gate CMOS process.

The signal conditioning of the accelerometer channel begins with a capacitance to voltage conversion (C to V) followed by a 2-stage switched capacitor amplifier. This 2-stage amplifier has adjustable offset and gain trimming. The offset and gain of the interface IC can be controlled by the serially accessed EPROM trimming register.

Following the 2-stage amplifier the signal passes through a 2-pole, switched capacitor filter with a Bessel characteristic. The rolloff frequency of the filter is trimmed by adjusting the frequency of the single on-chip oscillator. The frequency is adjusted by trimming the bias current to the oscillator using the EPROM trim register.

The output of the filter is then amplified by the output stage which also has a temperature compensation circuit for sensitivity which can be adjusted using the EPROM trim register.

An adjustable self-test voltage to be applied to the electrostatic deflection plate in the sensing element. Other support circuits include a bandgap voltage reference for the bias sources and the self-test voltage. The interface IC also has its own power supply filter which feeds all the analog functions in order to increase the power supply rejection ratio (PSRR)

Included are several fault checks for low voltage detect (LVD), clock and/or bias monitoring, and a check of the stored "even" parity of the EPROM trim register. Failure of any of these monitoring functions will result in the STATUS input being driven high.

**Table 1. Maximum Ratings**

(Maximum ratings are the limits to which the device can be exposed without causing permanent damage.)

| Rating                                                                       | Symbol                    | Value                             | Unit |

|------------------------------------------------------------------------------|---------------------------|-----------------------------------|------|

| Unpowered Acceleration (all axes) <sup>(1)</sup>                             | 9 <sub>shock</sub>        | 2000<br>0.5 ms duration           | g    |

| In use g shocks powered or unpowered Capable of < 5 ppm device failure rate  | G <sub>shock in use</sub> | < 100<br>any duration             | g    |

| In use g shocks powered or unpowered Capable of < 50 ppm device failure rate | G <sub>shock in use</sub> | < 100 - 1500<br>≤ 0.6 ms duration | g    |

| Supply Voltage                                                               | V <sub>DD</sub>           | -0.3 to +7.0                      | V    |

| Storage Temperature Range                                                    | T <sub>stg</sub>          | -40 to +125                       | °C   |

This device is sensitive to mechanical shock. Improper handling can cause permanent damage of the part or cause the part to otherwise fail.

# **ELECTRO STATIC DISCHARGE (ESD)**

# WARNING: This device is sensitive to electrostatic discharge.

Although the Freescale accelerometers contain internal 2kV ESD protection circuitry, extra precaution must be taken by the user to protect the chip from ESD. A charge of over 2000 volts can accumulate on the human body or associated test equipment. A charge of this magnitude can alter the

performance or cause failure of the chip. When handling the accelerometer, proper ESD precautions should be followed to avoid exposing the device to discharges which may be detrimental to its performance.

# **Table 2. Operating Characteristics**

(Unless otherwise noted:  $-40^{\circ}\text{C} \le T_{\text{A}} \le +85^{\circ}\text{C}$ ,  $4.75 \le V_{\text{DD}} \le 5.25$ , Acceleration = 0g, Loaded output.<sup>(1)</sup>)

| Characteristic                                                           | Symbol             | Min                   | Тур                  | Max                   | Unit   |

|--------------------------------------------------------------------------|--------------------|-----------------------|----------------------|-----------------------|--------|

| Operating Range <sup>(2)</sup>                                           |                    |                       |                      |                       |        |

| Supply Voltage <sup>(3)</sup>                                            | $V_{DD}$           | 4.75                  | 5.00                 | 5.25                  | V      |

| Supply Current                                                           | I <sub>DD</sub>    | 4.0                   | 5.0                  | 6.0                   | mA     |

| Operating Temperature Range                                              | T <sub>A</sub>     | -40                   | _                    | +85                   | С      |

| Acceleration Range                                                       | 9 <sub>FS</sub>    | _                     | 7                    | _                     | g      |

| Output Signal                                                            |                    |                       |                      |                       |        |

| Zero-g ( $T_A = 25^{\circ}C$ , $V_{DD} = 5.0 \text{ V}$ ) <sup>(4)</sup> | V <sub>OFF</sub>   | 2.300                 | 2.500                | 2.700                 | V      |

| Zero-g                                                                   | $V_{OFF,V}$        | 0.44 V <sub>D</sub>   | 0.50 V <sub>DD</sub> | 0.56 V <sub>DD</sub>  | V      |

| Sensitivity $(T_A = 25^{\circ}C, V_{DD} = 5.0 \text{ V})^{(5)}$          | S                  | 285.0                 | 300.0                | 315.0                 | mV/g   |

| Sensitivity                                                              | S <sub>V</sub>     | 55.8                  | 60.0                 | 64.2                  | mV/g/V |

| Bandwidth Response                                                       | f_3dB              | 360                   | 400                  | 440                   | Hz     |

| Nonlinearity                                                             | NL <sub>OUT</sub>  | -1.0                  | _                    | +1.0                  | % FSO  |

| Noise                                                                    |                    |                       |                      |                       |        |

| RMS (10 Hz – 1 kHz)                                                      | n <sub>RMS</sub>   | _                     | 3.5                  | _                     | mVrms  |

| Self-Test                                                                |                    |                       |                      |                       |        |

| Output Response                                                          | $V_{ST}$           | 0.45                  | 0.60                 | 0.75                  | V      |

| Input Low                                                                | $V_{IL}$           | $V_{SS}$              | _                    | 0.3 x V <sub>DD</sub> | V      |

| Input High                                                               | V <sub>IH</sub>    | 0.7 x V <sub>DD</sub> | _                    | $V_{DD}$              | V      |

| Input Loading <sup>(6)</sup>                                             | I <sub>IN</sub>    | -30                   | -100                 | -300                  | μΑ     |

| Response Time <sup>(7)</sup>                                             | t <sub>ST</sub>    | _                     | 2.0                  | 10                    | ms     |

| Status <sup>(8), (9)</sup>                                               |                    |                       |                      |                       |        |

| Output Low (I <sub>load</sub> = 100 μA)                                  | $V_{OL}$           | _                     | _                    | 0.4                   | V      |

| Output High (I <sub>load</sub> = 100 μA)                                 | V <sub>OH</sub>    | V <sub>DD</sub> −0.8  | _                    | _                     | V      |

| Minimum Supply Voltage (LVD Trip)                                        | V <sub>LVD</sub>   | 2.7                   | 3.25                 | 4.0                   | V      |

| Clock Monitor Fail Detection Frequency                                   | f <sub>min</sub>   | 150                   | _                    | 400                   | kHz    |

| Output Stage Performance                                                 |                    |                       |                      |                       |        |

| Electrical Saturation Recovery Time <sup>(10)</sup>                      | t <sub>DELAY</sub> | _                     | 0.2                  | _                     | ms     |

| Full Scale Output Range (I <sub>OUT</sub> = 200 μA)                      | $V_{FSO}$          | 0.25                  | _                    | V <sub>DD</sub> −0.25 | V      |

| Capacitive Load Drive <sup>(11)</sup>                                    | C <sub>L</sub>     | _                     | _                    | 100                   | pF     |

| Output Impedance                                                         | Z <sub>O</sub>     | _                     | 300                  | _                     | Ω      |

| Mechanical Characteristics                                               |                    |                       |                      |                       |        |

| Transverse Sensitivity <sup>(12)</sup>                                   | $V_{XZ,YZ}$        | _                     | _                    | 5.0                   | % FSO  |

| Package Resonance                                                        | f <sub>PKG</sub>   | _                     | 10                   | _                     | kHz    |

- 1. For a loaded output the measurements are observed after an RC filter consisting of a 1  $k\Omega$  resistor and a 0.01  $\mu$ F capacitor to ground.

- 2. These limits define the range of operation for which the part will meet specification.

- 3. Within the supply range of 4.75 V and 5.25 V, the device operates as a fully calibrated linear accelerometer. Beyond these supply limits the device may operate as a linear device but is not guaranteed to be in calibration.

- 4. The device can measure both + and acceleration. With no input acceleration the output is at midsupply. For positive acceleration the output will increase above  $V_{DD}/2$  and for negative acceleration the output will decrease below  $V_{DD}/2$ .

- 5. The device is calibrated at 5g.

- 6. The digital input pin has an internal pull-down current source to prevent inadvertent self test initiation due to external board level leakages.

- 7. Time for the output to reach 90% of its final value after a self-test is initiated.

- 8. The Status pin output is not valid following power-up until at least one rising edge has been applied to the self-test pin. The Status pin is high whenever the self-test input is high, as a means to check the connectivity of the self-test and Status pins in the application.

- 9. The Status pin output latches high if a Low Voltage Detection or Clock Frequency failure occurs, or the EPROM parity changes to odd. The Status pin can be reset low if the self-test pin is pulsed with a high input for at least 100 μs, unless a fault condition continues to exist.

- 10. Time for amplifiers to recover after an acceleration signal causing them to saturate.

- 11. Preserves phase margin (60°) to guarantee output amplifier stability.

- 12. A measure of the device's ability to reject an acceleration applied 90° from the true axis of sensitivity.

#### PRINCIPLE OF OPERATION

The Freescale accelerometer is a surface-micromachined integrated-circuit accelerometer.

The device consists of a surface micromachined capacitive sensing cell (g-cell) and a CMOS signal conditioning ASIC contained in a single integrated circuit package. The sensing element is sealed hermetically at the wafer level using a bulk micromachined "cap" wafer.

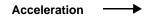

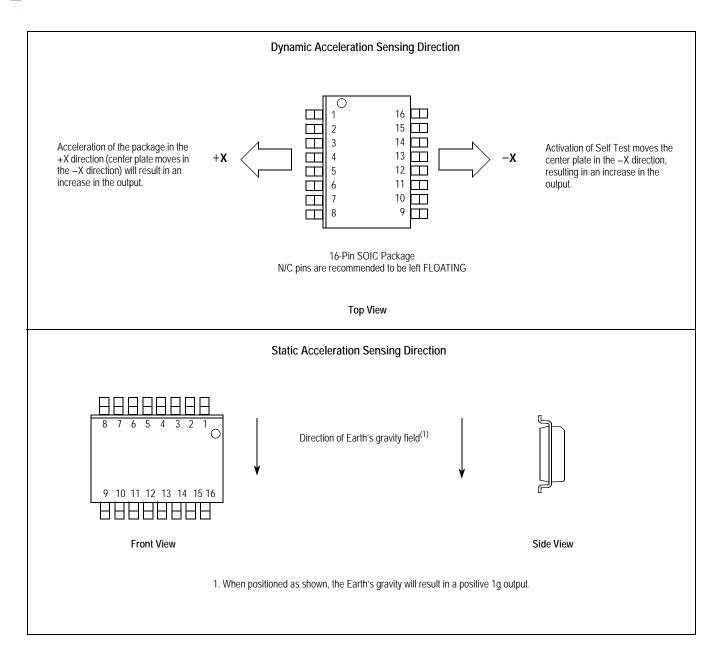

The g-cell is a mechanical structure formed from semiconductor materials (polysilicon) using semiconductor processes (masking and etching). It can be modeled as a set of beams attached to a movable central mass that moves between fixed beams. The movable beams can be deflected from their rest position by subjecting the system to an acceleration (Figure 3).

When the beams attached to the center mass move, the distance from them to the fixed beams on one side will increase by the same amount that the distance to the fixed beams on the other side decreases. The change in distance is a measure of acceleration.

The g-cell beams form two back-to-back capacitors (Figure 3). As the center plate moves with acceleration, the distance between the beams change and each capacitor's value will change, (C = NA $\epsilon$ /D). Where A is the area of the facing side of the beam,  $\epsilon$  is the dielectric constant, and D is the distance between the beams, and N is the number of beams.

The CMOS ASIC uses switched capacitor techniques to measure the g-cell capacitors and extract the acceleration data from the difference between the two capacitors. The ASIC also signal conditions and filters (switched capacitor) the signal, providing a high level output voltage that is ratiometric and proportional to acceleration.

Figure 3. Simplified Transducer Physical Model

#### **SPECIAL FEATURES**

# **Filtering**

The Freescale accelerometers contain an onboard 2-pole switched capacitor filter. A Bessel implementation is used because it provides a maximally flat delay response (linear phase) thus preserving pulse shape integrity. Because the filter is realized using switched capacitor techniques, there is no requirement for external passive components (resistors and capacitors) to set the cut-off frequency.

#### Self-Test

The sensor provides a self-test feature that allows the verification of the mechanical and electrical integrity of the accelerometer at any time before or after installation. This feature is critical in applications such as automotive airbag systems where system integrity must be ensured over the life of the vehicle. A fourth "plate" is used in the g-cell as a self-test plate. When the user applies a logic high input to the self-test pin, a calibrated potential is applied across the self-test plate and the moveable plate. The resulting electrostatic force (Fe =  $^{1}$ /<sub>2</sub> AV $^{2}$ /d $^{2}$ ) causes the center plate to deflect. The resultant deflection is measured by the accelerometer's control ASIC and a proportional output voltage results. This procedure assures that both the mechanical (g-cell) and electronic sections of the accelerometer are functioning.

#### Ratiometricity

Ratiometricity simply means that the output offset voltage and sensitivity will scale linearly with applied supply voltage. That is, as you increase supply voltage the sensitivity and offset increase linearly; as supply voltage decreases, offset and sensitivity decrease linearly. This is a key feature when interfacing to a microcontroller or an A/D converter because it provides system level cancellation of supply induced errors in the analog to digital conversion process.

#### **Status**

Freescale accelerometers include fault detection circuitry and a fault latch. The Status pin is an output from the fault latch, OR'd with self-test, and is set high whenever one (or more) of the following events occur:

- Supply voltage falls below the Low Voltage Detect (LVD) voltage threshold

- Clock oscillator falls below the clock monitor minimum frequency

- Parity of the EPROM bits becomes odd in number.

The fault latch can be reset by a falling edge on the selftest input pin, unless one (or more) of the fault conditions continues to exist.

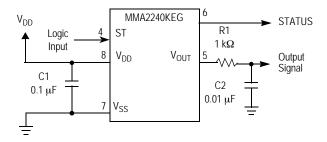

# **BASIC CONNECTIONS**

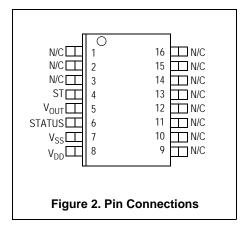

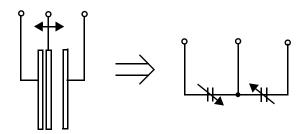

# **Pinout Description**

**Table 3. Pin Descriptions**

| Pin No.    | Pin Name         | Description                                 |

|------------|------------------|---------------------------------------------|

| 1 thru 3   | _                | No internal connection. Leave unconnected.  |

| 4          | ST               | Logic input pin used to initiate self-test. |

| 5          | V <sub>OUT</sub> | Output voltage of the accelerometer.        |

| 6          | STATUS           | Logic output pin to indicate fault.         |

| 7          | V <sub>SS</sub>  | The power supply ground.                    |

| 8          | $V_{DD}$         | The power supply input.                     |

| 9 thru 13  | Trim pins        | Used for factory trim. Leave unconnected.   |

| 14 thru 16 | _                | No internal connection. Leave unconnected.  |

Figure 4. SOIC Accelerometer with Recommended Terminations

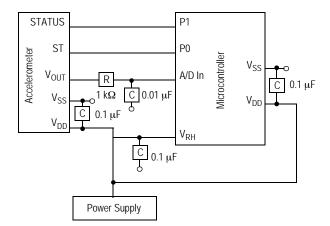

# **PCB Layout**

Figure 5. Recommended PCB Layout for Interfacing Accelerometer to Microcontroller

#### NOTES

- 1. Use a 0.1  $\mu\text{F}$  capacitor on  $V_{DD}$  to decouple the power source.

- 2. Physical coupling distance of the accelerometer to the microcontroller should be minimal.

- 3. Place a ground plane beneath the accelerometer to reduce noise, the ground plane should be attached to all of the open ended terminals shown in Figure 5.

- 4. Use an RC filter of 1 k $\Omega$  and 0.01  $\mu$ F on the output of the accelerometer to minimize clock noise (from the switched capacitor filter circuit).

- 5. PCB layout of power and ground should not couple power supply noise.

- 6. Accelerometer and microcontroller should not be a high current path.

- 7. A/D sampling rate and any external power supply switching frequency should be selected such that they do not interfere with the internal accelerometer sampling frequency. This will prevent aliasing errors.

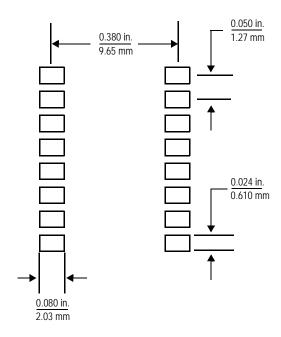

# MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the surface mount packages must be the correct size to ensure proper solder connection interface between the board and the package. With the correct

footprint, the packages will self-align when subjected to a solder reflow process. It is always recommended to design boards with a solder mask layer to avoid bridging and shorting between solder pads.

Figure 6. Footprint SOIC-16 (Case 475-01)

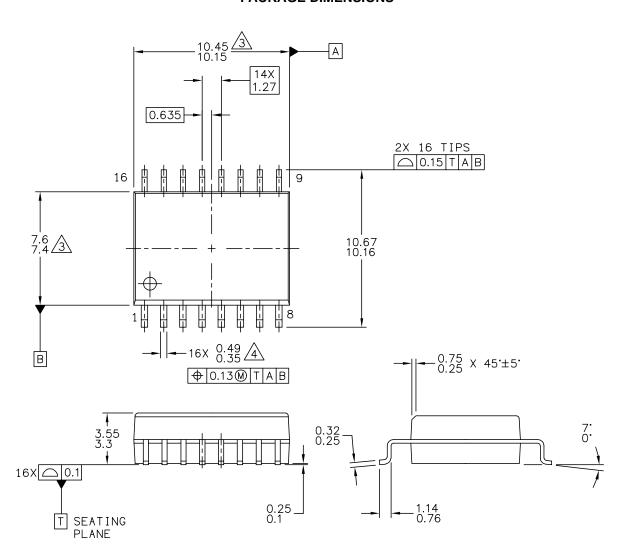

# **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | AL OUTLINE               | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------|-----------|--------------------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO: 98ASB16926C |                  | REV: C      |

| 16 LEAD SOIC                                            |           | CASE NUMBER              | R: 475–01        | 17 MAR 2005 |

| //CCELETIONETE                                          |           | STANDARD: NO             | N-JEDEC          |             |

PAGE 1 OF 2

CASE 475-01 ISSUE C 16-LEAD SOIC

# **PACKAGE DIMENSIONS**

# NOTES:

- 1. ALL DIMENSONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15 PER SIDE.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION.

PROTRUSIONS SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.75

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ASB16926C   | REV: C      |

| 16 LEAD SOIC<br>ACCELEROMETER                        |           | CASE NUMBER  | R: 475–01        | 17 MAR 2005 |

| //OOLLLINGWILTEN                                     | •         | STANDARD: NO | N-JEDEC          |             |

PAGE 2 OF 2

**CASE 475-01 ISSUE C 16-LEAD SOIC**

MMA2240KEG

9

#### How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

# Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

# For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life. or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2009. All rights reserved.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.