### **General Description**

The MAX4952B dual-channel redriver is designed to redrive one full lane of SAS or SATA signals up to 6.0Gbps and operates from a single +3.3V supply. The MAX4952B is designed for commercial SAS or SAS/SATA applications, such as servers.

The MAX4952B features independent output boost and enhances signal integrity at the receiver by re-establishing full output levels. SAS/SATA out-of-band (OOB) signaling is supported using high-speed amplitude detection on the inputs and squelch on the corresponding outputs.

Inputs and outputs are all terminated in  $50\Omega$  internally and exhibit excellent return loss.

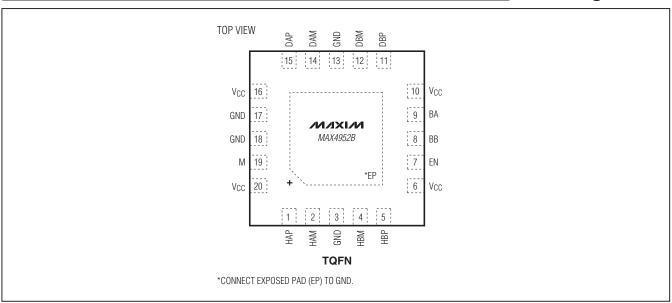

The MAX4952B is available in a small, 20-pin, 4.0mm x 4.0mm TQFN package with flow-through traces for ease of layout. This device is specified over the 0°C to +70°C operating temperature range.

**Applications**

Servers

Data Storage

## **Features**

- ♦ Single +3.3V Supply Operation

- ♦ Low Power-Down Current (350µA typ) for Power-**Sensitive Applications**

- **♦** Supports SAS I/II/III ≤ 6.0Gbps

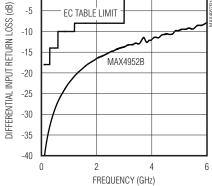

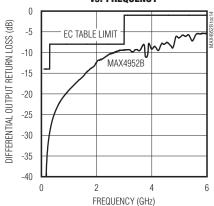

- **♦ Excellent Return Loss Exceeds SAS/SATA Return Loss Mask (Better** Than 8dB Up to 3GHz)

- Supports SAS/SATA OOB-Level Signaling **Very Fast Entry and Exit Time of 5ns (Max) Programmable SAS/SATA Threshold**

- ◆ Independent Output-Boost Selection Two Levels: 0dB, 6dB

- ♦ On-Chip 50Ω Input/Output Terminations

- ♦ In-Line Signal Traces for Flow-Through Layout

- ♦ Space-Saving, 4.0mm x 4.0mm TQFN Package

- ♦ ESD Protection on All Pins: ±5.5kV (Human Body Model)

## **Ordering Information**

| PART         | TEMP RANGE   | PIN-PACKAGE |  |  |

|--------------|--------------|-------------|--|--|

| MAX4952BCTP+ | 0°C to +70°C | 20 TQFN-EP* |  |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>EP = Exposed Pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)    |                      |

|--------------------------------------|----------------------|

| Vcc                                  | 0.3V to +4.0V        |

| All Other Pins (Note 1)              | 0.3V to (VCC + 0.3V) |

| Short-Circuit Output Current DAP, DA | M, HBM, HBP90mA      |

| Continuous Power Dissipation (TA = - | +70°C)               |

| 20-Pin TQFN (derate 25.6mW/°C at     | oove +70°C)2051mW    |

| Junction-to-Case Thermal Resistance  | (θJC) (Note 2)       |

| 20-Pin TQFN                          | 6°C/W                |

| Junction-to-Ambient Thermal Resistance | ce (θJA) (Note 2) |

|----------------------------------------|-------------------|

| 20-Pin TQFN                            | 39°C/W            |

| Operating Temperature Range            | 0°C to +70°C      |

| Junction Temperature                   | +150°C            |

| Storage Temperature Range              | 55°C to +150°C    |

| Lead Temperature (soldering, 10s)      | +300°C            |

|                                        |                   |

- Note 1: All I/O pins are clamped by internal diodes.

- **Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maxim-ic.com/thermal-tutorial**.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, C_{CL} = 10 \text{nF coupling capacitor on each output}, R_L = 50\Omega \text{ on each output}, T_A = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25^{\circ}\text{C}$ .) (Note 3)

| PARAMETER                       | SYMBOL                 | CONE                | OITIONS       | MIN | TYP  | MAX | UNITS |  |

|---------------------------------|------------------------|---------------------|---------------|-----|------|-----|-------|--|

| DC PERFORMANCE                  | •                      |                     |               | •   |      |     |       |  |

| Power-Supply Range              | Vcc                    |                     |               | 3.0 |      | 3.6 | V     |  |

| Power-Down Current              | IPWRDN                 | EN = GND            |               |     | 0.35 | 2   | mA    |  |

| Cupaly Current                  | loo                    | E                   | BA = BB = VCC |     | 100  | 130 |       |  |

| Supply Current                  | Icc                    | EN = VCC            | BA = BB = GND |     | 85   | 100 | - mA  |  |

| Input Impedance, Differential   | Z <sub>RX-DIFF</sub> - | DC                  |               | 85  | 100  | 115 | Ω     |  |

| Output Impedance, Differential  | Z <sub>TX-DIFF-</sub>  | DC                  |               | 85  | 100  | 115 | Ω     |  |

| AC PERFORMANCE                  |                        |                     |               |     |      |     |       |  |

|                                 | RL <sub>RX-DIFF</sub>  | 0.1GHz < f ≤ 0.3GHz | 7-            |     |      | -18 | -18   |  |

|                                 |                        | 0.3GHz < f ≤ 0.6GHz | 2             |     |      | -14 |       |  |

| Input Return Loss, Differential |                        | 0.6GHz < f ≤ 1.2GHz | 7             |     |      | -10 | dB    |  |

| (Note 4)                        | I I LEXT-DIFF          | 1.2GHz < f ≤ 2.4GHz | 2             |     |      | -8  |       |  |

|                                 |                        | 2.4GHz < f ≤ 3.0GHz | 2             |     |      | -8  |       |  |

|                                 |                        | 3.0GHz < f ≤ 6.0GHz | 2             |     |      | -1  |       |  |

|                                 | Di py ou               | 0.1GHz < f ≤ 0.3GHz | 2             |     |      | -6  |       |  |

|                                 |                        | 0.3GHz < f ≤ 0.6GHz | 7-            |     |      | -5  |       |  |

| Input Return Loss,              |                        | 0.6GHz < f ≤ 1.2GHz | 2             |     |      | -5  | dB    |  |

| Common Mode (Note 4)            | RLRX-CM                | 1.2GHz < f ≤ 2.4GHz | 7             | -5  |      | -5  |       |  |

|                                 |                        | 2.4GHz < f ≤ 3.0GHz | 7             |     |      | -5  |       |  |

|                                 |                        | 3.0GHz < f ≤ 6.0GHz | 7             |     |      | -1  | ]     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, C_{CL} = 10 \text{nF coupling capacitor on each output}, R_L = 50 \Omega$  on each output,  $T_A = 0 ^{\circ}\text{C}$  to  $+70 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ .) (Note 3)

| PARAMETER                        | SYMBOL                | CONDITIONS                                                    | MIN | TYP | MAX  | UNITS             |  |

|----------------------------------|-----------------------|---------------------------------------------------------------|-----|-----|------|-------------------|--|

|                                  |                       | 0.1GHz < f ≤ 0.3GHz                                           |     |     | -14  |                   |  |

|                                  |                       | 0.3GHz < f ≤ 0.6GHz                                           |     |     | -8   | -8                |  |

| Output Return Loss, Differential |                       | 0.6GHz < f ≤ 1.2GHz                                           |     |     | -8   |                   |  |

| (Note 4)                         | RLTX-DIFF             | 1.2GHz < f ≤ 2.4GHz                                           |     |     | -8   | dB                |  |

|                                  |                       | 2.4GHz < f ≤ 3.0GHz                                           |     |     | -8   |                   |  |

|                                  |                       | 3.0GHz < f ≤ 6.0GHz                                           |     |     | -1   |                   |  |

|                                  |                       | 0.1GHz < f ≤ 0.3GHz                                           |     |     | -8   |                   |  |

|                                  |                       | 0.3GHz < f ≤ 0.6GHz                                           |     |     | -5   | 1                 |  |

| Output Return Loss,              | DI                    | 0.6GHz < f ≤ 1.2GHz                                           |     |     | -5   | -10               |  |

| Common Mode (Note 4)             | RLTX-CM               | 1.2GHz < f ≤ 2.4GHz                                           |     |     | -5   | dB                |  |

|                                  |                       | 2.4GHz < f ≤ 3.0GHz                                           |     |     | -5   |                   |  |

|                                  |                       | 3.0GHz < f ≤ 6.0GHz                                           |     |     | -1   |                   |  |

|                                  |                       | SATA 1.5Gbps, 3Gbps, 6Gbps, M = GND                           | 225 |     | 1600 |                   |  |

| Differential Input Signal Range  | VRX-DFF-PP            | SAS 1.5Gbps, 3Gbps, M = VCC                                   | 275 |     | 1600 | mV <sub>P-P</sub> |  |

|                                  |                       | SAS 6.0Gbps, M = V <sub>CC</sub>                              | 300 |     | 1600 |                   |  |

|                                  | V <sub>SQ-DIFF</sub>  | SATA OOB, M = GND                                             | 50  |     | 150  |                   |  |

| OOB Squelch Threshold            |                       | SAS OOB, M = VCC                                              | 120 |     | 220  | mV <sub>P-P</sub> |  |

| Differential Output-Voltage      | 1,7                   | f = 750MHz, 1.5GHz BA = BB = GND BA = BB = VCC                | 450 |     | 650  | mV <sub>P-P</sub> |  |

| Swing                            | VTX-DIFF-PP           |                                                               | 900 |     | 1300 |                   |  |

| Propagation Delay                | tpD                   |                                                               |     | 300 |      | ps                |  |

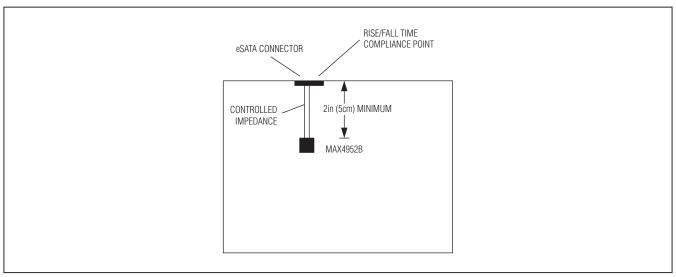

| Output Rise/Fall Time            | ttx-rise-<br>Fall     | Figure 1 (Notes 4, 5)                                         | 40  |     | 40   | ps                |  |

| Deterministic Jitter             | t <sub>TX-DJ-DD</sub> | Up to 6.0Gbps (Notes 4, 6)                                    |     |     | 15   | psp-p             |  |

| Random Jitter                    | ttx-rj-dd             | Up to 6.0Gbps (Notes 4, 6)                                    |     |     | 1.4  | psrms             |  |

| OOB Output Startup/Shutdown Time | toob                  | (Note 7)                                                      |     | 3   | 5    | ns                |  |

| Differential Offset Delta        | ΔVOOB,DIFF            | Difference between OOB and active-mode output offset          | -80 |     | +80  | mV                |  |

| Common-Mode Delta                | ΔV <sub>OOB</sub> ,CM | Difference between OOB and active-mode output V <sub>CM</sub> | -50 |     | +50  | mV                |  |

| CONTROL LOGIC                    |                       | ,                                                             |     |     |      |                   |  |

| Input Logic-Level Low            | VIL                   |                                                               |     |     | 0.6  | V                 |  |

| Input Logic-Level High           | VIH                   |                                                               | 1.4 |     |      | V                 |  |

| Input Logic Hysteresis           | VHYST                 |                                                               |     | 100 |      | mV                |  |

| Input Pulldown Resistor          | RDOWN                 |                                                               |     | 70  |      | kΩ                |  |

| ESD PROTECTION                   |                       |                                                               |     |     |      |                   |  |

| LOD PROTECTION                   |                       |                                                               |     |     |      |                   |  |

Note 3: This device is 100% production tested at  $T_A = +70$ °C. Specifications for all temperature limits are guaranteed by design.

Note 4: Guaranteed by design.

Note 5: Rise and fall times are measured using 20% and 80% levels.

Note 6: DJ measured using K28.5 pattern; RJ measured using D10.2 pattern.

Note 7: Total time for OOB detection circuit to enable/squelch the output.

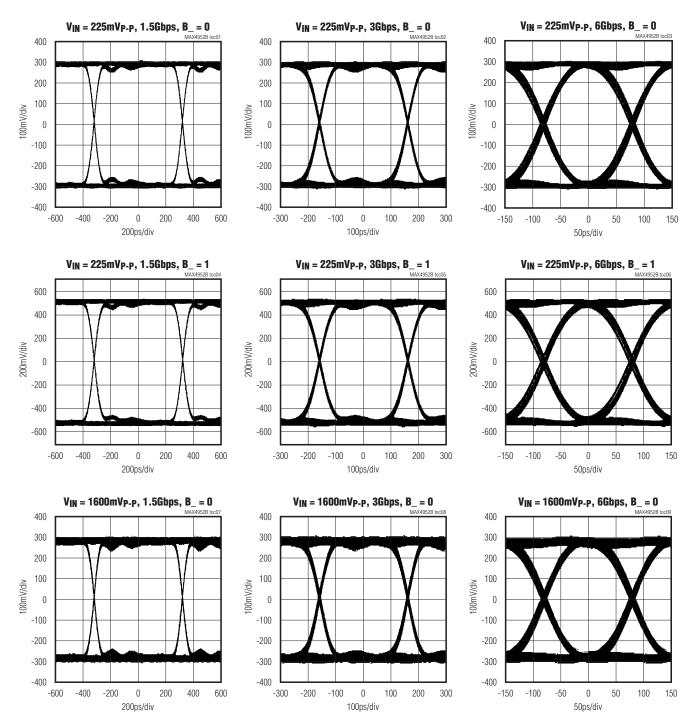

## **Typical Operating Characteristics**

(VCC = +3.3V, M = GND, TA = +25°C; all eye diagrams measured using K28.5 pattern, unless otherwise noted.)

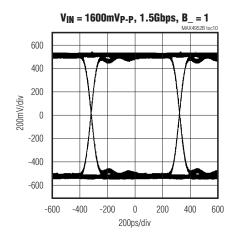

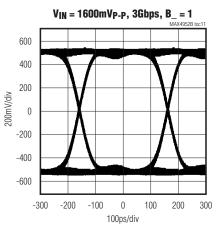

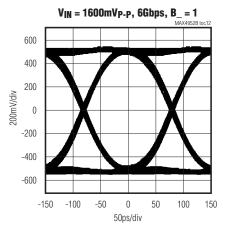

## **Typical Operating Characteristics (continued)**

(VCC = +3.3V, M = GND, TA = +25°C; all eye diagrams measured using K28.5 pattern, unless otherwise noted.)

**DIFFERENTIAL INPUT RETURN LOSS**

#### **DIFFERENTIAL OUTPUT RETURN LOSS** vs. FREQUENCY

## **Pin Configuration**

## **Pin Description**

| PIN              | NAME | FUNCTION                                                                                                                                                                                          |

|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | HAP  | Noninverting Input from Host Channel A. HAP must be capacitively coupled (see note).                                                                                                              |

| 2                | HAM  | Inverting Input from Host Channel A. HAM must be capacitively coupled (see note).                                                                                                                 |

| 3, 13, 17, 18    | GND  | Ground                                                                                                                                                                                            |

| 4                | HBM  | Inverting Output to Host Channel B. HBM must be capacitively coupled (see note).                                                                                                                  |

| 5                | HBP  | Noninverting Output to Host Channel B. HBP must be capacitively coupled (see note).                                                                                                               |

| 6, 10, 16, 20    | Vcc  | Power-Supply Input. Bypass V <sub>CC</sub> to GND with low-ESR 0.01µF and 4.7µF capacitors in parallel as close to the device as possible; recommended for each V <sub>CC</sub> pin.              |

| 7                | EN   | Enable Input. Drive EN low for low-power standby mode. Drive EN high for normal operation. EN is internally pulled down by a $70k\Omega$ (typ) resistor.                                          |

| 8 BB 9 BA 11 DBP |      | Channel B Boost-Enable Input. Drive BB high to enable channel B +6dB output boost. Drive BB low for standard SAS/SATA output level. BB is internally pulled down by a $70k\Omega$ (typ) resistor. |

|                  |      | Channel A Boost-Enable Input. Drive BA high to enable channel A +6dB output boost. Drive BA low for standard SAS/SATA output level. BA is internally pulled down by a $70k\Omega$ (typ) resistor. |

|                  |      | Noninverting Input from Device Channel B. DBP must be capacitively coupled (see note).                                                                                                            |

| 12               | DBM  | Inverting Input from Device Channel B. DBM must be capacitively coupled (see note).                                                                                                               |

| 14               | DAM  | Inverting Output to Device Channel A. DAM must be capacitively coupled (see note).                                                                                                                |

| 15               | DAP  | Noninverting Output to Device Channel A. DAP must be capacatively coupled (see note).                                                                                                             |

|                  |      | OOB-Mode Logic Input. M is internally pulled down by a $70k\Omega$ (typ) resistor. Drive M low or leave unconnected for SATA OOB threshold. Drive M high for SAS OOB threshold.                   |

| _                | EP   | Exposed Pad. Internally connected to GND. Connect to a large ground plane for proper thermal and electrical operation. Not intended as an electrical connection point.                            |

**Note:** For proper operation, Maxim recommends the use of low-ESR, X7R, 10nF, 0402-sized capacitors for all redriver inputs and outputs.

Figure 1. Circuit for Measuring t<sub>R/F</sub> for MAX4952B (refer to the SATA specifications for compliance measurement)

#

## Functional Diagram/Truth Table

| EN | ВА | ВВ | CHANNEL A OUTPUT LEVEL | CHANNEL B<br>OUTPUT LEVEL |

|----|----|----|------------------------|---------------------------|

| 0  | X  | X  | Power-Down             | Power-Down                |

| 1  | 0  | 0  | No Boost               | No Boost                  |

| 1  | 0  | 1  | No Boost               | Boost                     |

| 1  | 1  | 0  | Boost                  | No Boost                  |

| 1  | 1  | 1  | Boost                  | Boost                     |

X = Don't care.

| М | OOB THRESHOLD |  |  |  |

|---|---------------|--|--|--|

| 0 | SATA          |  |  |  |

| 1 | SAS           |  |  |  |

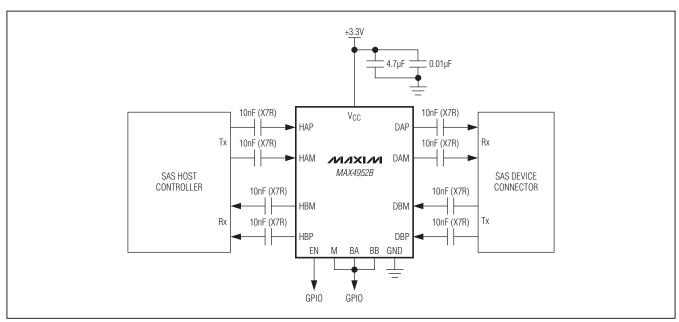

Figure 2. Typical Application Circuit

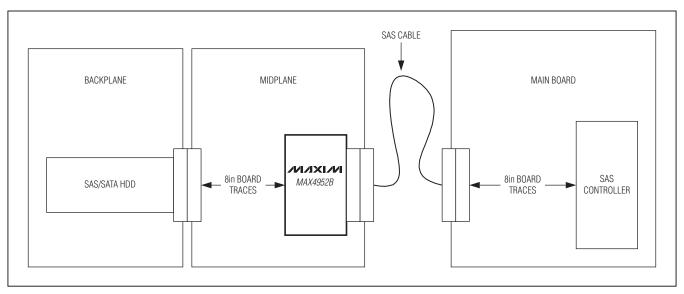

Figure 3. MAX4952B Driving a SAS Cable

## **Detailed Description**

The MAX4952B dual-channel redriver is designed to redrive one full lane of SAS/SATA signals up to 6.0Gbps while operating from a single +3.3V supply.

The MAX4952B features independent output boost and enhances signal integrity at the receiver by re-establishing full output levels. SAS/SATA OOB signaling is supported using high-speed amplitude detection on the inputs and squelch on the corresponding outputs.

#### **Input/Output Terminations**

Inputs and outputs are internally 50 $\Omega$  terminated to VCC (see the *Functional Diagram/Truth Table*) and must be AC-coupled using low-ESR, X7R, 10nF capacitors to the SAS/SATA controller IC and SAS/SATA device for proper operation.

#### Enable Input (EN)/Power-Down Mode

The MAX4952B features an active-high enable input, EN, which has an internal pulldown resistor of  $70k\Omega$  (typ). When EN is driven low or left unconnected, the MAX4952B enters power-down mode and squelches the output. Drive EN high for normal operation.

#### **SAS/SATA Mode Input (M)**

The MAX4952B supports both SAS and SATA OOB levels. When in SAS mode, the OOB threshold is 120mVP-P (min), and when in SATA mode, the OOB threshold is 50mVP-P (min). Signals below the OOB threshold are squelched to prevent unwanted noise from being redriven at the output. Drive M low or leave unconnected to set SATA OOB levels. Drive M high to set SAS OOB levels. See the *Functional Diagram/Truth Table*. M has an internal pulldown resistor of  $70\text{k}\Omega$  (typ).

#### **Output Boost-Selection Inputs (BA, BB)**

The MAX4952B has two digital control logic inputs, BA and BB. BA and BB have internal pulldown resistors of  $70k\Omega$  (typ). BA and BB control the boost level of their corresponding redrivers (see the *Functional Diagram/Truth Table*). Drive BA or BB low or leave unconnected for standard SAS/SATA output levels. Drive BA or BB high to boost the output.

### Applications Information

#### Layout

Circuit board layout and design can significantly affect the performance of the MAX4952B. Use good, high-frequency design techniques, including minimizing ground inductance and using controlled-impedance transmission lines on data signals. Place low-ESR 0.01µF and 4.7µF power-supply bypass capacitors in parallel as close to VCC as possible, or, as recommended, on each VCC pin. Always connect VCC to a power plane. The MAX4952B requires coupling capacitors for all redriver inputs and outputs. Maxim recommends high-quality, low-ESR, X7R, 10nF, 0402-sized capacitors.

#### **Exposed-Pad Package**

The exposed-pad, 20-pin TQFN package incorporates features that provide a very low-thermal resistance path for heat removal from the IC. The exposed pad on the MAX4952B must be soldered to the circuit board ground plane for proper thermal and electrical performance. For more information on exposed-pad packages, refer to Application Note 862: HFAN-08.1: Thermal Considerations of QFN and Other Exposed-Paddle Packages.

#### **ESD Protection**

As with all Maxim devices, ESD protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The MAX4952B is protected against ESD up to ±5.5kV (Human Body Model) without damage. The ESD structures withstand ±5.5kV in all states (normal operation and powered down). After an ESD event, the MAX4952B continues to function without latchup.

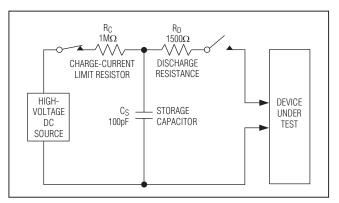

#### **Human Body Model**

The MAX4952B is characterized for  $\pm 5.5$ kV ESD protection using the Human Body Model (MIL-STD-883, Method 3015). Figure 4 shows the Human Body Model and Figure 5 shows the current waveform it generates when discharged into low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest that is then discharged into the device through a 1.5k $\Omega$  resistor.

#### **Power-Supply Sequencing**

Caution: Do not exceed the absolute maximum ratings because stresses beyond the listed ratings can cause permanent damage to the device.

Proper power-supply sequencing is recommended for all devices. Always apply GND then V<sub>CC</sub> before applying signals, especially if the signal is not current limited.

Figure 4. Human Body ESD Test Model

PROCESS: BICMOS

IP 100% 90% Ir (NOT DRAWN TO SCALE)

AMPS

36.8% TIME CURRENT WAVEFORM

Figure 5. Human Body Current Waveform

\_\_\_\_\_Chip Information

### \_Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO. |  |

|--------------|--------------|--------------|--|

| 20 TQFN-EP   | T2044+2      | 21-0139      |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX4952BCTP+ MAX4952BCTP+T