## Wired M-BUS Slave Transceiver

#### Description

The NCN5150 is a single-chip integrated slave transceiver for use in two-wire Meter Bus (M-BUS) slave devices and repeaters. The transceiver provides all of the functions needed to satisfy the European Standards EN 13757–2 and EN 1434–3 describing the physical layer requirements for M-BUS. It includes a programmable power level of up to 2 (SOIC version) or 6 (NQFP version) unit loads, which are available for use in external circuits through a 3.3 V LDO regulator.

The NCN5150 can provide communication up to the maximum M-BUS communication speed of 38,400 baud (half-duplex).

#### **Features**

- Single-chip MBUS Transceiver

- UART Communication Speeds Up to 38,400 baud

- Integrated 3.3 V VDD LDO Regulator with Extended Peak Current Capability of 15 mA

- Supports Powering Slave Device from the Bus or from External Power Supply

- Adjustable I/O Levels

- Adjustable Constant Current Sink up to 2 or 6 Unit Loads Depending on the Package

- Low Bus Voltage Operation

- Extended Current Budget for External Circuits: at least 0.88 mA

- Polarity Independent

- Power-Fail Function

- Fast Startup No External Transistor Required on STC Pin

- Industrial Ambient Temperature Range of -40°C to +85°C

- Available in:

- 16-pin SOIC (Pin-to-Pin Compatible with TSS721A)

- 20-pin QFN

- These are Pb-free Devices

## **Typical Applications**

- Multi-energy Utility Meters

- Water

- Gas

- ◆ Electricity

- Heating systems

#### Related Standards - European Standard

EN 13757-2, EN 1434-3

For more information visit www.m-bus.com

## ON Semiconductor®

www.onsemi.com

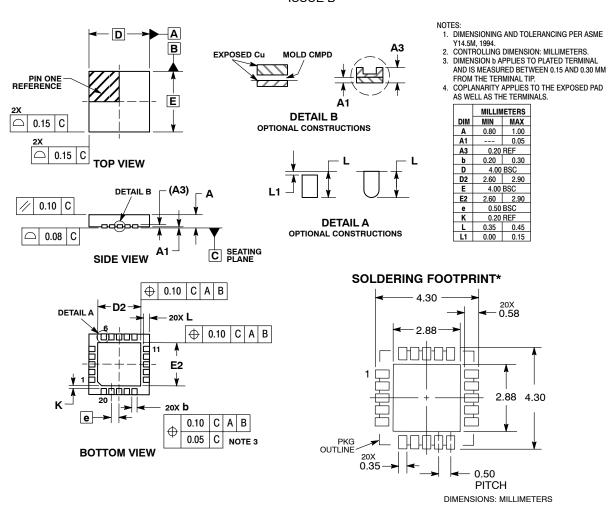

NQFP-20 MN SUFFIX CASE 485E SOIC-16 D SUFFIX CASE 751B

#### **MARKING DIAGRAMS**

NQFP-20

A = Assembly Location L = Wafer Lot (optional)

Y, YY = Year W, WW = Work Week G or • = Pb-free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

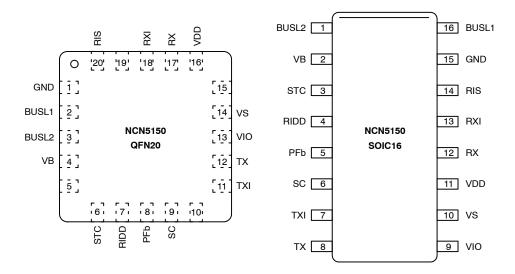

Figure 1. Pin Out NCN5150 in 20-pin NQFP and 16 Pin SOIC (Top View)

Table 1. NCN5150 PINOUT

|             |        |              | umber         |                                                                                                                                |

|-------------|--------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре   | NCN5150 SOIC | NCN5150 QFN   | Pin Description                                                                                                                |

| BUSL1       | Bus    | 16           | 2             | MBUS line. Connect to bus through 220 $\Omega$ series resistors.                                                               |

| BUSL2       | Bus    | 1            | 3             | Connections are polarity independent                                                                                           |

| VB          | Power  | 2            | 4             | Rectified bus voltage                                                                                                          |

| STC         | Output | 3            | 6             | Storage capacitor pin. Connect to bulk storage capacitor (minimum 10 $\mu$ F, maximum 330 $\mu$ F–2,700 $\mu$ F – see Table 9) |

| RIDD        | Input  | 4            | 7             | Mark current adjustment pin. Connect to programming resistor                                                                   |

| PFb         | Output | 5            | 8             | Power Fail, active low                                                                                                         |

| sc          | Output | 6            | 9             | Mark bus voltage level storage capacitor pin. Connect to ceramic capacitor (typically 220 nF)                                  |

| TXI         | Output | 7            | 11            | UART Data output (inverted)                                                                                                    |

| TX          | Output | 8            | 12            | UART Data output                                                                                                               |

| VIO         | Input  | 9            | 13            | I/O pins (RX, RXI, TX, TXI, PFb) high level voltage                                                                            |

| VS          | Output | 10           | 14            | Gate driver for PMOS switch between bus powered operation and external power supply                                            |

| VDD         | Power  | 11           | 16            | Voltage regulator output. Connect to minimum 1 µF decoupling capacitor                                                         |

| RX          | Input  | 12           | 17            | UART Data input                                                                                                                |

| RXI         | Input  | 13           | 18            | UART Data input (inverted)                                                                                                     |

| RIS         | Input  | 14           | 20            | Modulation current adjustment pin                                                                                              |

| GND         | Ground | 15           | 1             | Ground                                                                                                                         |

| NC          | NC     | -            | 5, 10, 15, 19 | Not connected pins. Tie to GND                                                                                                 |

| EP          | Ground | _            | EP            | Exposed Pad. Tie to GND                                                                                                        |

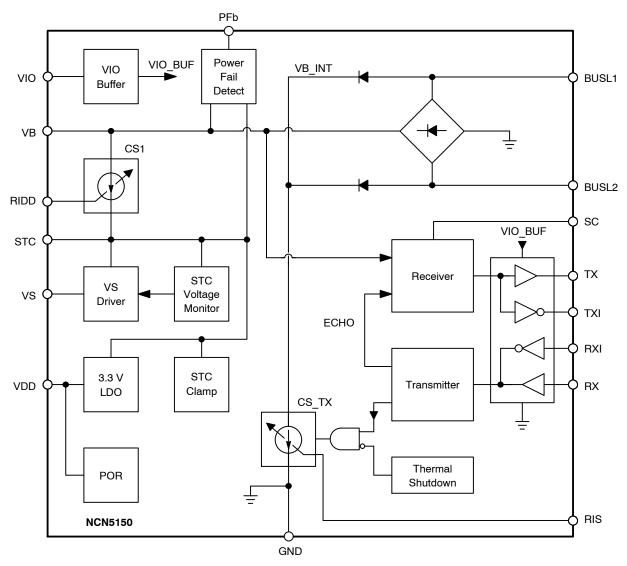

Figure 2. NCN5150 Block Diagram

Table 2. ABSOLUTE MAXIMUM RATINGS (Note 1)

| Symbol                          | Parameter                         | Min  | Max  | Unit |

|---------------------------------|-----------------------------------|------|------|------|

| $T_J$                           | Junction Temperature              | -40  | +150 | °C   |

| T <sub>S</sub>                  | Storage Temperature               | -55  | +150 | °C   |

| V <sub>BUS</sub>                | Bus Voltage ( BUSL1 - BUSL2 )     | -50  | 50   | V    |

| $V_{TX}, V_{TXI}$               | Voltage on Pin TX, TXI            | -0.3 | 7.5  | V    |

| $V_{RX}$ , $V_{RXI}$ , $V_{IO}$ | Voltage on Pin RX, RXI, VIO       | -0.3 | 5.5  | V    |

| ESD <sub>HBM</sub>              | ESD Rating - Human Body Model     | 4.0  | -    | kV   |

| ESD <sub>MM</sub>               | ESD Rating – Machine Model        | 250  | -    | V    |

| ESD <sub>CDM</sub>              | ESD Rating - Charged Device Model | 750  |      | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All voltages are referenced to GND.

**Table 3. THERMAL CHARACTERISTICS**

| Rating                                                                 | Symbol          | Typical Value | Unit |

|------------------------------------------------------------------------|-----------------|---------------|------|

| Thermal Characteristics, SOIC-16 - Thermal Resistance, Junction-to-Air | $R_{\theta JA}$ | 125           | °C/W |

| Thermal Characteristics, QFN-20 - Thermal Resistance, Junction-to-Air  | $R_{\theta JA}$ | 42            | °C/W |

NOTE:  $R_{\theta JA}$  obtained with 1S0P (SOIC) or 2S2P (QFN) test boards according to  $\overline{\text{JEDEC JESD51}}$  standard.

Table 4. RECOMMENDED OPERATING CONDITIONS (Notes 2 and 3)

| Symbol           | Parameter                                               |                | Min | Max | Unit |

|------------------|---------------------------------------------------------|----------------|-----|-----|------|

| T <sub>A</sub>   | Ambient Temperature                                     |                | -40 | +85 | °C   |

| V <sub>BUS</sub> | Bus Voltage ( V <sub>BUSL1</sub> - V <sub>BUS2</sub>  ) | 1-2 Unit Loads | 9.2 | 42  | V    |

|                  |                                                         | 3-6 Unit Loads | 9.7 | 42  | V    |

| V <sub>IO</sub>  | VIO Pin Voltage (Note 4)                                |                | 2.5 | 3.8 | V    |

- 2. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 3. All voltages are referenced to GND.

- 4.  $V_{STC}$  must be at least 1V higher than  $V_{IO}$  for proper operation.

Table 5. ELECTRICAL CHARACTERISTICS (Note 5)

| Symbol                          | Parameter                                                                                             | Min                                                 | Тур                    | Max  | Unit                   |    |

|---------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------|------|------------------------|----|

| $\Delta V_{BR}$                 | Voltage drop over bus rectifier (V <sub>BUS</sub> – V <sub>B</sub> )                                  | $(R_{IDD} \text{ (Note 6)} = 4.02 \text{ k}\Omega)$ | _                      | -    | 1.25                   | V  |

| $\Delta V_{CS}$                 | Voltage drop over CS1                                                                                 | $R_{IDD}$ (Note 6) $\geq$ 13 k $\Omega$             | 1.30                   | -    | -                      | V  |

|                                 | (V <sub>B</sub> - V <sub>STC</sub> )                                                                  | $R_{IDD}$ (Note 6) $\leq$ 4.02 k $\Omega$           | 1.70                   | -    | -                      |    |

| I <sub>BUS</sub>                | Total Current Drawn from the Bus, Mark                                                                | $R_{IDD}$ (Note 6) = 30 k $\Omega$                  | _                      | 1.32 | 1.50                   | mA |

|                                 | State                                                                                                 | $R_{IDD}$ (Note 6) = 13 k $\Omega$                  | _                      | 2.71 | 3.00                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 8.45 k $\Omega$             | _                      | 4.10 | 4.50                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 6.19 k $\Omega$             | _                      | 5.50 | 6.00                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 4.87 k $\Omega$             | _                      | 6.80 | 7.50                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 4.02 k $\Omega$             | _                      | 8.22 | 9.00                   |    |

| $\Delta I_{BUS}$                | Bus Current Stability (over $\Delta V_{BUS}$ = 10 V, F                                                | RX/RXI = mark)                                      | _                      | 0.2  | 2                      | %  |

| I <sub>STC</sub>                | Idle Current Available for the Application                                                            | $R_{IDD}$ (Note 6) = 30 k $\Omega$                  | 0.88                   | 1.05 | 1.20                   | mA |

|                                 | to Draw from STC and V <sub>DD</sub> (Including Current Drawn from IO Pins)                           | $R_{IDD}$ (Note 6) = 13 k $\Omega$                  | 2.10                   | 2.35 | 2.60                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 8.45 k $\Omega$             | 3.10                   | 3.60 | 4.00                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 6.19 k $\Omega$             | 4.20                   | 4.80 | 5.40                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 4.87 k $\Omega$             | 5.30                   | 6.10 | 6.90                   |    |

|                                 |                                                                                                       | $R_{IDD}$ (Note 6, 7) = 4.02 k $\Omega$             | 6.50                   | 7.45 | 8.40                   |    |

| $\Delta I_{STC, \text{ space}}$ | Additional Current Available for the Application                                                      | tion when Transmitting a                            | -                      | 200  | -                      | μΑ |

| I <sub>CC</sub>                 | Internal Supply Current (R <sub>IDD</sub> (Note 6) = 13                                               | $B k\Omega$ , RX/RXI = mark)                        | _                      | 359  | 500                    | μΑ |

| I <sub>IO</sub>                 | Current Drawn by the V <sub>IO</sub> Pin                                                              |                                                     | -0.5                   | -    | 0.5                    | μΑ |

| V <sub>STC, clamp</sub>         | Clamp Voltage on Pin STC (I <sub>DD</sub> < I <sub>STC</sub> )                                        |                                                     | 6.0                    | 6.5  | 7.0                    | V  |

| V <sub>B, PFb</sub>             | Threshold Voltage on V <sub>B</sub> to Trigger PFb (No                                                | ote 8)                                              | V <sub>STC</sub> + 0.3 | -    | V <sub>STC</sub> + 0.8 | ٧  |

| V <sub>PFb, OH</sub>            | PFb Voltage High (I <sub>PFb</sub> = -100 μA)                                                         |                                                     | V <sub>IO</sub> – 0.6  | -    | V <sub>IO</sub>        | V  |

| V <sub>PFb, OL</sub>            | PFb Voltage Low (Note 9) (I <sub>PFb</sub> = 50 μA)                                                   |                                                     | 0                      | -    | 0.6                    | V  |

| V <sub>RIDD</sub>               | Voltage on RIDD Pin                                                                                   |                                                     | 1.15                   | 1.20 | 1.25                   | V  |

| V <sub>VS, OH</sub>             | Voltage on VS during High State ( $V_{STC} > V_{STC, VDD ON}$ , $I_{VS} = -5 \mu A$ )                 |                                                     | V <sub>STC</sub> - 0.4 | -    | V <sub>STC</sub>       | V  |

| R <sub>VS, PD</sub>             | Pull-down Resistor on VS during Low State (V <sub>DD</sub> > 2 V, V <sub>STC</sub> > V <sub>S</sub> ) | ,                                                   | 50                     | 100  | 150                    | kΩ |

- 5. All voltages are referenced to GND.

- 6. Resistor with 1% accuracy.

- 7. Only possible in NQFP variant.8. PFb comparator has a 70 mV hysteresis.

- 9. PFb pin is pulled down with an on-chip resistor of typically 2 M $\Omega$ .

Table 6. VDD REGULATOR ELECTRICAL CHARACTERISTICS (Note 10)

| Symbol                    | Parameter                                                                                                          | Min  | Тур  | Max  | Unit |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{DD}$                  | Voltage on V <sub>DD</sub> (Note 11 ) (I <sub>DD</sub> < 15 mA)                                                    | 3.1  | 3.3  | 3.6  | V    |

| I <sub>DD</sub>           | Peak Current that can be Supplied by V <sub>DD</sub> (Note 12)                                                     | 15   | -    | -    | mA   |

| I <sub>DD</sub> , OFF     | V <sub>BUS</sub> = 0 V, V <sub>STC</sub> = 0 V                                                                     | -0.5 | -    | 0.5  | μΑ   |

| V <sub>POR, ON</sub>      | Power-on Reset Threshold, Release                                                                                  | 2.65 | 2.85 | 3.15 | V    |

| V <sub>POR, OFF</sub>     | Power-on Reset Threshold, Reset                                                                                    | 2.55 | 2.75 | 3.00 | V    |

| V <sub>STC</sub> , VDD ON | Threshold Voltage on Pin STC to Turn On V <sub>DD</sub> Regulator, Pull the VS Pin High and Enable the PF Function | 5.6  | 6.0  | 6.4  | V    |

| V <sub>STC, VDD</sub> OFF | Threshold Voltage on Pin STC to Turn Off V <sub>DD</sub> Regulator and Pull the PFb and VS Pins Low                | 3.7  | 4.0  | 4.3  | V    |

<sup>10.</sup> All voltages are referenced to GND.

#### Table 7. RECEIVER ELECTRICAL CHARACTERISTICS (Note 13)

| Symbol                                        | Parameter                                                             |                                | Min                   | Тур                                 | Max                   | Unit |

|-----------------------------------------------|-----------------------------------------------------------------------|--------------------------------|-----------------------|-------------------------------------|-----------------------|------|

| $V_{T}$                                       | Receiver Threshold Voltage                                            |                                | V <sub>SC</sub> - 8.2 | -                                   | V <sub>SC</sub> – 5.7 | V    |

| V <sub>SC</sub>                               | Mark Level Storage Capacitor Volta                                    | ıge                            | -                     | -                                   | V <sub>B</sub>        | V    |

| I <sub>SC, charge</sub>                       | Mark Level Storage Capacitor Char                                     | ge Current                     | -40                   | -25                                 | -15                   | μΑ   |

| I <sub>SC, discharge</sub>                    | Mark Level Storage Capacitor Disc                                     | 0.3                            | 0.6                   | -0.033 ×<br>I <sub>SC, charge</sub> | μΑ                    |      |

| CDR                                           | Charge/Discharge Current Ratio                                        |                                | 30                    | 40                                  | -                     |      |

| V <sub>TX, OH</sub> ,<br>V <sub>TXI, OH</sub> | TX/TXI High-level Voltage ( $I_{TX}/I_{TXI} = -100 \mu A$ ) (Note 14) |                                | V <sub>IO</sub> – 0.6 | -                                   | V <sub>IO</sub>       | V    |

| V <sub>TX, OL</sub> ,                         | TX/TXI Low-level Voltage                                              | $(I_{TX}/I_{TXI} = 100 \mu A)$ | 0                     | =                                   | 0.35                  | V    |

| $V_{TXI, OL}$                                 | (I <sub>TX</sub> = 1.1 mA)                                            |                                | 0                     | -                                   | 1.5                   | V    |

| I <sub>TX</sub> , I <sub>TXI</sub>            | V <sub>TX</sub> = 7.5 V, V <sub>STC</sub> = 6 V                       |                                | 0                     | -                                   | 16                    | μΑ   |

<sup>13.</sup> All voltages are referenced to GND.

## Table 8. TRANSMITTER ELECTRICAL CHARACTERISTICS (Note 15)

| Symbol                                     | Parameter                                                                   | Min                   | Тур  | Max  | Unit |

|--------------------------------------------|-----------------------------------------------------------------------------|-----------------------|------|------|------|

| Імс                                        | Space Level Modulating Current ( $R_{RIS} = 100 \Omega$ (Note 16))          | 12.5                  | 15.0 | 18.0 | mA   |

| V <sub>RIS</sub>                           | Voltage on RIS Pin                                                          | 1.2                   | 1.4  | 1.6  | V    |

| V <sub>RX, IH</sub> , V <sub>RXI, IH</sub> | RX/RXI Input High                                                           | V <sub>IO</sub> – 0.8 | -    | 5.5  | V    |

| V <sub>RX, IL</sub> , V <sub>RXI, IL</sub> | RX/RXI Input Low                                                            | 0                     | -    | 8.0  | V    |

| I <sub>RX</sub> , I <sub>RXI</sub>         | Current Drawn or Sourced from RX/RXI Pins (Note 17) (V <sub>IO</sub> = 3 V) | ±6                    | -    | ±30  | μΑ   |

<sup>15.</sup> All voltages are referenced to GND.

<sup>11.</sup> Including output resistance of V<sub>DD</sub>.

<sup>12.</sup> Average current draw limited by I<sub>STC</sub>.

<sup>14.</sup>  $V_{STC}$  must be at least 1 V higher than  $V_{IO}$  for proper operation.

<sup>16.</sup> Resistor with 1% accuracy.

<sup>17.</sup> Including internal pull-up resistor on RX and internal pull-down resistor on RXI.

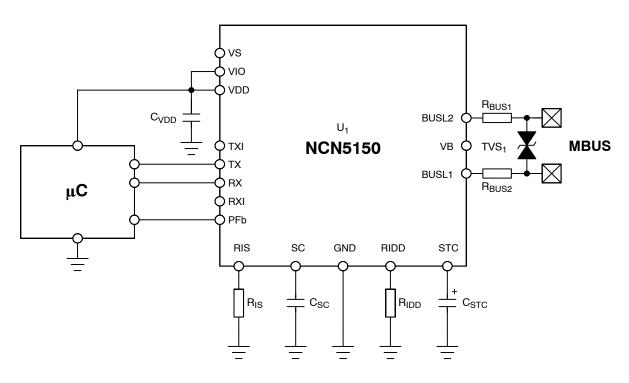

## **APPLICATION SCHEMATICS**

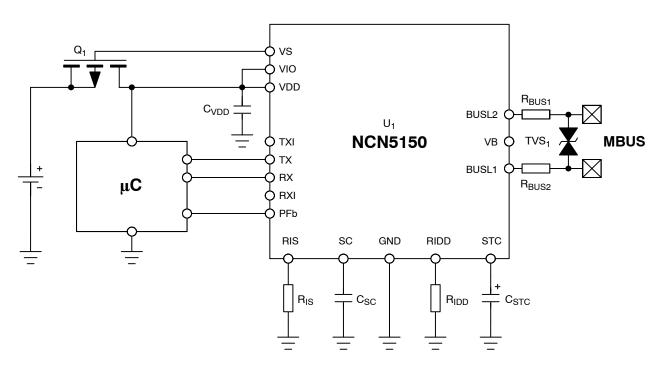

Figure 3. General Application Schematic

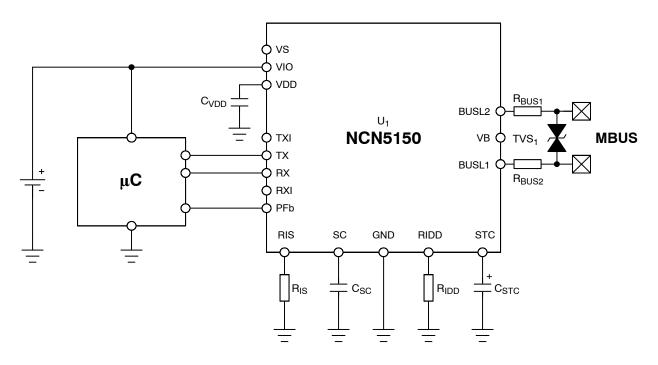

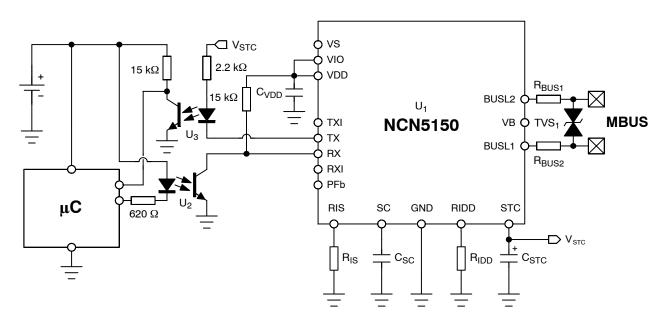

Figure 4. Application Schematic with External Power Supply (Battery)

## **APPLICATION SCHEMATICS**

Figure 5. Application Schematic with Backup External Power Supply

Figure 6. Optically Isolated Application Schematic

**Table 9. TYPICAL BILL OF MATERIALS**

| Reference         | Designator          | Value (Typical) | Tolerance  | Manufacturer     | Part Number |

|-------------------|---------------------|-----------------|------------|------------------|-------------|

| l                 | J <sub>1</sub>      | -               | -          | ON Semiconductor | NCN5150     |

| T\                | TVS <sub>1</sub>    |                 | -          | ON Semiconductor | 1SMA40CAT3G |

| C                 | C <sub>VDD</sub>    |                 | -20%, +80% |                  |             |

| F                 | R <sub>IS</sub>     | 100 Ω           | 1%         |                  |             |

| C                 | sc                  | 220 nF          | -20%, +80% |                  |             |

| R <sub>BUS1</sub> | , R <sub>BUS2</sub> | 220 Ω           | 10%        |                  |             |

| R <sub>IDD</sub>  | 1 UL                | 30 kΩ           | 1%         |                  |             |

|                   | 2 UL                | 13 kΩ           | 1%         |                  |             |

|                   | 3 UL (Note 18)      | 8.45 kΩ         | 1%         |                  |             |

|                   | 4 UL (Note 18)      | 6.19 kΩ         | 1%         |                  |             |

|                   | 5 UL (Note 18)      | 4.87 kΩ         | 1%         |                  |             |

|                   | 6 UL (Note 18)      | 4.02 kΩ         | 1%         |                  |             |

| C <sub>STC</sub>  | 1 UL                | ≤ 330 μF        | 10%        |                  |             |

|                   | 2 UL                | ≤ 820 μF        | 10%        |                  |             |

|                   | 3 UL (Note 18)      | ≤ 1,200 μF      | 10%        |                  |             |

|                   | 4 UL (Note 18)      | ≤ 1,500 μF      | 10%        |                  |             |

|                   | 5 UL (Note 18)      | ≤ 2,200 μF      | 10%        |                  |             |

|                   | 6 UL (Note 18)      | ≤ 2,700 μF      | 10%        |                  |             |

18.3-6 UL configurations are only possible for the NQFP variant.

#### APPLICATION INFORMATION

The NCN5150 is a slave transceiver for use in the meter bus (M-BUS) protocol. The bus connection is fully polarity independent. The transceiver will translate the bus voltage modulation from master-to-slave communication to TTL UART communication, and in the other direction translate UART voltage levels to bus current modulation. The transceiver also integrates a voltage regulator for utilizing the current drawn in this way from the bus, and an early power fail warning. The transceiver also supports an external power supply and the I/O high level can be set to match the slave sensor circuit. A complete block diagram is shown in Figure 2. Each section will be explained in more detail below.

#### **Meter Bus Protocol**

M-BUS is a European standard for communication and powering of utility meters and other sensors. Communication from master to slave is achieved by voltage-level signaling. The master will apply a nominal +36 V to the bus in idle state, or when transmitting a logical 1 ("mark"). When transmitting a logical 0 ("space"), the master will drop the bus voltage to a nominal +24 V.

Communication from the slave to the master is achieved by current modulation. In idle mode or when transmitting a logical 1 ("mark"), the slave will draw a fixed current from the bus. When transmitting a logical 0 ("space"), the slave will draw an extra nominal 15 mA from the bus. M-BUS uses a half-duplex 11-bit UART frame format, with 1 start

bit, 8 data bits, 1 even parity bit, and a stop bit. Communication speeds allowed by the M-BUS standard are 300, 600, 2400, 4800, 9600, 19200 and 38400 baud, all of which are supported by the NCN5150.

#### **Bus Connection and Rectification**

The bus should be connected to the pins BUSL1 and BUSL2 through series resistors to limit the current drawn from the bus in case of failure (according to the M-BUS standard). Typically, two 220  $\Omega$  resistors are used for this purpose.

Since the M-BUS connection is polarity independent, the NCN5150 will first rectify the bus voltage through an active diode bridge.

## Slave Power Supply (Bus Powered)

A slave device can be powered by the M-BUS or from an external supply. The M-BUS standard requires the slave to draw a fixed current from the bus. This is accomplished by the constant current source CS1. This current is used to charge the external storage capacitor  $C_{STC}$ . The current drawn from the bus is defined by the programming resistor  $R_{IDD}$ . The bus current can be chosen in increments of 1.5 mA called unit loads. Table 5 list the different values of programming resistors needed for different unit loads, as well as the current drawn from the bus ( $I_{BUS}$ ) and the current that can be drawn from the STC pin ( $I_{STC}$ ).  $I_{STC}$  is slightly less than  $I_{BUS}$  to account for the internal power consumption

of the NCN5150. The  $R_{\rm IDD}$  resistor used must be at least 1% accurate. Note that using 5 and 6 Unit Loads is not covered by the M-BUS standard.

When the voltage on the STC pin reaches  $V_{STC,\,VDD\,ON}$  the LDO is turned on, and will regulate the voltage on the VDD pin to 3.3 V, drawing current from the storage capacitor. A decoupling capacitor of minimum 1  $\mu F$  is required on the VDD pin for stability of the regulator. On the STC pin, a minimum capacitance of 10  $\mu F$  is required. Furthermore, the ratio  $C_{STC}/C_{VDD}$  must be larger than 9. The voltage on the STC pin is clamped to  $V_{STC,\,clamp}$  by a shunt regulator, which will dissipate any excess current that is not used by the NCN5150 or external circuits.

### Slave Power Supply (External)

In case the external sensor circuit consumes more than the allowed bus current or the sensor should be kept operational when the bus is not present, an external power supply, such as a battery, is required.

When the external circuitry uses different logical voltage levels, simply connect the power supply of that voltage level to  $V_{IO}$ , so that the RX, RXI, TX, TXI and PFb pins will respond to the correct voltage levels. The NCN5150 will still be powered from the bus, but all communication will be translated to the voltage level of  $V_{IO}$ .

If the external power supply should be used only as a backup when the bus power supply fails, a PMOS transistor can be inserted between the external power supply and VDD as shown in Figure 5. The gate is connected to VS, and will be driven high when the voltage on STC goes above the turn-on threshold of the LDO, nl. V<sub>STC, VDD ON</sub>. For more information see the paragraph on the power on sequence and corresponding Figure 12 on page 10.

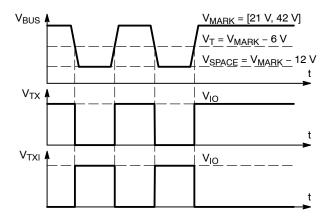

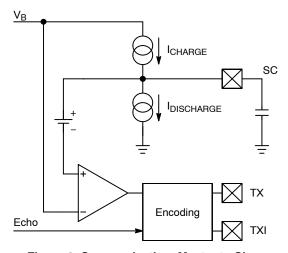

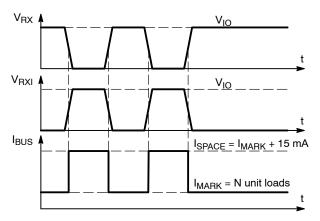

### Communication, Master to Slave

M-BUS communication from master to slave is based on voltage level signaling. To differentiate between master signaling and voltage drop caused by the signaling of another slave over cabling resistance, etc., the mark level  $V_{BUS,\,MARK}$  is stored, and only when the bus voltage drops to less than  $V_T$  will the NCN5150 detect communication. A simplified schematic of the receiver is shown in Figure 8. The received data is transmitted on the pins TX and TXI, as shown in the waveforms of Figure 7.

An external capacitor must be connected to the SC pin to store the mark voltage level. This capacitor is charged to  $V_{\rm B}.$  Discharging of this capacitor is typically 40x slower, so that the voltage on SC drops only a little during the time the master is transmitting a space. The value of  $C_{\rm SC}$  must be chosen it the range of 100 nF–330 nF.

Figure 7. Communication, Master to Slave

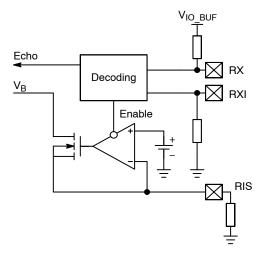

Figure 8. Communication, Master to Slave

#### **Communication, Slave to Master**

M-BUS communication from slave to master uses bus current modulation while the voltage remains constant. This current modulation can be controlled from either the RX or RXI pin as shown in Figure 10. When transmitting a space ("0"), the current modulator will draw an additional current from the bus. This current can be set with a programming resistor  $R_{RIS}$ . To achieve the space current required the M-BUS standard,  $R_{RIS}$  should be 100  $\Omega$ . A simplified schematic of the transmitter is shown in Figure 11.

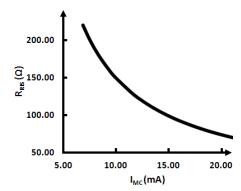

Figure 9. Typical Relationship between RIS and Current Modulation Level

Because the M-BUS protocol is specified as half-duplex, an echo function will cause the transmitted signal on RX or RXI to appear on the receiver outputs TX and TXI. Should the master attempt to send at the same time, the bitwise added signal of both sources will appear on these pins, resulting in invalid data.

Figure 10. Communication, Slave to Master

Figure 11. Communication, Slave to Master

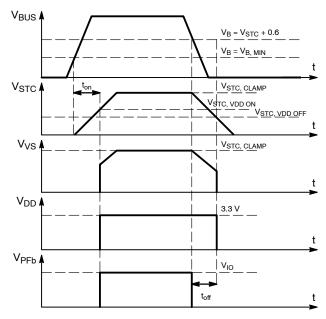

#### Power On/Off Sequence

The power-on and power-off sequence of the NCN5150 is shown in Figure 12. Shown also in Figure 12 is the operation of the PFb pin. This pin is used to give an early warning to the microcontroller that the bus power is collapsing, allowing the microcontroller to save its data and

shut down gracefully. The times  $t_{on}$  and  $t_{off}$  can be approximated by the following formulas:

$$t_{on} = \frac{C_{STC}}{I_{STC}} V_{STC, \, VDD \, ON}$$

(eq. 1)

$$t_{\rm off} = \frac{C_{\rm STC}}{I_{\rm CC} + I_{\rm DD}} \Big( V_{\rm STC, \, Clamp} - V_{\rm STC, \, VDD \, OFF} \Big) \quad (\text{eq. 2})$$

Where  $I_{CC}$  is the internal current consumption of the NCN5150 and  $I_{DD}$  is the current consumed by external circuits drawn from either VDD or STC.

These formulas can be used to dimension the value of the bulk  $C_{STC}$  needed, taking into account that the M-BUS standard requires  $t_{on}$  to be less than 3 s.

For certain applications where the power drawn from the bus is not used in external circuits, the storage capacitor value can be much lower. The NCN5150 requires a minimum STC capacitance of  $10~\mu F$  to ensure that the bus current regulation is stable under all conditions.

Figure 12. Power-on and Power-off

## Thermal Shutdown

The NCN5150 includes a thermal shutdown function that will disable the transmitter when the junction temperature of the IC becomes too hot. The thermal protection is only active when the slave is transmitting a space to the master.

**Table 10. ORDERING INFORMATION**

| Device       | Package                  | Shipping <sup>†</sup> |  |

|--------------|--------------------------|-----------------------|--|

| NCN5150DG    | SOIC16                   | 48 Units / Tube       |  |

| NCN5150DR2G  | (Pb-free)                | 3,000 / Tape & Reel   |  |

| NCN5150MNTWG | NQFP20, 4x4<br>(Pb-free) | 2,500 / Tape & Reel   |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **PACKAGE DIMENSIONS**

#### **QFN20, 4x4, 0.5P** CASE 485E ISSUE B

\*For additional information on our Pb-free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

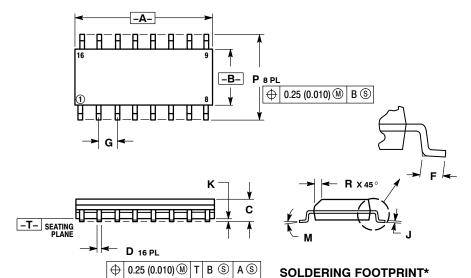

#### PACKAGE DIMENSIONS

#### SOIC-16 CASE 751B-05 ISSUE K

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR PROTRUSION

SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC       | HES   |

|-----|--------|--------|-----------|-------|

| DIM | MIN    | MAX    | MIN       | MAX   |

| Α   | 9.80   | 10.00  | 0.386     | 0.393 |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |

| С   | 1.35   | 1.75   | 0.054     | 0.068 |

| D   | 0.35   | 0.49   | 0.014     | 0.019 |

| F   | 0.40   | 1.25   | 0.016     | 0.049 |

| G   | 1.27   | BSC    | 0.050 BSC |       |

| J   | 0.19   | 0.25   | 0.008     | 0.009 |

| K   | 0.10   | 0.25   | 0.004     | 0.009 |

| M   | 0°     | 7°     | 0°        | 7°    |

| P   | 5.80   | 6.20   | 0.229     | 0.244 |

| R   | 0.25   | 0.50   | 0.010     | 0.019 |

**PITCH DIMENSIONS: MILLIMETERS**

ЯX 6.40 16X 1.12

\*For additional information on our Pb-free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and (ii) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor: NCN5150MNTWG