## Step-Up/Step-Down Li+ Battery Charger

#### **General Description**

The MAX1870A step-up/step-down multichemistry battery charger charges with battery voltages above and below the adapter voltage. This highly integrated charger requires a minimum number of external components. The MAX1870A uses a proprietary step-up/ step-down control scheme that provides efficient charging. Analog inputs control charge current and voltage, and can be programmed by the host or hardwired.

The MAX1870A accurately charges two to four lithiumion (Li+) series cells at greater than 4A. A programmable input current limit is included, which avoids overloading the AC adapter when supplying the load and the battery charger simultaneously. This reduces the maximum adapter current, which reduces cost. The MAX1870A provides analog outputs to monitor the current drawn from the AC adapter and charge current. A digital output indicates the presence of an AC adapter. When the adapter is removed, the MAX1870A consumes less than 1µA from the battery.

The MAX1870A is available in a 32-pin thin QFN (5mm x 5mm) package and is specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C extended temperature range. The MAX1870A evaluation kit (MAX1870AEVKIT) is available to help reduce design time.

#### **Applications**

- Notebook and Subnotebook Computers

- Handheld Terminals

### **Benefits and Features**

- Highly Flexible Input Voltage Range Works with Affordable AC Adapters

- Step-Up/Step-Down Control Scheme

- Input Voltage from 8V to 28V

- Analog Output Indicates Adapter Current

- Accurately Charge Li+ or NiCd/NiMH Batteries

- Battery Voltage from 0V to 17.6V

- ±0.5% Charge-Voltage Accuracy

- ±9% Charge-Current Accuracy

- ±8% Input Current-Limit Accuracy

- Tune Design to Increase Safety and Efficiency

- Programmable Maximum Battery Charge Current

- Analog Inputs Control-Charge Current, Charge Voltage, and Input-Current Limit

- 32-Pin Thin QFN (5mm x 5mm) Package Saves Space while Supporting Step-Up and Step-Down Operation

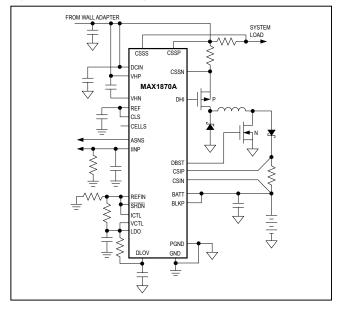

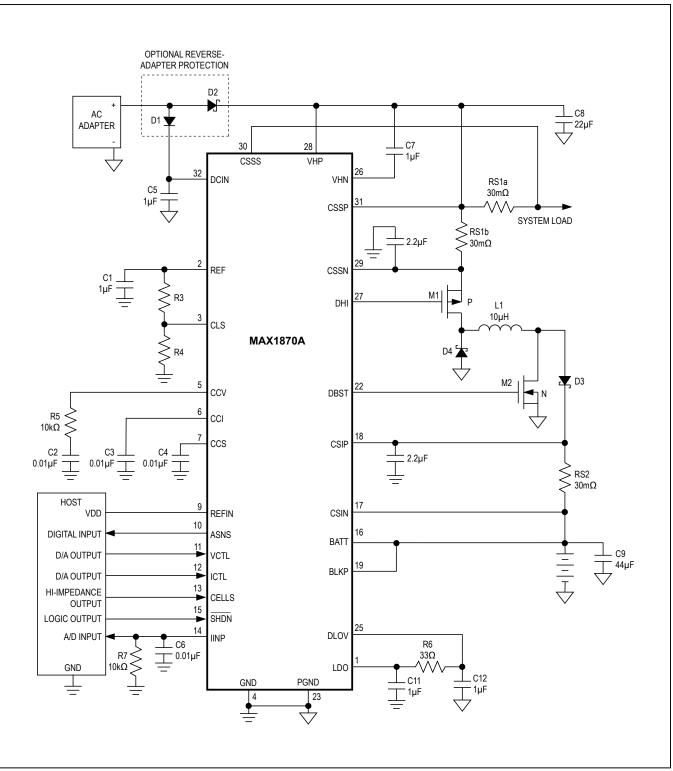

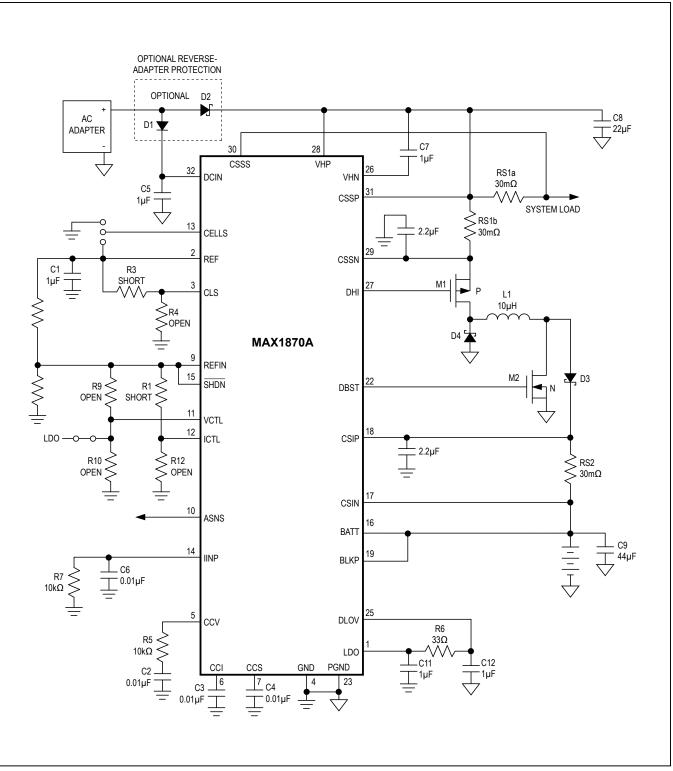

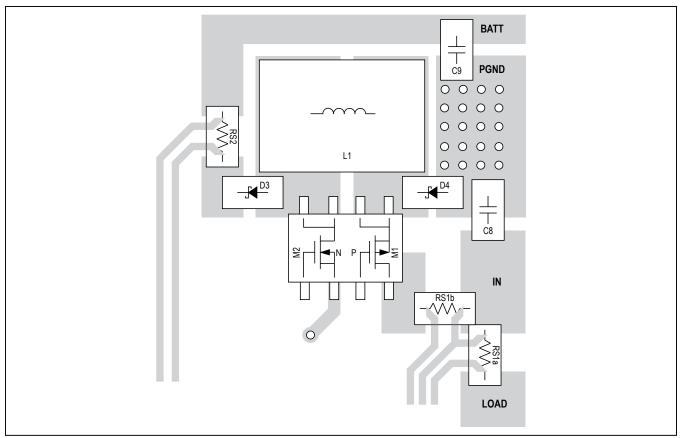

### **Typical Operating Circuit**

Ordering Information appears at end of data sheet.

## Step-Up/Step-Down Li+ Battery Charger

### **Absolute Maximum Ratings**

| DCIN, CSSP, CSSS, CSSN,                                          |

|------------------------------------------------------------------|

| VHP, VHN, DHI to GND0.3V to +30V                                 |

| VHP, DHI to VHN0.3V to +6V                                       |

| BATT, CSIP, CSIN, BLKP to GND0.3V to +20V                        |

| CSIP to CSIN, CSSP to CSSN,                                      |

| CSSP to CSSS, PGND to GND0.3V to +0.3V                           |

| CCI, CCS, CCV, REF, IINP to GND0.3V to (V <sub>LDO</sub> + 0.3V) |

| DBST to GND0.3V to (V <sub>DLOV</sub> + 0.3V)                    |

| DLOV, VCTL, ICTL, REFIN, CELLS,                                  |

| CLS, LDO, ASNS, SHDN to GND0.3V to +6V                           |

| LDO Current                                           | 50mA            |

|-------------------------------------------------------|-----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

| 32-Pin Thin QFN 5mm x 5mm                             |                 |

| (derate 21mW/°C above +70°C)                          | 1.7W            |

| Operating Temperature Range                           |                 |

| MAX1870AETJ                                           | 40°C to +85°C   |

| Storage Temperature Range                             | -60°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **32 TQFN**

| Package Code        | T3255+4        |

|---------------------|----------------|

| Outline Number      | 21-0140        |

| Land Pattern Number | <u>90-0012</u> |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

### **Electrical Characteristics**

| PARAMETER                              | CONDITIONS                                            | MIN  | TYP | MAX  | UNITS |

|----------------------------------------|-------------------------------------------------------|------|-----|------|-------|

| CHARGE-VOLTAGE REGULA                  | TION                                                  |      |     |      |       |

| VCTL Range                             |                                                       | 0    |     | 3.6  | V     |

|                                        | V <sub>VCTL</sub> = V <sub>LDO</sub> (2 cells)        | -0.5 |     | +0.5 |       |

|                                        | V <sub>VCTL</sub> = V <sub>LDO</sub> (3 cells)        | -0.5 |     | +0.5 |       |

| Battery Regulation Voltage<br>Accuracy | V <sub>VCTL</sub> = V <sub>LDO</sub> (4 cells)        | -0.5 |     | +0.5 |       |

|                                        | V <sub>VCTL</sub> = V <sub>REFIN</sub> (2 cells)      | -0.8 |     | +0.8 |       |

|                                        | V <sub>VCTL</sub> = V <sub>REFIN</sub> (3 cells)      | -0.8 |     | +0.8 | %     |

| riodruoy                               | V <sub>VCTL</sub> = V <sub>REFIN</sub> (4 cells)      | -0.8 |     | +0.8 |       |

|                                        | V <sub>VCTL</sub> = V <sub>REFIN</sub> / 20 (2 cells) | -1.2 |     | +1.2 |       |

|                                        | V <sub>VCTL</sub> = V <sub>REFIN</sub> / 20 (3 cells) | -1.2 |     | +1.2 |       |

|                                        | V <sub>VCTL</sub> = V <sub>REFIN</sub> / 20 (4 cells) | -1.2 |     | +1.2 |       |

| VCTL Default Threshold                 | VCTL rising                                           | 4.0  | 4.1 | 4.2  | V     |

| VCTL Input Bias Current                | 0 < V <sub>VCTL</sub> < V <sub>REFIN</sub>            | -1   |     | +1   |       |

|                                        | DCIN = 0, $V_{REFIN} = V_{VCTL} = 3.6V$               | -1   |     | +1   | μA    |

|                                        | VCTL = DCIN = 0, V <sub>REFIN</sub> = 3.6V            | -1   |     | +1   |       |

### **Electrical Characteristics (continued)**

| PARAMETER                                         | C                                                          | CONDITIONS                                   |                | TYP           | MAX              | UNITS |  |

|---------------------------------------------------|------------------------------------------------------------|----------------------------------------------|----------------|---------------|------------------|-------|--|

| CHARGE-CURRENT REGULATI                           | ON                                                         |                                              | ·              |               |                  |       |  |

| ICTL Range                                        |                                                            |                                              | 0              |               | 3.6              | V     |  |

|                                                   | V <sub>ICTL</sub> = V <sub>REFIN</sub>                     | V <sub>ICTL</sub> = V <sub>REFIN</sub>       |                | 73            | 79               |       |  |

| Quick-Charge-Current Accuracy                     | V <sub>ICTL</sub> = V <sub>REFIN</sub> x 0.8               |                                              | 54             | 59            | 64               | mV    |  |

|                                                   | V <sub>ICTL</sub> = V <sub>REFIN</sub> x 0.58              | 3                                            | 39             | 43            | 47               |       |  |

| Trickle-Charge-Current Accuracy                   | V <sub>ICTL</sub> = V <sub>REFIN</sub> x 0.06              | 25                                           | 3.0            | 4.5           | 6.0              | mV    |  |

| BATT/CSIP/CSIN Input Voltage<br>Range             |                                                            |                                              | 0              |               | 19               | V     |  |

|                                                   | DCIN = 0                                                   |                                              |                | 0.1           | 2                |       |  |

| CSIP Input Current                                | ICTL = 0                                                   |                                              |                | 0.1           | 2                | μA    |  |

|                                                   | ICTL = REFIN                                               |                                              |                | 350           | 600              |       |  |

|                                                   | DCIN = 0                                                   |                                              |                | 0.1           | 2                |       |  |

| CSIN Input Current                                | ICTL = 0                                                   |                                              |                | 0.1           | 2                | μA    |  |

|                                                   | ICTL = REFIN                                               |                                              |                | 0.1           | 2                | 2     |  |

| ICTL Power-Down-Mode<br>Threshold Voltage         |                                                            |                                              | REFIN<br>/ 100 | REFIN<br>/ 55 | REFIN<br>/ 32    | V     |  |

|                                                   | 0 < V <sub>ICTL</sub> < V <sub>REFIN</sub>                 |                                              | -1             |               | +1               |       |  |

| ICTL Input Bias Current                           | ICTL = DCIN = 0, V <sub>REFIN</sub> = 3.6V -1              |                                              |                | +1            | μΑ               |       |  |

| INPUT-CURRENT REGULATION                          |                                                            |                                              |                |               |                  |       |  |

| Charger-Input Current-Limit                       | 0000 - 000D                                                | CLS = REF                                    | 97             | 105           | 113              |       |  |

| Accuracy (V <sub>CSSP</sub> - V <sub>CSSN</sub> ) | CSSS = CSSP                                                | CLS = REF x 0.845                            | 81             | 88            | 95               | mV    |  |

| System-Input Current-Limit                        | CSSN = CSSP                                                | CLS = REF                                    | 97             | 105           | 113              | mV    |  |

| Accuracy (V <sub>CSSP</sub> - V <sub>CSSS</sub> ) | C33N - C33F                                                | CLS = REF x 0.845                            | 81             | 88            | 95               | IIIV  |  |

| CSSP/CSSS/CSSN Input<br>Voltage Range             |                                                            |                                              | 8              |               | 28               | V     |  |

| CSSP Input Current                                | $V_{CSSP} = V_{CSSN} = V_{CSSN}$                           | <sub>SSS</sub> = V <sub>DCIN</sub> = 6V      | -1             |               | +1               |       |  |

| Coor input Current                                | $V_{CSSP} = V_{CSSN} = V_{CSSN}$                           | <sub>SSS</sub> = V <sub>DCIN</sub> = 8V, 28V |                | 700           | 1200             | μA    |  |

| CSSS/CSSN Input Current                           | $V_{CSSP} = V_{CSSN} = V_{CSSN}$                           | <sub>SSS</sub> = V <sub>DCIN</sub> = 6V      | -1             |               | +1               |       |  |

|                                                   | $V_{CSSP} = V_{CSSN} = V_{CSSS} = V_{DCIN} = 8V, 28V$      |                                              | -1             |               | +1               | μA    |  |

| CLS Input Range                                   |                                                            |                                              |                |               | V <sub>REF</sub> | V     |  |

| CLS Input Bias Current                            | CLS = REF                                                  |                                              | -1             |               | +1               | μA    |  |

| IINP Transconductance                             | V <sub>CSSP</sub> - V <sub>CSSS</sub> = 102mV, CSSN = CSSP |                                              | 2.5            | 2.8           | 3.1              | µA/mV |  |

| IINP Output Current                               | $V_{CSSP}$ - $V_{CSSN}$ = 200                              | mV, V <sub>IINP</sub> = 0V                   | 350            |               |                  | μA    |  |

|                                                   | $V_{CSSP}$ - $V_{CSSS}$ = 200                              | mV, V <sub>IINP</sub> = 0V                   | 350            |               |                  | μΑ    |  |

| IINP Output Voltage                               | $V_{CSSP}$ - $V_{CSSN}$ = 200                              | mV, IINP float                               | 3.5            |               |                  | V     |  |

|                                                   | $V_{CSSP} - V_{CSSS} = 200$                                | mV, IINP float                               | 3.5            |               |                  | v     |  |

### **Electrical Characteristics (continued)**

| PARAMETER                                                          | CONDITIONS                                         | MIN   | ТҮР   | MAX   | UNITS |

|--------------------------------------------------------------------|----------------------------------------------------|-------|-------|-------|-------|

| SUPPLY AND LINEAR REGULAT                                          | OR                                                 |       |       |       |       |

| DCIN Input Voltage Range                                           |                                                    | 8     |       | 28    | V     |

|                                                                    | DCIN falling                                       | 4     | 6.2   |       |       |

| DCIN Undervoltage Lockout                                          | DCIN rising                                        |       | 6.3   | 7.85  | V     |

| DCIN Quiescent Current                                             | 8.0V < V <sub>DCIN</sub> < 28V                     |       | 3.5   | 6     | mA    |

| BATT Input Voltage Range                                           |                                                    | 0     |       | 19    | V     |

|                                                                    | DCIN = 0                                           |       | 0.1   | 1     |       |

| BATT Input Bias Current                                            | V <sub>BATT</sub> = 2V to 19V                      |       | 300   | 500   | μA    |

| LDO Output Voltage                                                 | No load                                            | 5.3   | 5.4   | 5.5   | V     |

| LDO Load Regulation                                                | 0 < I <sub>LDO</sub> < 10mA                        |       | 70    | 150   | mV    |

| LDO Undervoltage Lockout                                           | V <sub>DCIN</sub> = 8V, LDO rising                 | 4.00  | 5.0   | 5.25  | V     |

| REFERENCE                                                          |                                                    |       |       |       |       |

| REF Output Voltage                                                 | I <sub>REF</sub> = 0μA                             | 4.076 | 4.096 | 4.116 | V     |

| REF Load Regulation                                                | 0 < I <sub>REF</sub> < 500μA                       |       | 5     | 10    | mV    |

| REF Undervoltage-Lockout Trip<br>Point                             | V <sub>REF</sub> falling                           |       | 3.1   | 3.9   | V     |

| REFIN Input Range                                                  |                                                    | 2.5   |       | 3.6   | V     |

| REFIN UVLO Rising                                                  |                                                    |       | 1.9   | 2.2   | V     |

| REFIN UVLO Hysteresis                                              |                                                    |       | 50    |       | mV    |

|                                                                    | V <sub>DCIN</sub> = 18V                            |       | 50    | 100   |       |

| REFIN Input Bias Current                                           | DCIN = 0, V <sub>REFIN</sub> = 3.6V                | -1    |       | +1    | μA    |

| SWITCHING REGULATOR                                                |                                                    | ·     |       |       |       |

| Cycle-by-Cycle Step-Up Maximum<br>Current-Limit Sense Voltage      | V <sub>DCIN</sub> = 12V, V <sub>BATT</sub> = 16.8V | 135   | 150   | 165   | mV    |

| Cycle-by-Cycle Step-Down<br>Maximum Current-Limit Sense<br>Voltage | V <sub>DCIN</sub> = 19V, V <sub>BATT</sub> = 16.8V | 135   | 150   | 165   | mV    |

| Step-Down On-Time                                                  | V <sub>DCIN</sub> = 18V, V <sub>BATT</sub> = 16.8V | 2.2   | 2.4   | 2.6   | μs    |

| Minimum Step-Down Off-Time                                         | V <sub>DCIN</sub> = 18V, V <sub>BATT</sub> = 16.8V | 0.15  | 0.4   | 0.50  | μs    |

| Step-Up Off-Time                                                   | V <sub>DCIN</sub> = 12V, V <sub>BATT</sub> = 16.8V | 1.6   | 1.8   | 2.0   | μs    |

| Minimum Step-Up On-Time                                            | V <sub>DCIN</sub> = 12V, V <sub>BATT</sub> = 16.8V | 0.15  | 0.3   | 0.40  | μs    |

### **Electrical Characteristics (continued)**

| PARAMETER                              | CONDITIONS                                                                                        |                                   | TYP | MAX  | UNITS        |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------|-----|------|--------------|--|

| MOSFET DRIVERS                         |                                                                                                   |                                   |     | •    |              |  |

| VHP - VHN Output Voltage               | 8V < V <sub>VHP</sub> < 28V, no load                                                              | 4.5                               | 5   | 5.5  | V            |  |

| VHN Load Regulation                    | 0 < I <sub>VHN</sub> < 10mA                                                                       | 0 < I <sub>VHN</sub> < 10mA 70 15 |     | 150  | mV           |  |

| DHI On-Resistance High                 | I <sub>SOURCE</sub> = 10mA                                                                        | I <sub>SOURCE</sub> = 10mA 2      |     | 5    | Ω            |  |

| DHI On-Resistance Low                  | I <sub>SINK</sub> = 10mA                                                                          |                                   | 1   | 3    | Ω            |  |

| VHP Input Bias Current                 | DCIN = 0                                                                                          |                                   | 0.1 | 1    | μA           |  |

|                                        | V <sub>DCIN</sub> = 18V                                                                           |                                   | 1.3 | 2    | mA           |  |

| PLKD Input Diag Current                | ICTL = 0                                                                                          |                                   | 0.1 | 2    |              |  |

| BLKP Input Bias Current                | V <sub>ICTL</sub> = V <sub>REFIN</sub> = 3.3V                                                     |                                   | 100 | 400  | μA           |  |

| DLOV Supply Current                    | DBST low                                                                                          |                                   | 5   | 10   | μA           |  |

| DBST On-Resistance High                | I <sub>SOURCE</sub> = 10mA                                                                        |                                   | 2   | 5    | Ω            |  |

| DBST On-Resistance Low                 | I <sub>SINK</sub> = 10mA                                                                          |                                   | 1   | 3    | Ω            |  |

| ERROR AMPLIFIERS                       |                                                                                                   |                                   |     |      |              |  |

| GMV Amplifier Loop<br>Transconductance | VCTL = REFIN, V <sub>BATT</sub> = 16.8V                                                           | 0.05                              | 0.1 | 0.20 | µA/mV        |  |

| GMI Amplifier Loop<br>Transconductance | ICTL = REFIN, V <sub>CSIP</sub> - V <sub>CSIN</sub> = 72mV                                        | 1.8                               | 2.4 | 3.0  | µA/mV        |  |

| GMS Amplifier Loop                     | $V_{CLS}$ = REF, $V_{CSSP}$ - $V_{CSSN}$ = 102mV, $V_{CSSP}$ = $V_{CSSS}$                         | 1.2                               | 1.7 | 2.2  | u//m/        |  |

| Transconductance                       | $V_{CLS}$ = REF, $V_{CSSP}$ - $V_{CSSS}$ = 102mV, $V_{CSSP}$ = $V_{CSSN}$                         | 1.2                               | 1.7 | 2.2  | μΑ/mV<br>2.2 |  |

| COV/ Output Current                    | VCTL = REFIN, V <sub>BATT</sub> = 15.8V                                                           | 50                                |     |      |              |  |

| CCV Output Current                     | VCTL = REFIN, V <sub>BATT</sub> = 17.8V                                                           |                                   |     | -50  | μA           |  |

| COL Output Ourseat                     | ICTL = REFIN, V <sub>CSIP</sub> - V <sub>CSIN</sub> = 0mV                                         | 150                               |     |      |              |  |

| CCI Output Current                     | ICTL = REFIN, V <sub>CSIP</sub> - V <sub>CSIN</sub> = 150mV                                       |                                   |     | -150 | μA           |  |

|                                        | CLS = REF, V <sub>CSSP</sub> = V <sub>CSSN</sub> , V <sub>CSSP</sub> = V <sub>CSSS</sub>          | 100                               |     |      |              |  |

| CCS Output Current                     | CLS = REF, $V_{CSSP}$ - $V_{CSSN}$ = 200mV,<br>$V_{CSSP}$ - $V_{CSSS}$ = 200mV                    |                                   |     | -100 | μA           |  |

| CCI/CCS/CCV Clamp Voltage              | 1.1V < V <sub>CCV</sub> < 3.5V, 1.1V < V <sub>CCS</sub> < 3.5V,<br>1.1V < V <sub>CCI</sub> < 3.5V | 100                               | 300 | 500  | mV           |  |

### **Electrical Characteristics (continued)**

| PARAMETER                | CONDITIONS                                                           | MIN              | TYP  | MAX  | UNITS         |

|--------------------------|----------------------------------------------------------------------|------------------|------|------|---------------|

| LOGIC LEVELS             |                                                                      |                  |      |      |               |

| ASNS Output-Voltage Low  | V <sub>IINP</sub> = GND, I <sub>SINK</sub> = 1mA                     |                  |      | 0.4  | V             |

| ASNS Output-Voltage High | V <sub>IINP</sub> = 4V, I <sub>SOURCE</sub> = 1mA                    | LDO - 0.5        | 5    |      | V             |

| ASNS Current Detect      | V <sub>IINP</sub> rising                                             | 1.1              | 1.15 | 1.2  | V             |

| ASNS Current Delect      | Hysteresis                                                           |                  | 50   |      | mV            |

| SHDN Input Bias Current  | V <sub>SHDN</sub> = 0 to V <sub>REFIN</sub>                          | -1               |      | +1   |               |

|                          | DCIN = 0, $V_{REFIN}$ = 5V, $V_{\overline{SHDN}}$ = 0 to $V_{REFIN}$ | -1               |      | +1   | μA            |

| SHDN Threshold           | $\overline{\text{SHDN}}$ falling, $V_{\text{REFIN}}$ = 2.8V to 3.6V  | 22               | 23.5 | 25   | % of<br>REFIN |

| SHDN Hysteresis          |                                                                      |                  | 1    |      | % of<br>REFIN |

| CELLS Input Low Voltage  |                                                                      |                  |      | 0.75 | V             |

| CELLS Float Voltage      |                                                                      | 40               | 50   | 60   | % of<br>REFIN |

| CELLS Input High Voltage |                                                                      | REFIN -<br>0.75V |      |      | V             |

| CELLS Input Bias Current | CELLS = 0 to REFIN                                                   | -2               |      | +2   | μA            |

## Step-Up/Step-Down Li+ Battery Charger

### **Electrical Characteristics**

(Circuit of Figure 2,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = V_{CSSS} = V_{VHP} = 18V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = V_{BLKP} = 12V$ ,  $V_{REFIN} = 3.0V$ ,  $V_{ICTL} = 0.75 \times V_{REFIN}$ , VCTL = LDO, CELLS = FLOAT, GND = PGND = 0,  $V_{DLOV} = 5.4V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .) (Note 1)

| PARAMETER                                         |                                                | CONDITIONS                                        | MIN T                | YP MAX           | UNITS |  |

|---------------------------------------------------|------------------------------------------------|---------------------------------------------------|----------------------|------------------|-------|--|

| CHARGE-VOLTAGE REGULATIO                          | N                                              |                                                   | ·                    |                  |       |  |

| VCTL Range                                        |                                                |                                                   | 0                    | 3.6              | V     |  |

|                                                   | V <sub>VCTL</sub> = V <sub>LDO</sub> (2        | 2 cells)                                          | -0.8                 | +0.8             |       |  |

|                                                   | $V_{VCTL} = V_{LDO}$ (3)                       | V <sub>VCTL</sub> = V <sub>LDO</sub> (3 cells)    |                      | +0.8             | 1     |  |

|                                                   | V <sub>VCTL</sub> = V <sub>LDO</sub> (4        | V <sub>VCTL</sub> = V <sub>LDO</sub> (4 cells)    |                      | +0.8             |       |  |

|                                                   | V <sub>VCTL</sub> = V <sub>REFIN</sub>         | (2 cells)                                         | -1.2                 | +1.2             |       |  |

| Battery Regulation Voltage<br>Accuracy            | V <sub>VCTL</sub> = V <sub>REFIN</sub>         | (3 cells)                                         | -1.2                 | +1.2             | %     |  |

| , loouraby                                        | V <sub>VCTL</sub> = V <sub>REFIN</sub>         | (4 cells)                                         | -1.2                 | +1.2             |       |  |

|                                                   | V <sub>VCTL</sub> = V <sub>REFIN</sub>         | / 20 (2 cells)                                    | -1.4                 | +1.4             | 1     |  |

|                                                   | V <sub>VCTL</sub> = V <sub>REFIN</sub>         | / 20 (3 cells)                                    | -1.4                 | +1.4             |       |  |

|                                                   | V <sub>VCTL</sub> = V <sub>REFIN</sub>         | / 20 (4 cells)                                    | -1.4                 | +1.4             |       |  |

| VCTL Default Threshold                            | VCTL rising                                    |                                                   | 4.0                  | 4.2              | V     |  |

| CHARGE-CURRENT REGULATIO                          | N                                              |                                                   |                      |                  |       |  |

| ICTL Range                                        |                                                |                                                   | 0                    | 3.6              | V     |  |

|                                                   | V <sub>ICTL</sub> = V <sub>REFIN</sub>         |                                                   | 66                   | 80               |       |  |

| Quick-Charge-Current Accuracy                     | V <sub>ICTL</sub> = V <sub>REFIN</sub>         | V <sub>ICTL</sub> = V <sub>REFIN</sub> x 0.8      |                      | 65               | mV    |  |

|                                                   | V <sub>ICTL</sub> = V <sub>REFIN</sub> x 0.583 |                                                   | 38                   | 48               |       |  |

| BATT/CSIP/CSIN Input Voltage<br>Range             |                                                |                                                   |                      | 19               | V     |  |

| CSIP Input Current                                | ICTL = REFIN                                   |                                                   |                      | 600              | μA    |  |

| ICTL Power-Down-Mode<br>Threshold Voltage         |                                                |                                                   | REFIN<br>/ 100       | REFIN<br>/ 32    | V     |  |

| INPUT-CURRENT REGULATION                          |                                                |                                                   | I                    |                  | 1     |  |

| Charger-Input Current-Limit                       |                                                | CLS = REF                                         | 95                   | 115              |       |  |

| Accuracy (V <sub>CSSP</sub> - V <sub>CSSN</sub> ) | CSSS = CSSP                                    | CLS = REF x 0.845                                 | 79                   | 97               | mV    |  |

| System-Input Current-Limit                        |                                                | CLS = REF                                         | 95                   | 115              | .,    |  |

| Accuracy (V <sub>CSSP</sub> - V <sub>CSSS</sub> ) | CSSN = CSSP                                    | CLS = REF x 0.845                                 | 79                   | 97               | mV    |  |

| CSSP/CSSS/CSSN Input Voltage<br>Range             |                                                |                                                   | 8                    | 28               | V     |  |

| CSSP Input Current                                | V <sub>CSSP</sub> = V <sub>CSSN</sub>          | = V <sub>CSSS</sub> = V <sub>DCIN</sub> = 8V, 28V |                      | 1200             | μA    |  |

| CLS Input Range                                   |                                                |                                                   | V <sub>REF</sub> / 2 | V <sub>REF</sub> | V     |  |

| IINP Transconductance                             | V <sub>CSSP</sub> - V <sub>CSSS</sub>          | = 102mV, CSSN = CSSP                              | 2.5                  | 3.1              | µA/mV |  |

|                                                   |                                                | = 200mV, V <sub>IINP</sub> = 0V                   | 350                  |                  |       |  |

| IINP Output Current                               |                                                | = 200mV, V <sub>IINP</sub> = 0V                   | 350                  |                  | μA    |  |

|                                                   |                                                | = 200mV, IINP float                               | 3.5                  |                  |       |  |

| IINP Output Voltage                               |                                                | = 200mV, IINP float                               | 3.5                  |                  | V     |  |

## Step-Up/Step-Down Li+ Battery Charger

### **Electrical Characteristics (continued)**

(Circuit of Figure 2,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = V_{CSSS} = V_{VHP} = 18V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = V_{BLKP} = 12V$ ,  $V_{REFIN} = 3.0V$ ,  $V_{ICTL} = 0.75 \times V_{REFIN}$ , VCTL = LDO, CELLS = FLOAT, GND = PGND = 0,  $V_{DLOV} = 5.4V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .) (Note 1)

| PARAMETER                                                          | CONDITIONS                                         | MIN   | TYP MAX | UNITS |  |

|--------------------------------------------------------------------|----------------------------------------------------|-------|---------|-------|--|

| SUPPLY AND LINEAR REGULAT                                          | OR                                                 |       |         |       |  |

| DCIN Input Voltage Range                                           |                                                    | 8     | 28      | V     |  |

|                                                                    | DCIN falling                                       | 4     |         | N N   |  |

| DCIN Undervoltage Lockout                                          | DCIN rising                                        |       | 7.85    | - V   |  |

| DCIN Quiescent Current                                             | 8.0V < V <sub>DCIN</sub> < 28V                     |       | 6       | mA    |  |

| BATT Input Voltage Range                                           |                                                    | 0     | 19      | V     |  |

| BATT Input Bias Current                                            | V <sub>BATT</sub> = 2V to 19V                      |       | 500     | μA    |  |

| LDO Output Voltage                                                 | No load                                            | 5.3   | 5.5     | V     |  |

| LDO Undervoltage Lockout                                           | V <sub>DCIN</sub> = 8V, LDO rising                 | 4.00  | 5.25    | V     |  |

| REFERENCE                                                          |                                                    |       |         |       |  |

| REF Output Voltage                                                 | I <sub>REF</sub> = 0μA                             | 4.060 | 4.132   | V     |  |

| REF Load Regulation                                                | 0 < I <sub>REF</sub> < 500μA                       |       | 10      | mV    |  |

| REF Undervoltage-Lockout Trip<br>Point                             | V <sub>REF</sub> falling                           |       | 3.9     | v     |  |

| REFIN Input Range                                                  |                                                    | 2.5   | 3.6     | V     |  |

| REFIN UVLO Rising                                                  |                                                    |       | 2.2     | V     |  |

| REFIN Input Bias Current                                           | V <sub>DCIN</sub> = 18V                            |       | 100     | μA    |  |

| SWITCHING REGULATOR                                                |                                                    |       |         | •     |  |

| Cycle-by-Cycle Step-Up Maximum<br>Current-Limit Sense Voltage      | V <sub>DCIN</sub> = 12V, V <sub>BATT</sub> = 16.8V | 130   | 170     | mV    |  |

| Cycle-by-Cycle Step-Down<br>Maximum Current-Limit Sense<br>Voltage | V <sub>DCIN</sub> = 19V, V <sub>BATT</sub> = 16.8V | 130   | 170     | mV    |  |

| Step-Down On-Time                                                  | V <sub>DCIN</sub> = 18V, V <sub>BATT</sub> = 16.8V | 2.2   | 2.6     | μs    |  |

| Minimum Step-Down Off-Time                                         | V <sub>DCIN</sub> = 18V, V <sub>BATT</sub> = 16.8V | 0.15  | 0.50    | μs    |  |

| Step-Up Off-Time                                                   | V <sub>DCIN</sub> = 12V, V <sub>BATT</sub> = 16.8V | 1.6   | 2.0     | μs    |  |

| Minimum Step-Up On-Time                                            | V <sub>DCIN</sub> = 12V, V <sub>BATT</sub> = 16.8V | 0.15  | 0.40    | μs    |  |

| MOSFET DRIVERS                                                     |                                                    |       |         |       |  |

| VHP - VHN Output Voltage                                           | 8V < V <sub>VHP</sub> < 28V, no load               | 4.5   | 5.5     | V     |  |

| VHN Load Regulation                                                | 0 < I <sub>VHN</sub> < 10mA                        |       | 150     | mV    |  |

| DHI On-Resistance High                                             | I <sub>SOURCE</sub> = 10mA                         |       | 5       | Ω     |  |

| DHI On-Resistance Low                                              | I <sub>SINK</sub> = 10mA                           |       | 3       | Ω     |  |

| VHP Input Bias Current                                             | V <sub>DCIN</sub> = 18V                            |       | 2       | mA    |  |

| BLKP Input Bias Current                                            | V <sub>ICTL</sub> = V <sub>REFIN</sub> = 3.3V      |       | 400     | μA    |  |

| DLOV Supply Current                                                | DBST low                                           |       | 10      | μA    |  |

| DBST On-Resistance High                                            | I <sub>SOURCE</sub> = 10mA                         |       | 5       | Ω     |  |

| DBST On-Resistance Low                                             | I <sub>SINK</sub> = 10mA                           |       | 3       | Ω     |  |

## Step-Up/Step-Down Li+ Battery Charger

### **Electrical Characteristics (continued)**

(Circuit of Figure 2,  $V_{DCIN} = V_{CSSP} = V_{CSSN} = V_{CSSS} = V_{VHP} = 18V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = V_{BLKP} = 12V$ ,  $V_{REFIN} = 3.0V$ ,  $V_{ICTL} = 0.75 \times V_{REFIN}$ , VCTL = LDO, CELLS = FLOAT, GND = PGND = 0,  $V_{DLOV} = 5.4V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .) (Note 1)

| PARAMETER                              | CONDITIONS                                                                                        | MIN             | TYP  | MAX  | UNITS         |

|----------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|------|------|---------------|

| ERROR AMPLIFIERS                       |                                                                                                   |                 |      |      |               |

| GMV Amplifier Loop<br>Transconductance | VCTL = REFIN, V <sub>BATT</sub> = 16.8V                                                           | 0.05            |      | 0.20 | µA/mV         |

| GMI Amplifier Loop<br>Transconductance | ICTL = REFIN, V <sub>CSIP</sub> - V <sub>CSIN</sub> = 72mV                                        | 1.8             |      | 3.0  | µA/mV         |

| GMS Amplifier Loop                     | $V_{CLS}$ = REF, $V_{CSSP}$ - $V_{CSSN}$ = 102mV, $V_{CSSP}$ = $V_{CSSS}$                         | 1.2             |      | 2.2  |               |

| Transconductance                       | $V_{CLS}$ = REF, $V_{CSSP}$ - $V_{CSSS}$ = 102mV, $V_{CSSP}$ = $V_{CSSN}$                         | 1.2             |      | 2.2  | µA/mV         |

|                                        | VCTL = REFIN, V <sub>BATT</sub> = 15.8V                                                           | 50              |      |      |               |

| CCV Output Current                     | VCTL = REFIN, V <sub>BATT</sub> = 17.8V                                                           |                 |      | -50  | μA            |

| COL Output Current                     | ICTL = REFIN, V <sub>CSIP</sub> - V <sub>CSIN</sub> = 0mV                                         | 150             |      |      |               |

| CCI Output Current                     | ICTL = REFIN, V <sub>CSIP</sub> - V <sub>CSIN</sub> = 150mV                                       |                 |      | -150 | μA            |

| CCS Output Current                     | CLS = REF, $V_{CSSP}$ = $V_{CSSN}$ , $V_{CSSP}$ = $V_{CSSS}$                                      | 100             |      |      |               |

|                                        | CLS = REF, $V_{CSSP}$ - $V_{CSSN}$ = 200mV,<br>$V_{CSSP}$ - $V_{CSSS}$ = 200mV                    |                 |      | -100 | μA            |

| CCI/CCS/CCV Clamp Voltage              | 1.1V < V <sub>CCV</sub> < 3.5V, 1.1V < V <sub>CCS</sub> < 3.5V,<br>1.1V < V <sub>CCI</sub> < 3.5V | 100             |      | 500  | mV            |

| LOGIC LEVELS                           |                                                                                                   |                 |      |      |               |

| ASNS Output-Voltage Low                | V <sub>IINP</sub> = GND, I <sub>SINK</sub> = 1mA                                                  |                 |      | 0.4  | V             |

| ASNS Output-Voltage High               | V <sub>IINP</sub> = 4V, I <sub>SOURCE</sub> = 1mA                                                 | LDO -<br>0.5    |      |      | V             |

| ASNS Current Detect                    | V <sub>IINP</sub> rising                                                                          | 1.1             | 1.15 | 1.2  | V             |

| SHDN Threshold                         | SHDN falling, V <sub>REFIN</sub> = 2.8V to 3.6V                                                   | 22              |      | 25   | % of<br>REFIN |

| CELLS Input Low Voltage                |                                                                                                   | 1               |      | 0.75 | V             |

| CELLS Float Voltage                    |                                                                                                   | 40              |      | 60   | % of<br>REFIN |

| CELLS Input High Voltage               |                                                                                                   | REFIN<br>-0.75V |      |      | V             |

**Note 1:** Specifications to -40°C are guaranteed by design, not production tested.

## Step-Up/Step-Down Li+ Battery Charger

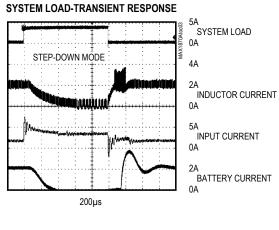

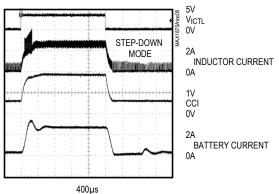

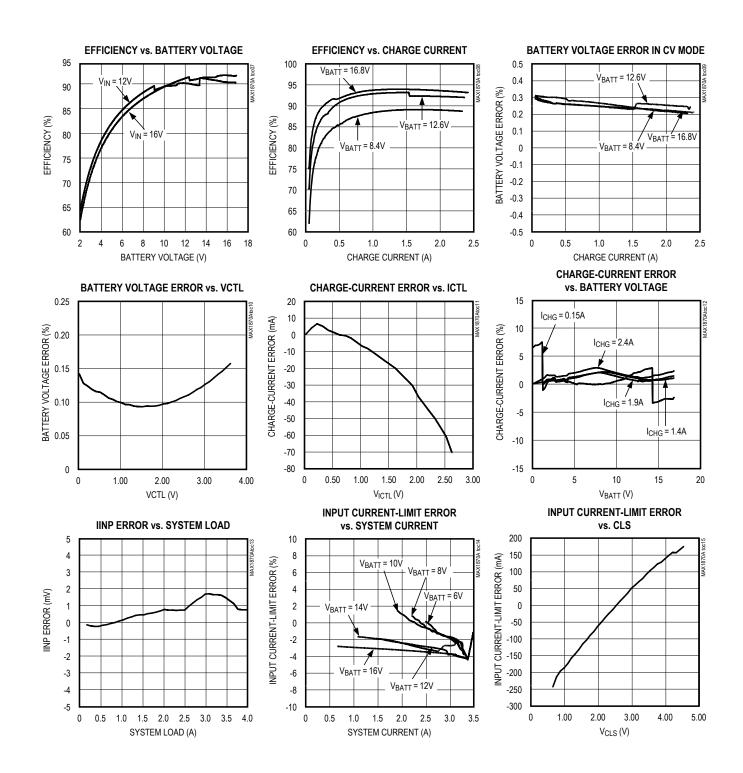

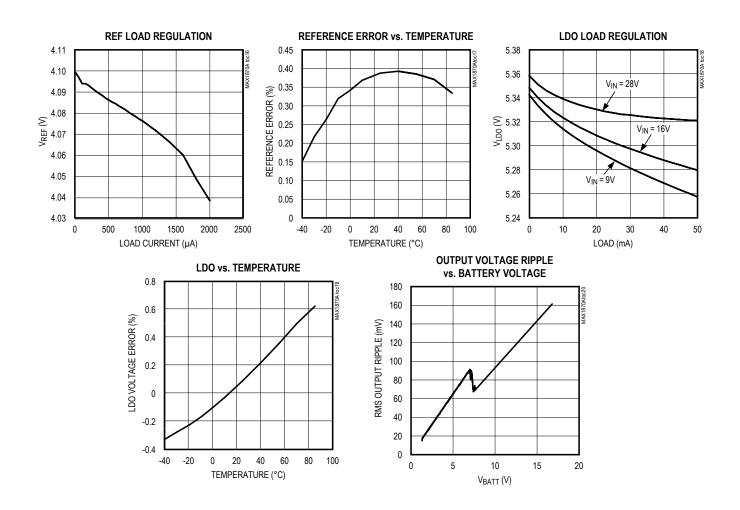

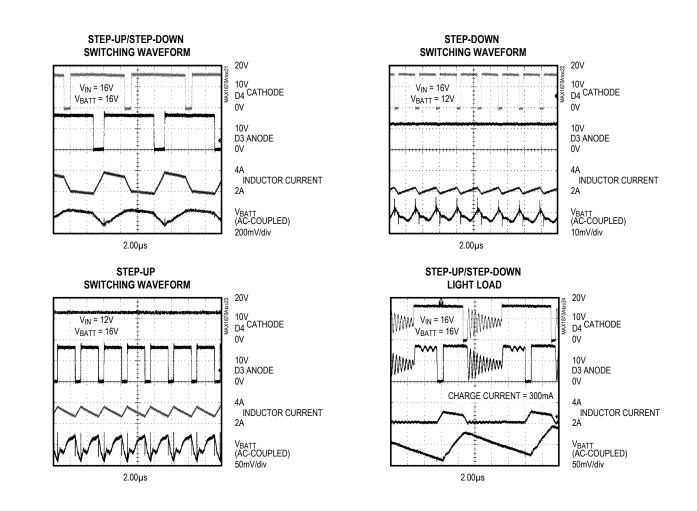

### **Typical Operating Characteristics**

(Circuit of Figure 1,  $V_{DCIN}$  = 16V, CELLS = REFIN,  $V_{CLS}$  =  $V_{REF}$ ,  $V_{ICTL}$  =  $V_{REFIN}$  = 3.3V,  $T_A$  = +25°C, unless otherwise noted.)

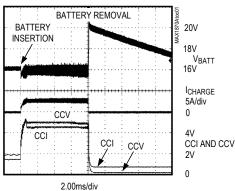

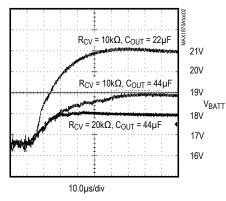

#### BATTERY INSERTION AND REMOVAL

#### CHARGE-CURRENT STEP RESPONSE

**BATTERY-REMOVAL RESPONSE**

#### CHARGE-CURRENT STEP RESPONSE

5V VICTL

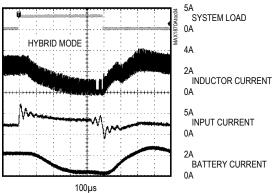

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, V<sub>DCIN</sub> = 16V, CELLS = REFIN, V<sub>CLS</sub> = V<sub>REF</sub>, V<sub>ICTL</sub> = V<sub>REFIN</sub> = 3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

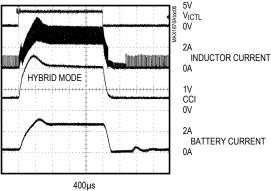

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{DCIN}$  = 16V, CELLS = REFIN,  $V_{CLS}$  =  $V_{REF}$ ,  $V_{ICTL}$  =  $V_{REFIN}$  = 3.3V,  $T_A$  = +25°C, unless otherwise noted.)

## Step-Up/Step-Down Li+ Battery Charger

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, V<sub>DCIN</sub> = 16V, CELLS = REFIN, V<sub>CLS</sub> = V<sub>REF</sub>, V<sub>ICTL</sub> = V<sub>REFIN</sub> = 3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Step-Up/Step-Down Li+ Battery Charger

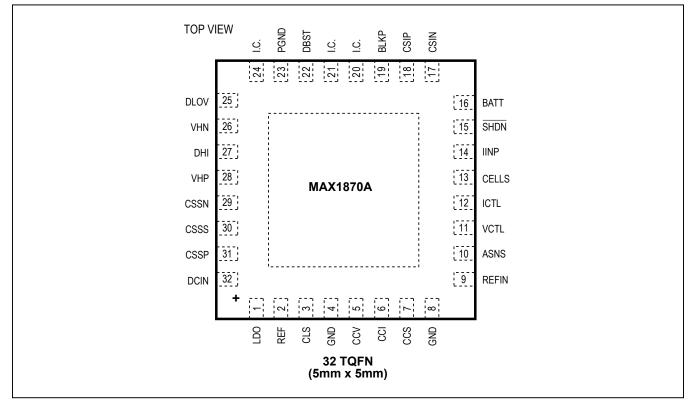

### **Pin Configuration**

### **Pin Description**

| PIN  | NAME  | FUNCTION                                                                                                                                                                                                            |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | LDO   | Device Power Supply. Output of the 5.4V linear regulator supplied from DCIN. Bypass LDO to GND with a $1\mu$ F or greater ceramic capacitor.                                                                        |

| 2    | REF   | 4.096V Voltage Reference. Bypass REF to GND with a $1\mu$ F or greater ceramic capacitor.                                                                                                                           |

| 3    | CLS   | Source Current-Limit Input. Voltage input for setting the current limit of the input source.<br>See the Setting the Input Current Limit section.                                                                    |

| 4, 8 | GND   | Analog Ground                                                                                                                                                                                                       |

| 5    | CCV   | Voltage Regulation Loop Compensation Point. Connect a $10k\Omega$ resistor in series with a $0.01\mu$ F capacitor to GND.                                                                                           |

| 6    | CCI   | Charge-Current Regulation Loop Compensation Point. Connect a 0.01µF capacitor to GND.                                                                                                                               |

| 7    | CCS   | Input-Current Regulation Loop Compensation Point. Connect a 0.01µF capacitor to GND.                                                                                                                                |

| 9    | REFIN | Reference Input. ICTL and VCTL are ratiometric with respect to REFIN for increased accuracy.                                                                                                                        |

| 10   | ASNS  | Adapter Sense Output. Logic output is high when input current is greater than 1.5A (using $30m\Omega$ sense resistors and a $10k\Omega$ resistor from IINP to GND).                                                 |

| 11   | VCTL  | Charge-Voltage Control Input. Drive VCTL from 0 to V <sub>REFIN</sub> to adjust the charge voltage from 4V to 4.4V per cell. See the <i>Setting the Charge Voltage</i> section.                                     |

| 12   | ICTL  | Charge-Current Control Input. Drive ICTL from V <sub>REFIN</sub> / 32 to V <sub>REFIN</sub> to adjust the charge current. See the <i>Setting the Charge Current</i> section. Drive ICTL to GND to disable charging. |

## Step-Up/Step-Down Li+ Battery Charger

## **Pin Description (continued)**

| PIN    | NAME   | FUNCTION                                                                                                                                                                                                                                      |  |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13     | CELLS  | Cell-Count Selection Input. Connect CELLS to GND for two Li+ cells. Float CELLS for three Li+ cells, or connect CELLS to REFIN for four Li+ cells.                                                                                            |  |

| 14     | IINP   | Input-Current Monitor Output. IINP is a replica of the input current sensed by the MAX1870. It represents the sum of the current consumed by the charger and the current consumed by the system IINP has a transconductance of $2.8\mu$ A/mV. |  |

| 15     | SHDN   | Shutdown Comparator Input. Pull SHDN low to stop charging. Optionally connect a thermistor to stop charging when the battery temperature is too hot.                                                                                          |  |

| 16     | BATT   | Battery-Voltage Feedback Input                                                                                                                                                                                                                |  |

| 17     | CSIN   | Charge Current-Sense Negative Input                                                                                                                                                                                                           |  |

| 18     | CSIP   | Charge Current-Sense Positive Input. Connect a current-sense resistor from CSIP to CSIN.<br>Connect a 2.2µF capacitor from CSIP to GND.                                                                                                       |  |

| 19     | BLKP   | Power Connection for Current-Sense Amplifier. Connect BLKP to BATT.                                                                                                                                                                           |  |

| 20, 21 | I.C.   | Internally Connected. Do not connect this pin.                                                                                                                                                                                                |  |

| 22     | DBST   | Step-Up Power MOSFET (NMOS) Gate-Driver Output                                                                                                                                                                                                |  |

| 23     | PGND   | Power Ground                                                                                                                                                                                                                                  |  |

| 24     | I.C.   | Internally Connected. Do not connect this pin.                                                                                                                                                                                                |  |

| 25     | DLOV   | Low-Side Driver Supply. Bypass DLOV with a 1µF capacitor to GND.                                                                                                                                                                              |  |

| 26     | VHN    | Power Connection for the High-Side MOSFET Driver. Bypass VHP to VHN with a $1\mu$ F or greater ceramic capacitor.                                                                                                                             |  |

| 27     | DHI    | High-Side Power MOSFET (PMOS) Driver Output. Connect to the gate of the high-side step-down MOSFET.                                                                                                                                           |  |

| 28     | VHP    | Power Connection for the High-Side MOSFET Driver. Bypass VHP to VHN with a $1\mu$ F or greater ceramic capacitor.                                                                                                                             |  |

| 29     | CSSN   | Negative Terminal for Current-Sense Resistor for Charger Current. Connect a 2.2µF capacitor from CSSN to GND.                                                                                                                                 |  |

| 30     | CSSS   | Negative Terminal for Current-Sense Resistor for System Load Current                                                                                                                                                                          |  |

| 31     | CSSP   | Positive Terminal for Input Current-Sense Resistors. Connect a current-sense resistor from CSSP to CSSN. Connect an equivalent sense resistor from CSSP to CSSS.                                                                              |  |

| 32     | DCIN   | DC Supply Voltage Input. Bypass DCIN with a 1µF or greater ceramic capacitor to power ground.                                                                                                                                                 |  |

| _      | Paddle | Paddle. Connect to GND.                                                                                                                                                                                                                       |  |

## Step-Up/Step-Down Li+ Battery Charger

Figure 1. µC-Controlled Typical Application Circuit

## Step-Up/Step-Down Li+ Battery Charger

Figure 2. Stand-Alone Typical Application Circuit

#### **Detailed Description**

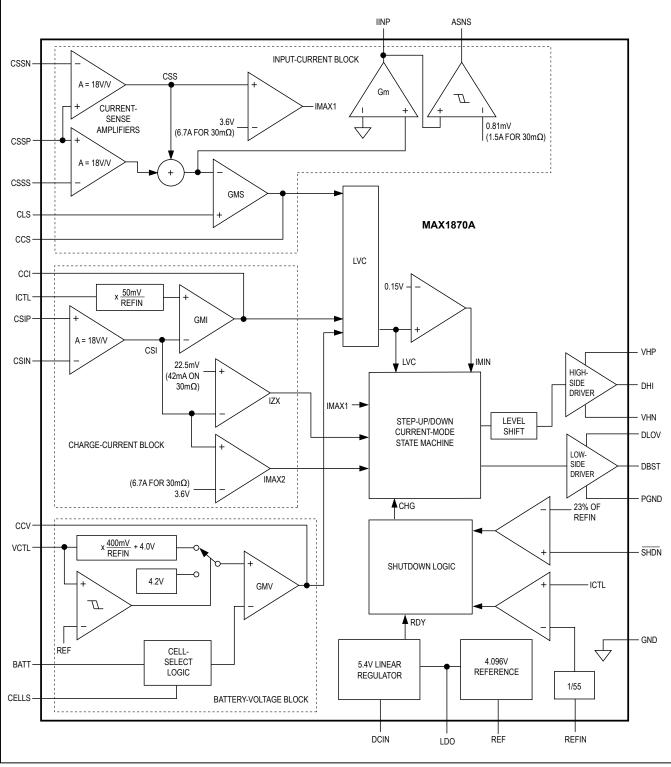

The MAX1870A includes all of the functions necessary to charge Li+, NiMH, and NiCd batteries. A high-efficiency H-bridge topology DC-DC converter controls charge voltage and current. A proprietary control scheme offers improved efficiency and smaller inductor size compared to conventional H-bridge controllers and operates from input voltages above and below the battery voltage. The MAX1870A includes analog control inputs to limit the AC adapter current, charge current, and battery voltage. An analog output (IINP) delivers a current proportional to the source current. The Typical Application Circuit shown in Figure 1 uses a microcontroller (µC) to control the charge current or voltage, while Figure 2 shows a typical application with the charge voltage and current fixed to specific values for the application. The voltage at ICTL and the value of RS2 set the charge current. The voltage at VCTL and the CELLS inputs set the battery regulation voltage for the charger. The voltage at CLS and the value of R3 and R4 set the source current limit.

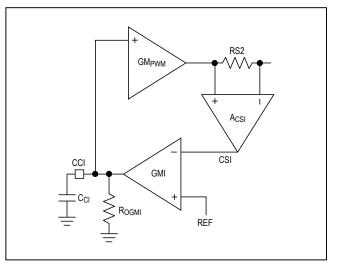

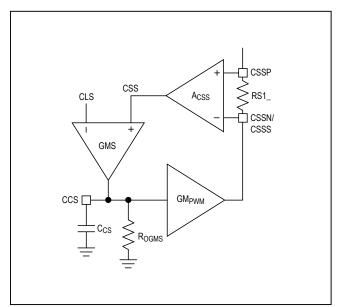

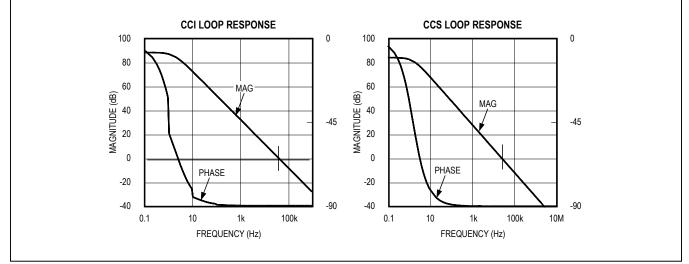

The MAX1870A features a voltage-regulation loop (CCV) and two current-regulation loops (CCI and CCS). CCV is the compensation point for the battery voltage regulation loop. CCI and CCS are the compensation points for the battery charge current and supply current loops, respectively. The MAX1870A regulates the adapter current by reducing battery charge current according to system load demands.

#### Setting the Charge Voltage

The MAX1870A provides high-accuracy regulation of the charge voltage. Apply a voltage to VCTL to adjust the battery-cell voltage limit. Set VCTL to a voltage between 0 and V<sub>REFIN</sub> for a 10% adjustment of the battery cell voltage, or connect VCTL to LDO for a default setting of 4.2V per cell. The limited adjustment range reduces the sensitivity of the charge voltage to external resistor tolerances. The overall accuracy of the charge voltage is better than  $\pm 1\%$  when using  $\pm 1\%$  resistors to divide down the reference to establish VCTL. The per-cell battery-termination voltage is a function of the battery chemistry and construction. Consult the battery voltage using the following equation:

$$V_{BATT} = N_{CELLS} x \left( 4V + 0.4V x \frac{V_{VCTL}}{V_{REFIN}} \right)$$

where N<sub>CELLS</sub> is the cell count selected by CELLS. VCTL is ratiometric with respect to REFIN to improve accuracy when using resistive voltage-dividers. Connect CELLS as

#### Table 1. Cell Connections

| CELLS | CELL COUNT |

|-------|------------|

| GND   | 2          |

| Float | 3          |

| REFIN | 4          |

shown in <u>Table 1</u> to charge two, three, or four cells. The cell count can either be hard-wired or software controlled. The internal error amplifier (GMV) maintains voltage regulation (see Figure 3 for the *Functional Diagram*). Connect a 10k $\Omega$  resistor in series with a 0.01 $\mu$ F capacitor from CCV to GND to compensate the battery voltage loop. See the <u>Voltage Loop Compensation</u> section for more information.

#### **Setting the Charge Current**

Set the maximum charge current using ICTL and the current-sense resistor RS2 connected between CSIP and CSIN. The current threshold is set by the ratio of  $V_{ICTL}$  /  $V_{REFIN}$ . Use the following equation to program the battery charge current:

$$I_{CHG} = \frac{V_{CSIT}}{R_{S2}} \times \frac{V_{ICTL}}{V_{REFIN}}$$

where V<sub>CSIT</sub> is the full-scale charge current-sense threshold, 73mV (typ). The input range for ICTL is V<sub>REFIN</sub> / 32 to V<sub>REFIN</sub>. To shut down the MAX1870A, force ICTL below V<sub>REFIN</sub> / 100.

The internal error amplifier (GMI) maintains chargecurrent regulation (see Figure 3 for the Functional Diagram). Connect a  $0.01\mu$ F capacitor from CCI to GND to compensate the charge-current loop. See the <u>Charge-Current and Wall-Adapter-Current</u> Loop Compensation section for more information.

#### Setting the Input-Current Limit

The total input current, from a wall adapter or other DC source, is a function of the system supply current and the battery charge current. The MAX1870A limits the wall adapter current by reducing the charge current when the input current exceeds the input current-limit set point. As the system supply current rises, the available charge current decreases linearly to zero in proportion to the system current. After the charge current has fallen to zero, the MAX1870A cannot further limit the wall adapter current if the system current continues to increase.

## Step-Up/Step-Down Li+ Battery Charger

Figure 3. Functional Diagram

The input source current is the sum of the MAX1870A quiescent current, the charger input current, and the system load current. The MAX1870A's 6mA maximum quiescent current is minimal compared to the charge and load currents. The actual wall adapter current is determined as follows:

$I_{ADAPTER} = I_{SYS\_LOAD} + \frac{I_{CHARGE x V_{BATT}}}{V_{IN} x \eta}$

where  $\eta$  is the efficiency of the DC-DC converter (85% to 95% typ),  $I_{SYS\_LOAD}$  is the system load current,  $I_{ADAPTER}$  is the adapter current, and  $I_{CHARGE}$  is the charge current.

By controlling the input current, the current requirements of the AC wall adapter are reduced, minimizing system size and cost. Since charge current is reduced to control input current, priority is given to system loads.

An internal amplifier compares the sum of ( $V_{CSSP}$  -  $V_{CSSN}$ ) and ( $V_{CSSP}$  -  $V_{CSSS}$ ) to a scaled voltage set by the CLS input. Drive  $V_{CLS}$  directly or set with a resistive voltage-divider between REF and GND. Connect CLS to REF for the maximum input current limit of 105mV. Sense resistors RS1a and RS1b set the maximum-allowable wall adapter current. Use the same values for RS1a, RS1b, and RS2. Calculate the maximum wall adapter current as follows:

$$\mathsf{I}_{\mathsf{ADAPTER}_\mathsf{MAX}} = \frac{\mathsf{V}_{\mathsf{CLS}}}{\mathsf{V}_{\mathsf{REF}}} \times \frac{\mathsf{V}_{\mathsf{CSST}}}{\mathsf{RS1}_{\mathsf{EST}}}$$

where V<sub>CSST</sub> is the full-scale source current-sense voltage threshold, and is 105mV (typ). The internal error amplifier (GMS) maintains input-current regulation (see Figure 3 for the *Functional Diagram*). Typically, connect a  $0.01\mu$ F capacitor from CCS to GND to compensate the source current loop (GMS). See the <u>Charge-Current and Wall-Adapter-Current</u> Loop Compensation section for more information.

#### Input-Current Measurement

The MAX1870A includes an input-current monitor output, IINP. IINP is a scaled-down replica of the system load current plus the input-referred charge current. The output voltage range for IINP is 0 to 3.5V. The voltage of IINP is proportional to the output current by the following equation:

$$V_{\text{IINP}} = I_{\text{ADAPTER}} \times \text{RS1}_{\times} G_{\text{IINP}} \times \text{R7}$$

where  $I_{ADAPTER}$  is the DC current supplied by the AC adapter,  $G_{IINP}$  is the transconductance of IINP (2.8µA/mV typ), and R7 is the resistor connected between IINP and ground.

In the *Typical Application Circuit*, the duty cycle and AC load current affect the accuracy of V<sub>IINP</sub> (see the <u>Typical</u> *Operating Characteristics*).

#### LDO Regulator

LDO provides a 5.4V supply derived from DCIN. The lowside MOSFET driver is powered by DLOV, which must be connected to LDO as shown in Figure 1. LDO also supplies the 4.096V reference (REF) and most of the internal control circuitry. Bypass LDO to GND with a 1 $\mu$ F or greater ceramic capacitor. Bypass DLOV to PGND with a 1 $\mu$ F or greater ceramic capacitor.

#### **AC-Adapter Detection**

The MAX1870A includes a logic output, ASNS, which indicates AC adapter presence. When the system load draws more than 1.5A (for  $30m\Omega$  sense resistors and R7 is  $10k\Omega$ ), the ASNS logic output pulls high.

#### Shutdown

When the AC adapter is removed, the MAX1870A shuts down to a low-power state, and typically consumes less than 1 $\mu$ A from the battery through the combined load of the CSIP, CSIN, BLKP, and BATT inputs. The charger enters this low-power state when DCIN falls below the undervoltage-lockout (UVLO) threshold of 7.5V.

Alternatively, drive SHDN below 23.5% of  $V_{REFIN}$  or drive ICTL below  $V_{REFIN}$  / 100 to inhibit charge. This suspends switching and pulls CCI, CCS, and CCV to ground. The LDO, input current monitor, and control logic all remain active in this state.

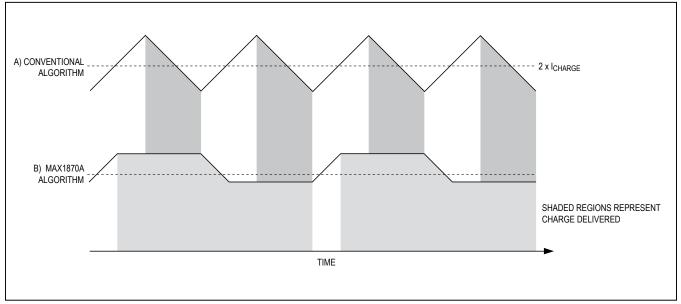

### Step-Up/Step-Down DC-DC Controller

The MAX1870A is a step-up/step-down DC-DC controller. The MAX1870A controls a low-side n-channel MOSFET and a high-side p-channel MOSFET to a constant output voltage with input voltage variation above, near, and below the output. The MAX1870A implements a control scheme that delivers higher efficiency with smaller components and less output ripple when compared with other step-up/step-down control algorithms. This occurs because the MAX1870A operates with lower inductor currents, as shown in Figure 4.

The MAX1870A proprietary algorithm offers the following benefits:

- Inductor current requirements are minimized.

- Low inductor-saturation current requirements allow the use of physically smaller inductors.

- Low inductor current improves efficiency by reducing I<sup>2</sup>R losses in the MOSFETs, inductor, and sense resistors.

Continuous output current for V<sub>IN</sub> > 1.4 x V<sub>OUT</sub> reduces output ripple.

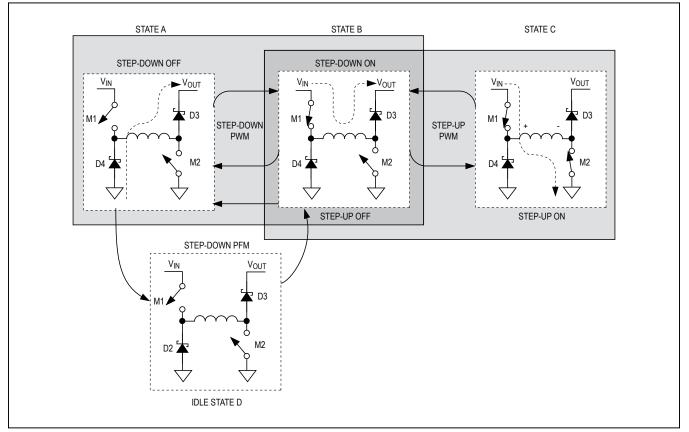

The MAX1870A uses the state machine shown in Figure 5. The controller switches between the states A, B, and C, depending on  $V_{IN}$  and  $V_{BATT}$ . State D provides PFM operation during light loads. Under moderate and heavy loads the MAX1870A operates in PWM.

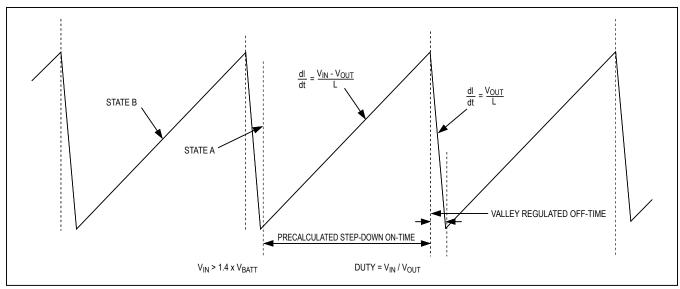

#### Step-Down Operation (VIN > 1.4 x VBATT)

During medium and heavy loads when  $V_{IN} > 1.4 \times V_{BATT}$ , the MAX1870A alternates between state A and state B, keeping MOSFET M2 off (Figure 5). Figure 6 shows the inductor current in step-down operation. During this mode, the MAX1870A regulates the step-down off-time. Initially, DHI switches M1 off (state A) and the inductor current ramps down with a dl/dt of  $V_{BATT}$  / L until a target current is reached (determined by the error integrator). After the target current is reached, DHI switches M1 on (state B), and the inductor current ramps up with a dl/dt

of  $(V_{IN} - V_{BATT}) / L$ . M1 remains on until a step-down on-time timer expires. This on-time is calculated based on the input and output voltage to maintain pseudofixed-frequency 400kHz operation. At the end of state B, another step-down off-time (state A) is initiated and the cycle repeats. The off-time is valley regulated according to the error signal. The error signal is set by the charge current or source current if either is at its limit, or the battery voltage if both charge current and source current are below their respective current limits.

During light loads, when the inductor current falls to zero during state A, the controller switches to state D to reduce power consumption and avoid shuttling current in and out of the output.

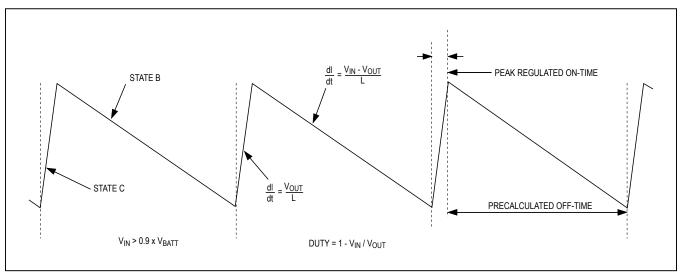

#### Step-Up Operation (VIN < 0.9 x VBATT)

When  $V_{IN} < 0.9 \times V_{BATT}$ , the MAX1870A alternates between state B and state C, keeping MOSFET M1 on. In this mode, the controller looks like a simple step-up controller. Figure 7 shows the inductor current in step-up

#### Table 2. MAX1870A H-Bridge Controller Advantages

| MAX1870A H-BRIDGE CONTROLLER                                                                           | TRADITIONAL H-BRIDGE CONTROLLER                                                                                                       |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>Only 1 MOSFET switched per cycle</li><li>Continuous output current in step-down mode</li></ul> | <ul> <li>2 MOSFETs switched per cycle</li> <li>Always discontinuous output current<br/>(requires higher inductor currents)</li> </ul> |

Figure 4. Inductor Current for  $V_{IN} = V_{BATT}$

operation. During this mode, the MAX1870A regulates the step-up on-time. Initially DBST switches M2 on (state C) and the inductor current ramps up with a dl/dt of V<sub>IN</sub> / L. After the inductor current crosses the target current (set by the error integrators), DBST switches M2 off (state B) and the inductor current ramps down with a dl/dt of (V<sub>BATT</sub> - V<sub>IN</sub>) / L. M2 remains off until a step-up off-time timer expires. This off-time is calculated based on the input and output voltage to maintain 400kHz pseudo-fixed-frequency operation. The step-up on-time is regulated by the error signal, set according to the charge current or source current if either is at its limit, or the battery voltage if both charge current and source current are below their respective current limits.

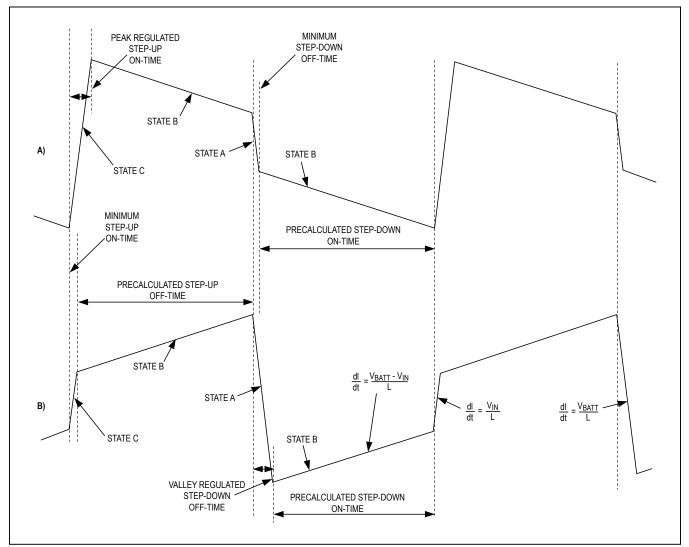

#### Step-Up/Step-Down Operation (0.9 x V<sub>BATT</sub> < V<sub>IN</sub> < 1.4 x V<sub>BATT</sub>)

The MAX1870A features a step-up/step-down mode that eliminates dropout. Figure 8 shows the inductor current in step-up/step-down operation. When V<sub>IN</sub> is within 10% of V<sub>BATT</sub>, the MAX1870A alternates through states A, B,

and C, following the order A, B, C, B, A, B, C, etc., with the majority of the time spent in state B. Since more time is spent in state B, the inductor ripple current is reduced, improving efficiency.

The time in state C is peak-current regulated, and the remaining time is spent in state B (Figure 8A). During this operating mode, the average inductor current is approximately 20% higher than the load current.

The time in state A is valley current and the remaining time is spent in state B (Figure 8B). During this mode, the average inductor current is approximately 10% higher than the load current.

Alternative algorithms require inductor currents twice as high, resulting in four times larger I<sup>2</sup>R losses and inductors typically four times larger in volume.

#### IMIN, IMAX, CCMP, and ZCMP

The MAX1870A state machine utilizes five comparators to decide which state to be in and when to switch states (Figure 3). The MAX1870A generates an error signal

Figure 5. MAX1870A State Machine

## Step-Up/Step-Down Li+ Battery Charger

Figure 6. MAX1870A Step-Down Inductor Current Waveform

Figure 7. Step-Up Inductor-Current Waveform

based on the integrated error of the input current, charge current, and battery voltage. The error signal, determined by the lowest voltage clamp (LVC), sets the threshold for current-mode regulation. The following comparators are used for regulation:

IMIN: The MAX1870A operates in discontinuous conduction if LVC is below 0.15V, and does not initiate another step-down on-time. In discontinuous step-up conduction, the peak current is set by IMIN. The peak inductor current in discontinuous step-up mode:

$$I_{PK} > \frac{V_{IMIN}}{A_{CSI} \times RS2}$$

where VIMIN is the IMIN comparator threshold, 0.15V, and ACSI is the charge current-sense amplifier gain, 18V/V.

## Step-Up/Step-Down Li+ Battery Charger

- CCMP: CCMP compares the current-mode control point, LVC, to the inductor current. In step-down mode, the off-time (state A) is terminated when the inductor current falls below the current threshold set by LVC. In step-up mode, the on-time (state C) is terminated when the inductor current rises above the current threshold set by LVC.

- IMAX: The IMAX comparators provide a cycle-bycycle inductor current limit. This circuit compares the inductor current (CSI in step-down mode or CSS in

step-up mode) to the internally fixed cycle-by-cycle current limit. The current-sense voltage limit is 200mV. With RS1\_ = RS2 =  $30m\Omega$ , which corresponds to 6.7A. If the inductor current-sense voltage is greater than V<sub>IMAX</sub> (200mV), a step-up on-time is terminated or a step-down on-time is not permitted.

• ZCMP: The ZCMP comparator detects when the inductor current crosses zero. If the ZCMP output goes high during a step-down off-time, the MAX1870A switches to the idle state (state D) to conserve power.

Figure 8. MAX1870A Step-Up/Step-Down Inductor-Current Waveform

#### Switching Frequency

The MAX1870A includes input and output-voltage feedforward to maintain pseudo-fixed-frequency (400kHz) operation. The time in state B is set according to the input voltage, output voltage, and a time constant. In step-up/ step-down mode the switching frequency is effectively cut in half to allow for both the step-up cycle and the stepdown cycle. The switching frequency is typically between 350kHz and 405kHz for V<sub>IN</sub> between 8V and 28V. See the *Typical Operating Characteristics*.

#### Compensation

Each of the three regulation loops (the battery voltage, the charge current, and the input current limit) are compensated separately using the CCV, CCI, and CCS pins, respectively. Compensate the voltage regulation loop with a 10k $\Omega$  resistor in series with a 0.01µF capacitor from CCV to GND. Compensate the charge current loop and source current loop with 0.01µF capacitors from CCI to GND and from CCS to GND, respectively.

#### **Voltage Loop Compensation**

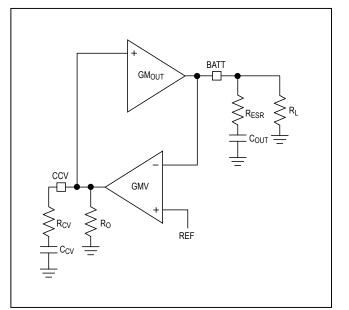

When regulating the charge voltage, the MAX1870A behaves as a current-mode step-down or step-up power supply. Since a current-mode controller regulates its output current as a function of the error signal, the duty-cycle modulator can be modeled as a GM stage (Figure 9). Results are similar in step-down, step-up, or step-up/down, with the exception of a load-dependent right-half-plane zero that occurs in step-up mode.

The required compensation network is a pole-zero pair formed with  $C_{CV}$  and  $R_{CV}$ .  $C_{CV}$  is chosen to be large enough that its impedance is relatively small compared to  $R_{CV}$  at frequencies near crossover.  $R_{CV}$  sets the gain of the error amplifier near crossover.  $R_{CV}$  and  $C_{OUT}$  determine the crossover frequency and, therefore, the closed-loop response of the system and the response time upon battery removal.

$R_{ESR}$  is the equivalent series resistance (ESR) of the charger's output capacitor ( $C_{OUT}$ ).  $R_L$  is the equivalent charger output load,  $R_L$  =  $\Delta V_{BATT}$  /  $\Delta I_{CHG}$  =  $R_{BATT}$ . The equivalent output impedance of the GMV amplifier,  $R_{OGMV}$ , is greater than 10M $\Omega$ . The voltage loop transconductance (GMV =  $\Delta I_{CCV}$  /  $\Delta V_{BATT}$ ) scales inversely with the number of cells. GMV = 0.1µA/mV for four cells, 0.133µA/mV for three cells, and 0.2µA/mV for two cells. The DC-DC converter's transconductance depends upon the charge current-sense resistor RS2:

$$GM_{PWM} = \frac{1}{A_{CSI} \times RS2}$$

where  $A_{CSI}$  = 18, and RS2 = 30m $\Omega$  in Figure 1 and 2 so GM<sub>PWM</sub> = 1.85A/V.

Use the following equation to calculate the loop transfer function (LTF):

$$LTF = GM_{PWM} \times \frac{R_{OGMV} \times (1 + sC_{CV} R_{CV})}{(1 + sC_{CV} \times R_{OGMV})} \times \frac{R_L}{(1 + sC_{OUT} \times R_{ESR})} \times G_{MV} \times (1 + sC_{OUT} \times R_{ESR})$$

The poles and zeros of the voltage-loop transfer function are listed from lowest frequency to highest frequency in Table 3.

Near crossover,  $C_{CV}$  has much lower impedance than  $R_{OGMV}$ . Since  $C_{CV}$  is in parallel with  $R_{OGMV}$ ,  $C_{CV}$  dominates the parallel impedance near crossover. Additionally,  $R_{CV}$  has a much higher impedance than  $C_{CV}$  and dominates the series combination of  $R_{CV}$  and  $C_{CV}$ , so:

$$\frac{R_{OGMV} \times (1 + sC_{CV} \times R_{CV})}{(1 + sC_{CV} \times R_{OGMV})} \cong R_{CV}, \text{ near crossover}$$

$C_{OUT}$  also has a much lower impedance than  $\mathsf{R}_L$  near crossover, so the parallel impedance is mostly capacitive and:

$$\frac{\mathsf{R}_{\mathsf{L}}}{(1+\mathsf{s}\mathsf{C}_{\mathsf{OUT}}\,\mathsf{x}\,\mathsf{R}_{\mathsf{L}})} \cong \frac{1}{\mathsf{s}\mathsf{C}_{\mathsf{OUT}}}$$

If  $R_{ESR}$  is small enough, its associated output zero has a negligible effect near crossover and the loop transfer function can be simplified as follows:

Figure 9. CCV Simplified Loop Diagram

Step-Up/Step-Down Li+ Battery Charger

$$LTF = GM_{PWM} \times \frac{R_{CV}}{sC_{OUT}} G_{MV}$$

Setting the LTF = 1 to solve for the unity-gain frequency yields:

$$f_{CO_CV} = GM_{PWM} \times G_{MV} \left( \frac{R_{CV}}{2\pi \times C_{OUT}} \right)$$

For stability, choose a crossover frequency lower than 1/10th of the switching frequency. The crossover frequency must also be below the RHP zero, calculated at maximum charge current, minimum input voltage, and maximum battery voltage.

Choosing a crossover frequency of 13kHz and solving for  $R_{CV}$  using the component values listed in Figure 1 yields:

| $GMV = 0.1 \mu A/mV$        |

|-----------------------------|

| GM <sub>PWM</sub> = 1.85A/V |

| f <sub>CO_CV</sub> = 13kHz  |

| f <sub>OSC</sub> = 400kHz   |

|                             |

$$R_{CV} = \frac{2\pi x C_{OUT} x f_{CO} CV}{GMV x GM_{PWM}} = 10 k\Omega$$

To ensure that the compensation zero adequately cancels the output pole, select  $f_{Z CV} \le f_{P OUT}$ .

$$C_{CV} \ge (R_L / R_{CV}) \times C_{OUT}$$

$C_{CV} \ge 440 pF$

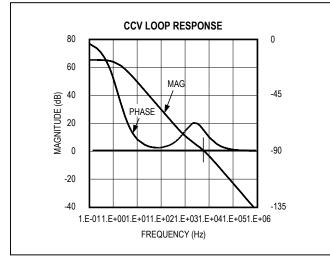

Figure 10 shows the Bode Plot of the voltage-loop frequency response using the values calculated above.

# Charge-Current and Wall-Adapter-Current Loop Compensation