HALOGEN

FREE

# 2.8 V to 5.5 V Input 5 A Synchronous Buck Regulator

#### **DESCRIPTION**

The SiP12108 is a high frequency current-mode constant on-time (CM-COT) synchronous buck regulator with integrated high-side and low-side power MOSFETs. Its power stage is capable of supplying 5 A continuous current at 4 MHz switching frequency. This regulator produces an adjustable output voltage down to 0.6 V from 2.8 V to 5.5 V input rail to accommodate a variety of applications, including computing, consumer electronics, telecom, and industrial.

SiP12108's CM-COT architecture delivers ultra-fast transient response with minimum output capacitance and tight ripple regulation at very light load. The part is stable with any capacitor type and no ESR network is required for loop stability. The device also incorporates a power saving scheme that significantly increases light load efficiency.

The SiP12108 integrates a full protection feature set, including output overvoltage protection (OVP), output under voltage protection (UVP) and thermal shutdown (OTP). The "A" version of the device, SiP12108A, does not have the UVP feature. They also incorporate UVLO for the input rail and an internal soft-start ramp.

The SiP12108 is available in lead (Pb)-free power enhanced 3 mm x 3 mm QFN-16 package.

#### **FEATURES**

- 2.8 V to 5.5 V input voltage

- Adjustable output voltage down to 0.6 V

- 5 A continuous output current

- Programmable switching frequency up to 4 MHz

- 95 % peak efficiency

- Stable with any capacitor. No external ESR network required.

- Ultrafast transient response

- Selectable power saving (PSM) mode or forced continuous mode

- ± 1 % accuracy of V<sub>OUT</sub> setting

- Pulse-by-pulse current limit

- Scalable with SiP12107 3 A

- SiP12108 is fully protected with OTP, SCP, UVP, OVP

- SiP12108A is fully protected with OTP, SCP, OVP

- PGOOD Indicator

- PowerCAD Simulation software available at vishay.transim.com/login.aspx

- Material categorization: For definitions of compliance please see <a href="https://www.vishay.com/doc?99912"><u>www.vishay.com/doc?99912</u></a>

#### **APPLICATIONS**

- Point of load regulation for low-power processors, network processors, DSPs, FPGAs, and ASICs

- Low voltage, distributed power architectures with 3.3 V or 5 V rails

- Computing, broadband, networking, LAN/WAN, optical, test and measurement

- A/V, high density cards, storage, DSL, STB, DVR, DTV, Industrial PC

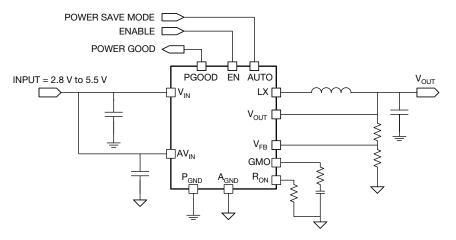

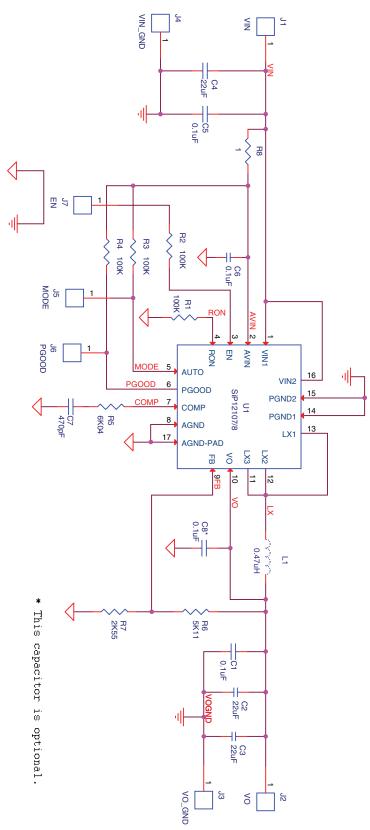

#### TYPICAL APPLICATION CIRCUIT

Fig. 1 - Typical Application Circuit for SiP12108

Vishay Siliconix

| ABSOLUTE MAXIMUM RATINGS                                   |                               |                                |      |  |  |  |

|------------------------------------------------------------|-------------------------------|--------------------------------|------|--|--|--|

| ELECTRICAL PARAMETER                                       | CONDITIONS                    | LIMIT                          | UNIT |  |  |  |

| V <sub>IN</sub>                                            | Reference to P <sub>GND</sub> | -0.3 to 6                      |      |  |  |  |

| AV <sub>IN</sub>                                           | Reference to A <sub>GND</sub> | -0.3 to 6                      |      |  |  |  |

| LX                                                         | Reference to P <sub>GND</sub> | -0.3 to 6                      | V    |  |  |  |

| A <sub>GND</sub> to P <sub>GND</sub>                       |                               | -0.3 to +0.3                   |      |  |  |  |

| All Logic Inputs                                           | Reference to A <sub>GND</sub> | -0.3 to AV <sub>IN</sub> + 0.3 |      |  |  |  |

| TEMPERATURE                                                |                               |                                |      |  |  |  |

| Max. Operating Junction Temperature                        |                               | 150                            | °C   |  |  |  |

| Storage Temperature                                        |                               | -65 to 150                     |      |  |  |  |

| POWER DISSIPATION                                          |                               |                                |      |  |  |  |

| Junction to Ambient Thermal Impedance (R <sub>thJA</sub> ) |                               | 36.3                           | °C/W |  |  |  |

| Maximum Power Dissipation                                  | Ambient temperature = 25 °C   | 3.4                            | W    |  |  |  |

| waximum rower bissipation                                  | Ambient temperature = 100 °C  | 1.3                            | VV   |  |  |  |

| ESD PROTECTION                                             |                               |                                |      |  |  |  |

|                                                            | НВМ                           | 4                              | kV   |  |  |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE |         |           |                        |      |  |

|-----------------------------|---------|-----------|------------------------|------|--|

| ELECTRICAL PARAMETER        | MINIMUM | TYPICAL   | MAXIMUM                | UNIT |  |

| V <sub>IN</sub>             | 2.8     | -         | 5.5                    |      |  |

| AV <sub>IN</sub>            | 2.8     | -         | 5.5                    | V    |  |

| LX                          | -1      | -         | 5.5                    |      |  |

| V <sub>OUT</sub>            | 0.6     | -         | 0.85 x V <sub>IN</sub> |      |  |

| Ambient Temperature         |         | -40 to 85 |                        | °C   |  |

|                                            |                                | TEST CONDITION                                                                                                     | LIMITS |       |       |      |  |

|--------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------|--------|-------|-------|------|--|

| PARAMETER                                  | SYMBOL                         | UNLESS OTHERWISE SPECIFIED $V_{IN} = AV_{IN} = 3.3 \text{ V}, T_A = -40 ^{\circ}\text{C}$ to 85 $^{\circ}\text{C}$ | MIN.   | TYP.  | MAX.  | UNIT |  |

| POWER SUPPLY                               |                                |                                                                                                                    |        | •     |       |      |  |

| Power Input Voltage Range                  | $V_{IN}$                       |                                                                                                                    | 2.8    | -     | 5.5   | V    |  |

| Bias Input Voltage Range                   | AV <sub>IN</sub>               |                                                                                                                    | 2.8    | -     | 5.5   | '    |  |

| Input Current                              | I <sub>IN_NOLOAD</sub>         | $I_{\text{IN\_NOLOAD}}$ Non- switching, $I_{\text{O}} = 0$ A, $R_{\text{on}} = 100 \text{ k}\Omega$ , AUTO = Low   |        | 1200  | -     | μA   |  |

| Shutdown Current                           | I <sub>IN_SHDN</sub>           | EN = 0 V                                                                                                           | -      | 6     | 9.5   |      |  |

| AV <sub>IN</sub> UVLO Threshold            | AV <sub>IN_UVLO</sub>          | AV <sub>IN</sub> rising                                                                                            | 2.3    | 2.55  | 2.8   | V    |  |

| AV <sub>IN</sub> UVLO Hysteresis           | AV <sub>IN_UVLO_HYS</sub>      |                                                                                                                    | -      | 300   | -     | m۷   |  |

| PWM CONTROLLER                             |                                |                                                                                                                    |        |       |       |      |  |

| Feedback Reference                         | V                              | T <sub>A</sub> = 0 °C to +70 °C                                                                                    | 0.594  | 0.600 | 0.606 | V    |  |

| reeuback neierence                         | V <sub>FB</sub>                | T <sub>A</sub> = -40 °C to +85 °C                                                                                  | 0.591  | 0.600 | 0.609 | v    |  |

| V <sub>FB</sub> Input Bias Current         | I <sub>FB</sub>                |                                                                                                                    | -      | 2     | 200   | nA   |  |

| Transconductance                           | g <sub>m</sub>                 |                                                                                                                    | -      | 1     | -     | mS   |  |

| GMO Source Current                         | I <sub>GMO_SOURCE</sub>        |                                                                                                                    | -      | 50    | -     |      |  |

| GMO Sink Current                           | I <sub>GMO_SINK</sub>          |                                                                                                                    | -      | 50    | -     | μΑ   |  |

| Switching Frequency Range                  | f <sub>SW</sub>                | Guaranted by design                                                                                                | 0.2    | -     | 4     | МН   |  |

| Minimum On-Time                            | t <sub>ON_MIN</sub>            | Guaranted by design                                                                                                | -      | 50    | -     |      |  |

| Minimum Off-Time                           | t <sub>OFF_MIN</sub>           | $V_{OUT} = 1.2 \text{ V}, R_{ON} = 100 \text{ k}\Omega$                                                            | -      | 125   | -     | ns   |  |

| Soft Start Time                            | t <sub>SS</sub>                |                                                                                                                    | -      | 1.5   | -     | ms   |  |

| INTEGRATED MOSFETS                         |                                |                                                                                                                    |        |       |       |      |  |

| High-Side On Resistance R <sub>ON_HS</sub> |                                | V AV 5V                                                                                                            | -      | 35    | 51    | 0    |  |

| Low-Side On Resistance                     | R <sub>ON_LS</sub>             | $V_{IN} = AV_{IN} = 5 V$                                                                                           | _      | 23    | 35    | mΩ   |  |

| FAULT PROTECTIONS                          |                                |                                                                                                                    |        |       |       |      |  |

| Over Current Limit                         | I <sub>OCP</sub>               | Inductor valley current                                                                                            | -      | 7.5   | -     | Α    |  |

| Output OVP Threshold                       | $V_{FB\_OVP}$                  | V with respect to 0.6 V reference                                                                                  | -      | 21    | -     | 0/   |  |

| Output UVP Threshold                       | $V_{FB\_UVP}$                  | V <sub>FB</sub> with respect to 0.6 V reference                                                                    | -      | -25   | -     | %    |  |

| Over Temperature Dretection                |                                | Rising temperature                                                                                                 | -      | 160   | -     | ۰.   |  |

| Over Temperature Protection                |                                | Hysteresis                                                                                                         | -      | 30    | -     | °C   |  |

| POWER GOOD                                 |                                |                                                                                                                    |        |       |       |      |  |

| Dever Cood Output Threehold                | V <sub>FB_RISING_VTH_OV</sub>  | V <sub>FB</sub> rising above 0.6 V reference                                                                       | -      | 21    | -     | 0/   |  |

| Power Good Output Threshold                | V <sub>FB_FALLING_VTH_UV</sub> | V <sub>FB</sub> falling below 0.6 V reference                                                                      | -      | -12.5 | -     | - %  |  |

| Power Good On Resistance                   | R <sub>ON_PGOOD</sub>          |                                                                                                                    | -      | 30    | 60    | Ω    |  |

| Power Good Delay Time                      | t <sub>DLY_PGOOD</sub>         |                                                                                                                    | -      | 4     | -     | μs   |  |

| ENABLE THRESHOLD                           | _                              |                                                                                                                    |        |       |       |      |  |

| Logic High Level                           | V <sub>EN_H</sub>              |                                                                                                                    | 1.5    | -     | -     | .,   |  |

| Logic Low Level                            | $V_{EN\_L}$                    |                                                                                                                    | -      | -     | 0.4   | \ \  |  |

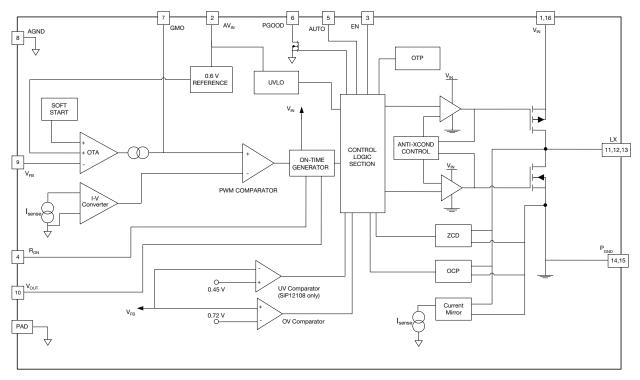

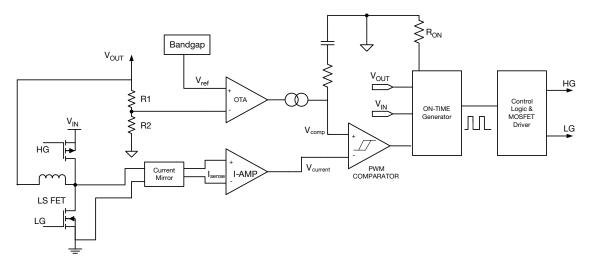

#### **FUNCTIONAL BLOCK DIAGRAM**

Fig. 2 - SiP12108 Functional Block Diagram

| ORDERING INFORMATION              |           |                          |  |  |  |

|-----------------------------------|-----------|--------------------------|--|--|--|

| PART NUMBER                       | PACKAGE   | MARKING<br>(LINE 2: P/N) |  |  |  |

| SiP12108DMP-T1GE4                 | QFN16 3x3 | 2108                     |  |  |  |

| SiP12108ADMP-T1GE4 <sup>(1)</sup> | QFN16 3x3 | 108A                     |  |  |  |

| SiP12108DB                        | N/A       |                          |  |  |  |

| SiP12108ADB <sup>(1)</sup>        | N/A       |                          |  |  |  |

#### Note

(1) Output undervoltage protection (UVP) disabled

Format:

Line 1: Dot Line 2: P/N

Line 3: Siliconix Logo + ESD Symbol

Line 4: Factory Code + Year Code + Work Week Code + LOT Code

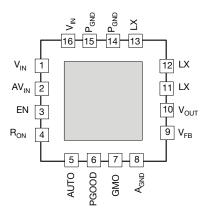

### **PIN CONFIGURATION**

QFN16 3x3

Fig. 3 - SiP12108 Pin Configuration (Top View)

| PIN CONFIG      | URATION          |                                                                                                                                    |  |  |  |

|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NUMBER NAME |                  | FUNCTION                                                                                                                           |  |  |  |

| 1, 16           | V <sub>IN</sub>  | Input supply voltage for power MOS. V <sub>IN</sub> = 2.8 V to 5.5 V                                                               |  |  |  |

| 2               | $AV_{IN}$        | Input supply voltage for internal circuitry. AV <sub>IN</sub> = 2.8 V to 5.5 V                                                     |  |  |  |

| 3               | EN               | Enable pin. Pull enable above 1.5 V to enable the part and below 0.4 V to disable. Do not float this pin.                          |  |  |  |

| 4               | R <sub>ON</sub>  | An external resistor between R <sub>ON</sub> and GND sets the switching on time.                                                   |  |  |  |

| 5               | AUTO             | Sets switching mode. Connect AUTO to ${\rm AV_{IN}}$ for forced continuous mode and AUTO to GND for power save mode. Do not float. |  |  |  |

| 6               | PGOOD            | Power good output. Open drain.                                                                                                     |  |  |  |

| 7               | GMO              | Connect to an external RC network for loop compensation and droop function                                                         |  |  |  |

| 8               | A <sub>GND</sub> | Analog ground                                                                                                                      |  |  |  |

| 9               | $V_{FB}$         | Feedback voltage. 0.6 V (typ.). Use a resistor divider between V <sub>OUT</sub> and A <sub>GND</sub> to set the output voltage.    |  |  |  |

| 10              | V <sub>OUT</sub> | V <sub>OUT</sub> , output voltage sense connection                                                                                 |  |  |  |

| 11, 12, 13      | LX               | Switching output, inductor connection point                                                                                        |  |  |  |

| 14, 15          | $P_{GND}$        | Power ground                                                                                                                       |  |  |  |

| EP              |                  | Exposed paddle (bottom). Connect to a good PCB thermal ground plane.                                                               |  |  |  |

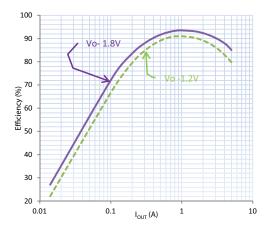

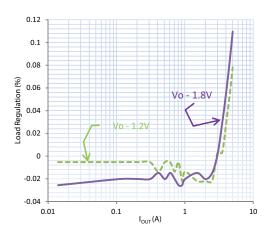

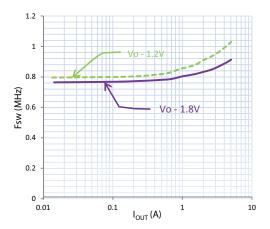

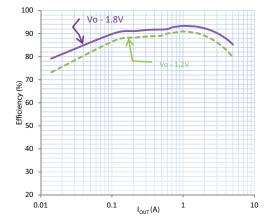

## **ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 3.3 \text{ V}$ , $L = 1 \mu\text{H}$ , $C = 3 \times 22 \mu\text{F}$ , $f_{SW} = 1.2 \text{ MHz}$ unless noted otherwise)

Fig. 4 - Efficiency - PWM Mode

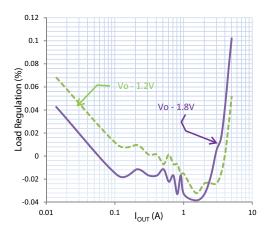

Fig. 5 - Load Regulation - PWM Mode

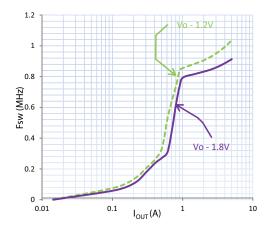

Fig. 6 - F<sub>SW</sub> Variation - PWM Mode

Fig. 7 - Efficiency - PSM Mode

Fig. 8 - Load Regulation - PSM Mode

Fig. 9 - F<sub>SW</sub> Variation - PSM Mode

# Vishay Siliconix

### **ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 3.3 \text{ V}$ , $L = 1 \mu\text{H}$ , $C = 3 \times 22 \mu\text{F}$ , $f_{SW} = 1.2 \text{ MHz}$ unless noted otherwise)

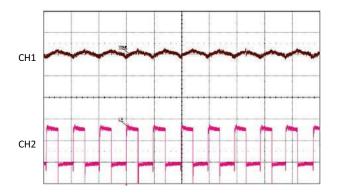

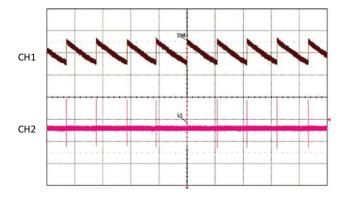

Fig. 10 - PWM Mode- Steady - State Ripple and LX, 5 A Load CH1 =  $V_{OUT}$ , 20 mV/div, CH2 = LX, 2 V/div, Time = 1  $\mu$ s/div

Fig. 13 - PWM Mode- Steady - State Ripple and LX, 0 A Load CH1 =  $V_{OUT}$ , 20 mV/div, CH2 = LX, 2 V/div, Time = 1  $\mu$ s/div

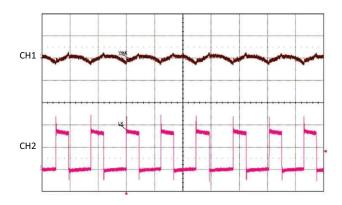

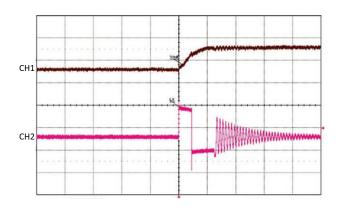

Fig. 11 - PSM Mode- Steady - State Ripple and LX, 0 A Load CH1 = V<sub>OUT</sub> , 20 mV/div, CH2 = LX, 2 V/div, Time = 10 ms/div

Fig. 14 - PSM Mode- Steady - State Ripple and LX, 0 A Load CH1 =  $V_{OUT}$  , 20 mV/div, CH2 = LX, 2 V/div, Time = 1  $\mu$ s/div

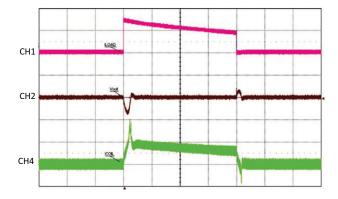

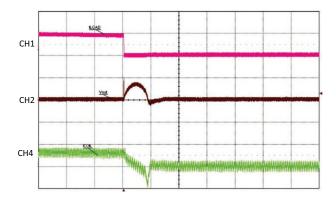

Fig. 12 - Load Step 0 A to 5 A to 0 A CH1 =  $I_{load}$ , CH2 =  $V_{OUT}$ , 500 mV/div, CH4 =  $I_{coil}$ , 5 A/div, Time = 100  $\mu$ s/div

Fig. 15 - Load Step 0 A to 5 A, Rising Edge CH1 = I<sub>load</sub>, CH2 = V<sub>OUT</sub>, 200 mV/div, CH4 = I<sub>coil</sub>, 5 A/div, Time = 20 μs/div

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Vishay Siliconix

### **ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 3.3 \text{ V}$ , $L = 1 \mu\text{H}$ , $C = 3 \times 22 \mu\text{F}$ , $f_{SW} = 1.2 \text{ MHz}$ unless noted otherwise)

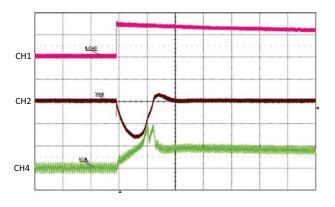

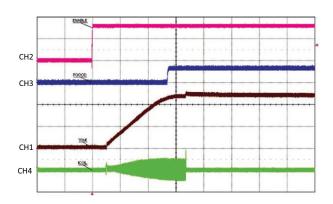

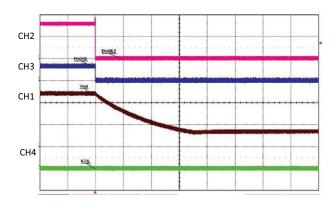

Fig. 16 - Load Step 0 A to 5 A, Falling Edge CH1 = I<sub>load</sub>, CH2 = V<sub>OUT</sub>, 200 mV/div, CH4 = I<sub>coil</sub>, 5 A/div, Time = 20 μs/div

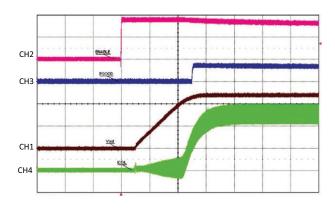

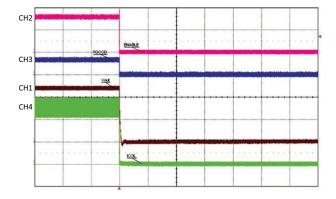

Fig. 19 - Turn-On Time PSM Mode, 0 A Load CH1 =  $V_{OUT}$ , 500 mV/div, CH2 = EN, 2 V/div, CH3 = PGOOD, 5 V/div, CH4 =  $I_{coil}$ , 2 A/div, Time = 500  $\mu$ s/div

Fig. 17 - Turn-Off Time PSM Mode, 0 A Load CH1 =  $V_{OUT}$ , 500 mV/div, CH2 = EN, 2 V/div, CH3 = PGOOD, 5 V/div, CH4 =  $I_{coil}$ , 2 A/div, Time = 500  $\mu$ s/div

Fig. 20 - Turn-On Time PWM Mode, 5 A Load CH1 =  $V_{OUT}$ , 500 mV/div, CH2 = EN, 2 V/div, CH3 = PGOOD, 5 V/div, CH4 =  $I_{coil}$ , 2 A/div, Time = 500  $\mu$ s/div

Fig. 18 - Turn-Off Time PWM Mode, 5 A Load CH1 =  $V_{OUT}$ , 500 mV/div, CH2 = EN, 2 V/div, CH3 = PGOOD, 5 V/div, CH4 =  $I_{coil}$ , 2 A/div, Time = 500  $\mu$ s/div

#### **OPERATIONAL DESCRIPTION**

#### **Device Overview**

SiP12108 is a high-efficiency monolithic synchronous buck regulator capable of delivering up to 5 A continuous current. The device has programmable switching frequency up to 4 MHz. The control scheme is based on current-mode constant-on-time architecture, which delivers fast transient response and minimizes external components. Thanks to the internal current ramp information, no high-ESR output bulk or virtual ESR network is required for the loop stability. This device also incorporates a power saving feature by enabling diode emulation mode and frequency foldback as load decreases.

SiP12108 has a full set of protection and monitoring features:

- Over current protection in pulse-by-pulse mode

- Output over voltage protection

- Output under voltage protection with device latch

- Over temperature protection with hysteresis

- Dedicated enable pin for easy power sequencing

- Power Good open drain output

This device is available in QFN16 3x3 package to deliver high power density and minimize PCB area.

#### **Power Stage**

SiP12108 integrated synchronous MOSFETs . The MOSFETs are optimized to achieve 95 % efficiency at 2 MHz switching frequency.

The power input voltage ( $V_{IN}$ ) can go up to 5.5 V and as low as 2.8 V for power conversion. The logic bias voltage ( $AV_{IN}$ ) ranges from 2.8 V to 5.5 V.

#### **PWM Control Mechanism**

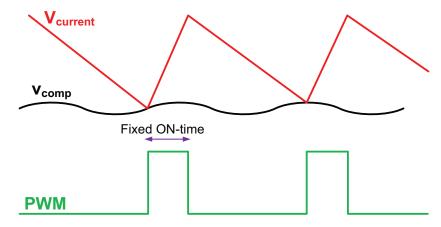

SiP12108 employs a state-of-the-art current-mode COT control mechanism. During steady-state operation, output voltage is compared with internal reference (0.6 V typ.) and the amplified error signal (V<sub>COMP</sub>) is generated on the COMP pin. In the meantime, inductor valley current is sensed, and its slope (I<sub>sense</sub>) is converted into a voltage signal (V<sub>current</sub>) to be compared with V<sub>COMP</sub>. Once V<sub>current</sub> is lower than V<sub>COMP</sub>, a single shot on-time is generated for a fixed time programmed by the external R<sub>ON</sub>. Figure 4 illustrates the basic block diagram for CM-COT architecture and figure 5 demonstrates the basic operational principle:

Fig. 21 - CM-COT Block Diagram

Fig. 22 - CM-COT Operational Principle

The following equation illustrates the relationship between on-time,  $V_{\text{IN}}$ ,  $V_{\text{OUT}}$  and  $R_{\text{ON}}$  value:

$$T_{ON} = R_{ON} \ x \ K \ x \ \frac{V_{OUT}}{V_{IN}}$$

, where K = 10.45 x 10<sup>-12</sup> a constant set internally

Once on-time is set, the pseudo constant frequency is then determined by the following equation:

$$f \text{sw} = \frac{D}{T_{ON}} = \frac{\frac{V_{OUT}}{V_{IN}}}{\frac{V_{OUT}}{V_{IN}} \times R_{ON} \times K} = \frac{1}{R_{ON} \times K}$$

#### **Loop Stability and Compensator Design**

Due to the nature of current mode control, a simple RC network (type II compensator) is required between COMP and A<sub>GND</sub> for loop stability and transient response purposes. The general concept of this loop design is to introduce a single zero through the compensator to determine the crossover frequency of overall close loop system.

The overall loop can be broken down into following segments.

Output feedback divider transfer function H<sub>fb</sub>:

$$H_{fb} = \frac{R_{fb2}}{R_{fb1} \times R_{fb2}}$$

Voltage compensator transfer function G<sub>COMP</sub> (s):

$$G_{COMP}(s) = \frac{R_O x (1 + sC_{COMP}R_{COMP})}{(1 + sR_OC_{COMP})} gm$$

Modulator transfer function H<sub>mod</sub> (s):

$$H_{mod}$$

(s) =  $\frac{1}{AV_1 \times R_{DS(on)}} \times \frac{R_{load} \times (1 + sC_0R_{ESR})}{(1 + sC_0R_{load})}$

The complete loop transfer function is given by:

$$H_{mod}(s) = \frac{R_{fb2}}{R_{fb1} x R_{fb2}} x \frac{R_O x (1 + sC_{COMP}R_{COMP})}{(1 + sR_OC_{COMP})} gm x \frac{1}{AV_1 x R_{DS(on)}} x \frac{R_{load} x (1 + sC_OR_{ESR})}{(1 + sC_OR_{load})}$$

#### When:

$C_{COMP}$  = Compensation capacitor  $R_{DS(on)}$  = LS switch resistance

$R_{COMP}$  = Compensation resistor  $R_{fb1}$  = Feedback resistor connect to LX gm = Error amplifier transconductance  $R_{fb2}$  = Feedback resistor connect to ground

$R_{load}$  = Load resistance  $R_{O}$  = Output impedance of error amplifier = 20  $M\Omega$

$C_O$  = Output capacitor  $AV_1$  = Voltage to current gain = 3

#### **Power Save Mode using AUTO Pin**

To further improve efficiency at light loads, SiP12108 provides a set of innovative implementations to eliminate LS recirculating current and switching losses. The internal Zero Crossing Detector (ZCD) monitors LX node voltage to determine when inductor current starts to flow negatively. In power saving mode (PSM), as soon as inductor valley current crosses zero, the device first deploys diode emulation mode by turning off LS FET. If load further decreases, switching frequency is further reduced

proportional to load condition to save switching losses. The switching frequency is set by the controller to maintain regulation. At zero load this frequency can go as low as hundreds of Hz.

Whenever fixed frequency PWM operation is required over the entire load span, the power saving mode feature can be disabled by connecting AUTO pin to  $V_{\text{IN}}$  or  $AV_{\text{IN}}$ .

#### **OUTPUT MONITORING AND PROTECTION FEATURES**

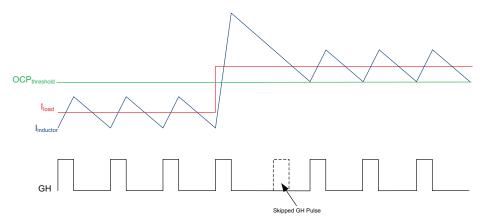

#### **Output Over-Current Protection (OCP)**

SiP12108 has pulse-by-pulse over-current limit control. The inductor valley current is monitored during LS FET turn-on period through  $R_{DS(on)}$  sensing. After a pre-defined time, the valley current is compared with internal threshold (7.5 A typ.) to determine the threshold for OCP. If monitored current is higher than threshold, HS turn-on pulse is skipped and LS FET is kept on until the valley current returns below OCP limit.

In the severe over-current condition, pulse-by-pulse current limit eventually triggers output under-voltage protection (UVP), which latches the device off to prevent catastrophic thermal-related failure. UVP is described in the next section.

OCP is enabled immediately after AV<sub>IN</sub> passes UVLO level. Figure 6 illustrates the OCP operation.

Fig. 23 - Over-Current Protection Illustration

#### **Output Under-Voltage Protection (UVP)**

UVP is implemented by monitoring output through  $V_{FB}$  pin. Once the voltage level at  $V_{FB}$  is below 0.45 V for more than 20  $\mu$ s, then UVP event is recognized and both HS and LS MOSFETs are turned off. UVP latches the device off until either  $AV_{IN}$  or EN is recycled.

UVP is only active after the completion of soft-start sequence. This function only exists on SiP12108. On the "A" version of the device, SiP12108A, this feature is disabled.

#### **Output Over-Voltage Protection (OVP)**

For OVP implementation, output is monitored through  $V_{FB}$  pin. After soft-start, if the voltage level at  $V_{FB}$  is above 21 % (typ.), OVP is triggered with HS FET turning off and LS FET turning on immediately to discharge the output. Normal operation is resumed once  $V_{FB}$  drops back to 0.6 V.

OVP is active immediately after AV<sub>IN</sub> passes UVLO level.

#### Over-Temperature Protection (OTP)

SiP12108 has internal thermal monitor block that turns off both HS and LS FETs when junction temperature is above 160 °C (typ.). A hysteresis of 30 °C is implemented, so when junction temperature drops below 130 °C, the device restarts by initiating the soft-start sequence again.

#### **Soft Startup**

SiP12108 deploys an internally regulated soft-start sequence to realize a monotonic startup ramp without any output overshoot. Once AV $_{\rm IN}$  is above UVLO level (2.55 V typ.). Both the reference and V $_{\rm OUT}$  will ramp up slowly to regulation in 1 ms (typ.) with the reference going from 0 V to 0.6 V and V $_{\rm OUT}$  rising monotonically to the programmed output voltage.

During soft-start period, OCP is activated. OVP and short-circuit protection are not active until soft-start is complete.

## Vishay Siliconix

#### **Pre-bias Startup**

In case of pre-bias startup, output is monitored through  $V_{FB}$  pin. If the sensed voltage on  $V_{FB}$  is higher than the internal reference ramp value, control logic prevents HS and LS FET from switching to avoid negative output voltage spike and excessive current sinking through LS FET.

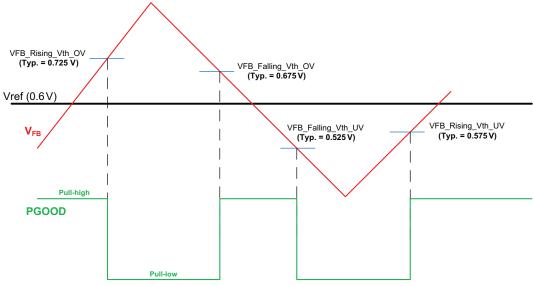

#### **Power Good (PGOOD)**

SiP12108's Power Good is an open-drain output. Pull PGOOD pin high up to 5 V through a 10K resistor to use this signal. Power Good window is shown in the below diagram. If voltage level on  $V_{FB}$  pin is out of this window, PGOOD signal is de-asserted by pulling down to GND.

Fig. 24 - PGOOD Window and Timing Diagram

#### **DESIGN PROCEDURE**

The design process of the SiP12108 is quite straight forward. Only few passive components such as output capacitors, inductor and  $R_{\rm on}$  resistor need to be selected.

The following paragraph describes the selection procedure for these peripheral components for a given operating conditions.

In the next example the following definitions apply:

V<sub>INmax.</sub>: the highest specified input voltage

V<sub>INmin.</sub>: the minimum effective input voltage subject to voltage drops due to connectors, fuses, switches, and PCB traces

There are two values of load current to evaluate - continuous load current and peak load current.

Continuous load current relates to thermal stress considerations which drive the selection of the inductor and input capacitors.

Peak load current determines instantaneous component stresses and filtering requirements such as inductor saturation, output capacitors, and design of the current limit circuit.

The following specifications are used in this design:

- $V_{IN} = 3.3 V \pm 10 \%$

- V<sub>OUT</sub> = 1.2 V ± 1 %

- F<sub>SW</sub> = 1 MHz

- Load = 5 A maximum

#### **Setting the Output Voltage**

The output voltage is set by using a resistor divider on the feedback ( $V_{FB}$ ) pin. The  $V_{FB}$  pin is the negative input of the internal error amplifier.

When in regulation the  $V_{\text{FB}}$  voltage is 0.6 V. The output voltage  $V_{\text{O}}$  is set based on the following formula.

$$V_O = V_{FB} (1 + R1/R2)$$

where R1 and R2 are shown in figure 21.

#### **Setting Switching Frequency**

Selection of the switching frequency requires making a trade-off between the size and cost of the external filter components (inductor and output capacitor) and the power conversion efficiency. The desired switching frequency, 1 MHz was chosen based on optimizing efficiency while maintaining a small footprint and minimizing component cost.

In order to set the design for 1 MHz switching frequency,  $(R_{ON})$  resistor which determines the on-time (indirectly setting the frequency) needs to be calculated using the following equation.

$$R_{ON} = \frac{1}{F_{SW} \times K} = \frac{1}{1 \times 10^6 \times 10.45 \times 10^{-12}} \approx 105 \text{ k}\Omega$$

## Vishay Siliconix

#### **INDUCTOR SELECTION**

In order to determine the inductance, the ripple current must first be defined. Cost, PCB size, output ripple, and efficiency are all used in the selection process. Low inductor values result in smaller size and allow faster transient performance but create higher ripple current which can reduce efficiency. Higher inductor values will reduce the ripple current while compromising the efficiency (higher DCR) and transient response.

The ripple current will also set the boundary for power-save operation. The switcher will typically enter power-save mode when the load current decreases to 1/2 of the ripple current. For example, if ripple current is 1 A then power-save operation will typically start at loads approaching 0.5 A. Alternatively, if ripple current is set at 40 % of maximum load current, then power-save will start for loads less than ~ 20 % of maximum current.

Inductor selection for the SiP12108 should be designed where the ripple current is  $\sim 50~\%$  in all situations with  $V_{IN}$  3.6 V and less.

For example 3.3  $V_{IN}$  to 1.2  $V_{OUT}$  at 1 MHz. dI = V/L x dt = ((3.3 - 1.2)/0.33) x 0.36 = 2.3 A, %dI = 2.3/5 = 46 %.

For higher  $V_{\text{IN}} > 3.6 \text{ V}$  ripple current should be set to less then 40 %.

For 5  $V_{IN}$  to 1.2  $V_{OUT}$  at 1 MHz dI = ((5 - 1.2)/0.68) x 0.36) = 2 A, %dI = 2/5 = 40 %.

#### **Output Capacitance Calculation**

The output capacitance is usually chosen to meet transient requirements. A worst-case load release, from maximum load to no load at the exact moment when inductor current is at the peak, determines the required capacitance. If the load release is instantaneous (load changes from maximum to zero in  $<1/\mbox{F}_{SW}$  µs), the output capacitor must absorb all the inductor's stored energy. This will approximately cause a peak voltage on the capacitor according to the following equation.

$$C_{OUTmin.} = \frac{L \times \left(I_{OUT} + \frac{1}{2} \times I_{RIPPLEmax.}\right)^{2}}{\left(V_{peak}\right)^{2} - \left(V_{OUT}\right)^{2}}$$

Assuming a peak voltage  $V_{PEAK}$  of 1.3 V (100 mV rise upon load release), and a 5 A load release, the required capacitance is shown by the next equation.

$$C_{OUTmin.} = \frac{1 \mu H \times (5 \text{ A} + 0.5 \times (0.81 \text{ A}))^2}{(1.3 \text{ V})^2 - (1.2 \text{ V})^2} = 116.8 \mu F$$

If the load release is relatively slow, the output capacitance can be reduced. Using MLCC ceramic capacitors we will use 5 x 22  $\mu$ F or 110  $\mu$ F as the total output capacitance.

#### STABILITY CONSIDERATIONS

Using the output capacitance as a starting point for compensation values. Then, taking Bode plots and transient response measurements we can fine tune the compensation values.

Setting the crossover frequency to 1/5 of the switching frequency:

$F_0 = F_{sw}/5 = 1 \text{ MHz}/5 = 200 \text{ kHz}$

Setting the compensation zero at 1/5 to 1/10 the crossover frequency for the phase boost:

$$F_Z = \frac{1}{2\pi \times R_C \times C_C} = \frac{F_0}{5}$$

Setting  $C_C = 0.47$  nF and solve for  $R_C$

$$R_C = \frac{5}{2\pi \times C_C \times F_0} = \frac{5}{2\pi \times 0.47 \text{ nF} \times 200 \text{K}} = 8.469 \text{K}$$

#### **SWITCHING FREQUENCY VARIATIONS**

The switching frequency variation in COT can be mainly attributed to the increase in conduction losses as the load increases. The on time is "ideally constant" so the controller must account for losses by reducing the off time which increases the overall duty cycle. Hence the  $F_{SW}$  will tend to increase with load.

In power save mode (PSM) the IC will run in pulse skip mode at light loads. As the load increases the  $F_{SW}$  will increase until it reaches the nominal set  $F_{SW}$ . This transition occurs approximately when the load reaches to 20 % of the full load current.

#### **DESIGN CONSIDERATION**

For  $V_{OUT}$  higher then UVLO (2.55 V typ) and/or very slow  $V_{IN}$  slew rates. The IC may have difficulty in starting-up because  $V_{IN}$  level is limiting how fast  $V_{OUT}$  can rise. In these situations a divider for EN pin threshold (~1.15 V) derived from  $V_{IN}$  can be used. Allowing a higher  $V_{IN}$  level before switching begins and a smooth start-up. For example  $R_{top} = 60 K$  and  $R_{bot} = 25 K$  when  $V_{IN} = 4$  V, EN level will be 1.18 V.

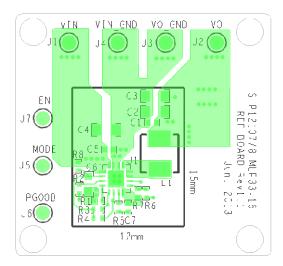

#### **THERMAL DESIGN**

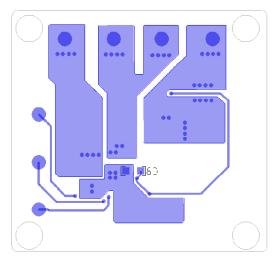

The 16 pin package includes a thermal pad for much better thermal performance when incorporated in the PCB footprint. As shown in the PCB layout at the end of this document. There are four vias evenly placed on the pad that help transfer the heat to other layers. Tying the paddle to the bottom layer through vias will provide the best thermal performance.

Fig. 25 - Reference Board Schematic

# Vishay Siliconix

| BILI | BILL OF MATERIALS |                   |                       |         |               |                    |              |  |

|------|-------------------|-------------------|-----------------------|---------|---------------|--------------------|--------------|--|

| ITEM | QTY.              | REFERENCE         | VALUE                 | VOLTAGE | PCB FOOTPRINT | PART NUMBER        | MANUFACTURER |  |

| 1    | 2                 | C1, C5            | 0.1 μF                | 50 V    | C0402-TDK     | VJ0402Y104MXQCW1BC | Vishay       |  |

| 2    | 2                 | C2, C3, C4        | 22 µF                 | 10 V    | C0805-TDK     | LMK212BJ226MG-T    | Murata       |  |

| 4    | 1                 | C6                | 0.1 μF                | 10 V    | C0603-TDK     | GRM188R71C104KA01D | Murata       |  |

| 5    | 1                 | C7                | 470 pF                | 50 V    | C0402-TDK     | VJ0402A471JXACW1BC | TDK          |  |

| 6    | 1                 | C8 <sup>(1)</sup> | DNP                   | -       | C0603-TDK     | -                  | -            |  |

| 7    | 1                 | J1                | VIN                   | -       | TP30          | 5002K-ND           | Keystone     |  |

| 8    | 1                 | J2                | VO                    | -       | TP30          | 5002K-ND           | Keystone     |  |

| 9    | 1                 | J3                | VO_GND                | -       | TP30          | 5002K-ND           | Keystone     |  |

| 10   | 1                 | J4                | VIN_GND               | -       | TP30          | 5002K-ND           | Keystone     |  |

| 11   | 1                 | J5                | MODE                  | -       | TP30          | 5002K-ND           | Keystone     |  |

| 12   | 1                 | J6                | PGOOD                 | -       | TP30          | 5002K-ND           | Keystone     |  |

| 13   | 1                 | J7                | EN                    | -       | TP30          | 5002K-ND           | Keystone     |  |

| 14   | 1                 | L1                | 0.47 µH               | -       | IHLP1616      | IHLP1616BZERR47M11 | Vishay       |  |

| 15   | 4                 | R1, R2, R3, R4    | 100K                  | 50 V    | R0402-Vishay  | CRCW0402100KFKED   | Vishay       |  |

| 16   | 1                 | R5                | 6K04                  | 50 V    | R0402-Vishay  | TNPW04026K04BETD   | Vishay       |  |

| 17   | 1                 | R6                | 5K11                  | 50 V    | R0402-Vishay  | CRCW04025K11FKED   | Vishay       |  |

| 18   | 1                 | R7                | 2K55                  | 50 V    | R0402-Vishay  | TNPW04022K55BETD   | Vishay       |  |

| 19   | 1                 | R8                | 1                     | 50 V    | R0402-Vishay  | RC0402FR-071RL     | Yageo        |  |

| 20   | 1                 | U1                | SiP12107,<br>SiP12108 | -       | MLP33-16      | SiP1210x           | Vishay       |  |

### **PCB LAYOUT OF REFERENCE BOARD**

Fig. 26 - Top Layer

Fig. 27 - Bottom Layer

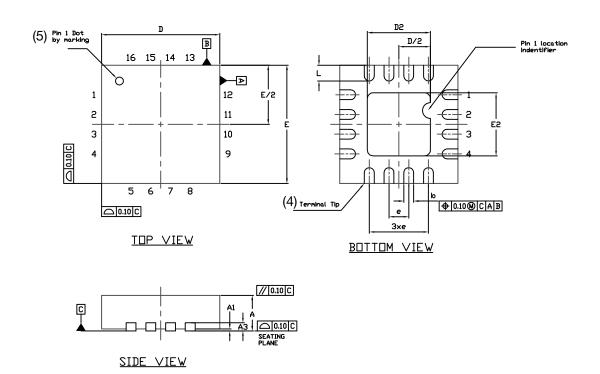

### **MLP33-16L CASE OUTLINE**

|                   | MILLIMETERS (1) |          |      | INCHES    |           |       |  |

|-------------------|-----------------|----------|------|-----------|-----------|-------|--|

| DIMENSION         | MIN.            | NOM.     | MAX. | MIN.      | NOM.      | MAX.  |  |

| Α                 | 0.75            | 0.85     | 0.95 | 0.029     | 0.033     | 0.037 |  |

| A1                | 0               | -        | 0.05 | 0         | -         | 0.002 |  |

| A3                |                 | 0.20 REF |      |           | 0.001 REF |       |  |

| b                 | 0.18            | 0.25     | 0.30 | 0.007     | 0.010     | 0.012 |  |

| D                 | 3.00 BSC        |          |      | 0.118 BSC |           |       |  |

| D2                | 1.5             | 1.6      | 1.7  | 0.059     | 0.063     | 0.067 |  |

| е                 | 0.50 BSC        |          |      | 0.020 BSC |           |       |  |

| E                 | 3.00 BSC        |          |      | 0.118 BSC |           |       |  |

| E2                | 1.5             | 1.6      | 1.7  | 0.059     | 0.063     | 0.067 |  |

| L                 | 0.3             | 0.4      | 0.5  | 0.012     | 0.016     | 0.020 |  |

| N (3)             | 16              |          |      | 16        |           |       |  |

| Nd <sup>(3)</sup> | 4               |          |      | 4         |           |       |  |

| Ne <sup>(3)</sup> | 4               |          |      | 4         |           |       |  |

#### Notes

- (1) Use millimeters as the primary measurement.

- (2) Dimensioning and tolerances conform to ASME Y14.5M. 1994.

- (3) N is the number of terminals. Nd and Ne is the number of terminals in each D and E site respectively.

- (4) Dimensions b applies to plated terminal and is measured between 0.15 mm and 0.30 mm from terminal tip.

- (5) The pin 1 identifier must be existed on the top surface of the package by using identification mark or other feature of package body.

- (6) Package warpage max. 0.05 mm.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?62699">www.vishay.com/ppg?62699</a>.

## **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Vishay:

SIP12108DMP-T1GE4 SIP12108DB SIP12108ADMP-T1GE4