**AIE Adaptive Image Enhancer Series**

# Video Encoders built-in Image Correction

BU6520KV,BU6521KV

No.10060ECT03

#### Description

BU6520KV, BU6521KV are video encoders with built-in AIE image correcting function. Also, BU6521KV has the image correcting function of the fog reduction, too.

Fog Reduction, the brightness correction, the backlight correction and the chroma emphasis can improve the visibility of the input image of the camera.

\* AIE and Fog Reduction function are image processing technology by ROHM's hardware.

#### Features

- Format of video output is compatible with NTSC/PAL composite video format (CVBS). Built-in DAC with direct 75Ω drive capability.

- 2) Built-in Fog Reduction function\*1, dynamic range correction, edge-emphasizing filter and gamma filter.

- 3) Input/output data format is compatible with ITU-R BT.656 and YCbCr=4:2:2 with synchronization signal.

- 4) Compatible with NTSC (27MHz, 28.63636MHz and 19.06993MHz)/ PAL(27MHz, 28.375MHz, 35.46895MHz and 18.9375MHz)<sup>\*2</sup>.

- 5) Registers can be set up with a 2-line serial interface.

- 6) Registers can be automatically set up by reading from external EEPROM, when after resetting or changing mode.

- \*1 As for the Fog Reduction feature, it loads only BU6521KV.

- \*2 NTSC 19,06993 MHz and PAL 18,9375 MHz support only BU6521KV.

## Applications

Security camera, camera for automotive, drive recorder etc.

#### Line up matrix

| Part No. | Power Sopply<br>Voltage(V)                                                                     | Image size          | Input<br>Interface                  | Control<br>Interface                               | Output<br>Interface                 | Feature                                | Temperature<br>Operating<br>Range(°C) | Package |

|----------|------------------------------------------------------------------------------------------------|---------------------|-------------------------------------|----------------------------------------------------|-------------------------------------|----------------------------------------|---------------------------------------|---------|

| BU6520KV | 1.4 to 1.6<br>(V <sub>DD</sub> Core)<br>2.7 to 3.6<br>(V <sub>DD</sub> I/O, AV <sub>DD</sub> ) | 720x480,<br>SD size | 8bit,<br>YUV=4:2:2,<br>ITU-R BT.656 | I <sup>2</sup> C,<br>Serial<br>EEPROM<br>interface | 8bit,<br>YUV=4:2:2,<br>ITU-R BT.656 | AIE,<br>Video output                   | -40 ~ +85                             | VQFP48C |

| BU6521KV | 1.4 to 1.6<br>(V <sub>DD</sub> Core)<br>2.7 to 3.6<br>(V <sub>DD</sub> I/O, AV <sub>DD</sub> ) | 720x480,<br>SD size | 8bit,<br>YUV=4:2:2,<br>ITU-R BT.656 | I <sup>2</sup> C,<br>Serial<br>EEPROM<br>interface | 8bit,<br>YUV=4:2:2,<br>ITU-R BT.656 | AIE,<br>Fog reduction,<br>Video output | -40 ~ +85                             | VQFP48C |

I<sup>2</sup>C BUS is a registered trademark of Philips

# Absolute maximum ratings

| Parameter                 | Symbol | Rating                                | Unit |

|---------------------------|--------|---------------------------------------|------|

| Supply voltage1 (IO)      | VDDIO  | -0.3~+4.2                             | V    |

| Supply voltage2 (IO)      | VDDI2C | -0.3~+4.2                             | V    |

| Supply voltage3 (DAC)     | AVDD   | -0.3~+4.2                             | V    |

| Supply voltage4 (CORE)    | VDD    | -0.3~+2.1                             | V    |

| Input voltage range       | VIN    | -0.3~IO_LVL+0.3 *1                    | V    |

| Storage temperature range | Tstg   | -40~+125                              | °C   |

| Power dissipation         | PD     | 400 <sup>*2</sup> , 900 <sup>*3</sup> | mW   |

# Operating conditions

| Parameter                   | Symbol | Ratings                  | Unit |

|-----------------------------|--------|--------------------------|------|

| Supply voltage 1 (IO)       | VDDIO  | 2.70 ~ 3.60 (Typ.: 3.30) | V    |

| Supply voltage 2 (IO)       | VDDI2C | 2.70 ~ 3.60 (Typ.: 3.30) | V    |

| Supply voltage 3 (DAC)      | AVDD   | 2.70 ~ 3.60 (Typ.: 3.30) | V    |

| Supply voltage 4 (CORE)     | VDD    | 1.40 ~ 1.60 (Typ.: 1.50) | V    |

| Input voltage range         | VIN    | 0.00 ~ IO_LVL *1         | V    |

| Operating temperature range | Topr   | -40 ~ +85                | °C   |

<sup>\*1</sup> IO\_LVL is a generic name of VDDIO, VDDI2C, and AVDD.

<sup>1</sup> IO\_LVL is a generic name of VDDIO, VDDI2C, and AVDD.

1 IC only. In the case exceeding 25°C, 4.0mW should be reduced at the rating 1°C.

1 When packaging a glass epoxy board of 70x70x1.6mm. If exceeding 25°C, 9.0mW should be reduced at the rating 1°C.

1 Has not been designed to withstand radiation.

Has not been designed to withstand radiation.

Operation is not guaranteed at absolute maximum ratings.

Please supply power source in order of VDD→(VDDIO, VDDI2C, and AVDD).

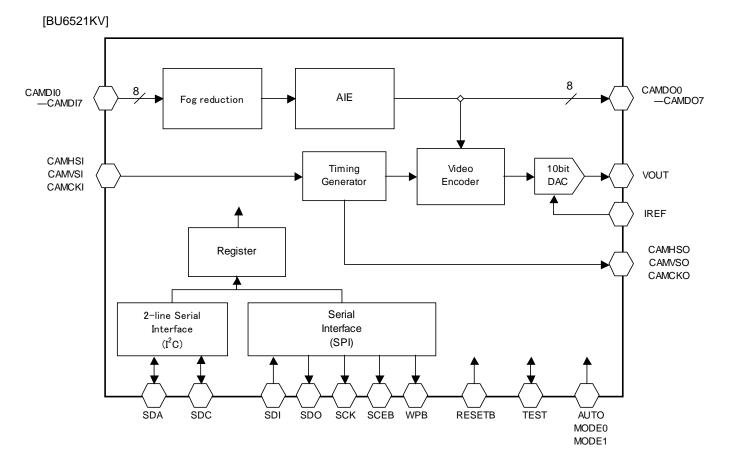

#### Block Diagram [BU6520KV] 8 CAMDO0 —CAMDO7 CAMDI0 AIE -CAMDI7 CAMHSI Timing 10bit Video CAMVSI VOUT Generator Encoder DAC CAMCKI IREF CAMHSO Register CAMVSO CAMCKO Serial 2-line Serial Interface Interface $(I^2C)$ (SPI) SCK RESETB SDA SDC SDI SDO SCEB WPB TEST AUTO MODE0 MODE1

Fig.1 BU6520KV Block Diagram

Fig.2 BU6521KV Block Diagram

# ●Pin functional descriptions • Equivalent circuit

| PIN<br>No. | PIN Name | In/Out | Active<br>Level | Init | Function explanation    | Power<br>Source<br>System | I/O<br>type <sup>*1</sup> |

|------------|----------|--------|-----------------|------|-------------------------|---------------------------|---------------------------|

| 1          | SDI      | In     | DATA            | -    | SPI-bus data input      | 1                         | Α                         |

| 2          | CAMDI7   | In     | DATA            | -    | Data input bit 7        | 1                         | С                         |

| 3          | CAMDI6   | In     | DATA            | -    | Data input bit 6        | 1                         | С                         |

| 4          | CAMDI5   | In     | DATA            | -    | Data input bit 5        | 1                         | С                         |

| 5          | CAMDI4   | In     | DATA            | -    | Data input bit 4        | 1                         | С                         |

| 6          | GND      | -      | GND             | -    | Common GROUND           | 1,2,4                     | -                         |

| 7          | VDD      | -      | PWR             | -    | CORE power source       | 4                         | -                         |

| 8          | CAMDI3   | In     | DATA            | -    | Data input bit 3        | 1                         | С                         |

| 9          | CAMDI2   | In     | DATA            | -    | Data input bit 2        | 1                         | С                         |

| 10         | CAMDI1   | In     | DATA            | -    | Data input bit 1        | 1                         | С                         |

| 11         | CAMDI0   | In     | DATA            | -    | Data input bit 0        | 1                         | С                         |

| 12         | CAMHSI   | In     | *               | -    | Horizontal timing input | 1                         | С                         |

| 13         | CAMVSI   | In     | *               | -    | Vertical timing input   | 1                         | С                         |

| 14         | CAMCKI   | In     | CLK             | -    | Clock input             | 1                         | E                         |

| 15         | GND      | -      | GND             | -    | Common GROUND           | 1,2,4                     | -                         |

| 16         | VDDIO    | -      | PWR             | -    | Digital IO power source | 1                         | -                         |

| 17         | CAMDO0   | Out    | DATA            | Low  | Data output bit 0       | 1                         | F                         |

| 18         | CAMDO1   | Out    | DATA            | Low  | Data output bit 1       | 1                         | F                         |

| 19         | CAMDO2   | Out    | DATA            | Low  | Data output bit 2       | 1                         | F                         |

| 20         | CAMDO3   | Out    | DATA            | Low  | Data output bit 3       | 1                         | F                         |

| 21         | CAMDO4   | Out    | DATA            | Low  | Data output bit 4       | 1                         | F                         |

| 22         | CAMDO5   | Out    | DATA            | Low  | Data output bit 5       | 1                         | F                         |

| 23         | CAMDO6   | Out    | DATA            | Low  | Data output bit 6       | 1                         | F                         |

| 24         | CAMDO7   | Out    | DATA            | Low  | Data output bit 7       | 1                         | F                         |

<sup>&</sup>quot; \* " in the Active Level column indicates that it may be changed during set-up of the register.

Init column indicates pin status when released from reset.

In the power system column, " 1 " stands for VDDIO, " 2 " stands for VDDI2C, " 3 " stands for AVDD, " 4 " stands for VDD.

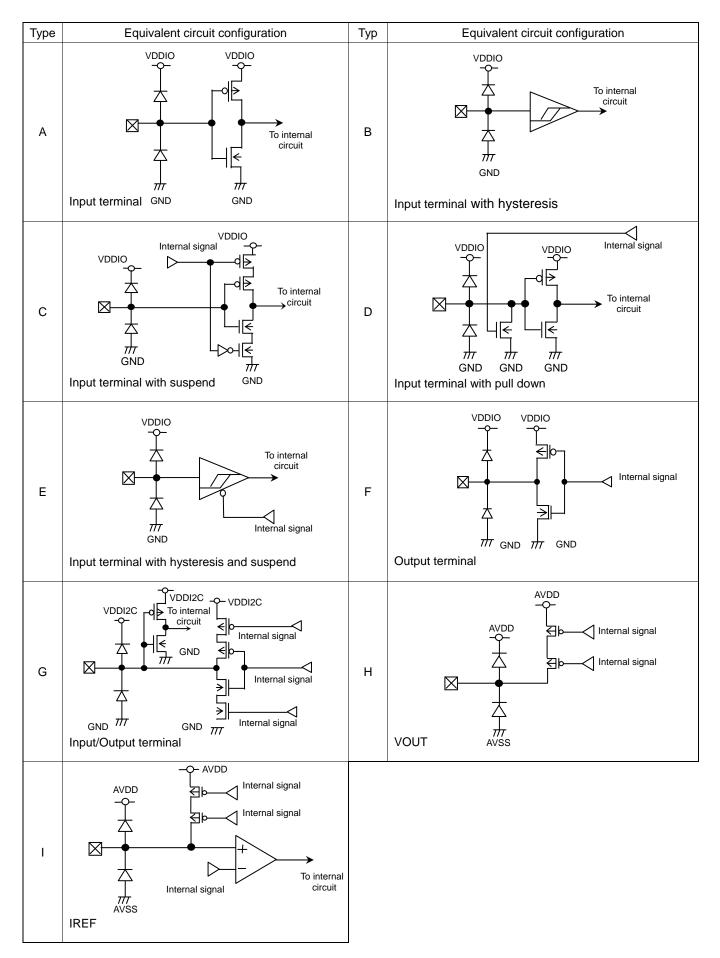

\*1 Fig.3 Equivalent Circuit Structures of input / output pins reference

| PIN<br>No. | PIN Name | In/Out | Active<br>Level | Init  | Function explanation                                               | Power<br>Source<br>System | I/O<br>type <sup>*1</sup> |

|------------|----------|--------|-----------------|-------|--------------------------------------------------------------------|---------------------------|---------------------------|

| 25         | CAMHSO   | Out    | *               | Low   | Horizontal timing output                                           | 1                         | F                         |

| 26         | CAMVSO   | Out    | *               | Low   | Vertical timing output                                             | 1                         | F                         |

| 27         | CAMCKO   | Out    | CLK             | Low   | Clock output                                                       | 1                         | F                         |

| 28         | GND      | -      | GND             | -     | Common GROUND                                                      | 1,2,4                     | -                         |

| 29         | VDD      | -      | PWR             | -     | CORE power source                                                  | 4                         | -                         |

| 30         | AUTO     | In     | High            | PD *2 | Auto register setting enable signal                                | 1                         | D                         |

| 31         | MODE0    | In     | DATA            | PD *2 | Auto register setting mode select bit 0                            | 1                         | D                         |

| 32         | MODE1    | In     | DATA            | PD *2 | Auto register setting mode select bit 1                            | 1                         | D                         |

| 33         | VOUT     | Out    | Analog          | -     | Analog composite output                                            | 3                         | Н                         |

| 34         | AVSS     | -      | GND             | -     | Analog GROUND for DAC                                              | 3                         | -                         |

| 35         | IREF     | Out    | Analog          | -     | Reference voltage for DAC                                          | 3                         | I                         |

| 36         | AVDD     | -      | PWR             | -     | Analog power source for DAC                                        | 3                         | -                         |

| 37         | GND      | -      | GND             | -     | Common GROUND                                                      | 1,2,4                     | -                         |

| 38         | VDDI2C   | -      | PWR             | -     | Digital IO power source (For 2-line serial interface input/output) | 2                         | -                         |

| 39         | SDA      | In/Out | DATA            | In    | 2-line serial interface data input/output                          | 2                         | G                         |

| 40         | SDC      | In/Out | CLK             | In    | 2-line serial interface clock input                                | 2                         | G                         |

| 41         | RESETB   | In     | Low             | -     | System reset signal                                                | 1                         | В                         |

| 42         | TEST     | In     | High            | PD *2 | Test mode terminal (Connect to GND)                                | 1                         | D                         |

| 43         | GND      | -      | GND             | -     | Common GROUND                                                      | 1,2,4                     | -                         |

| 44         | VDDIO    | -      | PWR             | -     | Digital IO power source                                            | 1                         | -                         |

| 45         | WPB      | Out    | Low             | Low   | Write protect signal to EEPROM                                     | 1                         | F                         |

| 46         | SCEB     | Out    | Low             | High  | Chip select signal to EEPROM                                       | 1                         | F                         |

| 47         | SCK      | Out    | CLK             | Low   | SPI-bus clock                                                      | 1                         | F                         |

| 48         | SDO      | Out    | DATA            | Low   | SPI-bus data output                                                | 1                         | F                         |

|            |          |        |                 |       |                                                                    |                           |                           |

<sup>\* &</sup>quot; \* " in the Active Level column indicates that it may be changed during set-up of the register.

Init column indicates pin status when released from reset.

In the power system column, "1" stands for VDDIO, "2" stands for VDDI2C, "3" stands for AVDD, "4" stands for VDD.

\*1 Fig.3 Equivalent Circuit Structures of input / output pins reference

<sup>\*2</sup> Pull-down status.

Fig.3 Equivalent Circuit Structures of input / output pins

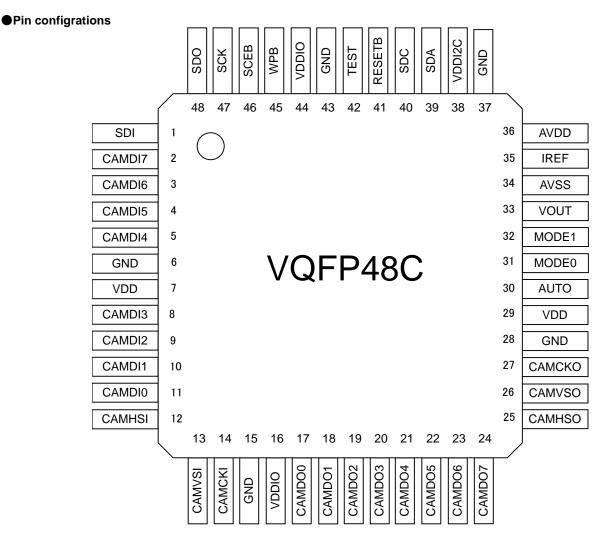

Fig.4 Pin configrations

## ● Electrical characteristics (common)

(Unless otherwise specified VDD=1.50V, VDDIO=3.3V, VDDI2C=3.3V, AVDD=3.3V, GND=0.0V, Ta=25°C, f<sub>IN</sub>=35.5MHz)

|                                |          |                 | ,    |        |                                                    |      | , , , , , , , , , , , , , , , , , , , ,             |

|--------------------------------|----------|-----------------|------|--------|----------------------------------------------------|------|-----------------------------------------------------|

| Param                          | otor     | Cumbal          |      | Limits |                                                    | Unit | Condition                                           |

| Param                          | letei    | Symbol          | MIN. | TYP.   | MAX.                                               | Unit | Condition                                           |

| Input frequency                |          | f <sub>IN</sub> | 2    | -      | 35.5                                               | MHz  | CAMCKI(DUTY45%~55%)                                 |

| Supply current                 | BU6520KV | IDD1            | -    | 30     | -                                                  | mA   | 35.5MHz operational setting*1                       |

| (CORE)                         | BU6521KV | IDD1            | -    | 40     | 62                                                 | mA   | 35.5MHz operational setting <sup>*2</sup>           |

| Leakage current                | (CORE)   | IDDst1          | -    | -      | 50                                                 | μA   | At sleep mode setting, input terminal = GND setting |

| Supply current                 | BU6520KV | IDD2            | -    | 38     | -                                                  | mA   | RL=37.5 $\Omega$ , RIREF=2.4k $\Omega$              |

| (DAC)                          | BU6521KV | IDD2            | -    | 38     | 56                                                 | mA   | RL=37.5 $\Omega$ , RIREF=2.4k $\Omega$              |

| Leakage current (DAC) IDDst2 - |          | -               | 5    | μΑ     | input terminal=GND and DAC power down mode setting |      |                                                     |

<sup>\*1</sup> Supply current(Total value of current of VDD, VDDIO, and VDDI2C) at color-bar image input in AIE enable and Digital output disable settings.

# ● Electrical characteristics (DC characteristics)

1. DC characteristics (IO)

(Unless otherwise specified VDD=1.50V, VDDIO=3.3V, VDDI2C=3.3V, AVDD=3.3V, GND=0.0V, Ta=25°C)

| (Offices offici wise specified v | DD-1.00 V | , 10010-0       | 7.0 V, VDL | 120-0.01,       | 7100- | -0.0 V, GIVE -0.0 V, IQ-20 O)                             |

|----------------------------------|-----------|-----------------|------------|-----------------|-------|-----------------------------------------------------------|

| Parameter                        | Symbol    |                 | Limits     |                 | Unit  | Condition                                                 |

| Parameter                        | Symbol    | MIN.            | TYP.       | MAX.            | Offic | Condition                                                 |

| Input "H" current                | IIH       | -10             | -          | 10              | μΑ    | VIH=IO_LVL                                                |

| Input "L" current                | IIL       | -10             | -          | 10              | μΑ    | VIL=GND                                                   |

| Pull-down current                | IPD       | 25              | 50         | 100             | μΑ    | VIH=IO_LVL                                                |

| Input "H" voltage 1              | VIH1      | IO_LVL<br>x0.8  | -          | IO_LVL<br>+0.3  | V     | Normal input (Including input mode of I/O terminal)       |

| Input "L" voltage 1              | VIL1      | -0.3            | -          | IO_LVL<br>x0.2  | ٧     | Normal input (Including input mode of I/O terminal)       |

| Input "H" voltage 2              | VIH2      | IO_LVL<br>x0.85 | -          | IO_LVL<br>+0.3  | V     | Hysteresis input (RESETB,CAMCKI,AUTO,MODE0,MODE1)         |

| Input "L" voltage 2              | VIL2      | -0.3            | -          | IO_LVL<br>x0.15 | V     | Hysteresis input (RESETB,CAMCKI,AUTO,MODE0,MODE1)         |

| Output "H" voltage               | VOH       | IO_LVL<br>-0.4  | -          | IO_LVL          | V     | IOH=-1.0mA(DC)<br>(including output mode of I/O terminal) |

| Output "L" voltage               | VOL       | 0.0             | -          | 0.4             | V     | IOL=1.0mA(DC) (including output mode of I/O terminal)     |

<sup>\*</sup> IO\_LVL is a generic name of VDDIO, VDDI2C and AVDD.

# 2. DC characteristics (DAC)

(Unless otherwise specified VDD=1.50V, VDDIO=3.3V, VDDI2C=3.3V, AVDD=3.3V, GND=0.0V, Ta=25°C)

| Parameter                  | Cymphol | Limits |      |      | Unit | Condition                                                     |  |

|----------------------------|---------|--------|------|------|------|---------------------------------------------------------------|--|

| Parameter                  | Symbol  | MIN.   | TYP. | MAX. | Unit | Condition                                                     |  |

| Integral Non-linearity     | INL     | -      | ±4.0 | ±8.0 | LSB  | RL=37.5 $\Omega$ , RIREF=2.4k $\Omega$ , DAC resolution=10bit |  |

| Differential Non-linearity | DNL     | -      | ±1.0 | ±2.0 | LSB  | RL=37.5 $\Omega$ , RIREF=2.4k $\Omega$ , DAC resolution=10bit |  |

| Output Voltage (full scale | ) VFS   | 1.1    | 1.25 | 1.4  | V    | RL=37.5 $\Omega$ , RIREF=2.4k $\Omega$ , DAC resolution=10bit |  |

<sup>\*2</sup> Supply current(VDD) at color-bar image input in Fog-Reduction enable, AIE enable and Digital output disable settings.

# Electrical characteristics(AC characteristics)

# 1. Data Input Interface Timing

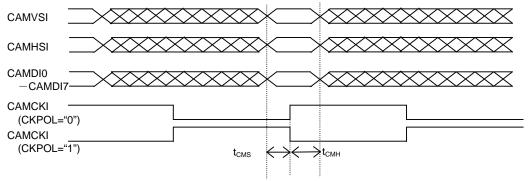

Fig.5 Data Input Interface Timing

| Symbol              | Description                          |          | MIN  | TYP | MAX | Unit |

|---------------------|--------------------------------------|----------|------|-----|-----|------|

| t <sub>CAMCKI</sub> | CAMCKI Clock Cycle                   |          | 27.8 | -   | -   | ns   |

| d <sub>CAMCKI</sub> | CAMCKI Clock Duty                    | 45       | 50   | 55  | %   |      |

| t <sub>CMS</sub>    | CAMCKI Rise / Fall Camera Setup Time |          | 8    | -   | -   | ns   |

|                     | CAMCKI Biog / Fall Corpora Hold Time | BU6520KV | 6    | -   | -   | ns   |

| t <sub>CMH</sub>    | CAMCKI Rise / Fall Camera Hold Time  | 5        | -    | -   | ns  |      |

<sup>\*</sup> CKPOL selects the CAMCKI polarity. (CKPOL is register at BU6520KV/BU6521KV)

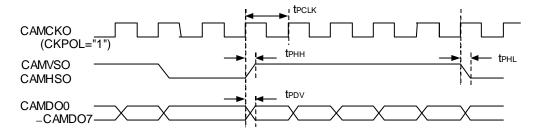

# 2. Data Output Interface Timing

Fig.6 Data Output Interface Timing

| Symbol                              | Description                              | MIN  | TYP | MAX | Unit |

|-------------------------------------|------------------------------------------|------|-----|-----|------|

| t <sub>PCLK</sub>                   | CAMCKO Clock Cycle                       | 27.8 | -   | -   | ns   |

| d <sub>PCLK</sub>                   | CAMCKO Clock Duty                        | 40   | 50  | 60  | %    |

| t <sub>PDV</sub>                    | Decision of CAMDO from CAMCKO            | -    | -   | 7   | ns   |

| t <sub>PHL</sub> , t <sub>PHH</sub> | Decision of CAMVSO or CAMHSO from CAMCKO | -    | -   | 7   | ns   |

<sup>\*</sup> This figure shows CKPOL setting is "1" In case of CKPOL= "0", CAMVSO, CAMHSO and CAMDO0-CAMCO7 change based on CAMCKO fall edge.

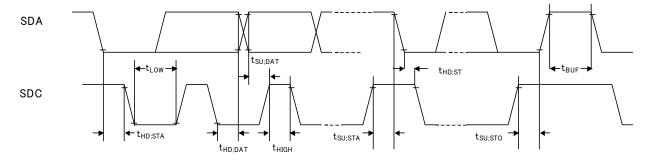

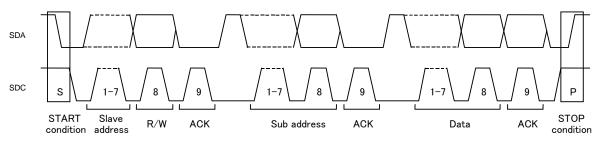

# 3. 2-line Serial Interface Timing

Fig.7 2-line Serial Interface Timing

| Symbol              | Description                                                                                      | MIN | TYP | MAX | Unit |

|---------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>SCL</sub>    | SDC Clock Frequency                                                                              | 0   | -   | 400 | kHz  |

| t <sub>HD;STA</sub> | Hold Time (repetition) "START" conditions. The first clock pulse is generated after this period. | 0.6 | -   | -   | μs   |

| $f_{LOW}$           | The "L" period of SDC clock                                                                      | 1.3 | -   | -   | μs   |

| t <sub>HIGH</sub>   | The "H" period of SDC clock                                                                      | 0.6 | -   | -   | μs   |

| t <sub>SU;STA</sub> | Setup Time of repetitive "START" conditions                                                      | 0.6 | -   | -   | μs   |

| t <sub>HD;DAT</sub> | Data Hold Time                                                                                   | 0   |     |     | μs   |

| t <sub>SU;DAT</sub> | Data Setup Time                                                                                  | 100 | -   | -   | ns   |

| t <sub>SU;STO</sub> | Setup Time of the "STOP" conditions                                                              | 0.6 | -   | -   | μs   |

| t <sub>BUF</sub>    | Bus free Time between "STOP" conditions and the "START" conditions                               | 1.3 | -   | -   | μs   |

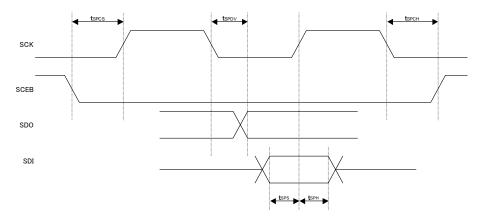

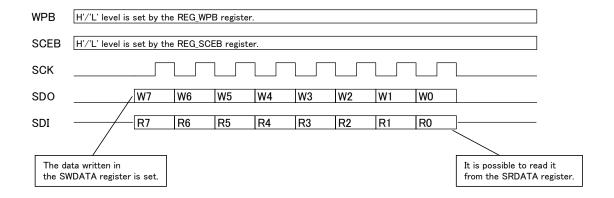

## 4. SPI-bus Interface Timing

Fig.8 SPI-bus Interface Timing

| Symbol             | Description                   | MIN | TYP                                | MAX   | Unit                |

|--------------------|-------------------------------|-----|------------------------------------|-------|---------------------|

| tspclk             | Clock Cycle                   | 2   | 736*1                              | 8192  | t <sub>CAMCKI</sub> |

| d <sub>SPCLK</sub> | Clock Duty                    | 45  | 50                                 | 55    | %                   |

| t <sub>SPCS</sub>  | SCK Rise SCEB Setup Time      | 4   | 738 <b>~</b><br>1105 <sup>*1</sup> | 12289 | t <sub>CAMCKI</sub> |

| t <sub>SPCH</sub>  | SCEB Rise after SCK Rise Time | 2   | 751 <sup>*1</sup>                  | 8319  | t <sub>CAMCKI</sub> |

| t <sub>SPDV</sub>  | Decision of SDO from SCK Fall | -   | -                                  | 28    | ns                  |

| t <sub>SPS</sub>   | SCK Rise SDI Setup Time       | -   | -                                  | 28    | ns                  |

| t <sub>SPH</sub>   | SCK Rise SDI Hold Time        | -   | -                                  | 28    | ns                  |

<sup>\*1</sup> Default status right after reset

When the automatic reading function with the AUTO pin is used, it becomes timing of SCEB to SCK as above. It is possible to access from the register of BU6520KV/BU6521KV to EEPROM.In that case, SCEB is controlled by the register.

After the value is set to the register, the SCEB pin is changed into the logic set at once.

# Functional descriptions

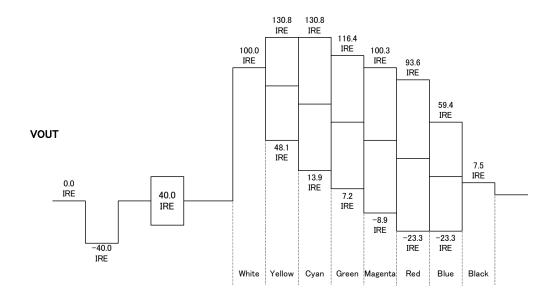

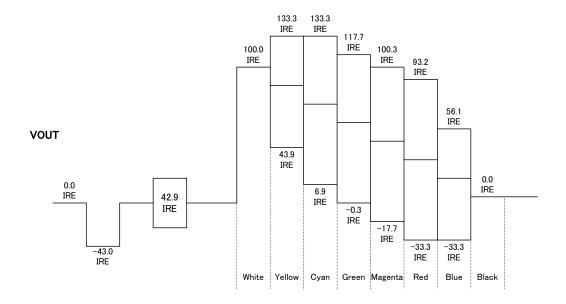

- 1. Analog Composite Output Waveform

- 1.1. Output waveform in NTSC

Fig.9 Color-bar corrugation in NTSC setting

# 1.2. Output waveform in PAL

Fig.10 Color-bar corrugation in PAL setting

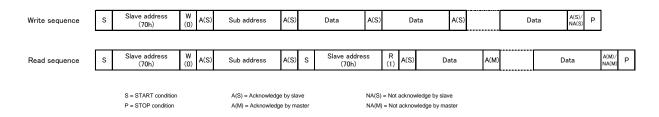

# 2. The 2 line formula serial interface format Slave address is 70h.

The sub-address is incremented automatically when accessing it (read / write) continuously 2 times or more.

Fig.11 Waveform of date transmission part

Fig.12 2-line serial interface format

#### 3. SPI-bus format

Fig.13 SPI-bus interface wave form

\* REG\_WPB, REG\_SCEB, SWDATA, and SRDATA in figure are the register names, and the each function is as follows.

REG\_WPB : Set WP Terminal logic. Register value is output directly.

REG\_SCEB : Set SCEB Terminal logic. Register value is output directly.

SWDATA[7:0] : Write data to EEPROM. Transfers MSB the first.

SRDATA[7:0] : Read data from EEPROM. Converts MSB the first.

The SCK clock frequency is as follows.

SCK frequency = CAMCKI frequency  $\div 2^{(SPIPREDIV+1)} \div (SPIDIV+1)$

Register range: SPIPREDIV = 0 to 7, SPIDIV = 0 to 31

When CAMCKI is 27MHz, SCK becomes 3.3 kHz from 13.5 MHz.

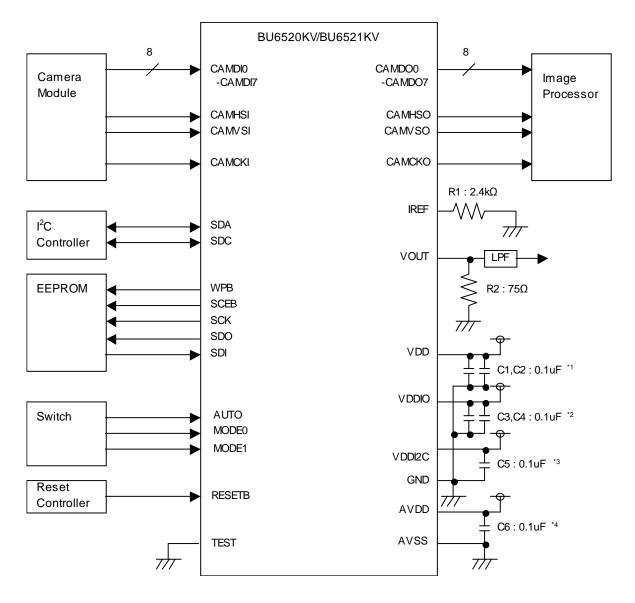

## Application example

<When registers are controlled by both of the automatic reading from EEPROM and the I<sup>2</sup>C controller >

<sup>\*1</sup> Please arrange a capacitor each near two VDD pin.

Fig.14 Application example 1

Fig.14 is a reference example when the system is connected, and the operation is not guaranteed.

<sup>\*2</sup> Please arrange a capacitor each near two VDDIO pin.

<sup>\*3</sup> Please arrange a capacitor near VDDI2C pin.

<sup>\*4</sup> Please arrange a capacitor near AVDD pin.

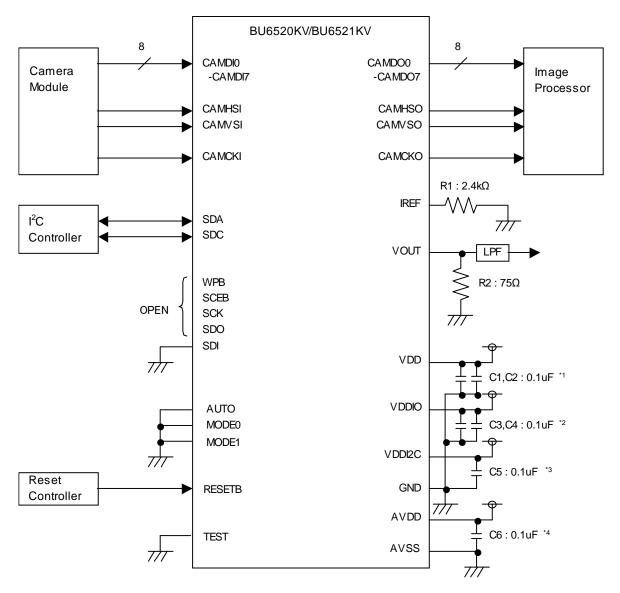

<When registers are controlled only by the I<sup>2</sup>C controller>

- \*1 Please arrange a capacitor each near two VDD pin.

\*2 Please arrange a capacitor each near two VDDIO p Please arrange a capacitor each near two VDDIO pin.

- Please arrange a capacitor near VDDI2C pin.

- Please arrange a capacitor near AVDD pin.

Fig.15 Application example 2

Fig.15 is a reference example when the system is connected, and the operation is not guaranteed.

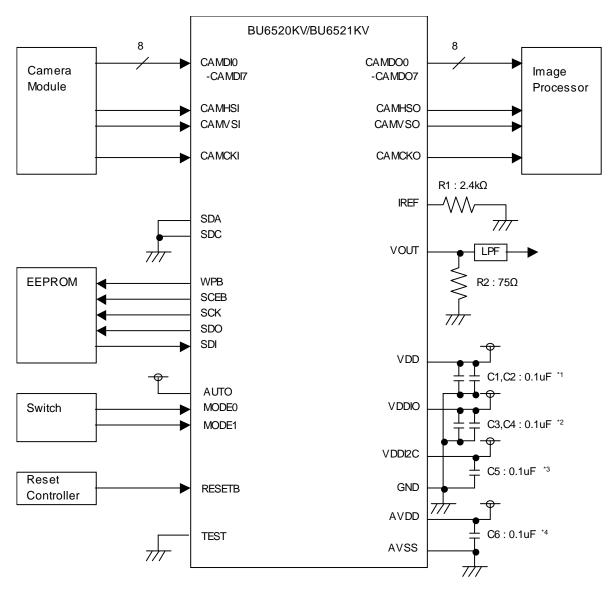

<When registers are controlled only by the automatic reading from EEPROM >

- \*1 Please arrange a capacitor each near two VDD pin.

- \*2 Please arrange a capacitor each near two VDDIO pin.

- \*3 Please arrange a capacitor near VDDI2C pin.

- \*4 Please arrange a capacitor near AVDD pin.

Fig.16 Application example 3

Fig.16 is a reference example when the system is connected, and the operation is not guaranteed.

#### Note for use

#### (1) Absolute Maximum Ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down devices, thus making impossible to identify breaking mode such as a short circuit or an open circuit. If any special mode exceeding the absolute maximum ratings is assumed, consideration should be given to take physical safety measures including the use of fuses, etc.

#### (2) Operating conditions

These conditions represent a range within which characteristics can be provided approximately as expected. The electrical characteristics are guaranteed under the conditions of each parameter.

#### (3) Reverse connection of power supply connector

The reverse connection of power supply connector can break down ICs. Take protective measures against the breakdown due to the reverse connection, such as mounting an external diode between the power supply and the IC's power supply terminal.

#### (4) Power supply line

Design PCB pattern to provide low impedance for the wiring between the power supply and the GND lines.

In this regard, for the digital block power supply and the analog block power supply, even though these power supplies has the same level of potential, separate the power supply pattern for the digital block from that for the analog block, thus suppressing the diffraction of digital noises to the analog block power supply resulting from impedance common to the wiring patterns. For the GND line, give consideration to design the patterns in a similar manner.

Furthermore, for all power supply terminals to ICs, mount a capacitor between the power supply and the GND terminal. At the same time, in order to use an electrolytic capacitor, thoroughly check to be sure the characteristics of the capacitor to be used present no problem including the occurrence of capacity dropout at a low temperature, thus determining the constant.

#### (5) GND voltage

Make setting of the potential of the GND terminal so that it will be maintained at the minimum in any operating state. Furthermore, check to be sure no terminals are at a potential lower than the GND voltage including an actual electric transient.

#### (6) Short circuit between terminals and erroneous mounting

In order to mount ICs on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can break down the ICs. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the ICs can break down.

#### (7) Operation in strong electromagnetic field

Be noted that using ICs in the strong electromagnetic field can malfunction them.

# (8) Inspection with set PCB

On the inspection with the set PCB, if a capacitor is connected to a low-impedance IC terminal, the IC can suffer stress. Therefore, be sure to discharge from the set PCB by each process. Furthermore, in order to mount or dismount the set PCB to/from the jig for the inspection process, be sure to turn OFF the power supply and then mount the set PCB to the jig. After the completion of the inspection, be sure to turn OFF the power supply and then dismount it from the jig. In addition, for protection against static electricity, establish a ground for the assembly process and pay thorough attention to the transportation and the storage of the set PCB.

#### (9) Input terminals}

In terms of the construction of IC, parasitic elements are inevitably formed in relation to potential. The operation of the parasitic element can cause interference with circuit operation, thus resulting in a malfunction and then breakdown of the input terminal. Therefore, pay thorough attention not to handle the input terminals, such as to apply to the input terminals a voltage lower than the GND respectively, so that any parasitic element will operate. Furthermore, do not apply a voltage to the input terminals when no power supply voltage is applied to the IC. In addition, even if the power supply voltage is applied, apply to the input terminals a voltage lower than the power supply voltage or within the guaranteed value of electrical characteristics.

# (10) Ground wiring pattern

If small-signal GND and large-current GND are provided, It will be recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Pay attention not to cause fluctuations in the GND wiring pattern of external parts as well.

#### (11) External capacitor

In order to use a ceramic capacitor as the external capacitor, determine the constant with consideration given to a degradation in the nominal capacitance due to DC bias and changes in the capacitance due to temperature, etc.

#### (12) Rush current

For ICs with more than one power supply, it is possible that rush current may flow instantaneously due to the internal powering sequence and delays. Therefore, give special consideration to power coupling capacitance, power wiring, width of GND wiring, and routing of wiring.

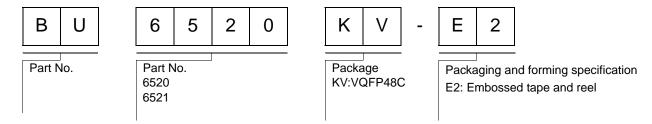

# Ordering part number

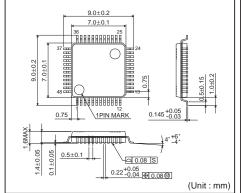

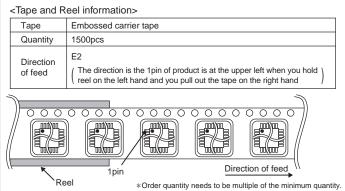

# VQFP48C

# **Notice**

#### **Precaution on using ROHM Products**

Our Products are designed and manufactured for application in ordinary electronic equipments (such as AV equipment, OA equipment, telecommunication equipment, home electronic appliances, amusement equipment, etc.). If you intend to use our Products in devices requiring extremely high reliability (such as medical equipment (Note 1), transport equipment, traffic equipment, aircraft/spacecraft, nuclear power controllers, fuel controllers, car equipment including car accessories, safety devices, etc.) and whose malfunction or failure may cause loss of human life, bodily injury or serious damage to property ("Specific Applications"), please consult with the ROHM sales representative in advance. Unless otherwise agreed in writing by ROHM in advance, ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of any ROHM's Products for Specific Applications.

(Note1) Medical Equipment Classification of the Specific Applications

| JAPAN   | USA     | EU         | CHINA    |

|---------|---------|------------|----------|

| CLASSⅢ  | CLASSII | CLASS II b | CLASSIII |

| CLASSIV |         | CLASSⅢ     |          |

- 2. ROHM designs and manufactures its Products subject to strict quality control system. However, semiconductor products can fail or malfunction at a certain rate. Please be sure to implement, at your own responsibilities, adequate safety measures including but not limited to fail-safe design against the physical injury, damage to any property, which a failure or malfunction of our Products may cause. The following are examples of safety measures:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits to reduce the impact of single or multiple circuit failure

- 3. Our Products are designed and manufactured for use under standard conditions and not under any special or extraordinary environments or conditions, as exemplified below. Accordingly, ROHM shall not be in any way responsible or liable for any damages, expenses or losses arising from the use of any ROHM's Products under any special or extraordinary environments or conditions. If you intend to use our Products under any special or extraordinary environments or conditions (as exemplified below), your independent verification and confirmation of product performance, reliability, etc, prior to use, must be necessary:

- [a] Use of our Products in any types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use of our Products outdoors or in places where the Products are exposed to direct sunlight or dust

- [c] Use of our Products in places where the Products are exposed to sea wind or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use of our Products in places where the Products are exposed to static electricity or electromagnetic waves

- [e] Use of our Products in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Sealing or coating our Products with resin or other coating materials

- [g] Use of our Products without cleaning residue of flux (even if you use no-clean type fluxes, cleaning residue of flux is recommended); or Washing our Products by using water or water-soluble cleaning agents for cleaning residue after soldering

- [h] Use of the Products in places subject to dew condensation

- 4. The Products are not subject to radiation-proof design.

- 5. Please verify and confirm characteristics of the final or mounted products in using the Products.

- 6. In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse. is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.

- 7. De-rate Power Dissipation (Pd) depending on Ambient temperature (Ta). When used in sealed area, confirm the actual ambient temperature.

- 8. Confirm that operation temperature is within the specified range described in the product specification.

- 9. ROHM shall not be in any way responsible or liable for failure induced under deviant condition from what is defined in this document.

#### Precaution for Mounting / Circuit board design

- 1. When a highly active halogenous (chlorine, bromine, etc.) flux is used, the residue of flux may negatively affect product performance and reliability.

- 2. In principle, the reflow soldering method must be used; if flow soldering method is preferred, please consult with the ROHM representative in advance.

For details, please refer to ROHM Mounting specification

# **Precautions Regarding Application Examples and External Circuits**

- If change is made to the constant of an external circuit, please allow a sufficient margin considering variations of the characteristics of the Products and external components, including transient characteristics, as well as static characteristics.

- You agree that application notes, reference designs, and associated data and information contained in this document are presented only as guidance for Products use. Therefore, in case you use such information, you are solely responsible for it and you must exercise your own independent verification and judgment in the use of such information contained in this document. ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of such information.

#### **Precaution for Electrostatic**

This Product is electrostatic sensitive product, which may be damaged due to electrostatic discharge. Please take proper caution in your manufacturing process and storage so that voltage exceeding the Products maximum rating will not be applied to Products. Please take special care under dry condition (e.g. Grounding of human body / equipment / solder iron, isolation from charged objects, setting of lonizer, friction prevention and temperature / humidity control).

# **Precaution for Storage / Transportation**

- 1. Product performance and soldered connections may deteriorate if the Products are stored in the places where:

- [a] the Products are exposed to sea winds or corrosive gases, including Cl2, H2S, NH3, SO2, and NO2

- [b] the temperature or humidity exceeds those recommended by ROHM

- the Products are exposed to direct sunshine or condensation

- [d] the Products are exposed to high Electrostatic

- 2. Even under ROHM recommended storage condition, solderability of products out of recommended storage time period may be degraded. It is strongly recommended to confirm solderability before using Products of which storage time is exceeding the recommended storage time period.

- 3. Store / transport cartons in the correct direction, which is indicated on a carton with a symbol. Otherwise bent leads may occur due to excessive stress applied when dropping of a carton.

- Use Products within the specified time after opening a humidity barrier bag. Baking is required before using Products of which storage time is exceeding the recommended storage time period.

#### **Precaution for Product Label**

QR code printed on ROHM Products label is for ROHM's internal use only.

#### **Precaution for Disposition**

When disposing Products please dispose them properly using an authorized industry waste company.

#### **Precaution for Foreign Exchange and Foreign Trade act**

Since our Products might fall under controlled goods prescribed by the applicable foreign exchange and foreign trade act, please consult with ROHM representative in case of export.

#### **Precaution Regarding Intellectual Property Rights**

- 1. All information and data including but not limited to application example contained in this document is for reference only. ROHM does not warrant that foregoing information or data will not infringe any intellectual property rights or any other rights of any third party regarding such information or data. ROHM shall not be in any way responsible or liable for infringement of any intellectual property rights or other damages arising from use of such information or data.:

- 2. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of ROHM or any third parties with respect to the information contained in this document.

# **Other Precaution**

- 1. This document may not be reprinted or reproduced, in whole or in part, without prior written consent of ROHM.

- 2. The Products may not be disassembled, converted, modified, reproduced or otherwise changed without prior written consent of ROHM.

- 3. In no event shall you use in any way whatsoever the Products and the related technical information contained in the Products or this document for any military purposes, including but not limited to, the development of mass-destruction weapons.

- The proper names of companies or products described in this document are trademarks or registered trademarks of ROHM, its affiliated companies or third parties.

#### **General Precaution**

- 1. Before you use our Products, you are requested to care fully read this document and fully understand its contents. ROHM shall not be in an y way responsible or liable for failure, malfunction or accident arising from the use of a ny ROHM's Products against warning, caution or note contained in this document.

- 2. All information contained in this docume nt is current as of the issuing date and subject to change without any prior notice. Before purchasing or using ROHM's Products, please confirm the latest information with a ROHM sale s representative.

- 3. The information contained in this doc ument is provided on an "as is" basis and ROHM does not warrant that all information contained in this document is accurate an d/or error-free. ROHM shall not be in an y way responsible or liable for any damages, expenses or losses incurred by you or third parties resulting from inaccuracy or errors of or concerning such information.

**Notice – WE** © 2014 ROHM Co., Ltd. All rights reserved. Rev.001

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ROHM Semiconductor: BU6520KV-E2 BU6521KV-E2