# LV8161MU

## Monolithic Linear IC Single-Phase Fan Motor Driver

ON Semiconductor®

http://onsemi.com

### Overview

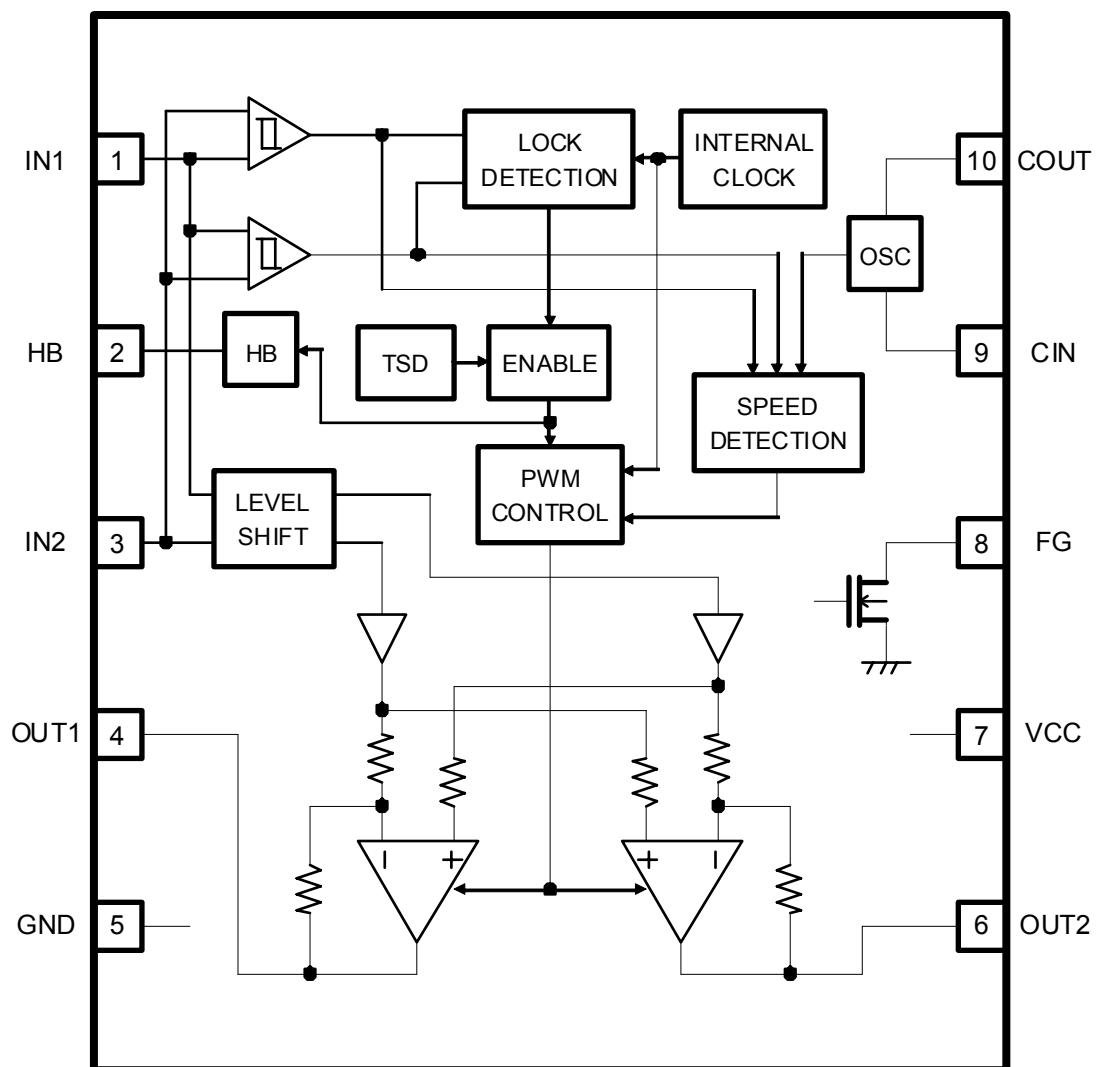

LV8161MU is the driver IC with BTL linear output for single-phase fan motor, and that drives at low noise by suppressing the reactive power. Moreover, it has the function to fix to the rotational speed corresponding to the oscillatory frequency set with CIN/COUT pins, and that speed control is done by PWM. So, the output signal forms BTL combined with PWM.

It is optimum for the small fan motor that requires low power dissipation, low noise, and the fixed rotational speed.

### Function

- Single-phase full wave operating by BTL output

(BTL amplifier gain: +45.5dB)

- The fixed rotational speed function

(possible to adjust the speed by the value of resistor and capacitor connected to CIN/COUT pins)

- Hall bias output pin (VHB = 1.03V (typ))

- FG (rotation signal) output pin (Open drain output)

- Built-in motor start-up assistance function

(PWM with 100% duty in output at start-up)

- Built-in lock protection and automatic restart circuit

- Built-in thermal-shutdown (TSD) circuit

UDFN10 (2.5 × 2.0)

### Specifications

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                      | Symbol               | Conditions            | Ratings    | Unit |

|--------------------------------|----------------------|-----------------------|------------|------|

| Maximum supply voltage         | V <sub>CC</sub> max  |                       | 7          | V    |

| OUT1/2 output current          | I <sub>OUT</sub> max |                       | 0.7        | A    |

| OUT1/2 output voltage handling | V <sub>OUT</sub> max |                       | 7          | V    |

| HB output current              | I <sub>HB</sub> max  |                       | 10         | mA   |

| CIN output voltage handling    | V <sub>PWM</sub>     |                       | 7          | V    |

| FG output current              | I <sub>FG</sub> max  |                       | 5          | mA   |

| FG output voltage handling     | V <sub>FG</sub> max  |                       | 7          | V    |

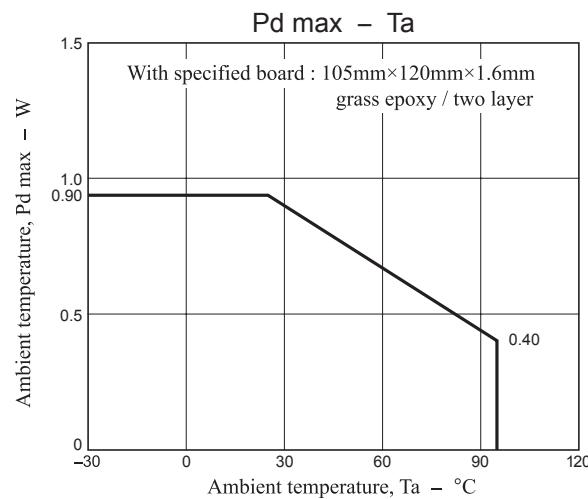

| Allowable power dissipation    | P <sub>d</sub> max   | IC on board*          | 900        | mW   |

| Operating temperature          | T <sub>opr</sub>     | T <sub>j</sub> <150°C | -30 to 95  | °C   |

| Storage temperature            | T <sub>stg</sub>     |                       | -55 to 150 | °C   |

\* Specified board: 105mm × 120mm × 1.6mm, glass epoxy board / two layers.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### ORDERING INFORMATION

See detailed ordering and shipping information on page 11 of this data sheet.

Recommended Operating Conditions at  $T_a = 25^\circ\text{C}$

| Parameter                                      | Symbol       | Conditions                                        | Ratings |     |     | Unit             |

|------------------------------------------------|--------------|---------------------------------------------------|---------|-----|-----|------------------|

|                                                |              |                                                   | min     | typ | max |                  |

| Recommended Supply voltage                     | $V_{CC}$     |                                                   |         | 5.0 |     | V                |

| Operating supply voltage                       | $V_{CC\ op}$ |                                                   | 2.2     |     | 6.0 | V                |

| Hall amplifier common mode input voltage range | $V_{ICM}$    |                                                   | 0.3     |     | 1.5 | V                |

| Feedback resistance                            | $R_{COUT}$   | Resistance between $C_{OUT}$ pin and $C_{IN}$ pin | 5       |     |     | $\text{k}\Omega$ |

| $C_{IN}$ input frequency range                 | $f_{CIN}$    |                                                   | 10      |     | 400 | kHz              |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Electrical Characteristics at  $T_a = 25^\circ\text{C}$ ,  $V_{CC} = 5\text{V}$

| Parameter                                     | Symbol           | Conditions                                            | Ratings |          |       | Unit             |

|-----------------------------------------------|------------------|-------------------------------------------------------|---------|----------|-------|------------------|

|                                               |                  |                                                       | min     | typ      | max   |                  |

| Circuit current                               | $I_{CC}$         |                                                       |         | 1.8      | 2.7   | mA               |

| HB bias voltage                               | $V_{HB}$         | $I_{HB}=-5\text{mA}$                                  | 0.90    | 1.03     | 1.20  | V                |

| OUT1/2 output "H" voltage                     | $V_{OH}$         | $I_{OUT}=-200\text{mA}$ ( $V_{OH}=V_{CC}-V_{OUT}$ )   |         | 0.16     | 0.24  | V                |

| OUT1/2 output "L" voltage                     | $V_{OL}$         | $I_{OUT}=200\text{mA}$                                |         | 0.10     | 0.15  | V                |

| Hall amplifier output offset voltage          | $V_{INOS}$       |                                                       | -10     |          | 10    | mV               |

| Hall amplifier voltage gain                   | $G_H$            |                                                       | 44.0    | 45.5     | 47.0  | dB               |

| Hall comparator hysteresis width              | $\Delta V_{HIN}$ | *1                                                    |         | $\pm 15$ |       | mV               |

| $C_{IN}$ input "H" threshold level            | $V_{CINH}$       |                                                       | 2.365   | 2.490    | 2.615 | V                |

| $C_{IN}$ input "L" threshold level            | $V_{CINL}$       |                                                       | 1.190   | 1.255    | 1.320 | V                |

| $C_{IN}$ input hysteresis width               | $\Delta V_{CIN}$ |                                                       | 1.175   | 1.235    | 1.295 | V                |

| $C_{OUT}$ output "H" voltage                  | $V_{COH}$        | $I_{COH}=-0.5\text{mA}$ ( $V_{COH}=V_{CC}-V_{COUT}$ ) | 60      | 80       | 100   | mV               |

| $C_{OUT}$ output "L" voltage                  | $V_{COL}$        | $I_{COL}=0.5\text{mA}$                                | 60      | 80       | 100   | mV               |

| Number of counts at speed detection 1         | $N_1$            |                                                       |         | 990      |       |                  |

| Number of counts at speed detection 2         | $N_2$            |                                                       |         | 1010     |       |                  |

| PWM frequency                                 | $f_{PWM}$        |                                                       | 22      | 32       | 42    | kHz              |

| PWM minimum "H" duty                          | $D_{Hmin}$       |                                                       | 16      | 20       | 24    | %                |

| FG output "L" voltage                         | $V_{FGL}$        | $I_{FG}=3\text{mA}$                                   |         |          | 0.3   | V                |

| FG output leakage current                     | $I_{FGL}$        | $V_{FG}=7\text{V}$                                    |         |          | 10    | $\mu\text{A}$    |

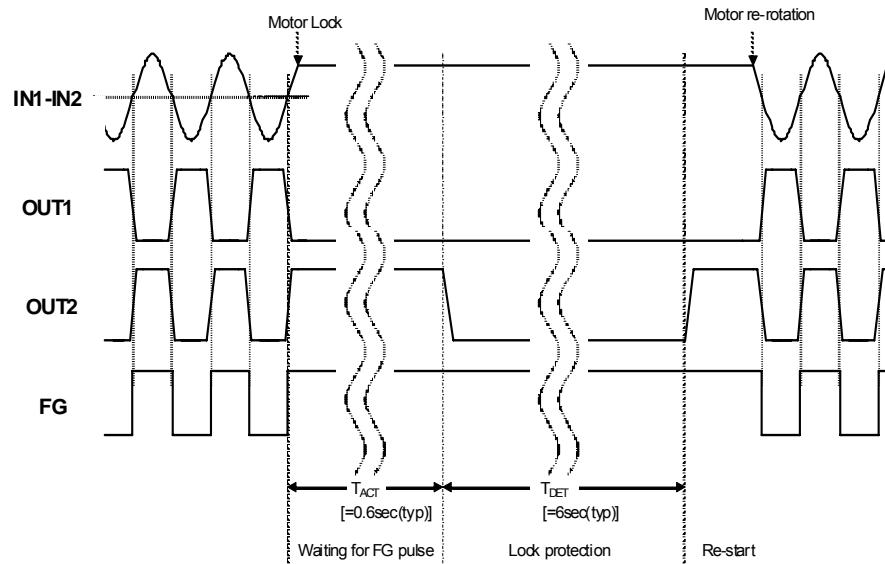

| Output on time in lock-detection              | $LT_1$           |                                                       | 0.4     | 0.6      | 0.8   | s                |

| Output off time in lock-detection             | $LT_2$           |                                                       | 4       | 6        | 8     | s                |

| Output on/off time ratio<br>In lock detection | $LRTO$           | $LRTO=LT_2/LT_1$                                      | 9       | 10       | 11    |                  |

| Thermal-shutdown operating temperature        | $T_{SD}$         | *1                                                    |         | 180      |       | $^\circ\text{C}$ |

| Thermal-shutdown hysteresis width             | $\Delta T_{SD}$  | *1                                                    |         | 30       |       | $^\circ\text{C}$ |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

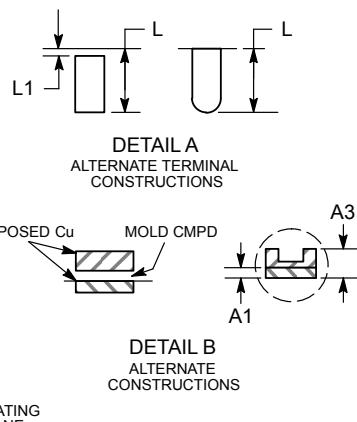

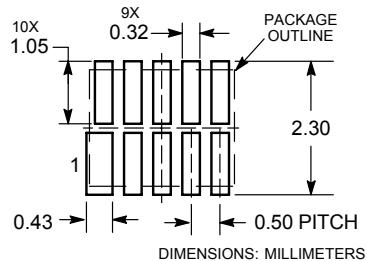

## Package Dimensions

UDFN10 2.5x2, 0.5P

CASE 517CM

ISSUE O

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSIONS b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM TERMINAL TIP.

4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

| MILLIMETERS |          |      |

|-------------|----------|------|

| DIM         | MIN      | MAX  |

| A           | 0.45     | 0.55 |

| A1          | 0.00     | 0.05 |

| A3          | 0.13 REF |      |

| b           | 0.20     | 0.30 |

| D           | 2.50 BSC |      |

| E           | 2.00 BSC |      |

| e           | 0.50 BSC |      |

| L           | 0.70     | 0.90 |

| L1          | 0.00     | 0.15 |

| L2          | 0.20 REF |      |

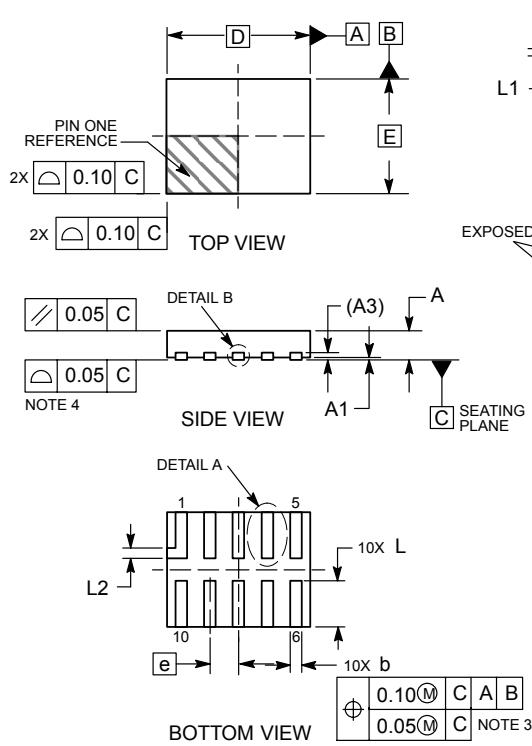

## GENERIC MARKING DIAGRAM\*

XXX = Specific Device Code

M = Date Code

■ = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking.

Pb-Free indicator, "G" or microdot "■", may or may not be present.

## RECOMMENDED MOUNTING FOOTPRINT

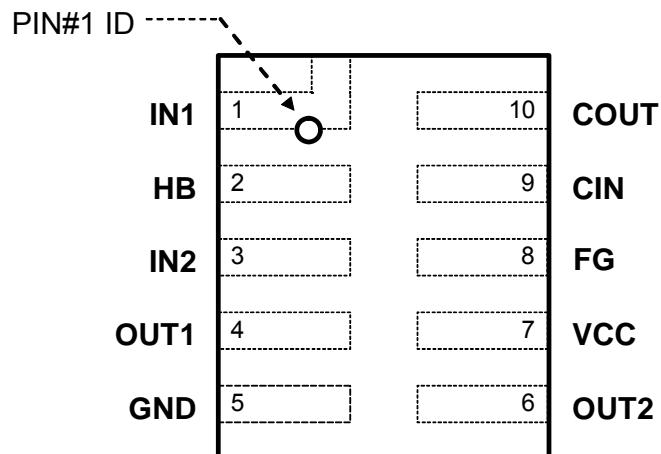

## Pin Assignment

**Package: UDFN10 2.5x2.0**

**(Top view)**

## Block Diagram

## Pin Function

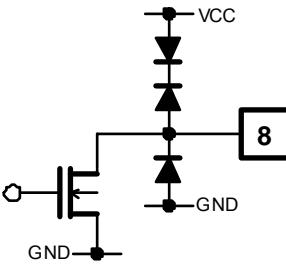

| Pin No. | Pin name | Function                                                                                                                                                                                                                                                                                                                | Equivalent circuit |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1       | IN1      | Hall input pin(1).                                                                                                                                                                                                                                                                                                      |                    |

| 3       | IN2      | Hall input pin (2).<br>Input the opposite phase signal to IN1 input.                                                                                                                                                                                                                                                    |                    |

| 2       | HB       | Regulated voltage output pin.<br>It is used for Hall bias. It is necessary to open when not using it.<br>Not to use HB bias and VCC bias together.                                                                                                                                                                      |                    |

| 4       | OUT1     | Output pin for motor drive (1).                                                                                                                                                                                                                                                                                         |                    |

| 6       | OUT2     | Output pin for motor drive (2).                                                                                                                                                                                                                                                                                         |                    |

| 5       | GND      | GND pin.                                                                                                                                                                                                                                                                                                                |                    |

| 7       | VCC      | Power supply pin.<br>The input voltage to this terminal must be stabilized without the influence of the noise, ripple, and etc.<br>Therefore, it is necessary to connect the capacitor near VCC terminal and GND terminal as much as possible. It must be over 1uF about the value of this capacitor. Not to detach it. |                    |

Continued on next page.

# LV8161MU

Continued from preceding page.

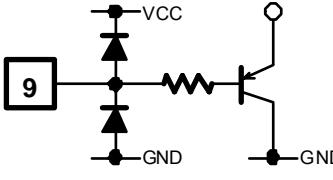

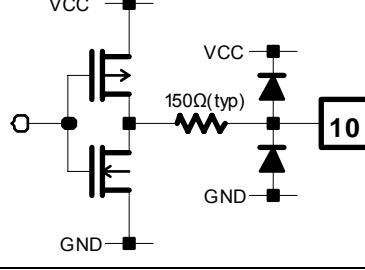

| Pin No. | Pin name | Function                                                                                                                                                              | Equivalent circuit                                                                  |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 8       | FG       | Output pin of the rotational signal.<br>It is necessary to open when not using it.                                                                                    |  |

| 9       | CIN      | Input pin of the clock for setting the rotational speed.                                                                                                              |  |

| 10      | COUT     | Output pin of the signal reversing CIN clock.<br>It works self-oscillating by returning this output signal through the filter with resistor and capacitor to CIN pin. |   |

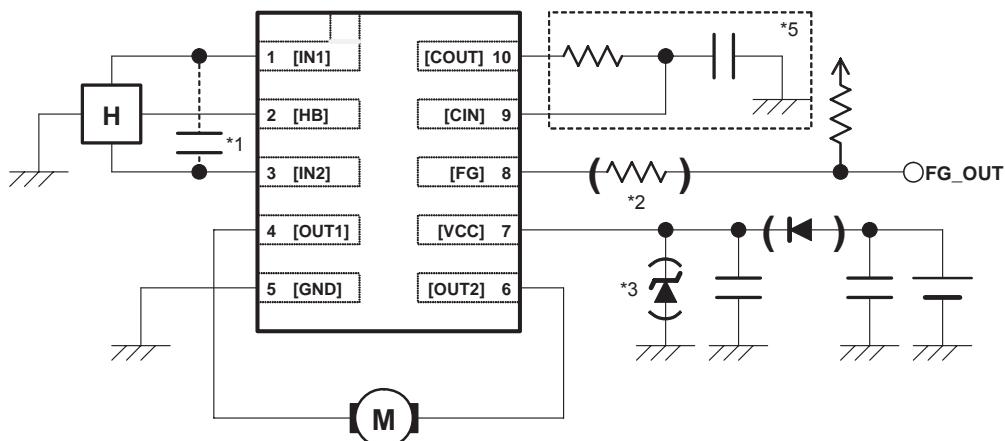

## Application Circuit Example

- \*1. The hall signal must be wired as short as possible for avoiding the noise.

If in influence of the noise, insert the capacitor between IN1 and IN2.

- \*2. It is recommendation that the resistance of  $1k\Omega$  or more is connected to FG pin to the series when GND-open or mis-connecting.

- \*3. The power-supply voltage might rise by the influence of the coil kickback etc. when using the diode for preventing the destruction at reverse-connected. In that case, insert the zener diode between the power supply and GND, and suppress the rise of the voltage of VCC pin.

- \*4. It is necessary to wire the VCC and the GND line as wide and short as possible.

- \*5. The reference clock that decides the rotational speed is generated with the connection of C1 pin, COUT pin, R1, and C1 as shown in figure. The relation among rotational speed  $N$  [rpm] of the motor with  $m$ -poles and the cycle of the reference clock  $T$  [s] is as follows.

$$\frac{N}{60} \times \frac{m}{2} = \frac{1}{1000 \times T}$$

Otherwise, the relation among T[s], C1 [F], and R1 [ $\Omega$ ] is as follows in consideration of 150 [ $\Omega$ ] built into COUT terminal.

$$T = 1.09862 \times C_1 \times (R_1 + 150)$$

Therefore, the relation among rotational speed  $N$  [rpm] of the motor with  $m$ -poles,  $C_1$  [F], and  $R_1$  [ $\Omega$ ] is led from above formula as follows.

$$\frac{N}{60} \times \frac{m}{2} = \frac{910.2328E-6}{C_1 \times (R_1 + 150)}$$

For example, when setting to rotate the motor with 4-poles at 2,700 [rpm] as  $C1=1,000$  [ $\mu$ F],

$$\frac{2700}{60} \times \frac{4}{2} = \frac{910.2328E - 6}{1000E - 12 \times (R_1 + 150)}$$

$$\Leftrightarrow R_1 = \frac{910232.8}{90} - 150 = 9.964[k\Omega]$$

Actually, the error margin of rotational speed is caused by the operation time of the circuit, the influence of parasitic elements on the circuit board, etc. Therefore, the value of C1 and R1 should be decided by confirming with the operation with the actual motor.

When the value of C1 or R1 changes by the thermal condition or the manufacturing tolerance etc, the rotational speed of the motor changes. So, it is necessary to use the capacitor and the resistor with better characteristics when high accuracy at rotational speed is needed.

\*Truth table

| IN1 | IN2 | (PWM) *1 | OUT1 | OUT2 | FG | Mode                 |

|-----|-----|----------|------|------|----|----------------------|

| H   | L   | H        | L    | H    | Z  | Drive (OUT2 to OUT1) |

|     |     | L        |      | L    |    | Regenerate           |

|     |     | X        |      | Z    |    | Lock protection *2   |

| L   | H   | H        | H    | L    | L  | Drive (OUT1 to OUT2) |

|     |     | L        | L    |      |    | Regenerate           |

|     |     | X        | Z    |      |    | Lock protection *2   |

X: Don't care, Z: High impedance

\*1. (PWM) is assumed the PWM signal generated in IC

\*2. When FG pulse is not generated in Output-On-time on Lock-Detection mode,

it goes into the state of Lock-Protection.

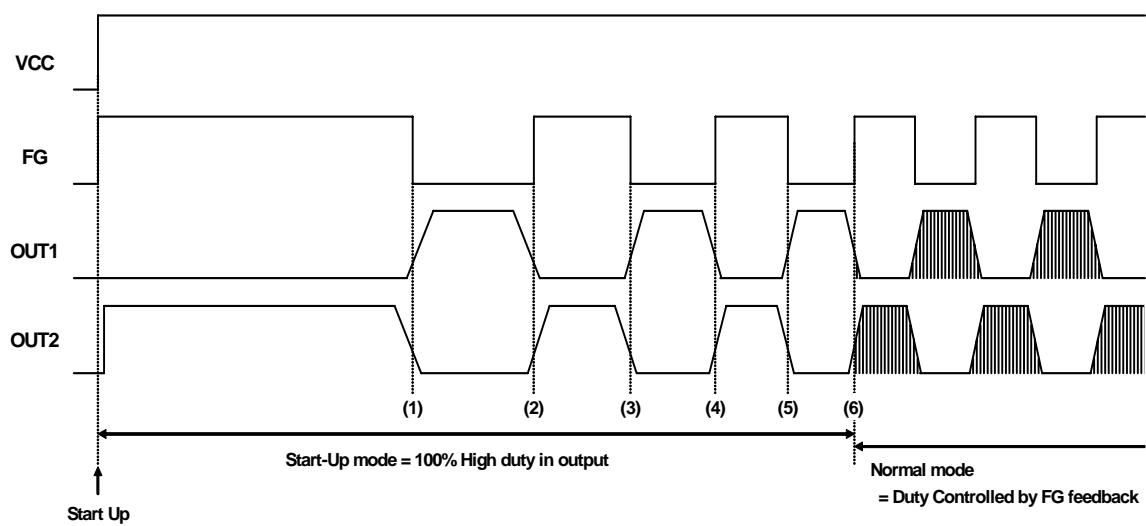

**Timing Chart****• Start Up**

# Output duty control switches from Start-Up mode to Normal mode after counting FG edge to 6.

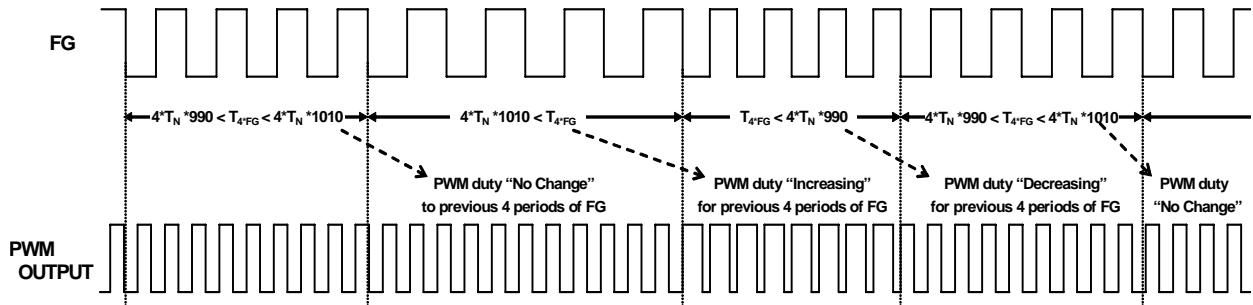

**• PWM duty control by FG feedback**

#  $T_{4*FG}$ : Time of 4 periods of FG output,  $T_N$ : Cycle time of COUT oscillation

**• Lock protection and Auto re-start**

# In the mode of motor protection, high side output turns to high impedance.

**ORDERING INFORMATION**

| Device      | Package                                        | Shipping (Qty / Packing) |

|-------------|------------------------------------------------|--------------------------|

| LV8161MUTAG | UDFN10 (2.5 x 2.0)<br>(Pb-Free / Halogen Free) | 3000 / Tape & Reel       |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[ON Semiconductor](#):

[LV8161MUTAG](#)