ISO5500

SLLSE64D - SEPTEMBER 2011 - REVISED JANUARY 2015

# ISO5500 2.5-A Isolated IGBT, MOSFET Gate Driver

#### **Features**

- 2.5-A Maximum Peak Output Current

- Drives IGBTs up to  $I_C = 150 \text{ A}$ ,  $V_{CE} = 600 \text{ V}$

- Capacitive Isolated Fault Feedback

- CMOS/TTL Compatible Inputs

- 300-ns Maximum Propagation Delay

- Soft IGBT Turnoff

- Integrated Fail-Safe IGBT Protection

- High V<sub>CE</sub> (DESAT) Detection

- Undervoltage Lockout (UVLO) Protection With Hysteresis

- User Configurable Functions

- Inverting, Noninverting Inputs

- Auto-Reset

- Auto-Shutdown

- Wide V<sub>CC1</sub> Range: 3 V to 5.5 V

- Wide V<sub>CC2</sub> Range: 15 V to 30 V

- Operating Temperature: -40°C to 125°C

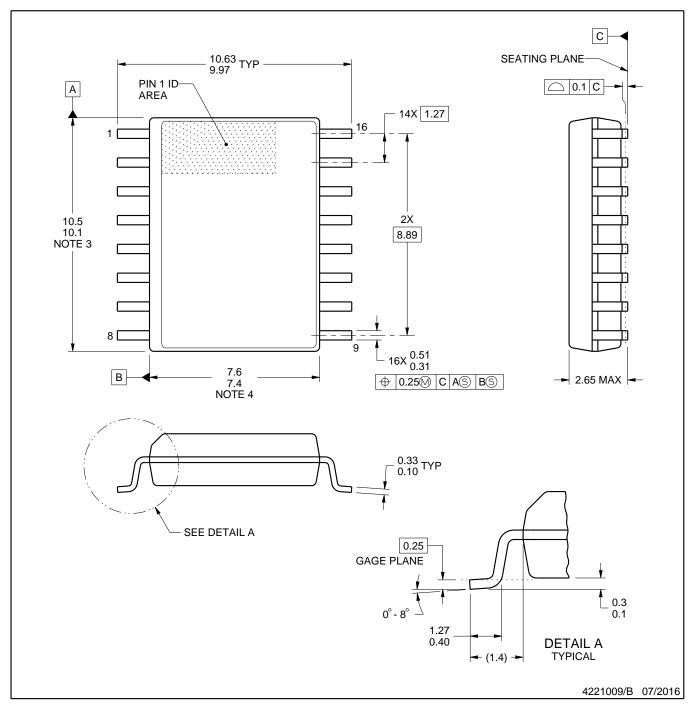

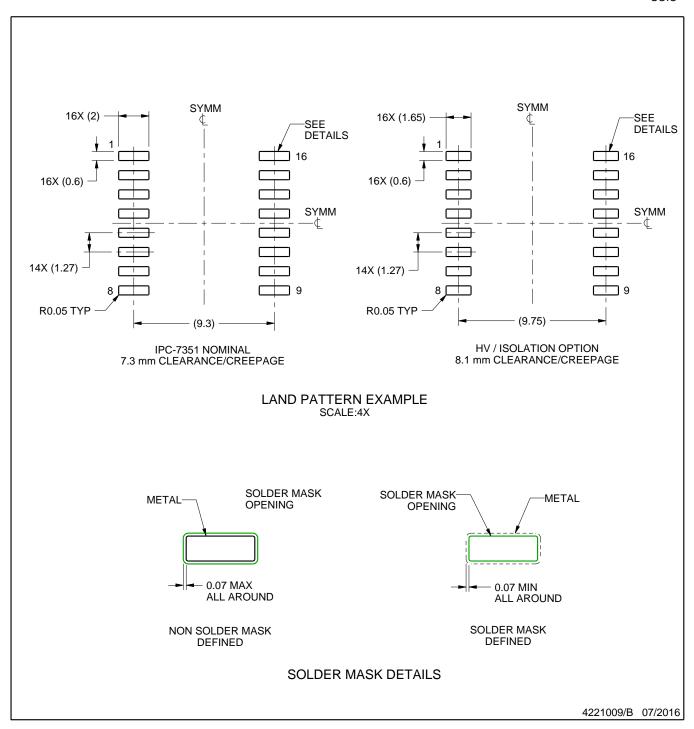

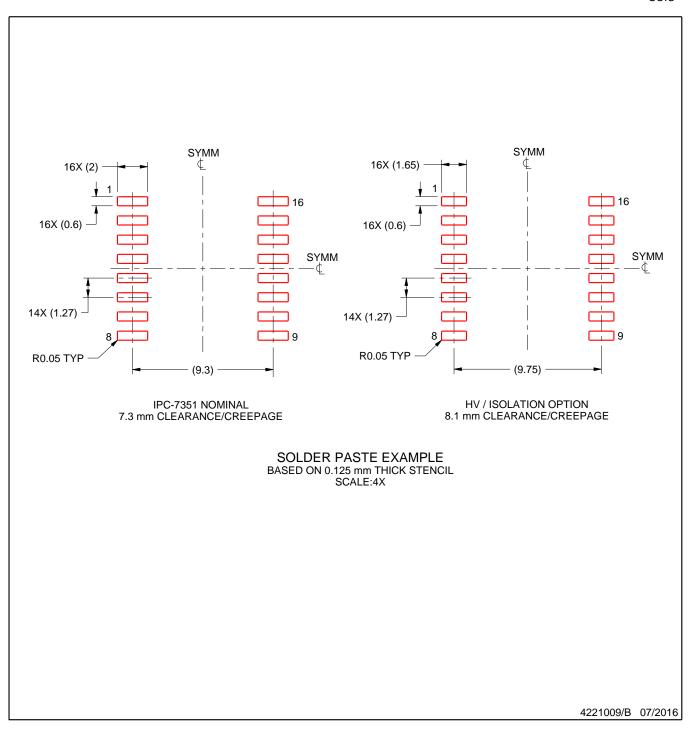

- Wide-Body SO-16 Package

- ±50-kV/us Transient Immunity Typical

- Safety and Regulatory Approvals:

- VDE 6000 V<sub>PK</sub> Basic Isolation per DIN V VDE V 0884-10 (VDE V 0884-10) and DIN EN

- 4243 V<sub>RMS</sub> Isolation for One Minute per UL

- CSA Component Acceptance Notice #5A, IEC 61010-1, and IEC 60950-1 End Equipment Standards

# **Applications**

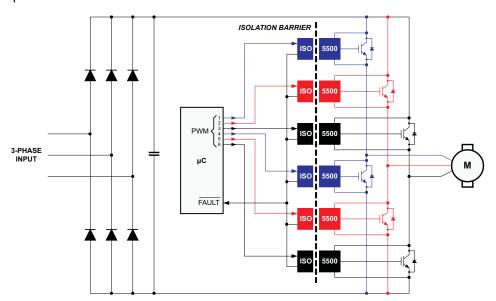

- Isolated IGBT and MOSFET Drives in

- Motor Control

- Motion Control

- **Industrial Inverters**

- Switched-Mode Power Supplies

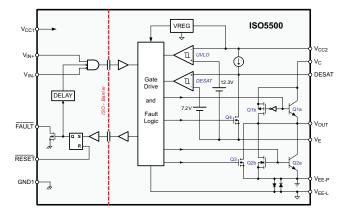

# 3 Description

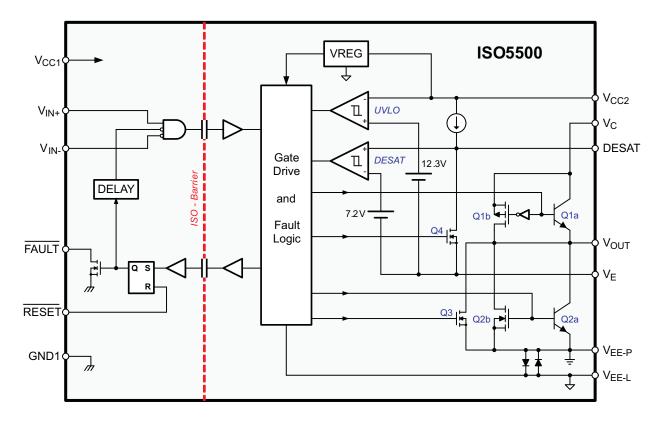

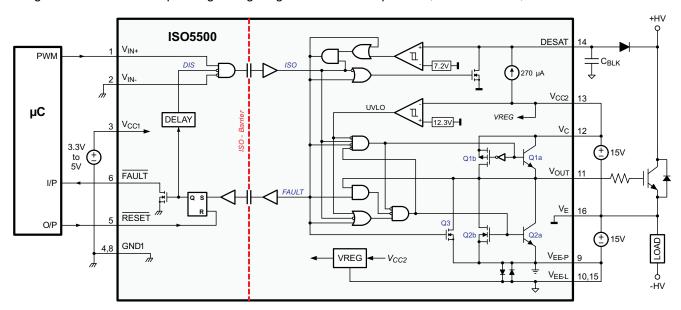

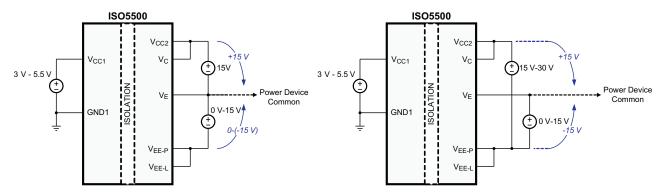

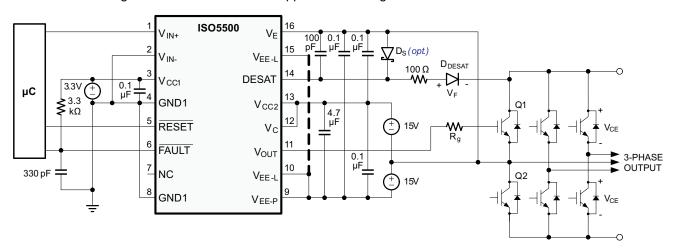

The ISO5500 is an isolated gate driver for IGBTs and MOSFETs with power ratings of up to  $I_C = 150$  A and V<sub>CE</sub> = 600 V. Input TTL logic and output power stage are separated by a capacitive, silicon dioxide (SiO<sub>2</sub>), isolation barrier. When used in conjunction with isolated power supplies, the device blocks high voltage, isolates ground, and prevents noise currents from entering the local ground and interfering with or damaging sensitive circuitry.

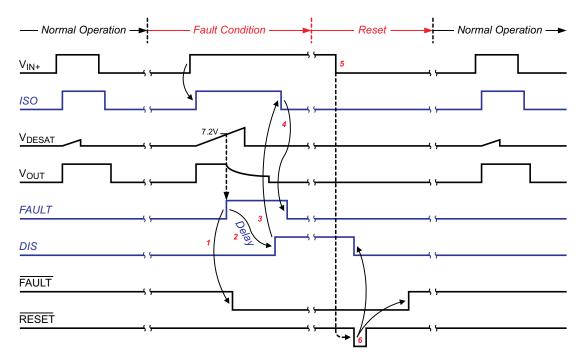

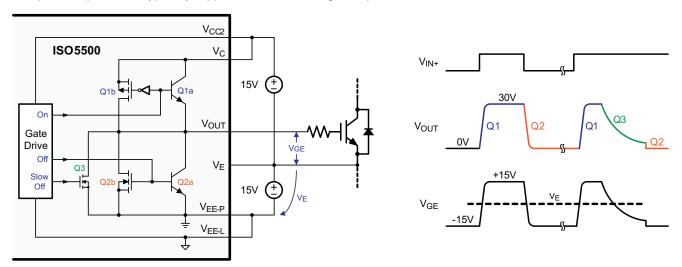

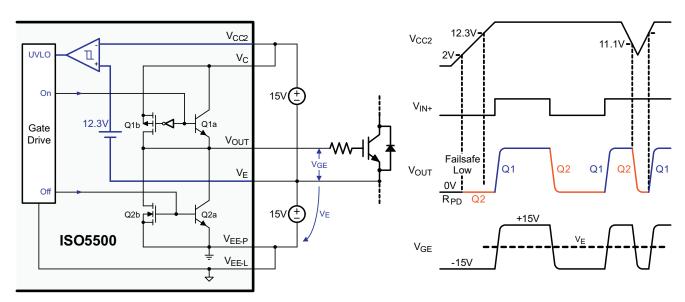

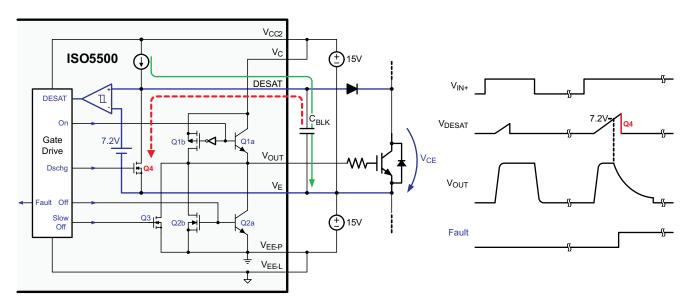

The device provides over-current protection (DESAT) to an IGBT or MOSFET while an Undervoltage Lockout circuit (UVLO) monitors the output power supply to ensure sufficient gate drive voltage. If the output supply drops below 12 V, the UVLO turns the power transistor off by driving the gate drive output to a logic low state.

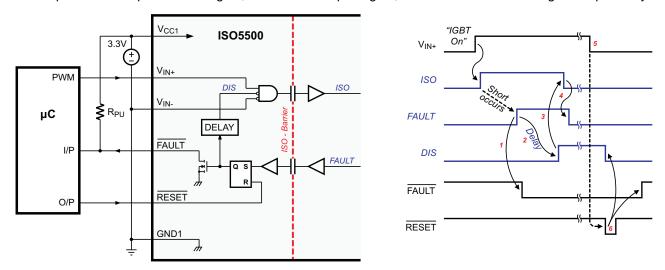

For a DESAT fault, the ISO5500 initiates a soft shutdown procedure that slowly reduces IGBT/MOSFET current to zero while preventing large di/dt induced voltage spikes. A fault signal is then transmitted across the isolation barrier, actively driving the open-drain FAULT output low and disabling the device inputs. The inputs are blocked as long as the FAULT-pin is low. FAULT remains low until the inputs are configured for an output low state, followed by a logic low input on the RESET pin.

The ISO5500 is available in a 16-pin SOIC package and is specified for operating temperatures from -40°C to 125°C.

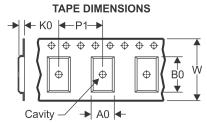

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)    |  |  |

|-------------|-----------|--------------------|--|--|

| ISO5500     | SOIC (16) | 10.30 mm × 7.50 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

#### **Functional Block Diagram**

# **Table of Contents**

| 1 | Features 1                           |    | 8.3 Feature Description              | 17              |

|---|--------------------------------------|----|--------------------------------------|-----------------|

| 2 | Applications 1                       |    | 8.4 Device Functional Modes          | 25              |

| 3 | Description 1                        | 9  | Application and Implementation       | 26              |

| 4 | Revision History2                    |    | 9.1 Application Information          | 26              |

| 5 | Pin Configuration and Functions      |    | 9.2 Typical Application              | 26              |

| 6 | Specifications4                      | 10 | Power Supply Recommendations         | 35              |

| ٠ | 6.1 Absolute Maximum Ratings         | 11 | Layout                               | 35              |

|   | 6.2 ESD Ratings                      |    | 11.1 Layout Guidelines               | 35              |

|   | 6.3 Recommended Operating Conditions |    | 11.2 PCB Material                    | 35              |

|   | 6.4 Thermal Information              |    | 11.3 Layout Example                  | 35              |

|   | 6.5 Electrical Characteristics 5     | 12 | Device and Documentation Support     | <mark>36</mark> |

|   | 6.6 Switching Characteristics 6      |    | 12.1 Device Support                  | 36              |

|   | 6.7 Typical Characteristics          |    | 12.2 Documentation Support           | 36              |

| 7 | Parameter Measurement Information 12 |    | 12.3 Trademarks                      | 36              |

| 8 | Detailed Description 16              |    | 12.4 Electrostatic Discharge Caution | 36              |

| • | 8.1 Overview                         | 13 | Mechanical, Packaging, and Orderable |                 |

|   | 8.2 Functional Block Diagram         |    | Information                          | 36              |

|   |                                      |    |                                      |                 |

# 4 Revision History

| CI | nanges from Revision C (June 2013) to Revision D                                                                                                                                                                                                                                                                             | Page                                   |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| •  | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |                                        |

| •  | VDE standard changed to DIN V VDE V 0884-10 (VDE V 0884-10):2006-12                                                                                                                                                                                                                                                          | ······································ |

| •  | Added FAULT limits to Absolute Maximum Ratings                                                                                                                                                                                                                                                                               | 4                                      |

| CI | nanges from Revision B (May 2013) to Revision C                                                                                                                                                                                                                                                                              | Page                                   |

| •  | Changed V <sub>CE</sub> from1200 V to 600 V                                                                                                                                                                                                                                                                                  |                                        |

| •  | Added the Thermal Information table inside the data sheet below the Absolute Maximum Ratings table                                                                                                                                                                                                                           | !                                      |

| •  | Changed row V <sub>IORM</sub> and V <sub>PR</sub> specification from V <sub>IORM</sub> of 1200V <sub>pk</sub> to 680 V <sub>pk</sub>                                                                                                                                                                                         | 17                                     |

| •  | Changed 1200 V <sub>PK</sub> in the Regulatory Information table from 1200 V <sub>PK</sub> to 680 V <sub>PK</sub>                                                                                                                                                                                                            | 17                                     |

| •  | Deleted last row of the IEC 60664-1 Rating Table                                                                                                                                                                                                                                                                             | 18                                     |

| •  | Added Isolation Lifetime at a Maximum Continuous Working Voltage table                                                                                                                                                                                                                                                       | 18                                     |

| •  | Added Function Table under the Functional Block Diagram                                                                                                                                                                                                                                                                      | 2                                      |

| CI | nanges from Revision A (July 2012) to Revision B                                                                                                                                                                                                                                                                             | Page                                   |

| •  | Changed the Regulatory Approvals List                                                                                                                                                                                                                                                                                        |                                        |

| •  | Changed the REGULATORY INFORMATION table, VDE Column From: File Number: pending To: File Number: 40016131                                                                                                                                                                                                                    | 1                                      |

| •  | Changed the REGULATORY INFORMATION table, CSA Column From: File Number: pending To: File Number: 220991                                                                                                                                                                                                                      | 13                                     |

Submit Documentation Feedback

Changes from Original (September 2011) to Revision A

Copyright © 2011–2015, Texas Instruments Incorporated

Page

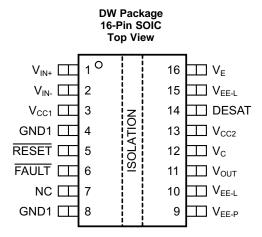

# 5 Pin Configuration and Functions

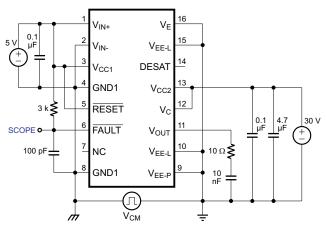

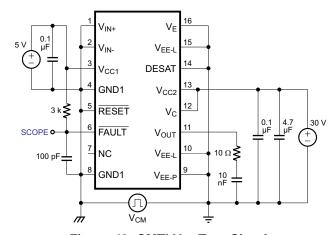

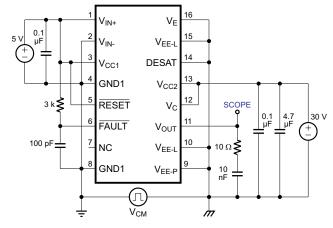

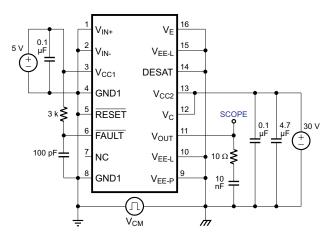

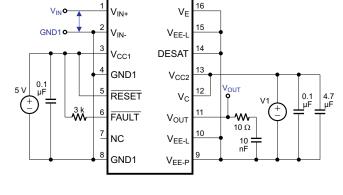

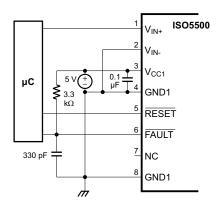

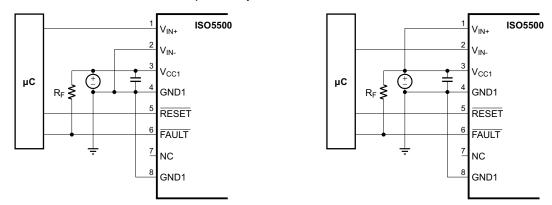

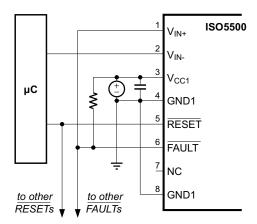

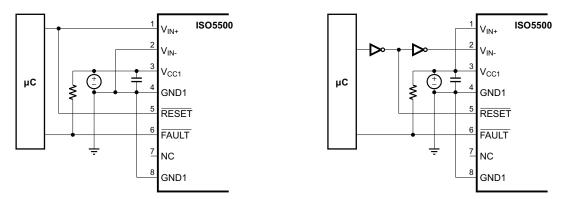

#### **Pin Functions**

|        | PIN               | 1/0    | DESCRIPTION                                                                                                                                                                |

|--------|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME              | 1/0    | DESCRIPTION                                                                                                                                                                |

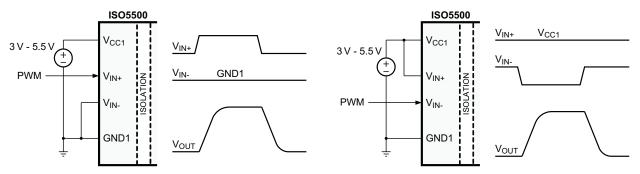

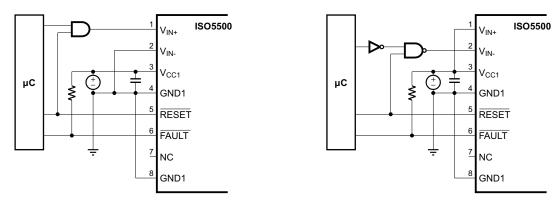

| 1      | $V_{IN+}$         | I      | Noninverting gate drive voltage control input                                                                                                                              |

| 2      | $V_{IN-}$         | I      | Inverting gate drive voltage control input                                                                                                                                 |

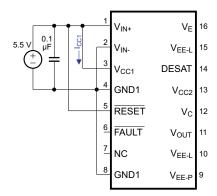

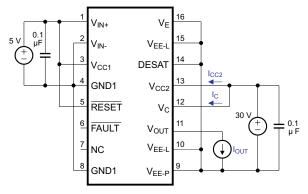

| 3      | V <sub>CC1</sub>  | Supply | Positive input supply (3 V to 5.5 V)                                                                                                                                       |

| 4,8    | GND1              | Ground | Input ground                                                                                                                                                               |

| 5      | RESET             | I      | FAULT reset input                                                                                                                                                          |

| 6      | FAULT             | 0      | Open-drain output. Connect to 3.3k pullup resistor                                                                                                                         |

| 7      | NC                | NC     | Not connected                                                                                                                                                              |

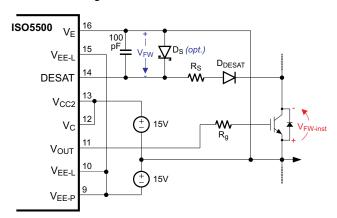

| 9      | $V_{EE-P}$        | Supply | Most negative output-supply potential of the power output. Connect externally to pin 10.                                                                                   |

| 10, 15 | V <sub>EE-L</sub> | Supply | Most negative output-supply potential of the logic circuitry. Pin 10 and 15 are internally connected. Connect at least pin 10 externally to pin 9. Pin 15 can be floating. |

| 11     | V <sub>OUT</sub>  | 0      | Gate drive output voltage                                                                                                                                                  |

| 12     | V <sub>C</sub>    | Supply | Gate driver supply. Connect to V <sub>CC2</sub> .                                                                                                                          |

| 13     | V <sub>CC2</sub>  | Supply | Most positive output supply potential                                                                                                                                      |

| 14     | DESAT             | I      | Desaturation voltage input                                                                                                                                                 |

| 16     | V <sub>E</sub>    | Ground | Gate drive common. Connect to IGBT Emitter.                                                                                                                                |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

|                                                      |                                                    | MIN                  | MAX                                                                          | UNIT |

|------------------------------------------------------|----------------------------------------------------|----------------------|------------------------------------------------------------------------------|------|

| Supply voltage, V <sub>CC1</sub>                     |                                                    | -0.5                 | 6                                                                            | V    |

| Total output supply voltage, V <sub>OUT(total)</sub> | (V <sub>CC2</sub> – V <sub>EE-P</sub> )            | -0.5                 | 35                                                                           | V    |

| Positive output supply voltage, V <sub>OUT+</sub>    | (V <sub>CC2</sub> - V <sub>E</sub> )               | -0.5                 | 35 –<br>(V <sub>E</sub> – V <sub>EE-P</sub> )                                | V    |

| Negative output supply voltage, V <sub>OUT</sub> .   | $(V_E - V_{EE-P})$                                 | -0.5                 | $V_{CC2}$                                                                    | V    |

| Valtage                                              | DESAT                                              | V <sub>E</sub> - 0.5 | V <sub>CC2</sub>                                                             | V    |

| Voltage at                                           | V <sub>IN+</sub> , V <sub>IN-</sub> , RESET, FAULT | -0.5                 | 6<br>35<br>35 –<br>(V <sub>E</sub> – V <sub>EE-P</sub> )<br>V <sub>CC2</sub> | V    |

| Peak gate drive output voltage                       | $V_{o(peak)}$                                      | -0.5                 | $V_{CC2}$                                                                    | V    |

| Collector voltage, V <sub>C</sub>                    |                                                    | -0.5                 | $V_{CC2}$                                                                    | V    |

| Output current , I <sub>O</sub> <sup>(1)</sup>       |                                                    |                      | ±2.8                                                                         | Α    |

| FAULT output current, I <sub>FL</sub>                |                                                    |                      | ±20                                                                          | mA   |

| Maximum junction temperature, T <sub>J</sub>         |                                                    |                      | 170                                                                          | °C   |

| Storage temperature, T <sub>stg</sub>                |                                                    | -65                  | 150                                                                          | °C   |

<sup>(1)</sup> Maximum pulse width = 10  $\mu$ s, maximum duty cycle = 0.2%.

# 6.2 ESD Ratings

|                                            |                                                                     |                                   | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------------------|-----------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4000                             |       |      |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) |                                   | V     |      |

|                                            |                                                                     | Machine model JEDEC JESD22-A115-A | ±200  |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                                                                             | MIN                   | NOM MAX                                       | UNIT |

|-------------------------|---------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------|------|

| V <sub>CC1</sub>        | Supply voltage                                                                              | 3                     | 5.5                                           | V    |

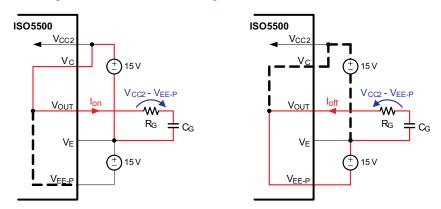

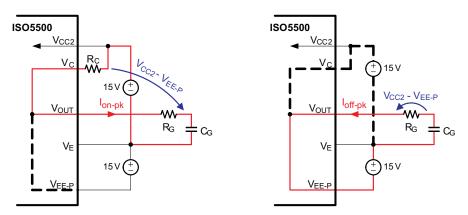

| V <sub>OUT(total)</sub> | Total output supply voltage (V <sub>CC2</sub> – V <sub>EE-P</sub> )                         | 15                    | 30                                            | V    |

| V <sub>OUT+</sub>       | Positive output supply voltage (V <sub>CC2</sub> – V <sub>E</sub> )                         | 15                    | 30 – (V <sub>E</sub> –<br>V <sub>EE-P</sub> ) | V    |

| V <sub>OUT</sub>        | Negative output supply voltage (V <sub>E</sub> – V <sub>EE-P</sub> )                        | 0                     | 15                                            | V    |

| V <sub>C</sub>          | Collector voltage                                                                           | V <sub>EE-P</sub> + 8 | V <sub>CC2</sub>                              | V    |

| t <sub>ui</sub>         | Input pulse width                                                                           | 0.1                   |                                               | μs   |

| t <sub>uiR</sub>        | RESET Input pulse width                                                                     | 0.1                   |                                               | μs   |

| V <sub>IH</sub>         | High-level input voltage (V <sub>IN+</sub> , V <sub>IN-</sub> , RESET)                      | 2                     | V <sub>CC</sub>                               | V    |

| V <sub>IL</sub>         | Low-level input voltage (V <sub>IN+</sub> , V <sub>IN-</sub> , RESET)                       | 0                     | 0.8                                           | V    |

| f <sub>INP</sub>        | Input frequency                                                                             |                       | 520 <sup>(1)</sup>                            | kHz  |

| V <sub>SUP_SR</sub>     | Supply Slew Rate (V <sub>CC1</sub> or V <sub>CC2</sub> – V <sub>EE-P</sub> ) <sup>(2)</sup> |                       | 75                                            | V/ms |

| TJ                      | Junction temperature                                                                        | -40                   | 150                                           | °C   |

| T <sub>A</sub>          | Ambient temperature                                                                         | -40                   | 25 125                                        | °C   |

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

If  $T_A$  = 125°C,  $V_{CC1}$ = 5.5 V,  $V_{CC2}$  = 30 V,  $R_G$  = 10  $\Omega$ ,  $C_L$  = 1 nF If  $V_{CC1}$  skew is faster that 75 V/ms (especially for the falling edge) then  $V_{CC2}$  must be powered up after  $V_{CC1}$  and powered down before V<sub>CC1</sub> to avoid output glitches.

#### 6.4 Thermal Information

|                       |                                                     | ISO5500              |      |

|-----------------------|-----------------------------------------------------|----------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                       | DW (SOIC) 16<br>PINS | UNIT |

| $\theta_{JA}$         | Junction-to-ambient thermal resistance              | 76                   |      |

| $\theta_{JCtop}$      | Junction-to-case (top) thermal resistance           | 34                   |      |

| $\theta_{JB}$         | Junction-to-board thermal resistance                | 36                   | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter          | 8                    |      |

| ΨЈВ                   | Junction-to-board characterization parameter        | 35                   |      |

| T <sub>SHDN+</sub>    | There of Obstations                                 | 185                  | °C   |

| T <sub>SHDN</sub> -   | Thermal Shutdown                                    | 173                  | °C   |

| T <sub>SHDN-HYS</sub> | Thermal Shutdown Hysteresis                         | 12                   | °C   |

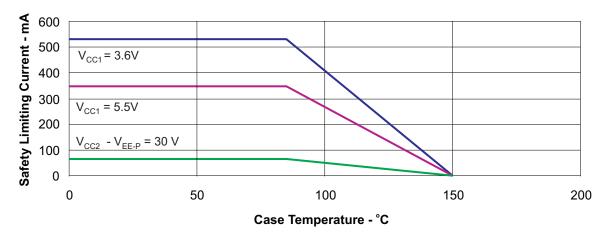

| P <sub>D</sub>        | Power Dissipation See Equation 2 through Equation 6 | 592                  | mW   |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

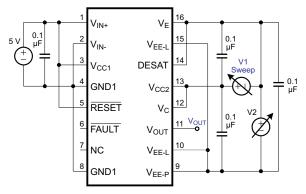

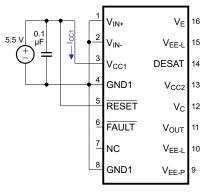

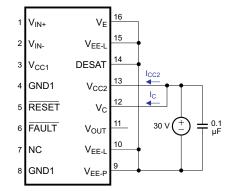

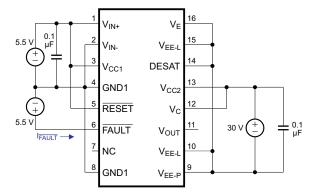

All typical values are at  $T_A = 25$ °C,  $V_{CC1} = 5$  V,  $V_{CC2} - V_E = 30$  V,  $V_E - V_{EE-P} = 0$  V (unless otherwise noted)

|                         | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | TEST CONDITIONS                                                                          | MIN                  | TYP                  | MAX  | UNIT |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|----------------------|----------------------|------|------|--|

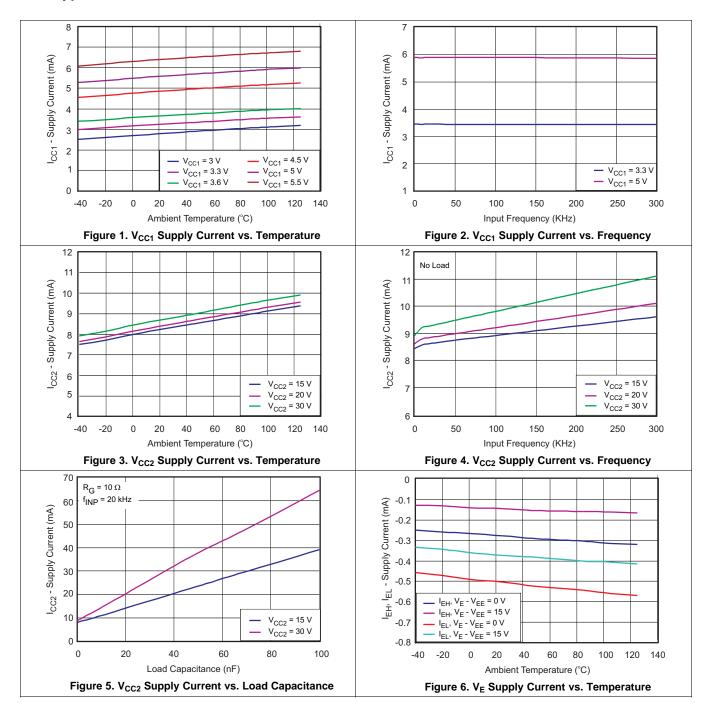

|                         | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Quiescent                               | V <sub>I</sub> = V <sub>CC1</sub> or 0 V, No load, See Figure 1,                         |                      | 5.5                  | 8.5  |      |  |

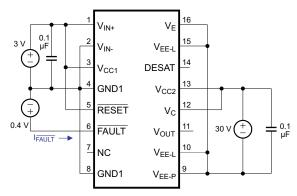

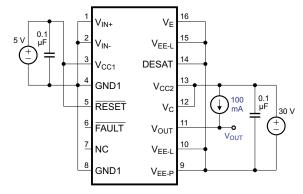

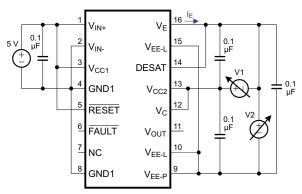

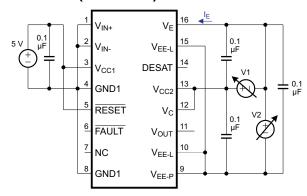

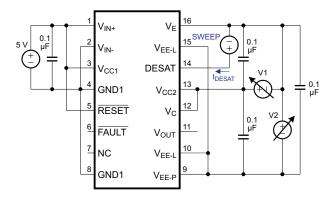

| I <sub>CC1</sub>        | Supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 300 kHz                                 | Figure 2, Figure 28, and Figure 29                                                       |                      | 5.7                  | 8.7  | mA   |  |

|                         | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Quiescent                               | V <sub>I</sub> = V <sub>CC1</sub> or 0 V, No load, See Figure 3                          |                      | 8.4                  | 12   |      |  |

| I <sub>CC2</sub>        | Supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 300 kHz                                 | through Figure 5, Figure 30, and Figure 31                                               |                      | 9                    | 14   | mA   |  |

|                         | Liberta de la compansa de la compans |                                         | I <sub>OUT</sub> = 0, See Figure 27 and Figure 30                                        |                      |                      | 1.3  | A    |  |

| I <sub>CH</sub>         | High-level collector curre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ent                                     | $I_{OUT} = -650 \mu A$ , See Figure 27 and Figure 30                                     |                      |                      | 1.9  | mA   |  |

| I <sub>CL</sub>         | Low-level collector currer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nt                                      | See Figure 27 and Figure 31                                                              |                      |                      | 0.4  | mA   |  |

| I <sub>EH</sub>         | V <sub>E</sub> High-level supply curr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rent                                    | See Figure 6 and Figure 40                                                               | -0.5                 | -0.3                 |      | mA   |  |

| I <sub>EL</sub>         | V <sub>E</sub> Low-level supply curre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ent                                     | See Figure 6 and Figure 41                                                               | -0.8                 | -0.53                |      | mA   |  |

| I <sub>IH</sub>         | High-level input leakage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | IN from 0 to V                                                                           |                      |                      | 10   |      |  |

| I <sub>IL</sub>         | Low-level input leakage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         | IN from 0 to V <sub>CC</sub>                                                             |                      |                      |      | μA   |  |

| I <sub>FH</sub>         | High-level FAULT pin ou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | tput current                            | $V_{\overline{FAULT}} = V_{CC1}$ , no pull-up,<br>See Figure 33                          | -10                  |                      | 10   | μΑ   |  |

| I <sub>FL</sub>         | Low-level FAULT pin out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | put current                             | V <sub>FAULT</sub> = 0.4 V, no pull-up, See Figure 34                                    | 5                    | 12                   |      | mA   |  |

| V <sub>IT+(UVLO)</sub>  | Positive-going UVLO three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | eshold voltage                          | See Figure 32                                                                            |                      | 12.3                 | 13.5 | ٧    |  |

| V <sub>IT-(UVLO)</sub>  | Negative-going UVLO the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | reshold voltage                         |                                                                                          |                      | 11.1                 | 12.4 |      |  |

| V <sub>HYS (UVLO)</sub> | UVLO Hysteresis voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e (V <sub>IT+</sub> – V <sub>IT</sub> ) |                                                                                          | 0.7                  | 1.2                  |      |      |  |

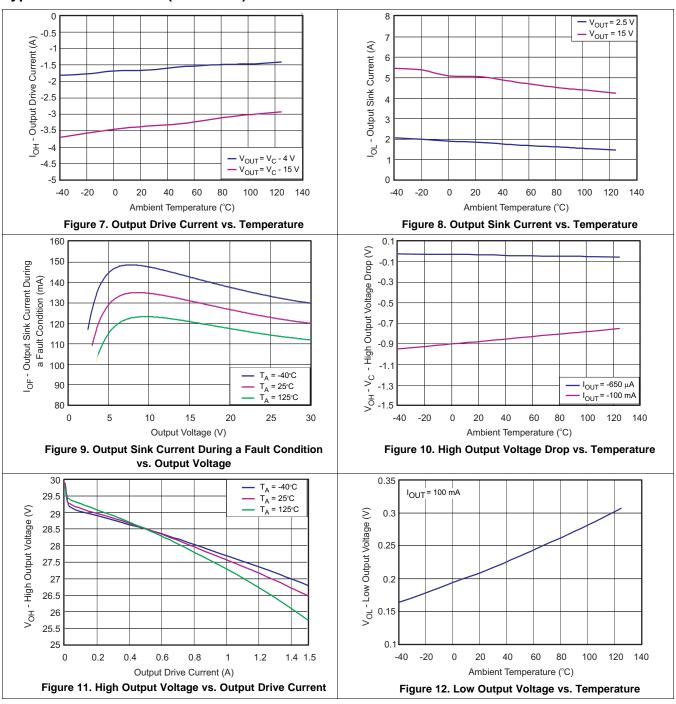

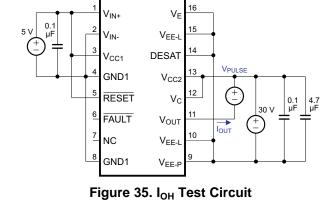

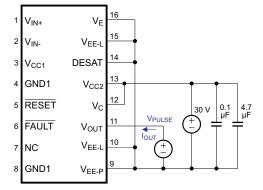

|                         | High lovel output ourrent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | $V_{OUT} = V_{CC2} - 4 V^{(1)}$ , See Figure 7 and Figure 35                             | -1                   | -1.6                 |      | А    |  |

| I <sub>ОН</sub>         | High-level output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | V <sub>OUT</sub> = V <sub>CC2</sub> – 15 V <sup>(2)</sup> , See Figure 7 and Figure 35   | -2.5                 |                      |      | Α    |  |

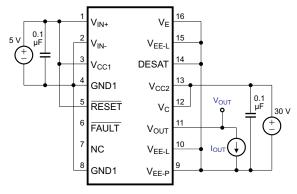

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | V <sub>OUT</sub> = V <sub>EE-P</sub> + 2.5 V <sup>(1)</sup> , See Figure 8 and Figure 36 | 1                    | 1.8                  |      |      |  |

| l <sub>OL</sub>         | Low-level output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | V <sub>OUT</sub> = V <sub>EE-P</sub> + 15 V <sup>(2)</sup> , See Figure 8 and Figure 36  | 2.5                  |                      |      | А    |  |

| I <sub>OF</sub>         | Output-low fault current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | V <sub>OUT</sub> – V <sub>EE-P</sub> = 14 V, See Figure 9 and Figure 37                  | 90                   | 140                  | 230  | mA   |  |

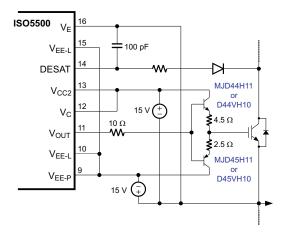

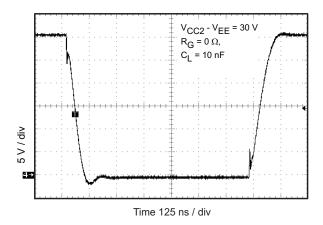

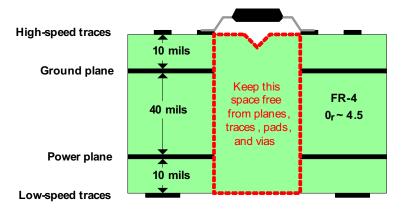

| .,                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | I <sub>OUT</sub> = -100 mA, See Figure 10, Figure 11 and Figure 38                       | V <sub>C</sub> -1.5  | V <sub>C</sub> -0.8  |      | .,   |  |