# () IDT.

### PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

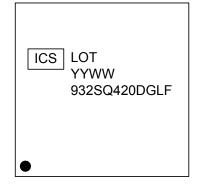

### 932SQ420D

### **General Description**

The 932SQ420D is a main clock synthesizer for Romley-generation Intel based server platforms. The 932SQ420D is driven with a 25 MHz crystal for maximum performance. It generates CPU outputs of 100 or 133.33 MHz.

### **Recommended Application**

CK420BQ

### **Output Features**

- 4 HCSL CPU outputs

- 4 HCSL Non-Spread SAS/SRC outputs

- 3 HCSL SRC outputs

- 1 HCSL DOT96 output

- 1 3.3V 48M output

- 5 3.3V PCI outputs

- 1-3.3V REF output

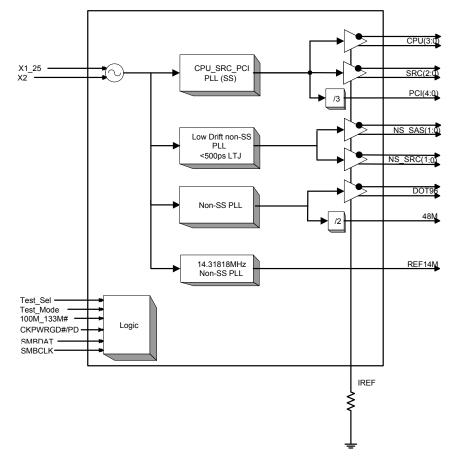

### **Block Diagram**

### Features/Benefits

- 0.5% down spread capable on CPU/SRC/PCI outputs/Lower EMI

- 64-pin TSSOP and MLF packages/Space Savings

### **Key Specifications**

- Cycle to cycle jitter: CPU/SRC/NS\_SRC/NS\_SAS < 50ps.

- Phase jitter: PCIe Gen2 < 3ps rms, Gen3 < 1ps rms</li>

- Phase jitter: QPI 9.6GB/s < 0.2ps rms</li>

- Phase jitter: NS-SAS < 0.4ps rms using raw phase data

- Phase jitter: NS-SAS < 1.3ps rms using Clk Jit Tool 1.6.3

1

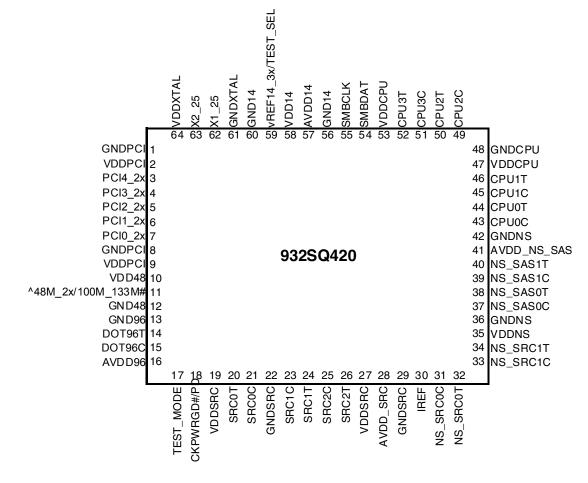

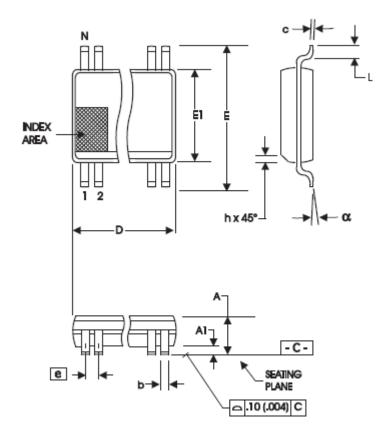

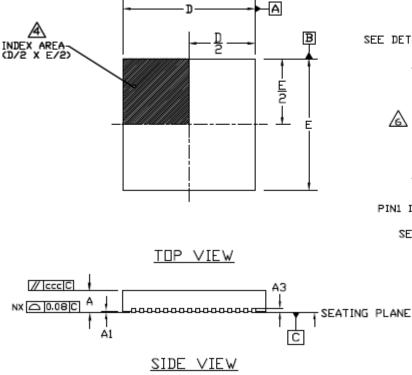

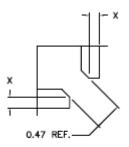

### **Pin Configuration - 64TSSOP**

| SMBCLK<br>GND14<br>AVD14<br>VDD14<br><sup>v</sup> REF14_3x/TEST_SEL<br>GND14<br>GNDXTAL<br>X1_25<br>X2_25<br>VDDXTAL<br>GNDPCI<br>VDDPCI<br>PCI4_2x<br>PCI3_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x<br>PCI2_2x | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>9<br>20<br>21<br>22<br>32<br>4<br>25<br>6<br>27<br>28<br>9<br>30 | 932SQ420 | <ul> <li>64 SMBDAT</li> <li>63 VDDCPU</li> <li>62 CPU3T</li> <li>61 CPU3C</li> <li>60 CPU2T</li> <li>59 CPU2C</li> <li>58 GNDCPU</li> <li>57 VDDCPU</li> <li>56 CPU1T</li> <li>55 CPU1C</li> <li>54 CPU0T</li> <li>53 CPU0C</li> <li>52 GNDNS</li> <li>51 AVDD_NS_SAS</li> <li>50 NS_SAS1T</li> <li>49 NS_SAS1C</li> <li>48 NS_SAS0T</li> <li>47 NS_SAS0C</li> <li>46 GNDNS</li> <li>44 NS_SRC1T</li> <li>43 NS_SRC1C</li> <li>42 NS_SRC1C</li> <li>42 NS_SRC0T</li> <li>41 NS_SRC0C</li> <li>40 IREF</li> <li>39 GNDSRC</li> <li>38 AVDD_SRC</li> <li>36 SRC2T</li> <li>35 SRC2C</li> <li>34 SRC1T</li> </ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRC0T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30                                                                                                                                                             |          | 35 SRC2C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GNDSRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32                                                                                                                                                             | 64-TSSOP | 33 SRC1C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Note: Pins with ^ prefix have internal 120K pullup Pins with v prefix have internal 120K pulldown

#### **Spread Spectrum Control**

| SS_Enable | CPU, SRC & |

|-----------|------------|

| (B1b0)    | PCI        |

| 0         | OFF        |

| 1         | ON         |

# 932SQ420 Power Down Functionality

| CKPWRGD#/PD | Differential Single-ended |         | Single ended     |

|-------------|---------------------------|---------|------------------|

|             | Outputs Outputs           |         | Outputs w/Latch  |

| 1           | HI-Z <sup>1</sup>         | Low     | Low <sup>2</sup> |

| 0           |                           | Running |                  |

Hi-Z on the differential outputs will result in both True and Complement being low due to the termination network

These outputs are Hi-Z after VDD is applied and before the first assertion of CKPWRGD#.

#### **Power Group Pin Numbers**

| ML    | F   | TSSOP  |        | Description                                |  |  |

|-------|-----|--------|--------|--------------------------------------------|--|--|

| VDD   | GND | VDD    | GND    | Description                                |  |  |

| 57    | 56  | 3      | 2      | 14MHz PLL Analog                           |  |  |

| 58    | 60  | 4      | 6      | REF14M Output and Logic                    |  |  |

| 64    | 61  | 10     | 7      | 25MHz XTAL                                 |  |  |

| 2,9   | 1,8 | 12, 19 | 11, 18 | PCI Outputs and Logic                      |  |  |

| 10    | 12  | 20     | 22     | 48MHz Output and Logic                     |  |  |

| 16    | 13  | 26     | 23     | 96MHz PLL Analog, Output and Logic         |  |  |

| 19,27 | 22  | 29, 37 | 32     | SRC Outputs and Logic                      |  |  |

| 28    | 29  | 38     | 39     | SRC PLL Analog                             |  |  |

| 35    | 36  | 45     | 46     | Non-Spreading Differential Outputs & Logic |  |  |

| 41    | 42  | 51     | 52     | NS-SAS/SRC PLL Analog                      |  |  |

| 47,53 | 48  | 57,63  | 58     | CPU Outputs and Logic                      |  |  |

2

### **Pin Descriptions - 64 TSSOP**

| 1     SMBCLK     IN     Clock pin of SMBUS circuitry, EV loterant       2     GND14     PVM Grownop intor 14MHz ouppit and logic       3     AVDD14     PVM Rover pin for 14MHz ouppit and logic       4     VDD14     PVM Rover pin for 14MHz ouppit and logic       6     GND14     PVM Grownop intor 14MHz ouppit and logic       7     GNDXTAL     PVM Grownop intor 14MHz ouppit and logic.       7     GNDXTAL     PVM Grownop intor 14MHz ouppit and logic.       7     GNDXTAL     PVM Grownop intor 15MHz ouppit and logic.       8     X1_25     Out Crystal loput, Normally 25.00MHz.       9     X2_25     Out Crystal loput, Normally 25.00MHz.       10     VDDXTAL     PVM Grownop intor the crystal socillator.       11     GNDPCI     PVM Grownop intor the crystal socillator.       12     VDDPCI     PVM Bit 32% Downer for the PCI ouppus and logic.       13     PCI4_2X     OUT 33.47 PCI clock output       15     PCI2_2X     OUT 33.47 PCI clock output       16     PCI1_2X     OUT 33.47 PCI clock output       17     PCI0_2X     OUT 33.47 PCI clock output       18     GNDPCI     PVM Grownop in for PCI outputs and logic.       19     VDDPCI     PVM Risk and social so                                                                                                                                                                                                                                                                                                                                                               |       |                                      |        |                                                                                                                |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|--------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2       GND14       PVM       Found pin for 14MH2 output and logic.         3       AVXD014       PVM       Avxper pin for 14MH2 output and logic.         5       VREF14_3x/TEST_SLL       VD       14.318 MH2 reference clock. 3X drive strength as default / TEST_SEL latched input to enable test mode.         6       GND14       PVM       Ground pin for 14MH2 output and logic.         7       GNDXTAL       PVM       Ground pin for 14MH2 output and logic.         8       X1_25       IN       Crystal output, Norminally 25.00MHz.         9       X2_25       OUT       Crystal output, Norminally 25.00MHz.         10       VDDXTAL       PVM       Ground pin for PC outputs and logic.         11       GNDPCI       PVM       Ground pin for PC outputs and logic.         12       VDDXTAL       PVM       S3.Y poer for the PC old outputs and logic.         13       GNDPCI       PVM       S3.Y poer for the PC old outputs and logic.         14       PCI2.2x       OUT       S3.Y PCI dock output         15       PCI2.2x       OUT       S3.Y PCI dock output         16       PCI1.2x       OUT       S3.Y owner for the PCI outputs and logic.         17       PCI0.2x       OUT       S3.Y AdMHz outputs and logic.         18 <th>PIN #</th> <th></th> <th>TYPE</th> <th></th>                                                                                                                                                                                                                                                                                                                                                                               | PIN # |                                      | TYPE   |                                                                                                                |  |  |  |  |

| 3         AVDD14         PWH Rever prior 14MHz PLL           4         VDD14         PWH Rever prior 14MHz and logic         PVE           5         vREF14_3x/TEST_SEL         IO         14.318 MHz reference clock. 3X drive strength as default / TEST_SEL listched input to enable test mode.<br>Refer to TSE Clarification Table. This pin has a weak (-12080hm) internal pull down.           6         GNDTAL         PWH Giound pin for 75410 Sociator.         PVE           7         GNDSTAL         PWH Giound pin for 75410 Sociator.         PVE           8         X1_25         IN         Crystal input. Nominaly 25.00MHz.         PVE           10         VDDCPCI         PWH Giound pin for PCI outputs and logic.         PVE         PVE           11         GNDPCI         PWH Giound pin for PCI outputs and logic.         PVE         PVE         PVE           12         VDDPCI         PWH Giound pin for PCI outputs and logic.         PVE         P                                                                                                                                                                                                                                                                                                                                                          |       |                                      |        |                                                                                                                |  |  |  |  |

| 4         VDD14         PWR         Power pin for 14MHz output and logic           5         VREF14_SVTEST_SEL         IV0         Refer to Test Clarification Table. This pin has a weak (-120Kohm) internal pull down.           6         KND14         PWR         Gound pin for 14MHz output and logic.           7         GNDXTAL         PWR         Gound pin for 14MHz output and logic.           8         X1.25         IN1         Crystal output, Normially 25:00MHz.           9         X2.25         OUT         Crystal output, Normially 25:00MHz.           10         VDDDPC1         PWR 33:V power for the PC1 outputs and logic           11         GNDPC1         PWR 33:V power for the PC1 outputs and logic           12         VDDPC1         PWR 33:V power for the PC1 outputs and logic           13         PC14; 2x         OUT         33:V PC1 dock output           14         PC13; 2x         OUT 33:V PC1 dock output         Test and VDPC1           17         PC14; 2x         OUT 33:V PC1 dock output         Test and VDPC1           18         ONDPC1         PWR 3:V power for the PC1 outputs and logic.         Test and VDPC1           14         PC13; 2x         OUT 33:V PC1 dock output and logic.         Test and VDPC1           14         PC14; 2x         OUT 33:V PC1                                                                                                                                                                                                                                                                                                                                                        |       |                                      |        |                                                                                                                |  |  |  |  |

| s         VREF14_3vTEST_SEL         IO         14318 MH z reference clock. 3X drive strength as default / TEST_SEL Lander input to enable test mode.<br>Refer to T28 Clarification Table. This pin has a week (-120Kohm) internal pull down.           6         GND14         PVM B Gound pin for 14MH z output and logic.         1           7         GND3TAL         PVM B Gound pin for 14MH z output and logic.         1           8         X1_25         IN         Crystal input, Nominally 25 00MHz.         2           10         VDDXTAL         PVM B Gound pin for 761 outputs and logic.         1         1           11         GNDFCI         PVM B Gound pin for PCI outputs and logic.         1         1         1           12         VDDPCI         PVM B Gound pin for PCI outputs and logic.         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                     | -     |                                      |        |                                                                                                                |  |  |  |  |

| Mich M., 39/165/1942         Work Rev and prior 14MHz output and logic.           GND TAL         PVME Ground pin for 14MHz output and logic.           K1, 25         IN         Crystal input, Normially 25.00MHz.           VEX.25         OUT Crystal output, Normially 25.00MHz.           VEX.25         OUT S3.97 Cl dock output           VEX.26         OUT S3.97 Cl dock output                                                                                                                                                                                                                                                                                                                                                                                                            | 4     | VDD14                                | PWR    |                                                                                                                |  |  |  |  |

| Bit Provide         Provide Test Control Table. The print has a week (-120kcom) internal pull down.           CRNDTAL         PWR         Ground prin for 14M/2 output and togic.           CRNDTAL         PWR         Ground prin for 14M/2 output and togic.           V1.25         IN         Crystal aduptu, Nominally 25 00M/12.           V0.261         PWR         SX prove for the crystal accilitator.           V0.2701         PWR         SX prove for the crystal accilitator.           V0.2702         PWR         SX prove for the crystal accilitator.           V0.2701         PWR         SX prove for the crystal accilitator.           V0.2702         PWR         SX prove for the crystal accilitator.           V0.2703         PVR         SX prove for the crystal accilitator.           V0.2704         PWR         SX prove for the crystal accilitator.           V0.2705         PWR         SX prove for the crystal accilitator.           V0.2804         OUT         SX Prove for the crystal accilitator.           V0.2804         OUT         SX Prove for the crystal accilitator.           V0.2804         PWR         SX Prove for the crystal accilitator.           V1.2804         PWR         SX Prove for the crystal accilitator.           V1.2804         PWR         SX Prove for the crystal accilita                                                                                                                                                                                                                                                                                                                                   | 5     | VBEE14 3X/TEST SEL                   | 1/0    |                                                                                                                |  |  |  |  |

| 7     GRDXTAL     PWR Ground pin for Crystal Deplator.       8     X1_25     IN     Crystal Input. Norminally 25:00MHz.       9     X2_25     OUT     Crystal output. Norminally 25:00MHz.       10     VDDXTAL     PWR I3:37 power for the crystal oscillator.       11     GNDPCI     PWR I3:37 power for the crystal oscillator.       12     VDDPCI     PWR I3:37 power for the Crystal outputs and logic.       13     PCI4.2x     OUT I3:37 PCI clock output       14     PCI3.2x     OUT I3:37 PCI clock output       15     PCI2.2x     OUT I3:37 PCI clock output       16     PCI2.2x     OUT I3:37 PCI clock output       17     PCI0.2x     OUT I3:37 PCI clock output       18     GNDPCI     PWR I3:37 power for the PCI outputs and logic.       20     VDDPCI     PWR I3:37 power for the PCI outputs and logic.       21     ^4BM_2x/100M_133Mi     IO     there PCI clock output I3:37 KBMHz output and logic.       22     GND48     PWR I3:37 power for the PCI outputs and logic.     there PCI clock output I3:37 KBMHz output I1:17 KBMZ output I1:17 KBMZ output I1:17                                                                                                                                                                                                                          |       |                                      |        |                                                                                                                |  |  |  |  |

| 8       X1 25       INI       Crystal input. Norminally 25 00MHz.         10       VDDXTAL       PVR [Gound prior PC) couputs and logic.         11       GNDPCI       PVR [Gound prior PC) couputs and logic.         12       VDDPCI       PVR [Gound prior PC) couputs and logic.         13       PCIA 2×       OUT [33V PC] dock ouput         14       PCIA 2×       OUT [33V PC] dock ouput         15       PCIA 2×       OUT [33V PC] dock ouput         16       PCIA 2×       OUT [33V PC] dock ouput         17       PCIA 2×       OUT [33V PC] dock ouput         18       GNDPCI       PVR [33V power for the PC] outputs and logic.         19       VDDPCI       PVR [33V power for the 48MHz output 30 logic.         19       VDDA8       PVR [33V power for the 48MHz output 30 logic.         20       VDD48       PVR [Gound prior fO? Loutput and logic.         21       ^48M_2x/100M_133M#       I/O       Intreshotds. This pin has a weak (-120Kom) internal pull up.         1       1       100 threshould and logic.       Complementary tocks of differential 96MHz output. These are current mode outputs. These are current mode outputs and logic.         23       GND496       PVR [Gound prior D? DE output and logic.       The cock of differential 96MHz output. These are current mode outputs and extemal 3                                                                                                                                                                                                                                                                                                                                            | -     |                                      |        |                                                                                                                |  |  |  |  |

| 9         X2_25         OUT         Crystal output, Nominally 25.00MHz.           10         VDDXTAL         PVM B 33/ power for the Cytal socialitor.           11         GNDPCI         PVM B 33/ power for the Cytal outputs and logic.           13         PCI4_2x         OUT 33/ PCI dock output           14         PCI3_2x         OUT 33/ PCI dock output           15         PCI2_2x         OUT 33/ PCI dock output           16         PCI1_2x         OUT 33/ PCI dock output           17         PCI0_2x         OUT 33/ PCI dock output           18         GNDPCI         PVM B Ground pin for PCI outputs and logic.           20         VDD48         PVM B 33/ power for the AMMHz output and logic.           21         ^48M_2x/100M_133M#         IO Treshoulds. This pin has a weak (-120KM) internal pull up.           21         ^48M_2x/100M_133M#         IO Treshoulds. This pin has a weak (-120KM) internal pull up.           22         GND48         PVM B Ground pin for 4MHz output. These are current mode outputs. These are current mode outputs.           24         DOT961         OUT         Treshoulds of differential 9MHz output. These are current mode outputs and exem al 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           26         AVDD96         PVM B 33/ power for the 84/9MHz output. These are current mode o                                                                                                                                                                                                                                                                      | 7     | GNDXTAL                              | PWR    | Ground pin for Crystal Oscillator.                                                                             |  |  |  |  |

| 10       VDDXTAL       PVM B Ground pin for PC locuputs and logic.         11       GNDPCI       PVM B Ground pin for PC locuputs and logic.         12       VDDPCI       PVM B Ground pin for PC locuputs and logic.         14       PCI3_2x       OUT 3.3V PCI dock output         15       PCI2_2x       OUT 3.3V PCI dock output         16       PCI3_2x       OUT 3.3V PCI dock output         17       PCI0_2x       OUT 3.3V PCI dock output         18       GNDPCI       PVM B Ground pin for PCI outputs and logic.         19       VDDPCI       PVM B 3.3V power for the 4MMz output and logic.         19       VDDPCI       PVM B 3.3V power for the 4MMz output and logic.         10       trestends. This pin has a wask (-120km) internal pull up.         12       VAMA_2X/100M_133M#       Iot trestends. This pin has a wask (-120km) internal pull up.         12       GND48       PVM B Ground pin for 2MM1z output and logic.         24       DOT96T       OUT       Tue clock of differential 9MMz output and logic.         25       DOT96C       OUT       Tue clock of differential 9MMz output and logic.         26       AVDD86       PVM Ground pin for 2MMMz December PL2 and REFN divider mode while in test mode. Refer to Task fork and the 9MMz output and logic.         27       TEST_MODE                                                                                                                                                                                                                                                                                                                                                           | 8     |                                      | IN     | Crystal input, Nominally 25.00MHz.                                                                             |  |  |  |  |

| 11       GNDPCI       PVMB 33V power for the PCI outputs and logic.         13       PCI4_2X       OUT 33V PCI dock output         14       PCI3_2X       OUT 33V PCI dock output         15       PCI4_2X       OUT 33V PCI dock output         16       PCI1_2X       OUT 33V PCI dock output         17       PCI0_2X       OUT 33V PCI dock output         18       GNDPCI       PVMB 33V power for the PCI outputs and logic.         19       VDDPCI       PVMB 33V power for the PCI outputs and logic.         20       VDD44       PVM 33V power for the PCI outputs and logic.         21       ~48M_2x/100M_133M#       I/O       thresholds. This pin has a weak (~120Kom) internal pull up.         22       GND48       PVMF Ground pin for PCI9 output and logic.       thresholds. This pin has a weak (~120Kom) internal pull up.         23       GND96       PVMF Ground pin for AdMHz output and logic.       thresholds. The Sec values for the administry output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49 ohm shunt resistors are required for termination.         24       D0T96T       OUT       and external 32 GMNSe developed for the 369GMHz output. These are current mode outputs and external 33 ohm series resistors and 49 ohm shunt resistors are required for termination.         26       DDT96C       OUT       fast faref                                                                                                                                                                                                                                                             | 9     | X2_25                                | OUT    | Crystal output, Nominally 25.00MHz.                                                                            |  |  |  |  |

| 12       VDDPCI       PVH 3: 3V power for the PCI outputs and logic         13       PCI4 2x       OUT 3: VPCI dock output         14       PCI3 2x       OUT 3: VPCI dock output         15       PCI2 2x       OUT 3: VPCI dock output         16       PCI1 2x       OUT 3: VPCI dock output         17       PCIO 2x       OUT 3: VPCI dock output         18       GNDPCI       PVH 3: SV power for the PCI outputs and logic.         19       VDDPCI       PVH 3: SV power for the AMHz output and logic.         20       VDD48       PVH 3: SV power for the PCI outputs and logic.         21       ^48M_2x/100M_133M#       I/O       thresholds. This pin has a weak (~120Korn) internal pull up.         22       GND48       PVH Ground pin for DO196 output and logic.       SV 48MHz output 3: SV dollard and logic.         23       GND48       PVH Ground pin for DO196 output and logic.       The colock of differential 96MHz output. These are current mode outputs. These are current mode outputs and external 3: 3 ohm series resistors and 49. ohm shunt resistors are required for termination.         24       DOT96C       OUT       The SCH ook of differential 96MHz output. These are current mode outputs and external 3: ohm series resistors and 49. ohm shunt resistors are required for termination.         25       DOT96C       OUT       TesCLandration Table.                                                                                                                                                                                                                                                                                        | 10    | VDDXTAL                              | PWR    | 3.3V power for the crystal oscillator.                                                                         |  |  |  |  |

| 13       PCId 2x       OUT       33V PCI dock output         14       PCIB 2x       OUT       33V PCI dock output         15       PCIE 2x       OUT       33V PCI dock output         16       PCII 2x       OUT       33V PCI dock output         17       PCIO 2x       OUT       33V PCI dock output         18       GNDPCI       PWR 32V PCI dock output         19       VDDPCI       PWR 33V power for the PCI outputs and logic.         20       VDD48       PWR 33V power for the PCI outputs and logic.         21       ^48M 2x/100M_133M#       IO       thresholds. This pin has a weak (-120Kom) internal pull up.         1       -1       10MHz, 0 = 133MHz operating frequency       1         22       GND48       PWR Ground p for CDT8 output and logic.         23       GND96       PWR Ground p for CDT8 output and logic.         24       D0T96T       OUT       advermal 33 Ohm series resistors and 49.0 ohm shunt resistors are required for termination.         25       D0T96C       OUT       advermal 33 Ohm series resistors and 49.0 ohm shunt resistors are required for termination.         26       AVDD66       PWR 33V power for the 48%6MLz PLL and the 96MHz output and logic       1         27       TEST_MODE       IN       TEST_MODE                                                                                                                                                                                                                                                                                                                                                                                                           | 11    | GNDPCI                               | PWR    | Ground pin for PCI outputs and logic.                                                                          |  |  |  |  |

| 14       PCI3_2x       OUT       33V PCI dock output         15       PCI2_2x       OUT       33V PCI dock output         16       PCI1_2x       OUT       33V PCI dock output         17       PCI0_2x       OUT       33V PCI dock output         18       GNDFCI       PWR       Borund ph for PCI outputs and logic         19       VDDP4       PWR       33V power for the PCI outputs and logic         20       VDD48       PWR 33V power for the PCI outputs and logic         21       V48M_2x/100M_133Mt       I/O       33V 48MHz output and logic         22       GND48       PWR Ground ph for 48MHz output and logic.         23       VDD44       PWR Ground ph for D0T96 output. These are current mode outputs.         24       D0T96T       OUT       Testick of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         25       D0T96C       OUT       Test_MODE       NT Test_MODE       IN         18       Test_MODE       IN       TEST_MODE       IN       SV power for the 4896MHz PL and the 96MHz output and logic         27       TEST_MODE       IN       SV pOWER for the A896MHz PL and the 96MHz output and logic       IN         28       VDD                                                                                                                                                                                                                                                                                                                                                                                                   | 12    | VDDPCI                               | PWR    | 3.3V power for the PCI outputs and logic                                                                       |  |  |  |  |

| 15       PCI2_2x       OUT       33V PCI dock output         16       PCII_2x       OUT       33V PCI dock output         17       PCI0_2x       OUT       33V PCI dock outputs and logic.         18       GNDPCI       PWR       33V PCI dock outputs and logic.         20       VDDFCI       PWR       33V power for the PCI outputs and logic.         21       ^48M_2v/100M_133M#       I/O       assW adM1z output and logic.         22       GND48       PWR       Ground pt for AMM1z output and logic.         23       GND48       PWR       Ground pt for AMM1z output and logic.         24       D0T96T       OUT       Tue clock of differential 6MHz output and logic.         25       D0T96C       OUT       Tue clock of differential 6MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       D0T96C       OUT       TesT_MODE       TEST_MODE       TEST_MODE is a real time input to select between H-iZ and REF/N divider mode while in test mode. Refer to test as resistors and 49.9 ohm shunt resistors are required for termination.         27       TEST_MODE       IN       TeST_MODE is a real time input to select between H-iZ and REF/N divider mode while in test mode. Refer to test calification Table.         28       CKPWRGD#/PD       IN                                                                                                                                                                                                                                                                                                          | 13    | PCI4_2x                              | OUT    | 3.3V PCI clock output                                                                                          |  |  |  |  |

| 15       PCI2_2x       OUT       33V PCI dock output         16       PCII_2x       OUT       33V PCI dock output         17       PCI0_2x       OUT       33V PCI dock outputs and logic.         18       GNDPCI       PWR       33V PCI dock outputs and logic.         20       VDDFCI       PWR       33V power for the PCI outputs and logic.         21       ^48M_2v/100M_133M#       I/O       assW adM1z output and logic.         22       GND48       PWR       Ground pt for AMM1z output and logic.         23       GND48       PWR       Ground pt for AMM1z output and logic.         24       D0T96T       OUT       Tue clock of differential 6MHz output and logic.         25       D0T96C       OUT       Tue clock of differential 6MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       D0T96C       OUT       TesT_MODE       TEST_MODE       TEST_MODE is a real time input to select between H-iZ and REF/N divider mode while in test mode. Refer to test as resistors and 49.9 ohm shunt resistors are required for termination.         27       TEST_MODE       IN       TeST_MODE is a real time input to select between H-iZ and REF/N divider mode while in test mode. Refer to test calification Table.         28       CKPWRGD#/PD       IN                                                                                                                                                                                                                                                                                                          | 14    | PCI3_2x                              | OUT    | 3.3V PCI clock output                                                                                          |  |  |  |  |

| 16       PCI1_2x       OUT       3.3V PCI dock output         17       PCI0_2x       OUT       3.3V PCI dock output         18       GNDPCI       PVM Ground pin for PCI outputs and logic.         19       VDDP4       PVM Ground pin for PCI outputs and logic.         20       VDD48       PVM 3.3V power for the 48MHz output and logic.         3.3V 48MHz output 3.3V loterant CPU forequency select latched input pin. See ViFS and VihFS values for         10       thresholds. This pin has a weak (-120Kom) internal pull up.         11       100       thresholds. This pin has a weak (-120Kom) internal pull up.         22       GND48       PVM Ground pin for 44MHz output and logic.         23       GND96       PVM Ground pin for 44MHz output and logic.         24       D0T96T       Output       Tese are current mode outputs. These are current mode outputs. These are current mode outputs. These are current mode outputs.         24       D0T96C       OUT       TeST_MODE       PVM 3.3V power for the 4896MHz PLL and the 96MHz output and logic.         27       TEST_MODE       IN       TEST_MODE is a real lime input to select between H-2 and HE-FN divider mode while in test mode. Refer to Test 02 affication Table.         28       VDDSRC       PVM 8.3V power for the SRC output. These are current mode outputs and external 33 ohm series resistors and 4.9.0 ohm shunt resistors are required to                                                                                                                                                                                                                                           | 15    |                                      |        |                                                                                                                |  |  |  |  |

| 17       PCI0_Zx       OUT       3.3V PCI deck output         18       GNDPCI       PWR Bround pit for PCI outputs and logic.         19       VDDPCI       PWR 3.3V power for the PCI outputs and logic.         20       VDD48       PWR 13.3V power for the PCI outputs and logic.         21       ^48ML_Zv100M_133M#       I/O       the PCI outputs and logic.         22       GND48       PWR Bround pit for PCI outputs and logic.       The sholds. This pin has a weak (-120Kom) internal pull up.         1       1       1       1       1       1         23       GND48       PWR Bround pit for PCI 96 output and logic.       The clock of differential 96MHz output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shurt resistors are required for termination.         25       DOT96C       OUT       Test_MODE       TEST_MODE       TEST_MODE is a real time input to select between H-Z and REF/N divider mode while in test mode. Refer to N res stopped.         26       KFWRGD#/PD       N asquertorine Ha96MHz PL, and the 96MHZ output and logic.         27       TEST_MODE       IN       TEST_MODE is an active low input used to sample latched inputs and allow the device to Power Up. PD is an active low input used to sample latched inputs and allow the device to Power Up. PD is an active low high input pin used to put the device into a low power state. The internal clocks and PL are stopped.<                                                                                                                                                                               | 16    |                                      | OUT    | 3.3V PCI clock output                                                                                          |  |  |  |  |

| 18       GNDPCI       PWR       Ground pin for PCI outputs and logic.         19       VDDP6I       PWR       3.3V power for the 48MHz output and logic         20       VDD48       PWR       3.3V power for the 48MHz output and logic         21       ^448M_2x/100M_133M#       I/V       3.3V 48MHz output 3.3V loterant CPU frequency select latched input pin. See VIFS and VihFS values for         22       GND48       PWR       Ground pin for 44MHz output 3.4V loterant CPU frequency select latched input pin. See VIFS and VihFS values for         23       GND46       PWR       Ground pin for 44MHz output and logic.         24       DOT961       OUT       True clock of differential 96MHz output and logic.         25       DOT96C       OUT       Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PVR       3.3V power for the 4896MHz PLL and the 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         27       TEST_MODE       IN       TEST_MODE is an adthe low input used to sample latched inputs and allow the device to Power Up. PD is an asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLL are clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and                                                                                                                          |       | _                                    |        |                                                                                                                |  |  |  |  |

| 19.         VDDPCI         PWR         3.3V power for the PGI outputs and logic           20         VDD48         PWR         3.3V power for the PAML output and logic.           21         v48M_2x/100M_133M         IO         thresholds. This pin has a weak (-120Kom) internal pull up.           21         v48M_2x/100M_133M         IO         thresholds. This pin has a weak (-120Kom) internal pull up.           22         GND48         PWR         Ground pin for VD196 output and logic.           23         GND96         PWR Ground pin for OD196 output and logic.           24         DOT96T         OUT         True clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors are required for termination.           25         DOT96C         OUT         True clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors are required for termination.           26         AVDD96         PWR 3.3V power for the 4996MHz PLL and the 96MHz output and logic.           27         TEST_MODE         IN         TEST_MODE is a real time input to select between H-Z and REF/N divider mode while in test mode. Refer to Test Clacification Table.           28         VDDSRC         PWR         3.3V power for the SRC outputs and logic.           30         SRC0T         OUT         True clock of differential SRC output. These are current mode outpu                                                                                                                                                                                                          |       |                                      |        |                                                                                                                |  |  |  |  |

| 20         VDD48         PWR 3.3V power for the 48MHz output and logic.           21         \48M_2x/100M_133M#         \VO         3.3V 48MHz output 3.3V tolerant CPU frequency select latched input pin. See VIFS and VIhFS values for thresholds. This pin has a weak (-120Kom) internal pull up.<br>1 = 100MHz, 0 = 133MHz operating frequency         2           22         GND48         PWR Ground pin for 48MHz output 1. These are current mode outputs. These are current mode outputs and external 30 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           23         DOT96T         OUT         The clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           24         DOT96C         OUT         Complementary clock of differential 96MHz output not select between Hi-2 and REF/N divider mode while in test mode. Refer to Test Clanfication Table.           26         AVDD96         PWR         3.3V power for the 8RC output to select between Hi-2 and REF/N divider mode while in test mode. Refer to Test Clanfication Table.           27         TEST_MODE         IN         TEST_MODE to SRC OUT         Tue clock of differential SRC output to select between Hi-2 and REF/N divider mode while in test mode. Refer to Test Clanfication Table.           29         VDDSRC         PWR         3.3V power for the SRC output and logic.           30         SRC0T         OUT         True clock of differential SRC output. T                                                                       |       |                                      |        |                                                                                                                |  |  |  |  |

| 21       48M_2x/100M_133M#       I/O       3.3V 48MHz output 3.3V tolerant CPU frequency select latched input pin. See VIIFS and VIhFS values for         21       48M_2x/100M_133M#       I/O       thresholds. This pin has a weak (~120Kom) internal pull up.         22       GND48       PVMR       Ground pin for 48MHz output and logic.         22       GND96       PVMR       Ground pin for 100T96 output and logic.         24       D0196T       OUT       Thre clock of differential 96MHz output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PVMR       Ground pin for the 4396MHz PL Land the 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         27       TEST_MODE       I/N       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Trest Carification Table.         28       CKPWRGD#/PD       I/N       CKPWRGD#/ED       I/N         30       SRC0T       OUT       The clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       Complementary clock of differential SRC output. These are current mode outputs. And external 33 ohm series r                                                                                                                                   |       |                                      |        |                                                                                                                |  |  |  |  |

| 21       ^48M_2x/100M_133M#       I/O       thresholds. This pin has a weak (-120Kom) internal pull up.<br>1 = 000H1z, 0 = 133M1z operating frequency         22       GND46       PVR       Ground pin for 48M1z output and logic.         23       GND96       PVR       Ground pin for 0000 bit of 48M1z output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         24       DOT96C       OUT       Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PVR       3.3V power for the 4896MHz PLL and the 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         27       TEST_MODE       IN       TEST_MODE is a real time input to select between Hi-z and REF/N divider mode while in test mode. Refer to Test Clanfication Table.         28       CKPWRGD#/PD       IN       Say power for the SRC outputs and logic         30       SRC0T       OUT       True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for terminati                                                                  | 20    | 100+0                                | I VVII |                                                                                                                |  |  |  |  |

| Intervention         Intervention           22         GND48         PWR         Ground pin for 48MHz output and logic.           23         GND96         PWR         Ground pin for 48MHz output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           24         DOT96T         OUT         True clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           25         DOT96C         OUT         Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           26         AVDD96         PWR         B.3V power for the 4896MHz PLL and the 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           27         TEST_MODE         N         TEST_MODE is a real time input to select between H-Z and REF/N divider mode while in test mode. Refer to track Christian Table.           28         CKPWRGD#/PD         N         asynchronous active high input pin used to sample latched inputs and allow the device to Power Up. PD is an asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLLi are stopped.           29         VDDSRC         PWR         3.3V power for the SRC output. These are current mode outp                                           | 21    | AARM 2x/100M 133M#                   | 1/0    |                                                                                                                |  |  |  |  |

| 22       GND48       PWR       Ground pin for 48MHz output and logic.         23       GND96       PWR       Ground pin for DD76 output and logic.         24       DOT96T       OUT       True clock of differential 98MHz output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         25       DOT96C       OUT       Complementary clock of differential 98MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic         27       TEST_MODE       IN       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.         28       CKPWRGD#/PD       IN       TEST_MODE is an active low input used to sample latched inputs and allow the device to Power Up. PD is an asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLL are stopped.         30       SRC0T       OUT       Tue clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       Tue clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required fo                                                            | 21    | <sup>4</sup> 40101_2X/100101_133101# | 1/0    |                                                                                                                |  |  |  |  |

| 23       GND96       PWR       Ground pin for DOT96 output and logic.         24       DOT96T       OUT       The clock of differential 96MHz output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         25       DOT96C       OUT       Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PWR       3.3V power for the 48/96MHz PLL and the 96MHz output and logic.         27       TEST_MODE       IN       Test Clafification Table.         28       CKPWRGD#/PD       IN       Test Clafification Table.         29       VDDSRC       PWR       3.3V power for the SRC outputs and logic.         29       VDDSRC       PWR       3.3V power for the SRC outputs and logic.         30       SRC0T       OUT       True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         33       SRC1C       OUT       Complementary clock of differential SRC outpu                                                                                                                                                                               | 00    |                                      |        |                                                                                                                |  |  |  |  |

| 24       DOT96T       Out       The clock of differential 96MHz output. These are current mode outputs. These are outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         25       DOT96C       Out       Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PWR 3.3V power for the 4396MeX PLL and the 96MHz put and logic.         27       TEST_MODE       IN       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.         28       CKPWRGD#/PD       IN       Asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLL are stopped.         29       VDDSRC       PWR 3.5V power for the SRC outputs and logic       The clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       Out       Tune clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         32       GNDSRC       PWR       Ground pin for SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         33       SRC1C       Out       Complementary clock                                                            |       |                                      |        |                                                                                                                |  |  |  |  |

| 24       DOT961       OUT       and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         25       DOT96C       OUT       Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PWR       3.3V power for the 48/96MHz PLL and the 96MHz output and logic         27       TEST_MODE       IN       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.         28       CKPWRGD#/PD       IN       asynchronous active high input pin used to sample latched inputs and allow the device to Power Up. PD is an asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLL are stopped.         29       VDDSRC       PVR       3.3V power for the SRC outputs and logic         30       SRC0T       OUT       True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         33       SRC1C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm                                                                     | 23    | GIND96                               | PWR    | Ground pin for DO 196 output and logic.                                                                        |  |  |  |  |

| 25       DOT96C       Out       Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PWR 3.3V power for the 49/96MHz PLL and the 96MHz output and logic         27       TEST_MODE       IN       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.         28       CKPWRGD#/PD       IN       CKPWRGD#/PD       EXPUNCE         30       SRC0T       OUT       CKPWRGD# is an active low input used to sample latched inputs and allow the device to Power Up. PD is an asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLL: are stopped.         30       SRC0T       OUT       Tue clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         32       GNDSRC       PWR       Ground pin for SRC outputs and logic.         33       SRC1C       OUT       Complementary clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors ar                                                                     | 24    | DOT96T                               | OUT    |                                                                                                                |  |  |  |  |

| 25       D0196C       001       series resistors and 49.9 ohm shunt resistors are required for termination.         26       AVDD96       PWR       3.3V power for the 48/96MHz PLL and the 96MHz output and logic         27       TEST_MODE       IN       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.         28       CKPWRGD#/PD       IN       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.         29       VDDSRC       PVR       3.3V power for the SRC outputs and logic         30       SRC0T       OUT       True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         32       GNDSRC       PVR       Ground pin for SRC outputs and logic.         33       SRC1C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         34       SRC1C       OUT       True clock of differential SRC output. These are current mode outputs and external 33 o                                                                                                                          |       |                                      |        |                                                                                                                |  |  |  |  |

| 26         AVDD96         PWR         3.3V power for the 49/96MHz PLL and the 96MHz output and logic           27         TEST_MODE         IN         TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Claffication Table.           28         CKPWRGD#/PD         IN         asynchronous active high input pin used to sample latched inputs and allow the device to Power Up. PD is an asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLL: are stopped.           29         VDDSRC         PWR         3.3V power for the SRC outputs and logic           30         SRC0T         OUT         True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           31         SRC0C         OUT         Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           32         GNDSRC         PWR         Ground pin for SRC outputs and logic.           33         SRC1C         OUT         Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.           34         SRC1T         OUT         True clock of differential SRC output. These are current mode outputs and external 33 ohm serie                                                             | 25    | DOT96C                               | OUT    |                                                                                                                |  |  |  |  |

| 27       TEST_MODE       IN       TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.         28       CKPWRGD#/PD       IN       CKPWRGD# is an active low input used to sample latched inputs and allow the device to Power Up. PD is an asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLLs are stopped.         29       VDDSRC       PWR       3.3V power for the SRC outputs and logic         30       SRC0T       OUT       True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         32       GNDSRC       PWR       Ground pin for SRC outputs and logic.         33       SRC1C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         34       SRC1T       OUT       True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         35       SRC1T       OUT       True clock of differentia                                                                     |       |                                      |        |                                                                                                                |  |  |  |  |

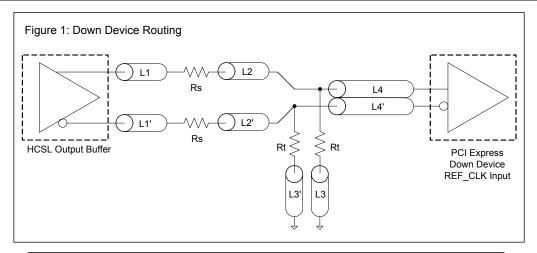

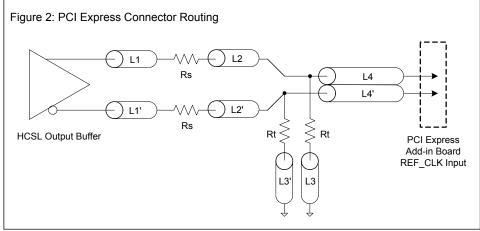

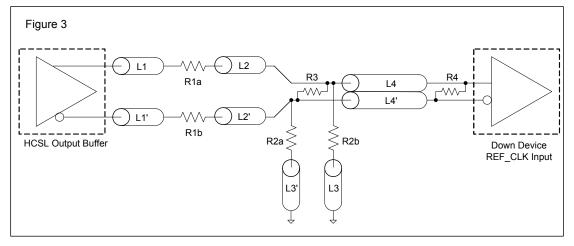

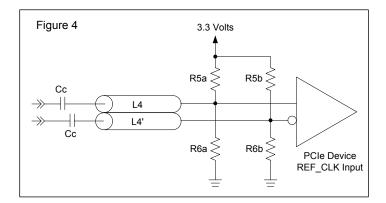

| 27       Test Clarification Table.         28       CKPWRGD#/PD       IN       Test Clarification Table.         28       CKPWRGD#/PD       IN       asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLLs are stopped.         29       VDDSRC       PWR       3.3V power for the SRC outputs and logic         30       SRC0T       OUT       True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         31       SRC0C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         32       GNDSRC       PWR       Ground pin for SRC outputs and logic.         33       SRC1C       OUT       Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         34       SRC1T       OUT       True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.         35       SRC2C       OUT       True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination. <tr< td=""><td>26</td><td>AVDD96</td><td>PWR</td><td></td></tr<>                                                              | 26    | AVDD96                               | PWR    |                                                                                                                |  |  |  |  |