**Data Sheet**

Document Number: WCT1101DS

Rev. 1.0, 02/2014

## Consumer Low Power Wireless Transmitter Controller

#### **Features**

- Low power (5 W) solution for Wireless Power Consortium (WPC) compliant transmitter design

- Conforms to the latest version low power WPC specifications

- Supports wide DC input voltage range starting from 4.2 V, typically 5 V, 12 V and 19 V

- Integrated digital demodulation on chip

- Supports all types of receiver modulation strategies (AC capacitor, AC resistor and DC resistor)

- Supports Foreign Object Detection (FOD)

- Super low standby power by Freescale Touch technology

- Supports any low power consumer power transmitter solutions using frequency and duty cycle control, or rail voltage control or phase shift control

- LED & buzzer for system status indication

- Over-voltage/current/temperature protection

- Supports CAN/IIC/SCI/SPI interfaces

- Software based solution to provide maximum design freedom and product differentiation

- FreeMASTER GUI tool to enable configuration, calibration and debugging

#### **Applications**

Low Power Wireless Power Transmitter

Any lower power consumer power transmitter solution

with frequency & duty cycle control, or rail voltage control, or phase-shift control (WPC A/B types or customer properties)

#### **Overview Description**

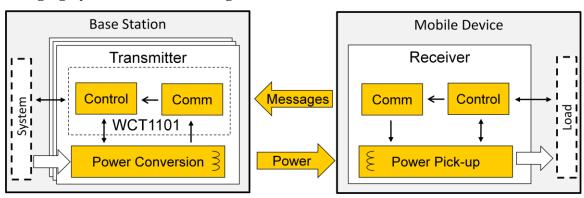

The WCT1101 is a wireless power transmitter controller that integrates all required functions for WPC "Qi" compliant wireless power transmitter design. It's an intelligent device to work with Freescale touch sensing technology or use periodically analog PING (configurable by user) to detect a mobile device for charging while gaining super low standby power. Once the mobile device is detected, the WCT1101 controls the power transfer by adjusting the operation frequency and duty cycle, or rail voltage, or phase shift of power stage according to message packets sent by mobile device.

To maximize the design freedom and product differentiation, WCT1101 supports any low power consumer power transmitter design (WPC A/B types or customization) using frequency and duty cycle control, or rail voltage control or phase shift control by software based solution. Besides, easy-to-use FreeMASTER GUI tool with configuration, calibration and debugging functions provides user-friendly design experience and speed time-to-market.

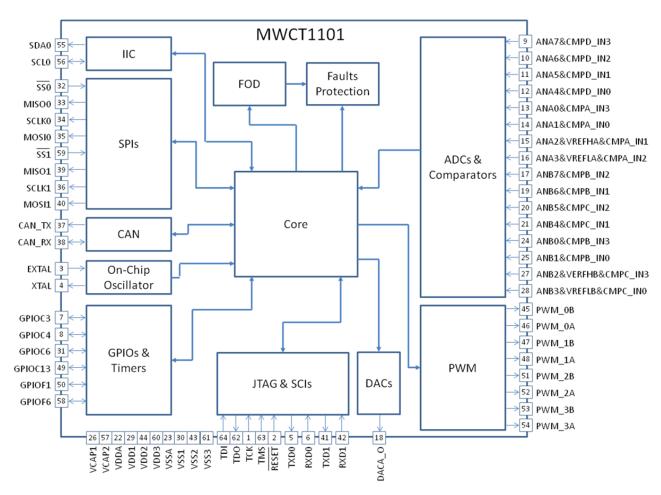

The WCT1101 includes digital demodulation module to reduce external components, over-voltage/current/ temperature protection, FOD method to protect from overheating by misplaced metallic foreign objects and general CAN/IIC/SCI/SPI interfaces for external communication purpose. It also handles any abnormal condition and operational status, and provides comprehensive indicator outputs for robust system design.

#### **Wireless Charging System Functional Diagram**

© Freescale Semiconductor, Inc., 2014. All rights reserved.

### **Contents**

| 1   | Absolute Maximum Ratings            | 4  |

|-----|-------------------------------------|----|

| 1.1 | Electrical Operating Ratings        | 4  |

| 1.2 | Thermal Handling Ratings            | 5  |

| 1.3 | ESD Handling Ratings                | 5  |

| 1.4 | Moisture Handling Ratings           | 5  |

| 2   | Electrical Characteristics          | 5  |

| 2.1 | General Characteristics             | 5  |

| 2.2 | Device Characteristics              | 8  |

| 2.3 | Thermal Operating Characteristics   | 17 |

| 3   | Typical Performance Characteristics | 18 |

| 3.1 | System Efficiency                   | 18 |

| 3.2 | Standby Power                       | 18 |

| 3.3 | Digital Demodulation                | 18 |

| 3.4 | Foreign Object Detection            | 18 |

| 3.5 | Dynamic Input Power Limit           | 19 |

| 4   | Device Information                  | 19 |

| 4.1 | Functional Block Diagram            | 19 |

| 4.2 | Product Features Overview           | 20 |

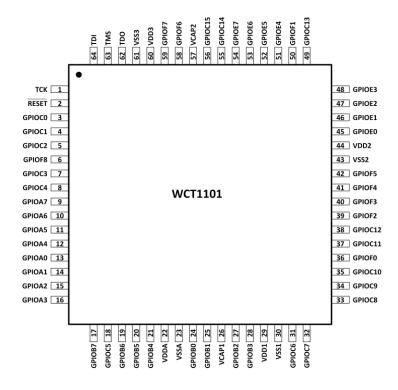

| 4.3 | Pinout Diagram                      | 21 |

| 4.4 | Pin Function Description            | 22 |

| 4.5 | Ordering Information                 | 31 |

|-----|--------------------------------------|----|

| 4.6 | Package Outline Drawing              | 31 |

| 5   | Software Library                     | 31 |

| 5.1 | Memory Map                           | 32 |

| 5.2 | Software Library and API Description | 32 |

| 6   | Design Considerations                | 32 |

| 6.1 | Electrical Design Considerations     | 32 |

| 6.2 | PCB Layout Considerations            | 33 |

| 6.3 | Thermal Design Considerations        | 34 |

| 7   | References and Links                 | 34 |

| 7.1 | References                           | 34 |

| 7.2 | Useful Links                         | 34 |

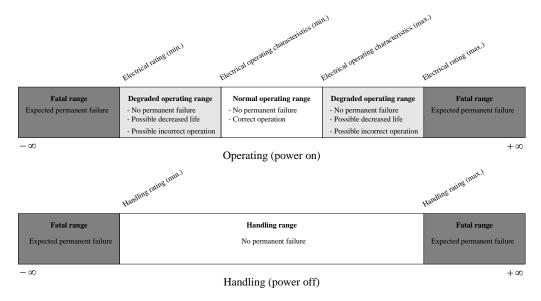

# 1 Absolute Maximum Ratings

## 1.1 Electrical Operating Ratings

Table 1. Absolute Maximum Electrical Ratings ( $V_{SS} = 0 V$ ,  $V_{SSA} = 0 V$ )

| Characteristic                                                               | Symbol                   | Notes <sup>1</sup> | Min.        | Max.  | Unit |

|------------------------------------------------------------------------------|--------------------------|--------------------|-------------|-------|------|

| Supply Voltage Range                                                         | V <sub>DD</sub>          |                    | -0.3        | 4.0   | ٧    |

| Analog Supply Voltage Range                                                  | $V_{DDA}$                |                    | -0.3        | 4.0   | V    |

| ADC High Voltage Reference                                                   | V <sub>REFHx</sub>       |                    | -0.3        | 4.0   | ٧    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>                       | $\Delta V_{DD}$          |                    | -0.3        | 0.3   | V    |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub>                       | ΔV <sub>ss</sub>         |                    | -0.3        | 0.3   | V    |

| Digital Input Voltage Range                                                  | V <sub>IN</sub>          | Pin Group 1        | -0.3        | 5.5   | V    |

| RESET Input Voltage Range                                                    | V <sub>IN_RESET</sub>    | Pin Group 2        | -0.3        | 4.0   | V    |

| Oscillator Input Voltage Range                                               | Vosc                     | Pin Group 4        | -0.4        | 4.0   | V    |

| Analog Input Voltage Range                                                   | V <sub>INA</sub>         | Pin Group 3        | -0.3        | 4.0   | V    |

| Input clamp current, per pin $(V_{IN} < V_{SS} - 0.3 \text{ V})^{2,3}$       | V <sub>IC</sub>          |                    | _           | -5.0  | mA   |

| Output clamp current, per pin <sup>4</sup>                                   | V <sub>oc</sub>          |                    | _           | ±20.0 | mA   |

| Contiguous pin DC injection current—regional limit sum of 16 contiguous pins | I <sub>Icont</sub>       |                    | -25         | 25    | mA   |

| Output Voltage Range (normal push-pull mode)                                 | V <sub>OUT</sub>         | Pin Group 1,2      | -0.3        | 4.0   | V    |

| Output Voltage Range (open drain mode)                                       | V <sub>OUTOD</sub>       | Pin Group 1        | -0.3        | 5.5   | V    |

| RESET Output Voltage Range                                                   | V <sub>OUTOD_RESET</sub> | Pin Group 2        | -0.3        | 4.0   | V    |

| DAC Output Voltage Range                                                     | V <sub>OUT_DAC</sub>     | Pin Group 5        | -0.3        | 4.0   | V    |

| Ambient Temperature                                                          | T <sub>A</sub>           |                    | -40         | 85    | °C   |

| Storage Temperature Range                                                    | T <sub>STG</sub>         |                    | <b>–</b> 55 | 150   | °C   |

#### Default Mode:

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET

- Pin Group 3: ADC and Comparator Analog Inputs

- Pin Group 4: XTAL, EXTAL

- Pin Group 5: DAC analog output

- 2. Continuous clamp current.

- 3. All 5 volt tolerant digital I/O pins are internally clamped to  $V_{SS}$  through an ESD protection diode. There is no diode connection to  $V_{DD}$ . If VIN greater than VDIO\_MIN (=  $V_{SS}$  –0.3 V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed, then a current limiting resistor is required.

- 4. I/O is configured as push-pull mode.

## 1.2 Thermal Handling Ratings

**Table 2. Thermal Handling Ratings**

| Symbol           | Description                   | Min.        | Max. | Unit | Notes |

|------------------|-------------------------------|-------------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | <b>-</b> 55 | 150  | °C   | 1     |

| $T_{SDR}$        | Solder temperature, lead-free | -           | 260  | °C   | 2     |

<sup>1.</sup> Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

## 1.3 ESD Handling Ratings

**Table 3. ESD Handling Ratings**

| Characteristic <sup>1</sup>                      | Min.  | Max.  | Unit |

|--------------------------------------------------|-------|-------|------|

| ESD for Human Body Model (HBM)                   | -2000 | +2000 | V    |

| ESD for Machine Model (MM)                       | -200  | +200  | V    |

| ESD for Charge Device Model (CDM)                | -500  | +500  | V    |

| Latch-up current at TA= 85°C (I <sub>LAT</sub> ) | -100  | +100  | mA   |

Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

### 1.4 Moisture Handling Ratings

**Table 4. Moisture Handling Ratings**

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | -    | 3    | -    | 1     |

Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 2 Electrical Characteristics

#### 2.1 General Characteristics

**Table 5. General Electrical Characteristics**

| Recommended Operating Conditions (V <sub>REFLx</sub> = 0 V, V <sub>SSA</sub> = 0 V, V <sub>SS</sub> = 0 V) |                      |       |      |      |      |      |                    |  |

|------------------------------------------------------------------------------------------------------------|----------------------|-------|------|------|------|------|--------------------|--|

| Characteristic                                                                                             | Symbol               | Notes | Min. | Тур. | Max. | Unit | Test<br>Conditions |  |

| Supply Voltage <sup>2</sup>                                                                                | $V_{DD}$ , $V_{DDA}$ |       | 2.7  | 3.3  | 3.6  | V    | -                  |  |

Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

| ADC (Cyclic) Reference<br>Voltage High                                                                                                       | V <sub>REFHA</sub>     |                                        | 3.0                   |   | $V_{DDA}$             | V  | -                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------|-----------------------|---|-----------------------|----|------------------------------------------------------------|

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>                                                                                       | $\Delta V_{DD}$        |                                        | -0.1                  | 0 | 0.1                   | V  | -                                                          |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub>                                                                                       | $\Delta V_{ss}$        |                                        | -0.1                  | 0 | 0.1                   | V  | -                                                          |

| Input Voltage High (digital inputs)                                                                                                          | V <sub>IH</sub>        | 1 (Pin Group 1)                        | 0.7×V <sub>DD</sub>   |   | 5.5                   | V  | -                                                          |

| RESET Voltage High                                                                                                                           | V <sub>IH_RESET</sub>  | 1 (Pin Group 2)                        | 0.7×V <sub>DD</sub>   | - | $V_{DD}$              | V  | -                                                          |

| Input Voltage Low (digital inputs)                                                                                                           | V <sub>IL</sub>        | 1 (Pin Group 1,2)                      |                       |   | 0.35×V <sub>DD</sub>  | V  | -                                                          |

| Oscillator Input Voltage High XTAL driven by an external clock source                                                                        | V <sub>IHOSC</sub>     | 1 (Pin Group 4)                        | 2.0                   |   | V <sub>DD</sub> + 0.3 | V  | -                                                          |

| Oscillator Input Voltage Low                                                                                                                 | V <sub>ILOSC</sub>     | 1 (Pin Group 4)                        | -0.3                  |   | 0.8                   | V  | -                                                          |

| Output Source Current High (at V <sub>OH</sub> min.) <sup>3,4</sup> • Programmed for low drive strength • Programmed for high drive strength | Іон                    | 1 (Pin Group 1)<br>1 (Pin Group 1)     | -<br>-                |   | -2<br>-9              | mA | -                                                          |

| Output Source Current Low (at V <sub>OL</sub> max.) <sup>3,4</sup> • Programmed for low drive strength • Programmed for high drive strength  | I <sub>OL</sub>        | 1 (Pin Group 1,2)<br>1 (Pin Group 1,2) | -                     |   | 2 9                   | mA | -                                                          |

| Output Voltage High                                                                                                                          | V <sub>OH</sub>        | 1 (Pin Group 1)                        | V <sub>DD</sub> - 0.5 | - | -                     | V  | $I_{OH} = I_{OHmax}$                                       |

| Output Voltage Low                                                                                                                           | V <sub>OL</sub>        | 1 (Pin Group 1,2)                      | -                     | - | 0.5                   | V  | $I_{OL} = I_{OLmax}$                                       |

| Digital Input Current High                                                                                                                   | I <sub>IH</sub>        | 1 (Pin Group 1)                        | -                     | 0 | +/-2.5                | μA | $V_{IN} = 2.4 \text{ V}$ to 5.5 V $V_{IN} = 2.4 \text{ V}$ |

| pull-up enabled or disabled                                                                                                                  |                        | 1 (Pin Group 2)                        |                       |   |                       |    | $V_{IN} = 2.4 \text{ V}$<br>to $V_{DD}$                    |

| Comparator Input Current<br>High                                                                                                             | Іінс                   | 1 (Pin Group 3)                        |                       | 0 | +/-2                  | μA | $V_{IN} = V_{DDA}$                                         |

| Oscillator Input Current High                                                                                                                | l <sub>iHOSC</sub>     | 1 (Pin Group 4)                        | -                     | 0 | +/-2                  | μA | $V_{IN} = V_{DDA}$                                         |

| Internal Pull-Up Resistance                                                                                                                  | R <sub>Pull-Up</sub>   |                                        | 20                    | - | 50                    | kΩ | -                                                          |

| Internal Pull-Down Resistance                                                                                                                | R <sub>Pull-Down</sub> |                                        | 20                    | - | 50                    | kΩ | -                                                          |

|                                                                                                                                              |                        | · · · · · · · · · · · · · · · · · · ·  |                       |   |                       | _  |                                                            |

| Comparator Input Current<br>Low                               | I <sub>ILC</sub>        | 1 (Pin Group 3)   | -                       | 0  | +/-2                    | μΑ           | V <sub>IN</sub> = 0V                              |

|---------------------------------------------------------------|-------------------------|-------------------|-------------------------|----|-------------------------|--------------|---------------------------------------------------|

| Oscillator Input Current Low                                  | I <sub>ILOSC</sub>      | 1 (Pin Group 4)   | -                       | 0  | +/-2                    | μA           | V <sub>IN</sub> = 0V                              |

| DAC Output Voltage Range                                      | $V_{DAC}$               | 1 (Pin Group 5)   | V <sub>SSA</sub> + 0.04 | -  | V <sub>DDA</sub> - 0.04 | V            | $R_{LD} = 3 \text{ k}\Omega,$ $C_{LD} = 400$ $pF$ |

| Output Current <sup>1</sup> High<br>Impedance State           | l <sub>oz</sub>         | 1 (Pin Group 1,2) | -                       | 0  | +/-1                    | μA           | -                                                 |

| Schmitt Trigger Input<br>Hysteresis                           | $V_{HYS}$               | 1 (Pin Group 1,2) | 0.06×V <sub>DD</sub>    | -  | -                       | V            | -                                                 |

| Input capacitance                                             | C <sub>IN</sub>         |                   | -                       | 10 | -                       | pF           | -                                                 |

| Output capacitance                                            | C <sub>OUT</sub>        |                   | -                       | 10 | -                       | pF           | -                                                 |

| GPIO pin interrupt pulse width <sup>5</sup>                   | $T_{INT\_Pulse}$        | 6                 | 1.5                     | 1  | -                       | Bus<br>clock | -                                                 |

| Port rise and fall time (high drive strength). Slew disabled. | $T_{Port\_H\_DIS}$      | 7                 | 5.5                     | -  | 15.1                    | ns           | 2.7 ≤ VDD ≤<br>3.6 V                              |

| Port rise and fall time (high drive strength). Slew enabled.  | T <sub>Port_H_EN</sub>  | 7                 | 1.5                     | -  | 6.8                     | ns           | 2.7 ≤ VDD ≤<br>3.6 V                              |

| Port rise and fall time (low drive strength). Slew disabled.  | T <sub>Port_L_DIS</sub> | 8                 | 8.2                     | -  | 17.8                    | ns           | 2.7 ≤ VDD ≤<br>3.6 V                              |

| Port rise and fall time (low drive strength). Slew enabled.   | T <sub>Port_L_EN</sub>  | 8                 | 3.2                     | 1  | 9.2                     | ns           | 2.7 ≤ VDD ≤<br>3.6 V                              |

| Device (system and core) clock frequency                      | f <sub>SYSCLK</sub>     |                   | 0                       | -  | 100                     | MHz          | -                                                 |

| Bus clock                                                     | $f_{BUS}$               |                   | -                       | -  | 50                      | MHz          | -                                                 |

#### 1. Default Mode

- o Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- o Pin Group 2: RESET

- o Pin Group 3: ADC and Comparator Analog Inputs

- o Pin Group 4: XTAL, EXTAL

- o Pin Group 5: DAC analog output

- 2. ADC (Cyclic) specifications are not guaranteed when VDDA is below 3.0 V.

- 3. Total chip source or sink current cannot exceed 75 mA.

- 4. Contiguous pin DC injection current of regional limit—including sum of negative injection currents or sum of positive injection currents of 16 contiguous pins—is 25 mA.

- 5. Applies to a pin only when it is configured as GPIO and configured to cause an interrupt by appropriately programming GPIOn\_IPOLR and GPIOn\_IENR.

- 6. The greater synchronous and asynchronous timing must be met.

- 7. 75 pF load.

- 8. 15 pF load.

## 2.2 Device Characteristics

| ower mode              | Fransition Behavior                                                                                                                                                                                                                           |                |                 |                  |       |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------------------|-------|

| Symbol                 | Description                                                                                                                                                                                                                                   | Min.           | Max.            | Unit             | Notes |

| $T_{POR}$              | After a POR event, the amount of delay from when VDD reaches 2.7 V to when the first instruction executes (over the operating temperature range).                                                                                             | 199            | 225             | μѕ               |       |

| T <sub>S2R</sub>       | STOP mode to RUN mode                                                                                                                                                                                                                         | 6.79           | 7.27            | μs               | 1     |

| T <sub>LPS2LPR</sub>   | LPS mode to LPRUN mode                                                                                                                                                                                                                        | 240.9          | 551             | μs               | 2     |

| T <sub>VLPS2VLPR</sub> | VLPS mode to VLPRUN mode                                                                                                                                                                                                                      | 1424           | 1459            | μs               | 4     |

| $T_{W2R}$              | WAIT mode to RUN mode                                                                                                                                                                                                                         | 0.57           | 0.62            | μs               | 3     |

| T <sub>LPW2LPR</sub>   | LPWAIT mode to LPRUN mode                                                                                                                                                                                                                     | 237.2          | 554             | μs               | 2     |

| T <sub>VLPW2VLPR</sub> | VLPWAIT mode to VLPRUN mode                                                                                                                                                                                                                   | 1413           | 1500            | μs               | 4     |

| ower Consu             | mption Operating Behaviors                                                                                                                                                                                                                    |                |                 |                  |       |

|                        |                                                                                                                                                                                                                                               |                | Typical at 3    | .3 V, 25 °C      |       |

| Mode                   | Conditions                                                                                                                                                                                                                                    | Max. Frequency | I <sub>DD</sub> | I <sub>DDA</sub> | Note  |

|                        | 100 MHz core clock, 50 MHz peripheral clock, regulators are in full regulation, relaxation oscillator on, PLL powered on, continuous MAC instructions with fetches from program Flash, all peripheral modules enabled. TMRs and SCIs using 1× |                |                 |                  |       |

| RUN1                   | from program Flash, all peripheral modules enabled, TMRs and SCIs using 1× peripheral clock, NanoEdge within                                                                                                                                  | 100 MHz        | 38.1 mA         | 9.9 mA           |       |

eFlexPWM using 2x peripheral clock, ADC/DAC (only one 12-bit DAC and all 6-bit DACs) powered on and clocked, comparator powered on, all ports

configured as inputs with input low and no

DC loads

| RUN2   | 50 MHz core and peripheral clock, regulators are in full regulation, relaxation oscillator on, PLL powered on, continuous MAC instructions with fetches from program Flash, all peripheral modules enabled, TMRs and SCIs using 1x peripheral clock, NanoEdge within eFlexPWM using 2x peripheral clock, ADC/DAC (only one 12-bit DAC and all 6-bit DACs) powered on and clocked, comparator powered on, all ports configured as inputs with input low and no DC loads | 50 MHz | 27.6 mA | 9.9 mA |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|--------|--|

| WAIT   | 50 MHz core and peripheral clock, regulators are in full regulation, relaxation oscillator on, PLL powered on, core in WAIT state, all peripheral modules enabled, TMRs and SCIs using 1× clock, NanoEdge within eFlexPWM using 2× clock, ADC/DAC (one 12-bit DAC, all 6-bit DACs)/comparator powered off, all ports configured as inputs with input low and no DC loads                                                                                               | 50 MHz | 24.0 mA | -      |  |

| STOP   | 4 MHz core and peripheral clock, regulators are in full regulation, relaxation oscillator on, PLL powered off, core in STOP state, all peripheral module and core clocks are off, ADC/DAC/Comparator powered off, all ports configured as inputs with input low and no DC loads                                                                                                                                                                                        | 4 MHz  | 6.3 mA  | -      |  |

| LPRUN  | 200 kHz core and peripheral clock from relaxation oscillator's low speed clock, relaxation oscillator in standby mode, regulators are in standby, PLL disabled, repeat NOP instructions, all peripheral modules enabled, except NanoEdge within eFlexPWM and cyclic ADCs, one 12-bit DAC and all 6-bit DACs enabled, simple loop with running from platform instruction buffer, all ports configured as inputs with input low and no DC loads                          | 2 MHz  | 2.8 mA  | 3.1 mA |  |

| LPWAIT | 200 kHz core and peripheral clock from relaxation oscillator's low speed clock, relaxation oscillator in standby mode, regulators are in standby, PLL disabled, all peripheral modules enabled, except NanoEdge within eFlexPWM and cyclic ADCs, one 12-bit DAC and all 6-bit DACs enabled, core in WAIT mode, all ports configured as inputs with input low and no DC loads                                                                                           | 2 MHz  | 2.7 mA  | 3.1 mA |  |

| $V_{POR\_A}$     | POR Assert Voltage <sup>7</sup>                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                   | 2.0    | -    | V     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------|------|-------|

| Symbol           | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                         | Min.                                                | Тур.   | Max. | Unit  |

| PMC Low-Volt     | age Detection (LVD) and Power-On Reset (                                                                                                                                                                                                                                                                                                                                                                                               | POR) Parameters                                     |        | Т    |       |

| t <sub>iF</sub>  | Delay from Interrupt Assertion to Fetch of first instruction (exiting STOP mode)                                                                                                                                                                                                                                                                                                                                                       | 361.3                                               | 570.9  | ns   |       |

| t <sub>RDA</sub> | RESET desertion to First Address Fetch                                                                                                                                                                                                                                                                                                                                                                                                 | 865 × T <sub>OSC</sub> + 8 ×<br>T <sub>SYSCLK</sub> | -      | ns   | 6     |

| t <sub>RA</sub>  | Minimum RESET Assertion Duration                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                  | -      | ns   | 5     |

| Symbol           | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                         | Min.                                                | Max.   | Unit | Notes |

| Reset and Inte   | errupt Timing                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |        |      |       |

| VLPSTOP          | 32 kHz core and peripheral clock from a 64 kHz external clock source, oscillator in power down, all relaxation oscillators disabled, large regulator is in standby, small regulator is disabled, PLL disabled, all peripheral modules, except COP, disabled and clocks gated off, core in STOP mode, all ports configured as inputs with input low and no DC loads                                                                     | 200 kHz                                             | 0.7 mA | -    |       |

| VLPWAIT          | 32 kHz core and peripheral clock from a 64 kHz external clock source, oscillator in power down, all relaxation oscillators disabled, large regulator is in standby, small regulator is disabled, PLL disabled, all peripheral modules, except COP, disabled and clocks gated off, core in WAIT mode, all ports configured as inputs with input low and no DC loads                                                                     | 200 kHz                                             | 0.7 mA | -    |       |

| VLPRUN           | 32 kHz core and peripheral clock from a 64 kHz external clock source, oscillator in power down, all relaxation oscillators disabled, large regulator is in standby, small regulator is disabled, PLL disabled, repeat NOP instructions, all peripheral modules, except COP and EWM, disabled and clocks gated off, simple loop running from platform instruction buffer, all ports configured as inputs with input low and no DC loads | 200 kHz                                             | 0.7 mA | -    |       |

| LPSTOP           | 200 kHz core and peripheral clock from relaxation oscillator's low speed clock, relaxation oscillator in standby mode, regulators are in standby, PLL disabled, only PITs and COP enabled, other peripheral modules disabled and clocks gated off, core in STOP mode, all ports configured as inputs with input low and no DC loads                                                                                                    | 2 MHz                                               | 1.2 mA | -    |       |

| $V_{POR\_R}$          | POR Release Voltage <sup>8</sup>                             | -                    | 2.7                    | -                   | V     |

|-----------------------|--------------------------------------------------------------|----------------------|------------------------|---------------------|-------|

| V <sub>LVI_2p7</sub>  | LVI_2p7 Threshold Voltage                                    | -                    | 2.73                   | -                   | V     |

| $V_{\text{LVI}\_2p2}$ | LVI_2p2 Threshold Voltage                                    | -                    | 2.23                   | -                   | V     |

| JTAG Timing           |                                                              |                      |                        | •                   | 1     |

| Symbol                | Description                                                  | Min.                 | Max.                   | Unit                | Notes |

| f <sub>OP</sub>       | TCK frequency of operation                                   | DC                   | f <sub>SYSCLK</sub> /8 | MHz                 |       |

| t <sub>PW</sub>       | TCK clock pulse width                                        | 50                   | -                      | ns                  |       |

| t <sub>DS</sub>       | TMS, TDI data set-up time                                    | 5                    | -                      | ns                  |       |

| t <sub>DH</sub>       | TMS, TDI data hold time                                      | 5                    | -                      | ns                  |       |

| t <sub>DV</sub>       | TCK low to TDO data valid                                    | -                    | 30                     | ns                  |       |

| t <sub>TS</sub>       | TCK low to TDO tri-state                                     | _                    | 30                     | ns                  |       |

|                       | 2 V Parameters                                               |                      | 00                     | 110                 |       |

| Symbol                | Characteristic                                               | Min.                 | Тур.                   | Max.                | Unit  |

| V <sub>CAP</sub>      | Output Voltage <sup>9</sup>                                  | -                    | 1.22                   | -                   | V     |

| I <sub>SS</sub>       | Short Circuit Current <sup>10</sup>                          | -                    | 600                    | -                   | mA    |

| T <sub>RSC</sub>      | Short Circuit Tolerance (V <sub>CAP</sub> shorted to ground) | -                    | -                      | 30                  | Mins  |

| V <sub>REF</sub>      | Reference Voltage (after trim)                               | -                    | 1.21                   | -                   | V     |

| xternal Cloc          | ck Timing                                                    |                      |                        |                     |       |

| Symbol                | Characteristic                                               | Min.                 | Тур.                   | Max.                | Unit  |

| f <sub>OSC</sub>      | Frequency of operation (external clock driver)               | -                    | -                      | 50                  | MHz   |

| t <sub>PW</sub>       | Clock pulse width <sup>11</sup>                              | 8                    |                        |                     | ns    |

| t <sub>rise</sub>     | External clock input rise time <sup>12</sup>                 | -                    | -                      | 1                   | ns    |

| t <sub>fall</sub>     | External clock input fall time <sup>13</sup>                 | -                    | -                      | 1                   | ns    |

| $V_{ih}$              | Input high voltage overdrive by an external clock            | 0.85×V <sub>DD</sub> | -                      | -                   | V     |

| $V_{il}$              | Input low voltage overdrive by an external clock             | -                    | -                      | 0.3×V <sub>DD</sub> | V     |

| Phase-Locke           | d Loop (PLL) Timing                                          |                      |                        |                     |       |

| Symbol                | Characteristic                                               | Min.                 | Тур.                   | Max.                | Unit  |

| f <sub>Ref_PLL</sub>  | PLL input reference frequency <sup>14</sup>                  | 8                    | 8                      | 16                  | MHz   |

| f <sub>OP_PLL</sub>   | PLL output frequency <sup>15</sup>                           | 200                  | -                      | 400                 | MHz   |

| t <sub>Lock_PLL</sub> | PLL lock time <sup>16</sup>                                  | 35.5                 | -                      | 73.2                | μs    |

| t <sub>DC_PLL</sub>   | Allowed Duty Cycle of input reference                        | 40                   | 50                     | 60                  | %     |

11

| Symbol                               | Characteristic                                              | Min. | Тур.       | Max. | Unit           |  |

|--------------------------------------|-------------------------------------------------------------|------|------------|------|----------------|--|

| f <sub>XOSC</sub>                    | Frequency of operation                                      | 4    | 8          | 16   | MHz            |  |

| Relaxation Os                        | cillator Electrical Specifications                          |      |            |      |                |  |

| Symbol                               | Characteristic                                              | Min. | Тур.       | Max. | Unit           |  |

|                                      | 8 MHz Output Frequency <sup>17</sup>                        |      |            |      |                |  |

|                                      | RUN Mode                                                    | 7.84 | 8          | 8.16 | MHz            |  |

| f <sub>ROSC 8M</sub>                 | • 0 °C to 85 °C                                             | 7.76 | 8          | 8.24 | MHz            |  |

|                                      | • -40 °C to 85 °C                                           | 7.70 | 8          | 0.24 | IVII IZ        |  |

|                                      | Standby Mode (IRC trimmed @ 8 MHz)                          |      | 405        |      | 1411=          |  |

|                                      | • -40 °C to 85 °C                                           | -    | 405        | -    | kHz            |  |

|                                      | 8 MHz Frequency Variation over 25 °C                        |      |            |      |                |  |

|                                      | RUN Mode                                                    |      |            |      |                |  |

| f <sub>ROSC_8M_Delta</sub>           | Due to temperature                                          | -    | +/-1.5     | +/-2 | %              |  |

|                                      | 0 °C to 85 °C      -40 °C to 85 °C                          | -    | +/-1.5     | +/-2 | /°<br>%        |  |

|                                      |                                                             |      | 17 1.0     | 1, 0 | 70             |  |

| <b>£</b> 17                          | 200 kHz Output Frequency <sup>18</sup> RUN Mode             |      |            |      |                |  |

| f <sub>ROSC_200k</sub> <sup>17</sup> | • -40 °C to 85 °C                                           | 194  | 200        | 206  | kHz            |  |

|                                      |                                                             | -    |            |      |                |  |

|                                      | 200 kHz Output Frequency Variation over 25 °C <sup>18</sup> |      |            |      |                |  |

| 4                                    | RUN Mode                                                    |      |            |      |                |  |

| f <sub>ROSC_200k_Delta</sub>         | Due to temperature                                          |      |            |      |                |  |

|                                      | • 0 °C to 85 °C                                             | -    | +/-1.5     | +/-2 | %              |  |

|                                      | • -40 °C to 85 °C                                           | -    | +/-1.5     | +/-3 | / <sub>%</sub> |  |

|                                      | Otal Biration Time                                          |      | ,,         | ., 0 | 1              |  |

|                                      | Stabilization Time  • 8 MHz output <sup>19</sup>            |      | 0.40       |      |                |  |

| t <sub>Stab</sub>                    | 8 MHz output     200 kHz output <sup>20</sup>               | -    | 0.12<br>10 | -    | μs             |  |

|                                      | ·                                                           | -    |            | -    | μs             |  |

| t <sub>DC_ROSC</sub>                 | Output Duty Cycle                                           | 48   | 50         | 52   | %              |  |

| Flash Specific<br>Symbol             | Description                                                 | Min. | Тур.       | Max. | Unit           |  |

| t <sub>hvpgm4</sub>                  | Longword Program high-voltage time                          | -    | 7.5        | 18   | μs             |  |

| t <sub>hversscr</sub>                | Sector Erase high-voltage time <sup>21</sup>                | -    | 13         | 113  | ms             |  |

| t <sub>hversall</sub>                | Erase All high-voltage time <sup>21</sup>                   | _    | 52         | 452  | ms             |  |

| *iivoi saii                          | Read 1s Section execution time (flash                       |      | <u> </u>   | 102  | 15             |  |

| t <sub>rd1sec1k</sub>                | sector) <sup>22</sup>                                       | -    | -          | 60   | μs             |  |

| t <sub>pgmchk</sub>                  | Program Check execution time <sup>22</sup>                  | -    | -          | 45   | μs             |  |

| t <sub>rdrsrc</sub>                  | Read Resource execution time <sup>22</sup>                  | -    | -          | 30   | μs             |  |

| t <sub>pgm4</sub>                    | Program Longword execution time                             | -    | 65         | 145  | μs             |  |

| t <sub>ersscr</sub>                  | Erase Flash Sector execution time <sup>23</sup>             | -    | 14         | 114  | ms             |  |

| Symbol                   | Characteristic                                                                          | Min.                                                            | Тур.               | Max.                                                          | Unit              |

|--------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|---------------------------------------------------------------|-------------------|

| 12-bit DAC El            | ectrical Specifications                                                                 |                                                                 |                    |                                                               |                   |

| C <sub>ADCI</sub>        | Input sampling capacitance                                                              | -                                                               | 4.8                | -                                                             | pF                |

| I <sub>INJ</sub>         | Input injection current <sup>34</sup>                                                   | -                                                               | -                  | +/-3                                                          | mA                |

| ENOB                     | Effective number of bits                                                                | -                                                               | 10.6               | -                                                             | bits              |

| E <sub>GAIN</sub>        | Gain Error                                                                              | -                                                               | 0.996 to 1.004     | 0.99 to<br>1.101                                              | -                 |

| V <sub>OFFSET</sub>      | Offset <sup>33</sup> • Fully differential • Single ended/Unipolar                       | -<br>-                                                          | +/- 8<br>+/- 12    | -                                                             | mV<br>mV          |

| DNL <sub>ADC</sub>       | Differential non-linearity <sup>31</sup>                                                | -                                                               | +/- 0.5            | +/- 0.8                                                       | LSB <sup>32</sup> |

| INL <sub>ADC</sub>       | Integral non-linearity <sup>31</sup>                                                    | -                                                               | +/- 1.5            | +/- 2.2                                                       | LSB <sup>32</sup> |

| $I_{VREFH}$              | V <sub>REFH</sub> current (in external mode)                                            | -                                                               | 190                | 225                                                           | μA                |

| I <sub>ADPWRDWN</sub>    | ADC power down current (adc_pdn enabled)                                                | -                                                               | 0.1                | -                                                             | μA                |

| I <sub>ADCRUN</sub>      | ADC RUN current (per ADC block)                                                         | -                                                               | 1.8                | -                                                             | mA                |

| t <sub>ADCPU</sub>       | ADC power-up time (from adc_pdn)                                                        | -                                                               | 13                 | -                                                             | tadcclk           |

| t <sub>ADC</sub>         | Conversion time                                                                         | -                                                               | 8                  | -                                                             | tADCCLK           |

| V <sub>ADCIN</sub>       | Input voltage range (per input) <sup>30</sup> • External Reference • Internal Reference | V <sub>REFL</sub><br>V <sub>SSA</sub>                           | -<br>-             | $V_{REFH}$                                                    | V<br>V            |

| R <sub>ADC</sub>         | Conversion range <sup>29</sup> • Fully differential • Single-ended/unipolar             | -( V <sub>REFH</sub> - V <sub>REFL</sub> )<br>V <sub>REFL</sub> | -                  | V <sub>REFH</sub> -<br>V <sub>REFL</sub><br>V <sub>REFH</sub> | V<br>V            |

| f <sub>ADCCLK</sub>      | ADC conversion clock <sup>28</sup>                                                      | 0.1                                                             | -                  | 10                                                            | MHz               |

| $V_{REFHX}$              | V <sub>REFH</sub> supply voltage <sup>27</sup>                                          | V <sub>DDA</sub> - 0.6                                          |                    | $V_{DDA}$                                                     | V                 |

| $V_{DDA}$                | Supply voltage <sup>26</sup>                                                            | 3.0                                                             | 3.3                | 3.6                                                           | V                 |

| Symbol                   | Characteristic                                                                          | Min.                                                            | Тур.               | Max.                                                          | Unit              |

| 12-bit Cyclic            | ADC Electrical Specifications                                                           |                                                                 |                    |                                                               |                   |

| n <sub>flashcyc</sub>    | Cycling endurance <sup>25</sup>                                                         | 10 K                                                            | 50 K <sup>24</sup> | -                                                             | cycles            |

| t <sub>flashret1k</sub>  | Data retention after up to 1 K cycles                                                   | 20                                                              | 100 <sup>24</sup>  | -                                                             | years             |

| t <sub>flashret10k</sub> | time <sup>22</sup> Data retention after up to 10 K cycles                               | 5                                                               | 50 <sup>24</sup>   | -                                                             | years             |

| t <sub>vfykey</sub>      | Verify Backdoor Access Key execution                                                    | -                                                               | -                  | 30                                                            | μs                |

| t <sub>ersall</sub>      | Erase All Blocks execution time <sup>23</sup>                                           | _                                                               | 70                 | 575                                                           | ms                |

| t <sub>pgmonce</sub>     | Program Once execution time                                                             | -                                                               | 65                 | -                                                             | μs                |

| $t_{rdonce}$             | Read Once execution time <sup>22</sup>                                                  | -                                                               | -                  | 25                                                            | μs                |

| t <sub>SETTLE</sub> | Settling time $^{35}$ under $R_{LD}$ = 3 k $\Omega,C_{LD}$ = 400 pF                                                   | -                     | 1                   | -                       | μs                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|-------------------------|-------------------|

| t <sub>DACPU</sub>  | DAC power-up time (from PWRDWN release to valid DACOUT)                                                               | -                     | -                   | 11                      | μs                |

| INL <sub>DAC</sub>  | Integral non-linearity <sup>37</sup>                                                                                  | -                     | +/- 3               | +/- 4                   | LSB <sup>36</sup> |

| DNL <sub>DAC</sub>  | Differential non-linearity <sup>37</sup>                                                                              | -                     | +/- 0.8             | +/- 0.9                 | LSB <sup>36</sup> |

| MON <sub>DAC</sub>  | Monotonicity (> 6 sigma monotonicity, < 3.4 ppm non-monotonicity)                                                     |                       | Guaranteed          |                         | -                 |

| V <sub>OFFSET</sub> | Offset error <sup>37</sup> (5% to 95% of full range)                                                                  | -                     | +/- 25              | +/- 43                  | mV                |

| E <sub>GAIN</sub>   | Gain error <sup>37</sup> (5% to 95% of full range)                                                                    | -                     | +/- 0.5             | +/- 1.5                 | %                 |

| $V_{OUT}$           | Output voltage range                                                                                                  | $V_{SSA} + 0.04$      | -                   | V <sub>DDA</sub> - 0.04 | V                 |

| SNR                 | Signal-to-noise ratio                                                                                                 | -                     | 85                  | -                       | dB                |

| ENOB                | Effective number of bits                                                                                              | -                     | 11                  | -                       | bits              |

| Comparator a        | and 6-bit DAC Electrical Specifications                                                                               |                       |                     |                         |                   |

| Symbol              | Description                                                                                                           | Min.                  | Тур.                | Max.                    | Unit              |

| $V_{DD}$            | Supply voltage                                                                                                        | 2.7                   | -                   | 3.6                     | V                 |

| I <sub>DDHS</sub>   | Supply current, High-speed mode(EN=1, PMODE=1)                                                                        | -                     | 300                 | -                       | μA                |

| I <sub>DDLS</sub>   | Supply current, Low-speed mode(EN=1, PMODE=0)                                                                         | -                     | 36                  | -                       | μA                |

| V <sub>AIN</sub>    | Analog input voltage                                                                                                  | V <sub>ss</sub>       | -                   | V <sub>DD</sub>         | V                 |

| $V_{AIO}$           | Analog input offset voltage                                                                                           | -                     | -                   | 20                      | mV                |

| $V_{H}$             | Analog comparator hysteresis <sup>38</sup> • CR0[HYSTCTR]=00  • CR0[HYSTCTR]=01  • CR0[HYSTCTR]=10  • CR0[HYSTCTR]=11 | -<br>-<br>-           | 5<br>25<br>55<br>80 | 13<br>48<br>105<br>148  | mV<br>mV<br>mV    |

| $V_{CMPOh}$         | Output high                                                                                                           | V <sub>DD</sub> - 0.5 | -                   | -                       | V                 |

| $V_{CMPOI}$         | Output low                                                                                                            | -                     | -                   | 0.5                     | V                 |

| t <sub>DHS</sub>    | Propagation delay, high-speed mode(EN=1, PMODE=1) <sup>39</sup>                                                       | -                     | 25                  | 50                      | ns                |

| t <sub>DLS</sub>    | Propagation delay, low-speed mode(EN=1, PMODE=0) 39                                                                   | -                     | 60                  | 200                     | ns                |

| t <sub>DInit</sub>  | Analog comparator initialization delay <sup>40</sup>                                                                  | -                     | 40                  | -                       | μs                |

| I <sub>DAC6b</sub>  | 6-bit DAC current adder (enabled)                                                                                     | -                     | 7                   | -                       | μA                |

| R <sub>DAC6b</sub>  | 6-bit DAC reference inputs                                                                                            | $V_{DDA}$             | -                   | $V_{DD}$                | V                 |

|                     |                                                                                                                       |                       |                     |                         |                   |

| INL <sub>DAC6b</sub>     | 6-bit DAC integral non-linearity                            | -0.5                         |                    | -                   | 0.5    | LSB <sup>41</sup> |

|--------------------------|-------------------------------------------------------------|------------------------------|--------------------|---------------------|--------|-------------------|

| DNL <sub>DAC6b</sub>     | 6-bit DAC differential non-linearity                        | -0.3 -                       |                    | -                   | 0.3    | LSB <sup>41</sup> |

| eFlexPWM Ti              | ming Parameters                                             |                              |                    |                     |        |                   |

| Symbol                   | Characteristic                                              | Min.                         | Ty                 | yp.                 | Max.   | Unit              |

| f <sub>PWM</sub>         | PWM clock frequency                                         | -                            | 1                  | 00                  | -      | MHz               |

| S <sub>PWMNEP</sub>      | NanoEdge Placement (NEP) step size 42,43                    | -                            | 3                  | 12                  | -      | ps                |

| t <sub>DFLT</sub>        | Delay for fault input activating to PWM output deactivated  | 1                            |                    | -                   | -      | ns                |

| t <sub>PWMPU</sub>       | Power-up time <sup>44</sup>                                 | -                            | 2                  | 25                  | -      | μs                |

| Quad Timer 1             | Fiming                                                      |                              | •                  | <u>'</u>            |        | •                 |

| Symbol                   | Characteristic                                              | Min.                         | M                  | ax.                 | Unit   | Notes             |

| P <sub>IN</sub>          | Timer input period                                          | 2T <sub>timer</sub> + 6      |                    | -                   | ns     | 45                |

| P <sub>INHL</sub>        | Timer input high/low period                                 | 1T <sub>timer</sub> + 3      |                    | -                   | ns     | 45                |

| Pout                     | Timer output period                                         | 2T <sub>timer</sub> - 2      |                    | -                   | ns     | 45                |

| Pouthl                   | Timer output high/low period                                | 1T <sub>timer</sub> - 2      |                    | -                   | ns     | 45                |

| QSPI Timing              |                                                             |                              |                    |                     |        |                   |

| Symbol                   | Characteristic                                              | Min.                         |                    | Max.                |        | Unit              |

|                          | Gharacteristic                                              | Master Slave Maste           | Maste              | r Slave             | Oille  |                   |

| t <sub>C</sub>           | Cycle time                                                  | 60                           | 60                 | -                   | -      | ns                |

| t <sub>ELD</sub>         | Enable lead time                                            | -                            | 20                 |                     |        | ns                |

| t <sub>ELG</sub>         | Enable lag time                                             | -                            | 20                 | -                   | -      | ns                |

| t <sub>CH</sub>          | Clock (SCLK) high time                                      | 28                           | 28                 | -                   | -      | ns                |

| t <sub>CL</sub>          | Clock (SCLK) low time                                       | 28                           | 28                 | -                   | -      | ns                |

| t <sub>DS</sub>          | Data set-up time required for inputs                        | 20                           | 1                  | -                   | -      | ns                |

| t <sub>DH</sub>          | Data hold time required for inputs                          | 1                            | 3                  | -                   | -      | ns                |

| t <sub>A</sub>           | Access time (time to data active from high-impedance state) |                              | 5                  |                     | -      | ns                |

| $t_D$                    | Disable time (hold time to high-impedance state)            | 5                            |                    | -                   | ns     |                   |

| $t_{DV}$                 | Data valid for outputs                                      |                              |                    |                     |        | ns                |

| t <sub>DI</sub>          | Data invalid                                                | 0                            | 0                  | -                   | -      | ns                |

| $t_R$                    | Rise time                                                   | -                            | -                  | 1                   | 1      | ns                |

| t <sub>F</sub>           | Fall time                                                   | 1                            |                    | 1                   | 1      | ns                |

| QSCI Timing              |                                                             |                              |                    |                     |        |                   |

|                          | Characteristic                                              | Min.                         | Min. Max.          |                     | Unit   | Note              |

| Symbol                   | ı                                                           | - (f <sub>MAX_SCI</sub> /16) |                    |                     |        |                   |

| Symbol BR <sub>SCI</sub> | Baud rate                                                   | -                            | (f <sub>MAX_</sub> | <sub>SCI</sub> /16) | Mbit/s | 46                |

| $PW_{TXD}$          | TXD pulse width                    | 0.965/BR <sub>SCI</sub> | 1.04/BR <sub>SCI</sub> | ns     |       |

|---------------------|------------------------------------|-------------------------|------------------------|--------|-------|

| CAN Timing          |                                    |                         |                        |        |       |

| Symbol              | Characteristic                     | Min.                    | Max.                   | Unit   | Notes |

| BR <sub>CAN</sub>   | Baud rate                          | -                       | 1                      | Mbit/s |       |

| T <sub>WAKEUP</sub> | CAN Wakeup dominant pulse filtered | -                       | 1.5                    | μs     |       |

| T <sub>WAKEUP</sub> | CAN Wakeup dominant pulse pass     | 5                       | -                      | μs     |       |

#### **IIC Timing**

| Cumbal                | Symbol Characteristic                                                                        |                   | Min.               |                        |       | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------------------------|-------------------|--------------------|------------------------|-------|------|-------|

| Symbol                | Characteristic                                                                               | Min. Max.         |                    | Min. Max.              |       | Unit | Notes |

| f <sub>SCL</sub>      | SCL clock frequency                                                                          | 0                 | 100                | 0                      | 400   | kHz  |       |

| t <sub>HD_STA</sub>   | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4                 | -                  | 0.6                    | -     | μs   |       |

| t <sub>SCL_LOW</sub>  | LOW period of the SCL clock                                                                  | 4.7               | -                  | 1.3                    | -     | μs   |       |

| t <sub>SCL_HIGH</sub> | HIGH period of the SCL clock                                                                 | 4                 | -                  | 0.6                    | -     | μs   |       |

| t <sub>SU_STA</sub>   | Set-up time for a repeated START condition                                                   | 4.7               | -                  | 0.6                    | -     | μs   |       |

| t <sub>HD_DAT</sub>   | Data hold time for IIC bus devices                                                           | 047               | 3.45 <sup>48</sup> | 0 <sup>49</sup>        | 0.947 | μs   |       |

| t <sub>SU_DAT</sub>   | Data set-up time                                                                             | 250 <sup>50</sup> | -                  | 100 <sup>51</sup>      | -     | ns   | 48    |

| t <sub>r</sub>        | Rise time of SDA and SCL signals                                                             | -                 | 1000               | 20 + 0.1C <sub>b</sub> | 300   | ns   | 52    |

| t <sub>f</sub>        | Fall time of SDA and SCL signals                                                             | -                 | 300                | 20 + 0.1C <sub>b</sub> | 300   | ns   | 51    |

| t <sub>SU_STOP</sub>  | Set-up time for STOP condition                                                               | 4                 | -                  | 0.6                    | -     | μs   |       |

| t <sub>BUS_Free</sub> | Bus free time between STOP and START condition                                               | 4.7               | -                  | 1.3                    | -     | μs   |       |

| t <sub>SP</sub>       | Pulse width of spikes that must be suppressed by the input filter                            | N/A               | N/A                | 0                      | 50    | ns   |       |

- 1. CPU clock = 4 MHz and System running from 8 MHz IRC Applicable to all wakeup times: Wakeup times (in 1,2,3,4) are measured from GPIO toggle for wakeup till GPIO toggle at the wakeup interrupt subroutine from respective stop/wait mode.

- 2. CPU clock = 200 kHz and 8 MHz IRC on standby. Exit via interrupt on Port C GPIO.

- 3. Clock configuration: CPU and system clocks= 100 MHz; Bus Clock = 50 MHz. Exit via an interrupt on PortC GPIO.

- 4. Using 64 KHz external clock; CPU Clock = 32 KHz. Exit via an interrupt on PortC GPIO.

- 5. If the RESET pin filter is enabled by setting the RST\_FLT bit in the SIM\_CTRL register to 1, the minimum pulse assertion must be greater than 21 ns.

- 6. TOSC means oscillator clock cycle; TSYSCLK means system clock cycle.

- 7. During 3.3 V VDD power supply ramp down.

- 8. During 3.3 V VDD power supply ramp up (gated by LVI\_2p7).

- 9. Value is after trim.

- 10. Guaranteed by design.

- 11. The chip may not function if the high or low pulse width is smaller than 6.25 ns.

- 12. External clock input rise time is measured from 10% to 90%.

- 13. External clock input fall time is measured from 90% to 10%.

- 14. An externally supplied reference clock should be as free as possible from any phase jitter for the PLL to work correctly. The PLL is optimized for 8 MHz input.

- 15. The frequency of the core system clock cannot exceed 100 MHz. If the NanoEdge PWM is available, the PLL output must be set to 400 MHz.

- 16. This is the time required after the PLL is enabled to ensure reliable operation.

- 17. Frequency after application of 8 MHz trimmed.

- 18. Frequency after application of 200 kHz trimmed.

- 19. Standby to run mode transition.

- 20. Power down to run mode transition.

- 21. Maximum time based on expectations at cycling end-of-life.

- 22. Assumes 25 MHz flash clock frequency.

- 23. Maximum times for erase parameters based on expectations at cycling end-of-life.

- 24. Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

- 25. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  Tj  $\leq$  125°C.

- 26. The ADC functions up to VDDA = 2.7 V. When VDDA is below 3.0 V, ADC specifications are not guaranteed.

- 27. When the input is at the V<sub>REFL</sub> level, the resulting output will be all zeros (hex 000), plus any error contribution due to offset and gain error. When the input is at the V<sub>REFH</sub> level the output will be all ones (hex FFF), minus any error contribution due to offset and gain error.

- 28. ADC clock duty cycle is 45% ~ 55%.

- 29. Conversion range is defined for x1 gain setting. For x2 and x4 the range is 1/2 and 1/4, respectively.

- 30. In unipolar mode, positive input must be ensured to be always greater than negative input.

- 31. INLADC/DNLADC is measured from VADCIN = VREFL to VADCIN = VREFH using Histogram method at x1 gain setting.

- 32. Least Significant Bit = 0.806 mV at 3.3 V VDDA, x1 gain setting.

- 33. Any off-channel with 50 kHz full-scale input to the channel being sampled with DC input (isolation crosstalk).

- 34. The current that can be injected into or sourced from an unselected ADC input without affecting the performance of the ADC.

- 35. Settling time is swing range from VSSA to VDDA.

- 36. LSB = 0.806 mV.

- 37. No guaranteed specification within 5% of VDDA or VSSA.