### **General Description**

The MAX3301E/MAX3302E fully integrated USB On-the-Go (OTG) transceivers and charge pumps allow mobile devices such as PDAs, cellular phones, and digital cameras to interface directly with USB peripherals and each other without the need of a host PC. Use the MAX3301E/MAX3302E with an embedded USB host to directly connect to peripherals such as printers or external hard drives.

The MAX3301E/MAX3302E integrate a USB OTG transceiver, a VBUS charge pump, a linear regulator, and an I<sup>2</sup>C-compatible, 2-wire serial interface. An internal level shifter allows the MAX3301E/MAX3302E to interface with +1.65V to +3.6V logic supply voltages. The MAX3301E/MAX3302E's OTG-compliant charge pump operates with +3V to +4.5V input supply voltages, and supplies an OTG-compatible output on VBUS while sourcing more than 8mA of output current.

The MAX3301E/MAX3302E enable USB OTG communication from highly integrated digital devices that cannot supply or tolerate the +5V VBUS levels that USB OTG requires. The device supports USB OTG session-request protocol (SRP) and host-negotiation protocol (HNP).

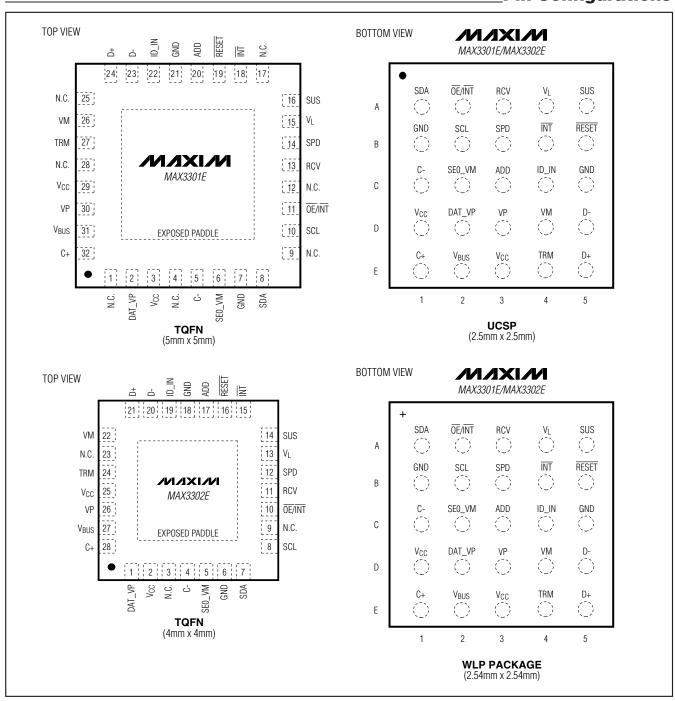

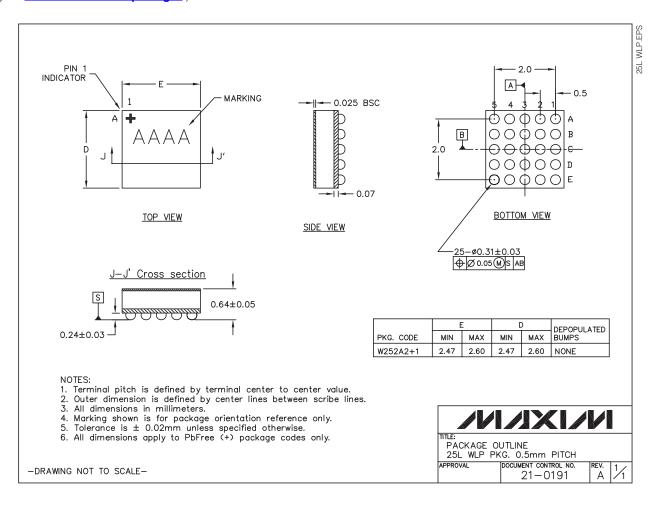

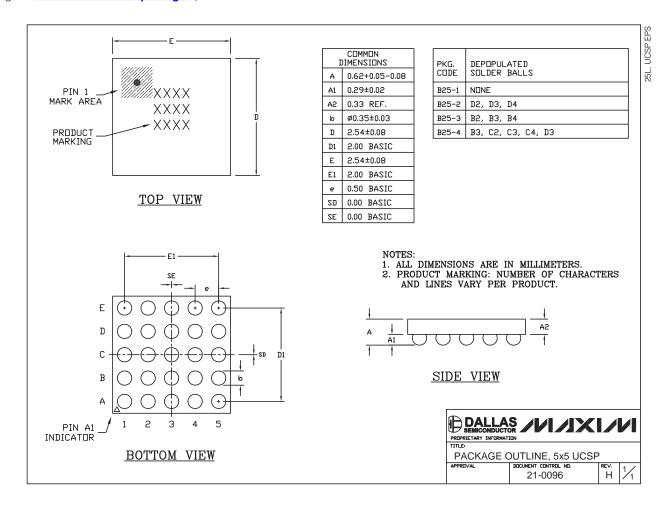

The MAX3301E/MAX3302E provide built-in ±15kV electrostatic-discharge (ESD) protection for the VBUS, ID\_IN, D+, and D- terminals. The MAX3301E/MAX3302E are available in 25-bump chip-scale (UCSP™), 25-bump WLP package, 28-pin TQFN, and 32-pin TQFN packages and operate over the extended -40°C to +85°C temperature range.

### **Selector Guide**

| PART     | POWER-UP STATE†                                                   | I <sup>2</sup> C ADDRESSES FOR<br>SPECIAL-FUNCTION<br>REGISTER 2 |

|----------|-------------------------------------------------------------------|------------------------------------------------------------------|

| MAX3301E | Shutdown (sdwn = 1,<br>bit 0 of special-<br>function register 2)  | 16h, 17h                                                         |

| MAX3302E | Operating (sdwn = 1,<br>bit 0 of special-<br>function register 2) | 10h, 11h, and 16h, 17h                                           |

†The MAX3301E powers up in its lowest power state and the MAX3302E powers up in the operational, VP/VM USB mode.

## **Applications**

Mobile Phones Digital Cameras **PDAs** MP3 Players

**Features**

- **USB 2.0-Compliant Full-/Low-Speed OTG Transceivers**

- ♦ Ideal for USB On-the-Go, Embedded Host, or **Peripheral Devices**

- ♦ ±15kV ESD Protection on ID\_IN, VBUS, D+, and D-**Terminals**

- ♦ Charge Pump for VBUS Signaling and Operation Down to 3V

- ♦ Internal VBUS and ID Comparators

- ♦ Internal Switchable Pullup and Pulldown **Resistors for Host/Peripheral Functionality**

- ♦ I<sup>2</sup>C Bus Interface with Command and Status Registers

- **♦ Linear Regulator Powers Internal Circuitry and** D+/D- Pullup Resistors

- ♦ Support SRP and HNP

### **Ordering Information**

| PART           | PACKAGE<br>SIZE<br>(mm) | PIN-<br>PACKAGE | PKG<br>CODE |

|----------------|-------------------------|-----------------|-------------|

| MAX3301EEBA-T  | 2.5 x 2.5               | 25 UCSP‡        | B25-1       |

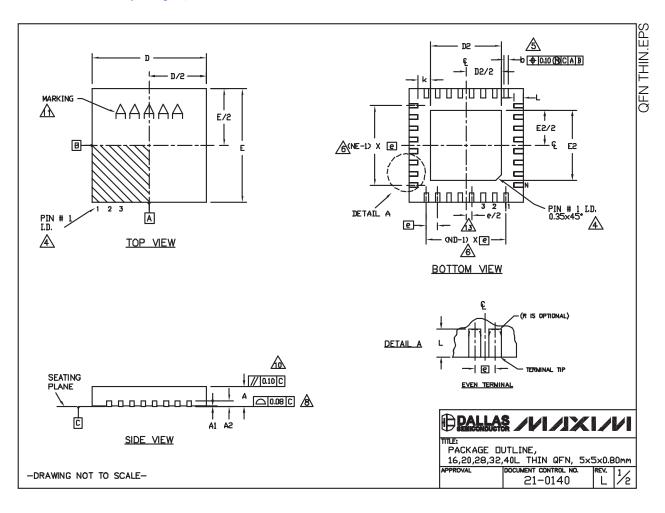

| MAX3301EETJ    | 5 x 5                   | 32 TQFN-EP**    | T3255-4     |

| MAX3302EEBA-T* | 2.5 x 2.5               | 25 UCSP‡        | B25-1       |

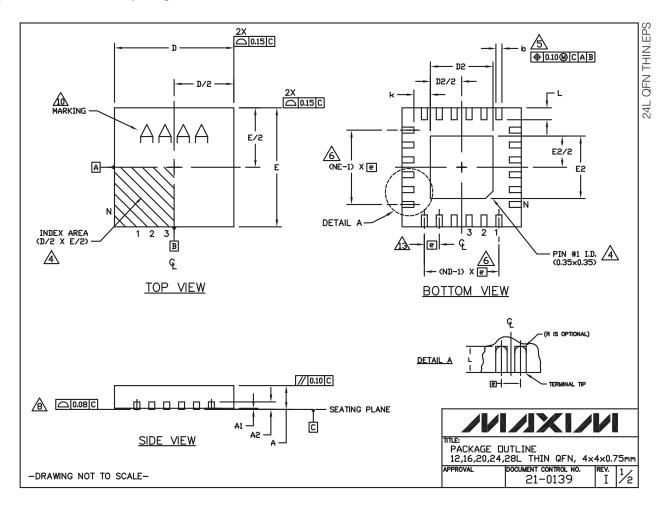

| MAX3302EETI    | 4 x 4                   | 28 TQFN-EP**    | T2844-1     |

| MAX3302EEWA+T  | 2.54 x 2.54             | 25 WLP          | W252A2-1    |

**Note:** All devices specified over the -40°C to +85°C operating

‡UCSP bumps are in a 5 x 5 array. The UCSP package size is 2.5mm x 2.5mm x 0.62mm. Requires solder temperature profile described in the Absolute Maximum Ratings section. UCSP reliability is integrally linked to the user's assembly methods, circuit board material and environment. See the UCSP Applications Information section of this data sheet for more information.

\*Future product—contact factory for availability.

T = Tape and reel.

+Denotes a lead-free package.

Pin Configurations appear at end of data sheet.

<sup>\*\*</sup>EP = Exposed paddle.

### **ABSOLUTE MAXIMUM RATINGS**

| All voltages are referenced to GND.                    |                                    |

|--------------------------------------------------------|------------------------------------|

| VCC, VL                                                | 0.3V to +6V                        |

| TRM (regulator off or supplied by V <sub>BUS</sub> )0. | $3V \text{ to } (V_{BUS} + 0.3V)$  |

| TRM (regulator supplied by V <sub>CC</sub> )C          |                                    |

| D+, D- (transmitter tri-stated)                        |                                    |

| D+, D- (transmitter functional)0                       | 0.3V to $(V_{CC} + 0.3V)$          |

| V <sub>BUS</sub>                                       | 0.3V to +6V                        |

| ID_IN, SCL, SDA                                        | 0.3V to +6V                        |

| ĪNT, SPD, RESET, ADD, OE/ĪNT, RCV, VP,                 |                                    |

| VM, SUS, DAT_VP, SE0_VM                                | $-0.3V$ to $(V_L + 0.3V)$          |

| C+0.                                                   | $.3V \text{ to } (V_{BUS} + 0.3V)$ |

| CC                                                     | 0.3V  to  (VCC + 0.3V)             |

| Short-Circuit Duration, V <sub>BUS</sub> to GND        | Continuous                         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-------------------------------------------------------|

| 25-Bump WLP (derate 12.2mW/°C above +70°C)976mW       |

| 25-Bump UCSP (derate 12.2mW/°C above +70°C)976mW      |

| 32-Pin TQFN (5mm x 5mm x 0.8mm) (derate 21.3mW/°C     |

| above +70°C)1702mW                                    |

| 28-Pin TQFN (4mm x 4mm x 0.8mm) (derate 20.8mW/°C     |

| above +70°C)1666mW                                    |

| Operating Temperature Range40°C to +85°C              |

| Junction Temperature+150°C                            |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

| Bump Reflow Temperature (Note 1)                      |

| Infrared (15s)+200°C                                  |

| Vapor Phase (20s)+215°C                               |

**Note 1:** The UCSP package is constructed using a unique set of packaging techniques that impose a limit on the thermal profile the device can be exposed to during board-level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification, JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3V \text{ to } +4.5V, \ V_L = +1.65V \text{ to } +3.6V, \ C_{FLYING} = 100 \text{nF}, \ C_{VBUS} = 1 \mu\text{F}, \ ESR_{CVBUS} = 0.1 \Omega \ (max), \ T_A = T_{MIN} \text{ to } T_{MAX}, \ unless otherwise noted. Typical values are at $V_{CC} = +3.7V, \ V_L = +2.5V, \ T_A = +25^{\circ}C.$) (Note 2)$

| PARAMETER                                                        | SYMBOL           | CONDITIONS                                                     | MIN                  | TYP | MAX  | UNITS |

|------------------------------------------------------------------|------------------|----------------------------------------------------------------|----------------------|-----|------|-------|

| Supply Voltage                                                   | Vcc              |                                                                | 3.0                  |     | 4.5  | V     |

| TRM Output Voltage                                               | V <sub>TRM</sub> |                                                                | 3.0                  |     | 3.6  | V     |

| Logic Supply Voltage                                             | VL               |                                                                | 1.65                 |     | 3.60 | V     |

| V <sub>L</sub> Supply Current                                    | lyL              | I2C interface in steady state                                  |                      |     | 5    | μΑ    |

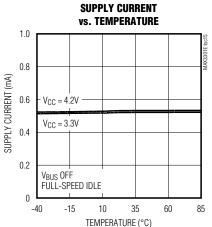

| V <sub>CC</sub> Operating Supply Current                         | Icc              | USB normal mode, $C_L = 50pF$ , device switching at full speed |                      |     | 10   | mA    |

| V <sub>CC</sub> Supply Current During Full-                      |                  | VvBus_DRV = 1, lvBus = 0                                       |                      | 1.4 | 2    | mA    |

| Speed Idle                                                       |                  | $V_{VBUS\_DRV} = 0$ , D+ = high, D- = low                      |                      | 0.5 | 0.8  | IIIA  |

| V <sub>CC</sub> Shutdown Supply Current                          | ICC(SHDN)        |                                                                |                      | 3.5 | 10   | μΑ    |

| V <sub>CC</sub> Interrupt Shutdown Supply<br>Current             | ICC(ISHDN)       | ID_IN unconnected or high                                      |                      | 20  | 30   | μΑ    |

| V <sub>CC</sub> Suspend Supply Current                           |                  | USB suspend mode, ID_IN unconnected or high                    |                      | 170 | 500  | μΑ    |

| LOGIC I/O                                                        |                  |                                                                |                      |     |      |       |

| RCV, DAT_VP, SE0_VM, INT, OE/INT, VP, VM Output High Voltage     | Voh              | I <sub>OUT</sub> = 1mA (sourcing)                              | V <sub>L</sub> - 0.4 |     |      | V     |

| RCV, DAT_VP, SE0_VM, INT, OE/INT, VP, VM Output Low Voltage      | V <sub>OL</sub>  | I <sub>OUT</sub> = 1mA (sinking)                               |                      |     | 0.4  | V     |

| OE/INT, SPD, SUS, RESET,<br>DAT_VP, SE0_VM Input High<br>Voltage | VIH              |                                                                | 2/3 x V <sub>L</sub> |     |      | V     |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3V \text{ to } +4.5V, \ V_L = +1.65V \text{ to } +3.6V, \ C_{FLYING} = 100 \text{nF}, \ C_{VBUS} = 1 \mu\text{F}, \ ESR_{CVBUS} = 0.1 \Omega \ (max), \ T_A = T_{MIN} \text{ to } T_{MAX}, \ unless otherwise noted. Typical values are at $V_{CC} = +3.7V, \ V_L = +2.5V, \ T_A = +25^{\circ}C.)$ (Note 2)$

| PARAMETER                                                      | SYMBOL            | CC                                   | ONDITIONS                            | MIN                  | TYP  | MAX                  | UNITS |

|----------------------------------------------------------------|-------------------|--------------------------------------|--------------------------------------|----------------------|------|----------------------|-------|

| OE/INT, SPD, SUS, RESET<br>DAT_VP, SE0_VM Input Low<br>Voltage | V <sub>IL</sub>   |                                      |                                      |                      |      | 0.4                  | V     |

| ADD Input High Voltage                                         | VIHA              |                                      |                                      | 2/3 x V <sub>L</sub> |      |                      | V     |

| ADD Input Low Voltage                                          | VILA              |                                      |                                      |                      |      | 1/3 x V <sub>L</sub> | V     |

| Input Leakage Current                                          |                   |                                      |                                      |                      | ±1   |                      | μΑ    |

| TRANSCEIVER SPECIFICATIONS                                     | 3                 |                                      |                                      |                      |      |                      |       |

| Differential Receiver Input<br>Sensitivity                     |                   | IV <sub>D+</sub> - V <sub>D-</sub> I |                                      | 0.2                  |      |                      | V     |

| Differential Receiver Common-<br>Mode Voltage                  |                   |                                      |                                      | 0.8                  |      | 2.5                  | V     |

| Single-Ended Receiver Input Low Voltage                        | VILD              | D+, D-                               |                                      |                      |      | 0.8                  | V     |

| Single-Ended Receiver Input<br>High Voltage                    | V <sub>IHD</sub>  | D+, D-                               |                                      | 2.0                  |      |                      | V     |

| Single-Ended Receiver Hysteresis                               |                   |                                      |                                      |                      | 0.2  |                      | V     |

| Single-Ended Output Low Voltage                                | V <sub>OLD</sub>  | $D+$ , $D-$ , $R_L = 1.5kg$          | $\Omega$ from D+ or D- to 3.6V       |                      |      | 0.3                  | V     |

| Single-Ended Output High Voltage                               | V <sub>OHD</sub>  | D+, D-, $R_L = 15k\Omega$            | 2 from D+ or D- to GND               | 2.8                  |      | 3.6                  | V     |

| Off-State Leakage Current                                      |                   | D+, D-                               |                                      |                      |      | ±1                   | μΑ    |

| Driver Output Impedance                                        |                   | D+, D-, not                          | Low steady-state drive               | 2                    |      | 13                   | Ω     |

| · · ·                                                          |                   | including REXT                       | High steady-state drive              | 2                    |      | 13                   | uu.   |

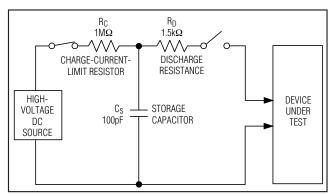

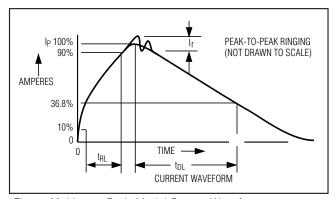

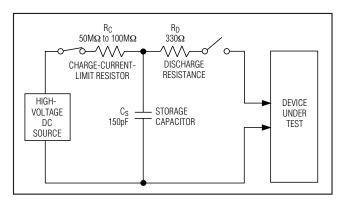

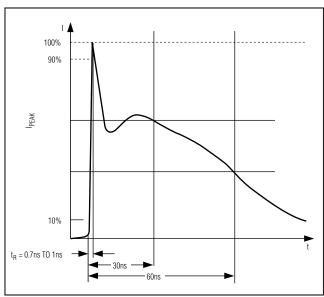

| ESD PROTECTION (V <sub>BUS</sub> , ID_IN,                      | D+, D-)           | 1                                    |                                      |                      |      |                      |       |

| Human Body Model                                               |                   |                                      |                                      |                      | ±15  |                      | kV    |

| IEC 61000-4-2 Air-Gap Discharge                                |                   |                                      |                                      |                      | ±10  |                      | kV    |

| IEC 61000-4-2 Contact Discharge                                |                   |                                      |                                      |                      | ±6   |                      | kV    |

| THERMAL SHUTDOWN                                               | 1                 | 1                                    |                                      |                      |      | -                    |       |

| Thermal Shutdown Low-to-High                                   |                   |                                      |                                      |                      | +160 |                      | °C    |

| Thermal Shutdown High-to-Low                                   |                   |                                      |                                      |                      | +150 |                      | °C    |

| CHARGE-PUMP SPECIFICATION                                      | S (vbus_drv       | 1                                    |                                      | T                    |      | -                    |       |

| V <sub>BUS</sub> Output Voltage                                | V <sub>BUS</sub>  | 3V < V <sub>CC</sub> < 4.5V, C       | VBUS = 10μF, I <sub>VBUS</sub> = 8mA | 4.80                 |      | 5.25                 | V     |

| V <sub>BUS</sub> Output Current                                | I <sub>VBUS</sub> |                                      |                                      | 8                    |      |                      | mA    |

| V <sub>BUS</sub> Output Ripple                                 |                   | $I_{VBUS} = 8mA, C_{VB}$             | BUS = 10μF                           |                      | 100  |                      | mV    |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC}=+3V\ to\ +4.5V,\ V_L=+1.65V\ to\ +3.6V,\ C_{FLYING}=100nF,\ C_{VBUS}=1\mu F,\ ESR_{CVBUS}=0.1\Omega\ (max),\ T_A=T_{MIN}\ to\ T_{MAX},\ unless otherwise noted.$  Typical values are at  $V_{CC}=+3.7V,\ V_L=+2.5V,\ T_A=+25^{\circ}C.)$  (Note 2)

| PARAMETER                                    | SYMBOL                        | CONDITIONS                                                                  | MIN                       | TYP | MAX                       | UNITS |

|----------------------------------------------|-------------------------------|-----------------------------------------------------------------------------|---------------------------|-----|---------------------------|-------|

| Switching Frequency                          | fsw                           |                                                                             |                           | 390 |                           | kHz   |

| V <sub>BUS</sub> Leakage Voltage             |                               | V <sub>VBUS_DRV</sub> = 0                                                   |                           |     | 0.2                       | V     |

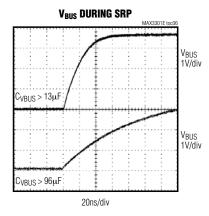

| V <sub>BUS</sub> Rise Time                   |                               | C <sub>VBUS</sub> = 10µF, I <sub>VBUS</sub> = 8mA, measured from 0 to +4.4V |                           |     | 100                       | ms    |

| V <sub>BUS</sub> Pulldown Resistance         |                               | VVBUS_DISCHRG = 1, VVBUS_DRV = 0,<br>VVBUS_CHRG = 0                         | 3.8                       | 5   | 6.5                       | kΩ    |

| V <sub>BUS</sub> Pullup Resistance           |                               | VvBUS_CHRG = 1, VvBUS_DRV = 0,<br>VvBUS_DISCHRG = 0                         | 650                       | 930 | 1250                      | Ω     |

| V <sub>BUS</sub> Input Impedance             | Z <sub>INVBUS</sub>           | VVBUS_DISCHRG = 0, VVBUS_DRV = 0,<br>VVBUS_CHRG = 0                         | 40                        | 70  | 100                       | kΩ    |

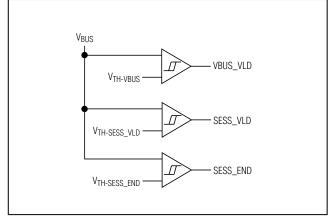

| COMPARATOR SPECIFICATIONS                    | S                             |                                                                             |                           |     |                           |       |

| V <sub>BUS</sub> Valid Comparator Threshold  | V <sub>TH-VBUS</sub>          |                                                                             | 4.4                       | 4.6 | 4.8                       | V     |

| V <sub>BUS</sub> Valid Comparator Hysteresis | V <sub>H</sub> YS-VBUS        |                                                                             |                           | 50  |                           | mV    |

| Session-Valid Comparator<br>Threshold        | V <sub>TH</sub> -<br>SESS_VLD |                                                                             | 0.8                       | 1.4 | 2.0                       | V     |

| Session-End Comparator<br>Threshold          | V <sub>TH</sub> -<br>SESS_END |                                                                             | 0.2                       | 0.5 | 0.8                       | V     |

| dp_hi Comparator Threshold                   |                               |                                                                             | 0.8                       | 1.3 | 2.0                       | V     |

| dm_hi Comparator Threshold                   |                               |                                                                             | 0.8                       | 1.3 | 2.0                       | V     |

| cr_int Pulse Width                           |                               |                                                                             |                           | 750 |                           | ns    |

| cr_int Comparator Threshold                  |                               |                                                                             | 0.4                       | 0.5 | 0.6                       | V     |

| ID_IN SPECIFICATIONS                         |                               |                                                                             |                           |     |                           |       |

| ID_IN Input Voltage for Car Kit              |                               |                                                                             | 0.2 x<br>V <sub>C</sub> C |     | 0.8 x<br>V <sub>C</sub> C | V     |

| ID_IN Input Voltage for A Device             |                               |                                                                             |                           |     | 0.1 x<br>V <sub>C</sub> C | V     |

| ID_IN Input Voltage for B Device             |                               |                                                                             | 0.9 x<br>V <sub>C</sub> C |     |                           | V     |

| ID_IN Input Impedance                        | Z <sub>ID_IN</sub>            |                                                                             | 70                        | 100 | 130                       | kΩ    |

| ID_IN Input Leakage Current                  |                               | ID_IN = V <sub>CC</sub>                                                     | -1                        |     | +1                        | μΑ    |

| ID_IN Pulldown Resistance                    |                               | id_pulldown = 1                                                             |                           | 150 | 300                       | Ω     |

| TERMINATING RESISTOR SPEC                    | FICATIONS                     | (D+, D-)                                                                    | •                         |     |                           |       |

| D+ Pulldown Resistor                         |                               | dp_pulldown = 1                                                             | 14.25                     | 15  | 15.75                     | kΩ    |

| D- Pulldown Resistor                         |                               | dm_pulldown = 1                                                             | 14.25                     | 15  | 15.75                     | kΩ    |

| D+ Pullup Resistor                           |                               | dp_pullup = 1                                                               | 1.425                     | 1.5 | 1.575                     | kΩ    |

| D- Pullup Resistor                           |                               | dm_pullup = 1                                                               | 1.425                     | 1.5 | 1.575                     | kΩ    |

### TIMING CHARACTERISTICS

$(V_{CC} = +3V \text{ to } +4.5V, \ V_L = +1.65V \text{ to } +3.6V, \ C_{FLYING} = 100nF, \ C_{VBUS} = 1\mu F, \ ESR_{CVBUS} = 0.1\Omega \ (max), \ T_A = T_{MIN} \text{ to } T_{MAX}, \ unless otherwise noted.}$

| PARAMETER                                  | SYMBOL             | CONDITIONS                                  | MIN        | TYP       | MAX         | UNITS |

|--------------------------------------------|--------------------|---------------------------------------------|------------|-----------|-------------|-------|

| TRANSMITTER CHARACTERIST                   | ICS (FULL-S        |                                             | I          |           |             |       |

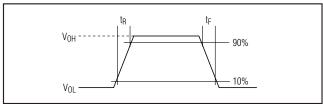

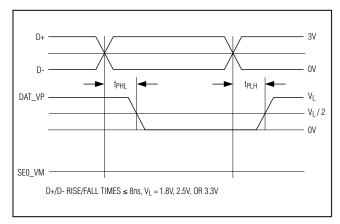

| D+, D- Rise Time                           | t <sub>R</sub>     | Figures 2 and 5                             | 4          |           | 20          | ns    |

| D+, D- Fall Time                           | t⊨                 | Figures 2 and 5                             | 4          |           | 20          | ns    |

| Rise-/Fall-Time Matching                   |                    | Figures 2 and 5 (Note 3)                    | 90         |           | 110         | %     |

| Output-Signal Crossover Voltage            | V <sub>CRS_F</sub> | Figures 2, 6, and 7 (Note 3)                | 1.3        |           | 2.0         | V     |

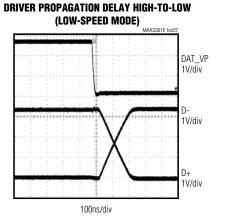

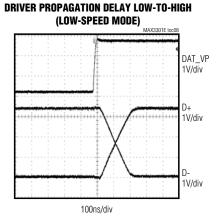

| TRANSMITTER CHARACTERIST                   | ICS (LOW-SI        | PEED MODE)                                  |            |           |             |       |

| D+, D- Rise Time                           | t <sub>R</sub>     | Figures 2 and 5                             | 75         |           | 300         | ns    |

| D+, D- Fall Time                           | tF                 | Figures 2 and 5                             | 75         |           | 300         | ns    |

| Rise-/Fall-Time Matching                   |                    | Figures 2 and 5                             | 80         |           | 125         | %     |

| Output-Signal Crossover Voltage            | V <sub>CRS_L</sub> | Figures 2, 6, and 7                         | 1.3        |           | 2.0         | V     |

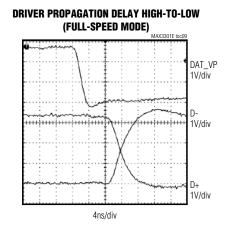

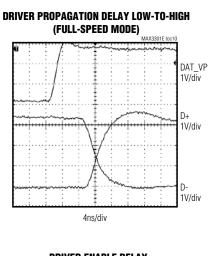

| TRANSMITTER TIMING (FULL-SF                | PEED MODE          | )                                           |            |           |             |       |

| Driver Propagation Delay                   | tpLH               | Low-to-high, Figures 2 and 6                |            |           | 25          |       |

| (DAT_VP, SE0_VM to D+, D-)                 | t <sub>PHL</sub>   | High-to-low, Figures 2 and 6                |            |           | 25          | ns    |

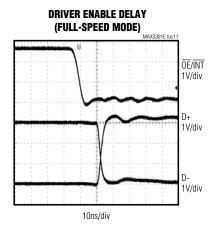

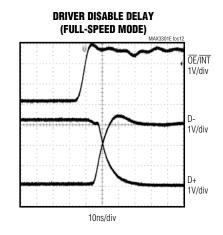

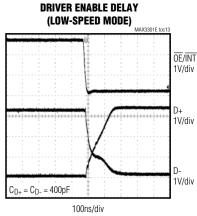

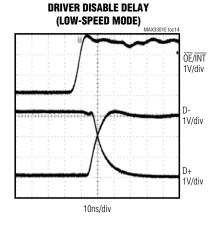

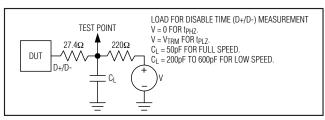

| Driver Disable Delay                       | tpdz               | Figures 1 and 8                             |            |           | 25          | ns    |

| Driver Enable Delay                        | tpzD               | Figures 2 and 8                             |            |           | 25          | ns    |

| TRANSMITTER TIMING (LOW-SP                 | EED MODE)          | (Low-speed delay timing is dominated by the | ne slow ri | se and fa | all times.) |       |

| SPEED-INDEPENDENT TIMING O                 | HARACTER           | ISTICS                                      |            |           |             |       |

| Receiver Disable Delay                     | tpvz               | Figure 4                                    |            |           | 30          | ns    |

| Receiver Enable Delay                      | tpzv               | Figure 4                                    |            |           | 30          | ns    |

| D+ Pullup Assertion Time                   |                    | During HNP                                  |            |           | 3           | μs    |

| RCV Rise Time                              | t <sub>R</sub>     | Figures 3 and 5, C <sub>L</sub> = 15pF      |            | 4         |             | ns    |

| RCV Fall Time                              | t⊨                 | Figures 3 and 5, C <sub>L</sub> = 15pF      |            | 4         |             | ns    |

| Differential-Receiver Propagation          | to to              | Figures 3 and 10, ID+ - D-I to DAT_VP       |            |           | 30          | 20    |

| Delay                                      | tphL, tpLH         | Figures 3 and 9, ID+ - D-I to RCV           |            |           | 30          | ns    |

| Single-Ended-Receiver<br>Propagation Delay | tphL, tpLH         | Figures 3 and 9, D+, D- to DAT_VP, SE0_VM   |            |           | 30          | ns    |

| Interrupt Propagation Delay                |                    |                                             |            |           | 100         | μs    |

| VBUS_CHRG Propagation Delay                |                    | Dominated by the V <sub>BUS</sub> rise time |            | 0.2       |             | μs    |

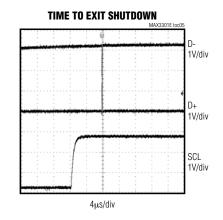

| Time to Exit Shutdown                      |                    |                                             |            |           | 1           | μs    |

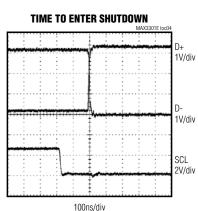

| Shutdown Delay                             |                    |                                             |            |           | 10          | μs    |

|                                            |                    | •                                           |            |           |             |       |

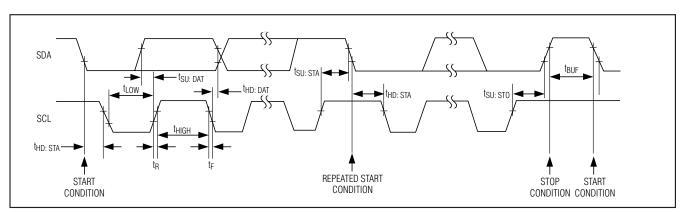

### I<sup>2</sup>C-/SMBus™-COMPATIBLE TIMING SPECIFICATIONS

$(V_{CC} = +3V \text{ to } +4.5V, V_L = +1.65V \text{ to } +3.6V, C_{FLYING} = 100nF, C_{VBUS} = 1\mu F, ESR_{CVBUS} = 0.1\Omega \text{ (max)}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.7V, V_L = +2.5V, T_A = +25^{\circ}C.) \text{ (Note 2)}$

| PARAMETER                                       | SYMBOL          | CONDITIONS                                                          | MIN                             | TYP | MAX                     | UNITS |

|-------------------------------------------------|-----------------|---------------------------------------------------------------------|---------------------------------|-----|-------------------------|-------|

| Serial Clock Frequency                          | fscl            |                                                                     |                                 |     | 400                     | kHz   |

| Bus-Free Time Between Stop and Start Conditions | tBUF            |                                                                     | 1.3                             |     |                         | μs    |

| Start-Condition Hold Time                       | tHD_STA         |                                                                     | 0.6                             |     |                         | μs    |

| Stop-Condition Setup Time                       | tsu_sto         |                                                                     | 0.6                             |     |                         | μs    |

| Clock Low Period                                | tLOW            |                                                                     | 1.3                             |     |                         | μs    |

| Clock High Period                               | thigh           |                                                                     | 0.6                             |     |                         | μs    |

| Data Setup Time                                 | tsu_dat         |                                                                     | 100                             |     |                         | ns    |

| Data Hold Time                                  | thd_dat         | (Note 4)                                                            |                                 |     | 0.9                     | μs    |

| Rise Time of SDA and SCL                        | t <sub>R</sub>  | (Note 5)                                                            | 20 +<br>0.1 x<br>C <sub>B</sub> |     | 300                     | ns    |

| Fall Time of SDA and SCL                        | t <sub>F</sub>  | Measured from 0.3 x V <sub>L</sub> to 0.7 x V <sub>L</sub> (Note 5) |                                 |     | 300                     | ns    |

| Capacitive Load for each Bus Line               | Св              |                                                                     |                                 |     | 400                     | pF    |

| SDA AND SCL I/O STAGE CHARA                     | ACTERISTIC      | S                                                                   |                                 |     |                         |       |

| Input-Voltage Low                               | V <sub>IL</sub> |                                                                     |                                 |     | 0.3 x<br>V <sub>L</sub> | V     |

| Input-Voltage High                              | VIH             |                                                                     | 0.7 x<br>VL                     |     |                         | V     |

| SDA Output-Voltage Low                          | V <sub>OL</sub> | I <sub>SINK</sub> = 3mA                                             |                                 |     | 0.4                     | V     |

| Pulse Width of Suppressed Spike                 | t <sub>SP</sub> | (Note 6)                                                            |                                 | 50  |                         | ns    |

- **Note 2:** Parameters are 100% production tested at +25°C. Limits over temperature are guaranteed by design.

- **Note 3:** Guaranteed by bench characterization. Limits are not production tested.

- Note 4: A master device must provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of SCL's falling edge.

- **Note 5:**  $C_B$  is the total capacitance of one bus line in pF, tested with  $C_B = 400$  pF.

- Note 6: Input filters on SDA, SCL, and ADD suppress noise spikes of less than 50ns.

SMBus is a trademark of Intel Corporation.

# MAX3301E/MAX3302E

# **USB On-the-Go Transceivers and Charge Pumps**

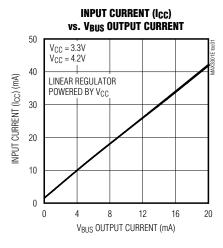

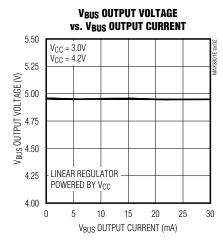

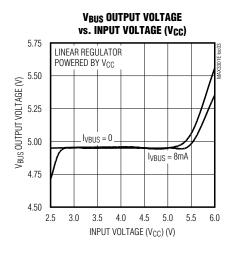

### Typical Operating Characteristics

(Typical operating circuit,  $V_{CC} = +3.7V$ ,  $V_{L} = +2.5V$ ,  $C_{FLYING} = 100nF$ ,  $T_{A} = +25^{\circ}C$ , unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Typical operating circuit, V<sub>CC</sub> = +3.7V, V<sub>L</sub> = +2.5V, C<sub>FLYING</sub> = 100nF, T<sub>A</sub> = +25°C, unless otherwise noted.)

# Pin Description

|                         | PIN                        |              |        | ME ELINCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-------------------------|----------------------------|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MAX3302E<br>28-PIN TQFN | MAX3301E<br>32-PIN TQFN    | UCSP/<br>WLP | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 1                       | 2                          | D2           | DAT_VP | System-Side Data Input/Output. DAT_VP is an input if OE/INT is logic 0. DAT_VP is an output if OE/INT is logic 1. Program the function of DAT_VP with the dat_se0 bit (bit 2 of control register 1, see Table 7).                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 2, 25                   | 3, 29                      | D1, E3       | Vcc    | Input Power Supply. Connect a +3V to +4.5V supply to $V_{CC}$ and bypass to GND with a 1 $\mu$ F capacitor. The supply range enables direct powering from one Li+ battery.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 3, 9, 23                | 1, 4, 9, 12, 17,<br>25, 28 | _            | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 4                       | 5                          | C1           | C-     | Charge-Pump Flying-Capacitor Negative Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 5                       | 6                          | C2           | SE0_VM | System-Side Data Input/Output. SE0_VM is an input if OE/INT is logic 0. SE0_VM is an output if OE/INT is logic 1. Program the function of SE0_VM with the dat_se0 bit (bit 2 of control register 1, see Table 7).                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 6, 18                   | 7, 21                      | B1, C5       | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 7                       | 8                          | A1           | SDA    | I2C-Compatible Serial Data Interface. Open-drain data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 8                       | 10                         | B2           | SCL    | I2C-Compatible Serial Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 10                      | 11                         | A2           | OE/INT | Output Enable. OE/INT controls the input or output status of DAT_VP/SE0_VM and D+/D When OE/INT is logic 0, the device is in transmit mode. When OE/INT is logic 1, the device is in receive mode. When in suspend mode, OE/INT can be programmed to function as an interrupt output that detects the same interrupts as INT. The oe_int_en bit (bit 5 of control register 1, see Table 7) enables and disables the interrupt circuitry of OE/INT. The irq_mode bit (bit 1 of special-function register 2, see Table 15) programs the output configuration of INT and OE/INT as open-drain or push-pull. |  |  |  |  |

| 11                      | 13                         | А3           | RCV    | D+ and D- Differential Receiver Output. In receive mode (see Table 4), when D+ is high and D- is low, RCV is high. In receive mode, when D+ is low and D- is high, RCV is low. RCV is low in suspend mode.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 12                      | 14                         | ВЗ           | SPD    | Speed-Selector Input. Connect SPD to GND to select the low-speed data rate (1.5Mbps). Connect SPD to $V_L$ to select the full-speed data rate (12Mbps). Disable the SPD input by writing a 1 to spd_susp_ctl (bit 1 in special-function register 1, see Table 14). The speed bit (bit 0 of control register 1, see Table 7) determines the maximum data rate of the MAX3301E/MAX3302E when the SPD input is disabled.                                                                                                                                                                                    |  |  |  |  |

| 13                      | 15                         | A4           | VL     | System-Side Logic-Supply Input. Connect to the system's logic-level power supply, +1.65V to +3.6V. This sets the maximum output levels of the logic outputs and the input thresholds of the logic inputs. Bypass to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 14                      | 16                         | A5           | SUS    | Active-High Suspend Input. Drive SUS low for normal USB operation. Drive SUS high to enable suspend mode. RCV asserts low in suspend mode. Disable the SUS input by writing a 1 to spd_susp_ctl (bit 1 in special-function register 1, see Table 14). The suspend bit (bit 1 of control register 1, see Table 7) determines the operating mode of the MAX3301E/MAX3302E when the SUS input is disabled.                                                                                                                                                                                                  |  |  |  |  |

### Pin Description (continued)

|                         | PIN                     |              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-------------------------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX3302E<br>28-PIN TQFN | MAX3301E<br>32-PIN TQFN | UCSP/<br>WLP | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15                      | 18                      | B4           | ĪNT              | Active-Low Interrupt Source. Program the INT output as push-pull or opendrain with the irq_mode bit (bit 1 of special-function register 2, see Tables 15 and 16).                                                                                                                                                                                                                                                                                                                                                        |

| 16                      | 19                      | B5           | RESET            | Active-Low Reset Input. Drive RESET low to asynchronously reset the MAX3301E/MAX3302E.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17                      | 20                      | C3           | ADD              | I2C-Interface Address Selection Input. (See Table 5.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19                      | 22                      | C4           | ID_IN            | ID Input. ID_IN is internally pulled up to V <sub>CC</sub> . The state of ID_IN determines ID bits 3 and 5 of the interrupt source register (see Table 10).                                                                                                                                                                                                                                                                                                                                                              |

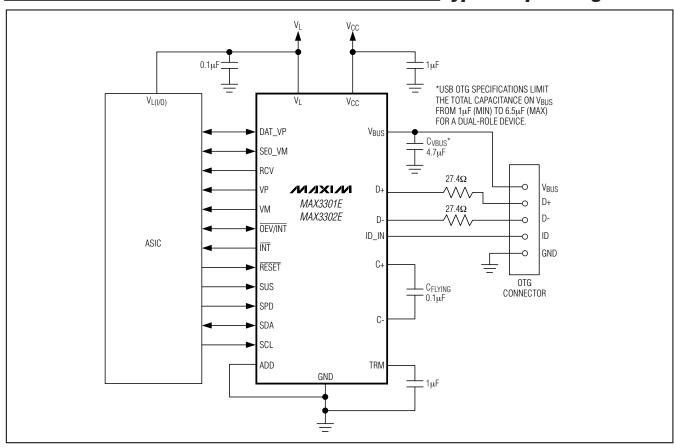

| 20                      | 23                      | D5           | D-               | USB Differential Data Input/Output. Connect D- to the D- terminal of the USB connector through a $27.4\Omega \pm 1\%$ series resistor.                                                                                                                                                                                                                                                                                                                                                                                   |

| 21                      | 24                      | E5           | D+               | USB Differential Data Input/Output. Connect D+ to the D+ terminal of the USB connector through a $27.4\Omega \pm 1\%$ series resistor.                                                                                                                                                                                                                                                                                                                                                                                   |

| 22                      | 26                      | D4           | VM               | Single-Ended Receiver Output. VM functions as a receiver output in all operating modes. VM duplicates D                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24                      | 27                      | E4           | TRM              | USB Transceiver Regulated Output Voltage. TRM provides a regulated 3.3V output. Bypass TRM to GND with a 1µF ceramic capacitor installed as close to the device as possible. TRM normally derives power from V <sub>CC</sub> . TRM provides power to internal circuitry and provides the pullup voltage for the internal USB pullup resistor. Do not use TRM to power external circuitry. The reg_sel bit (bit 3 of special-function register 2, see Table 15 and Table 16) controls the TRM power source with software. |

| 26                      | 30                      | D3           | VP               | Single-Ended Receiver Output. VP functions as a receiver output in all operating modes. VP duplicates D+.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27                      | 31                      | E2           | V <sub>BUS</sub> | USB Bus Power. Use V <sub>BUS</sub> as an output to power the USB bus, or as an input to power the internal linear regulator. Bits 5 to 7 of control register 2 (see Table 8) control the charging and discharging functions of V <sub>BUS</sub> .                                                                                                                                                                                                                                                                       |

| 28                      | 32                      | E1           | C+               | Charge-Pump Flying-Capacitor Positive Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EP                      | EP                      | _            | EP               | Exposed Paddle. Connect EP to GND or leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Test Circuits and Timing Diagrams

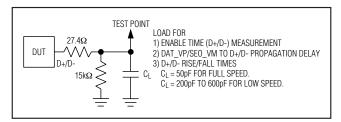

Figure 1. Load for Disable Time Measurement

Figure 2. Load for Enable Time, Transmitter Propagation Delay, and Transmitter Rise/Fall Times

N/IX/N/ \_\_\_\_\_\_ /N/IX/N/

### **Test Circuits and Timing Diagrams (continued)**

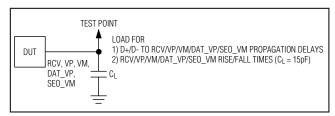

Figure 3. Load for Receiver Propagation Delay and Receiver Rise/Fall Times

Figure 4. Load for DAT\_VP, SE0\_VM Enable/Disable Time Measurements

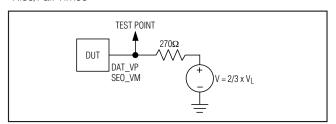

Figure 5. Rise and Fall Times

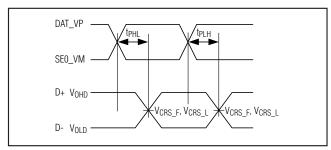

Figure 6. Timing of DAT\_VP, SE0\_VM to D+, D- in VP\_VM Mode (dat\_se0 = 0)

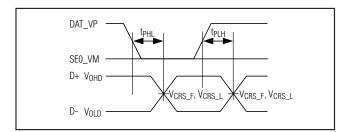

Figure 7. Timing of DAT\_VP, SE0\_VM to D+/D- in DAT\_SE0 Mode (dat\_se0 = 1)

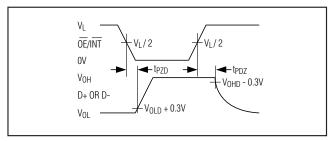

Figure 8. Enable and Disable Timing

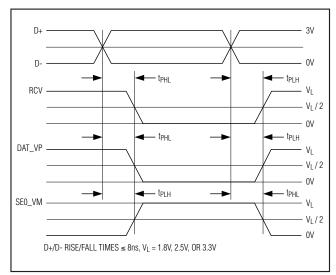

Figure 9. D+/D- to RCV, DAT\_VP, SE0\_VM Propagation Delays (VP\_VM Mode)

Figure 10. D+/D- to DAT\_VP, SE0\_VM Propagation Delays (DAT\_SE0 Mode)

### **Block Diagram** ID\_IN DETECTOR ADD -C+ V<sub>BUS</sub> CHARGE PUMP - C-ĪNT -SERIAL CONTROLLER RESET V<sub>BUS</sub> COMPARATORS - V<sub>BUS</sub> LINEAR - TRM REGULATOR SCL -PULLUP/PULLDOWN RESISTORS SDA -CAR KIT INTERRUPT DETECTOR DAT\_VP -– D+ SE0\_VM -DIFF TX OE/INT -– D-VM -DIFF LEVEL RCV -TRANSLATOR V<sub>CC</sub> -POWER V<sub>L</sub> -**BLOCK** GND -SPD -MIXIM SUS -MAX3301E MAX3302E

Figure 11. Block Diagram

### **Detailed Description**

The USB OTG specification defines a dual-role USB device that acts either as an A device or as a B device. The A device supplies power on VBUS and initially serves as the USB host. The B device serves as the initial peripheral and requires circuitry to monitor and pulse VBUS. These initial roles can be reversed using HNP.

The MAX3301E/MAX3302E combine a low- and full-speed USB transceiver with additional circuitry required by a dual-role device. The MAX3301E/MAX3302E employ flexible switching circuitry to enable the device to act as a dedicated host or peripheral USB transceiver. For example, the charge pump can be turned off and the internal regulator can be powered from VBUS for bus-powered peripheral applications.

The Selector Guide shows the differences between the MAX3301E and MAX3302E. The MAX3301E powers up in its lowest power state and must be turned on by setting the sdwn bit to 0. The MAX3302E powers up in the operational, VP/VM USB mode. This allows a microprocessor (µP) to use the USB port for power-on bootup, without having to access I<sup>2</sup>C. To put the MAX3302E into low-power shutdown, set the sdwn bit to 0. In the MAX3302E, special-function register 2 can be addressed at I<sup>2</sup>C register location 10h, 11h (as well as locations 16h, 17h) to support USB OTG serial-interface engine (SIE) implementations that are limited to I<sup>2</sup>C register addresses between 0h and 15h.

### **Transceiver**

The MAX3301E/MAX3302E transceiver complies with the USB version 2.0 specification, and operates at full-speed (12Mbps) and low-speed (1.5Mbps) data rates. Set the data rate with the SPD input. Set the direction of data transfer with the OE/INT input. Alternatively, control transceiver operation with control register 1 (Table 7) and special-function registers 1 and 2 (see Tables 14, 15, and 16).

### **Level Shifters**

Internal level shifters allow the system-side interface to run at logic-supply voltages as low as +1.65V. Interface logic signals are referenced to the voltage applied to the logic-supply voltage, V<sub>L</sub>.

### Charge Pump

The MAX3301E/MAX3302E's OTG-compliant charge pump operates with +3V to +4.5V input supply voltages (VCC) and supplies a +4.8V to +5.25V OTG-compatible output on VBUS while sourcing the 8mA or greater output current that an A device is required to supply. Connect a 0.1 $\mu$ F flying capacitor between C+ and C-. Bypass VBUS to GND with a 1 $\mu$ F to 6.5 $\mu$ F capacitor, in

accordance with USB OTG specifications. The charge pump can be turned off to conserve power when not used. Control of the charge pump is set through the vbus\_drv bit (bit 5) of control register 2 (see Table 8).

### **Linear Regulator (TRM)**

An internal 3.3V linear regulator powers the transceiver and the internal 1.5k $\Omega$  D+/D- pullup resistor. Under the control of internal register bits, the linear regulator can be powered from VCC or VBUS. The regulator power-supply settings are controlled by the reg\_sel bit (bit 3) in special-function register 2 (Tables 15 and 16). This flexibility allows the system designer to configure the MAX3301E/MAX3302E for virtually any USB power situation.

The output of the TRM is not a power supply. Do not use as a power source for any external circuitry. Connect a 1.0µF (or greater) ceramic or plastic capacitor from TRM to GND, as close to the device as possible.

### **VBUS Level-Detection Comparators**

Comparators drive interrupt source register bits 0, 1, and 7 (Table 10) to indicate important USB OTG V<sub>BUS</sub> voltage levels:

- VBUS is valid (vbus\_vld)

- USB session is valid (sess\_vld)

- USB session has ended (sess\_end)

The vbus\_valid comparator sets vbus\_vld to 1 if VBUS is higher than the VBUS valid comparator threshold. The VBUS valid status bit (vbus\_vld) is used by the A device to determine if the B device is sinking too much current (i.e., is not supported). The session\_valid comparator sets sess\_vld to 1 if VBUS is higher than the session valid comparator threshold. This status bit indicates that a data transfer session is valid. The session\_end comparator sets sess\_end to 1 if VBUS is higher than the

Figure 12. Comparator Network Diagram

session end comparator threshold. Figure 12 shows the level-detector comparators. The interrupt-enable registers (Tables 12 and 13) determine whether a falling or rising edge of VBUS asserts these status bits.

### ID IN

The USB OTG specification defines an ID input that determines which dual-role device is the default host. An OTG cable connects ID to ground in the connector of one end and is left unconnected in the other end. Whichever dual-role device receives the grounded end becomes the A device. The MAX3301E/MAX3302E provide an internal pullup resistor on ID\_IN. Internal comparators detect if ID IN is grounded or left floating.

### **Interrupt Logic**

When OTG events require action, the MAX3301E/MAX3302E provide an interrupt output signal on INT. Alternatively, OE/INT can be configured to act as an interrupt output while the device operates in USB suspend mode. Program INT and OE/INT as open-drain or push-pull interrupts with irq\_mode (bit 1 of special-function register 2, see Tables 15 and 16).

### **VBUS Power Control**

VBUS is a dual-function port that powers the USB bus and/or provides a power source for the internal linear regulator. The VBUS power-control block performs the various switching functions required by an OTG dual-role device. These actions are programmed by the system logic using bits 5 to 7 of control register 2 (see Table 8) to:

- Discharge VBUS through a resistor

- Provide power-on or receive power from VBUS

- Charge VBUS through a resistor

The OTG supplement allows an A device to turn VBUs off when the bus is not being used to conserve power. The B device can issue a request that a new session be started using SRP. The B device must discharge VBUS to a level below the session-end threshold (0.8V) to ensure that no session is in progress before initiating SRP. Setting bit 6 of control register 2 to 1, discharges VBUS to GND through a 5k $\Omega$  current-limiting resistor. When VBUS has discharged, the resistor is removed from the circuit by resetting bit 6 of control register 2.

An OTG A device is required to supply power on VBUS. The MAX3301E/MAX3302E provide power to VBUS from VCC or from the internal charge pump. Set bit 5 in control register 2 to 1 in both cases. Bit 5 in control register 2 controls a current-limited switch, preventing damage to the device in the event of a VBUS short circuit.

An OTG B device (peripheral mode) can request a session using SRP. One of the steps in implementing SRP requires pulsing VBUs high for a controlled time. A  $930\Omega$  resistor limits the current according to the OTG specification. Pulse VBUs through the pullup resistor by asserting bit 7 of control register 2. Prior to pulsing VBUs (bit 7), a B device first connects an internal pulldown resistor to discharge VBUS below the session-end threshold. The discharge current is limited by the  $5k\Omega$  resistor and set by bit 6 of control register 2. An OTG A device must

**Table 1. Functional Blocks Enabled During Specific Operating Modes**

|                                    |     |       |                  |                   | <b>J</b> 1        |                | 9             |               |     |    |            |          |

|------------------------------------|-----|-------|------------------|-------------------|-------------------|----------------|---------------|---------------|-----|----|------------|----------|

| MODE                               | I2C | ID_IN | sess_end<br>COMP | sess _vld<br>COMP | vbus_ vld<br>COMP | cr_int<br>COMP | dp_hi<br>COMP | dm_hi<br>COMP | TRM | тх | DIFF<br>RX | SE<br>RX |

| Shutdown <sup>1</sup>              | 1   | Χ     | Χ                | Χ                 | Χ                 | Χ              | Χ             | Χ             | Χ   | Χ  | Χ          | Χ        |

| Interrupt<br>Shutdown <sup>2</sup> | 1   | 1     | Х                | 1                 | X                 | Х              | 1             | 1             | Х   | X  | X          | Х        |

| Suspend <sup>3</sup>               | 1   | 1     | ✓                | ✓                 | ✓                 | ✓              | ✓             | 1             | 1   | /  | Χ          | /        |

| Normal<br>Operating                | 1   | 1     | 1                | 1                 | 1                 | 1              | 1             | 1             | 1   | 1  | <b>\</b>   | 1        |

<sup>✓ =</sup> Enabled.

- 1. For the MAX3301E, enter shutdown mode by writing a 1 to sdwn (bit 0 of special-function register 2). For the MAX3302E, enter shutdown mode by writing a 0 to sdwn (bit 0 of special-function register 2).

- 2. Enter interrupt shutdown mode by writing a 1 to int\_sdwn (bit 0 of special-function register 1).

- 3. Enter suspend mode by writing a 1 to spd\_susp\_ctl (bit 1 of special-function register 1) and suspend (bit 1 of control register 1), or by writing a 0 to spd\_susp\_ctl (bit 1 of special-function register 1) and driving SUS high.

X = Disabled.

supply 5V power and at least 8mA on V<sub>BUS</sub>. Setting bit 5 of control register 2 turns on the V<sub>BUS</sub> charge pump.

### **Operating Modes**

The MAX3301E/MAX3302E have four operating modes to optimize power consumption. Only the I<sup>2</sup>C interface remains active in shutdown mode, reducing supply current to 1µA. The I<sup>2</sup>C interface, the ID\_IN port, and the session-valid comparator all remain active in interrupt shutdown mode. RCV asserts low in suspend mode; however, all other circuitry remains active. Table 1 lists the active blocks' power in each of the operating modes.

### **Applications Information**

### **Data Transfer**

### Transmitting Data to the USB

The MAX3301E/MAX3302E transceiver features two modes of transmission: DAT\_SE0 or VP\_VM (see Table 3). Set the transmitting mode with dat\_se0 (bit 2 in control register 1, see Table 7). In DAT\_SE0 mode with OE/INT low, DAT\_VP specifies data for the differential transceiver, and SE0\_VM forces D+/D- to the single-ended zero (SE0) state. In VP\_VM mode with OE/INT low, DAT\_VP drives D+, and SE0\_VM drives D-. The differential receiver determines the state of RCV.

### Receiving Data from the USB

The MAX3301E/MAX3302E transceiver features two modes of receiving data: DAT\_SE0 or VP\_VM (see Table 4). Set the receiving mode with dat\_se0 (bit 2 in control register 1, see Table 7). In DAT\_SE0 mode with OE/INT high, DAT\_VP is the output of the differential receiver and SE0\_VM indicates that D+ and D- are both logic-low. In VP\_VM mode with OE/INT high, DAT\_VP provides the input logic level of D+ and SE0\_VM provides the input logic level of D-. The differential receiver determines the state of RCV. VP and VM echo D+ and D-, respectively.

### OE/INT

OE/INT controls the direction of communication. OE/INT can also be programmed to act as an interrupt output when in suspend mode. The output-enable portion controls the input or output status of DAT\_VP/SE0\_VM and D+/D-. When OE/INT is a logic 0, DAT\_VP and SE0\_VM function as inputs to the D+ and D- outputs in a method depending on the status of dat\_se0 (bit 2 in control register 1). When OE/INT is a logic 1, DAT\_VP and SE0\_VM indicate the activity of D+ and D-.

OE/INT functions as an interrupt output when the MAX3301E/MAX3302E is in suspend mode and oe\_int\_en = 1 (bit 5 in control register 1, see Table 7). In

this mode,  $\overline{OE/INT}$  detects the same interrupts as  $\overline{INT}$ . Set irq\_mode (bit 1 in special-function register 2, see Tables 15 and 16) to 0 to program  $\overline{OE/INT}$  as an opendrain interrupt output. Set irq\_mode to 1 to configure  $\overline{OE/INT}$  as a push-pull interrupt output.

### **RCV**

RCV monitors D+ and D- when receiving data. RCV is a logic 1 for D+ high and D- low. RCV is a logic 0 for D+ low and D- high. RCV retains its last valid state when D+ and D- are both low (single-ended zero, or SE0). RCV asserts low in suspend mode. Table 4 shows the state of RCV.

### **SPD**

Use hardware or software to control the slew rate of the D+ and D- terminals. The SPD input sets the slew rate of the MAX3301E/MAX3302E when spd\_susp\_ctl (bit 1 in special-function register 1, see Table 14) is 0. Drive SPD low to select low-speed mode (1.5Mbps). Drive SPD high to select full-speed mode (12Mbps). Alternatively, when spd\_susp\_ctl (bit 1 of special-function register 1) is 1, software controls the slew rate. The SPD input is ignored when using software to control the data rate. The speed bit (bit 0 of control register 1, see Table 7) sets the slew rate when spd\_susp\_ctl = 1.

### SUS

Use hardware or software to control the suspend mode of the MAX3301E/MAX3302E. Set spd\_susp\_ctl (bit 1 of special-function register 1, see Table 14) to 0 to allow the SUS input to enable and disable the suspend mode of the MAX3301E/MAX3302E. Drive SUS low for normal operation. Drive SUS high to enable suspend mode. RCV asserts low in suspend mode while all other circuitry remains active.

Alternatively, when the spd\_susp\_ctl bit (bit 1 of special-function register 1) is set to 1, software controls the suspend mode. Set the suspend bit (bit 1 of control register 1, see Table 7) to 1 to enable suspend mode. Set the suspend bit to 0 to resume normal operation. The SUS input is ignored when using software to control suspend mode. The MAX3301E/MAX3302E must be in full-speed mode (SPD = high or speed = 1) to issue a remote wake-up from the device when in suspend mode.

### **RESET**

The active-low RESET input allows the MAX3301E/MAX3302E to be asynchronously reset without cycling the power supply. Drive RESET low to reset the internal registers (see Tables 7–16 for the default power-up states). Drive RESET high for normal operation.

### 2-Wire I<sup>2</sup>C-Compatible Serial Interface

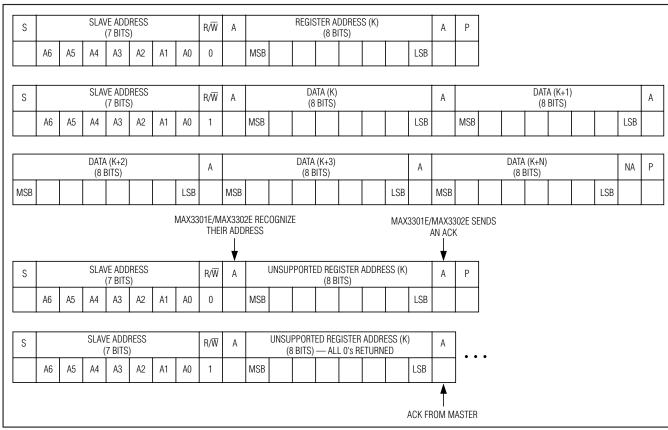

A register file controls the various internal switches and operating modes of the MAX3301E/MAX3302E through a simple 2-wire interface operating at clock rates up to 400kHz. This interface supports data bursting, where multiple data phases can follow a single address phase.

### **UART Mode**

Set uart\_en (bit 6 in control register 1) to 1 to place the MAX3301E/MAX3302E in UART mode. D+ transfers data to DAT\_VP and SE0\_VM transfers data to D- in UART mode.

### General-Purpose Buffer Mode

Set gp\_en (bit 7 in special-function register 1) and dat\_se0 (bit 2 in control register 1) to 1, set uart\_en (bit 6 in control register 1) to 0, and drive OE/INT low to place the MAX3301E/MAX3302E in general-purpose buffer mode. Control the direction of data transfer with dminus\_dir and dplus\_dir (bits 3 and 4 of special-function register 1, see Tables 2 and 14).

### Serial Addressing

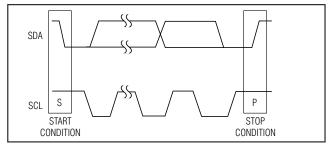

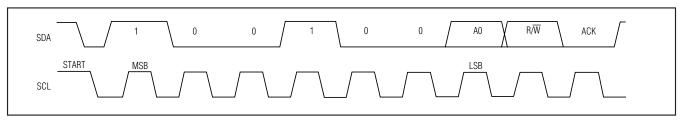

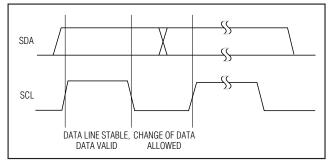

The MAX3301E/MAX3302E operate as a slave device that sends and receives control and status signals through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial data line (SDA) and a serial clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX3301E/MAX3302E and generates the SCL clock that synchronizes the data transfer (Figure 13).

The MAX3301E/MAX3302E SDA line operates as both an input and as an open-drain output. SDA requires a

Table 2. Setting the Direction of Data Transfer in General-Purpose Buffer Mode

| dplus_dir | dminus_ dir | DIRECTION OF DATA<br>TRANSFER                                   |

|-----------|-------------|-----------------------------------------------------------------|

| 0         | 0           | $\begin{array}{c} DAT\_VP \to D+ \\ SE0\_VM \to D- \end{array}$ |

| 0         | 1           | DAT_VP → D+<br>SE0_VM ← D-                                      |

| 1         | 0           | DAT_VP ← D+<br>SE0_VM → D-                                      |

| 1         | 1           | DAT_VP ← D+<br>SE0_VM ← D-                                      |

pullup resistor, typically  $4.7k\Omega$ . The MAX3301E/MAX3302E SCL line only operates as an input. SCL requires a pullup resistor if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output.

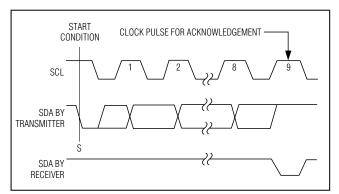

Each transmission consists of a start condition (see Figure 14) sent by a master device, the MAX3301E/MAX3302E 7-bit slave address (determined by the state of ADD), plus an R/W bit (see Figure 15), a register address byte, one or more data bytes, and a stop condition (see Figure 14).

Figure 13. 2-Wire Serial-Interface Timing Details

**Table 3. Transmit Mode**

| MODE                          |     | CONTR | OL PIN/BI | Т       | INF    | PUT    | ОИТ               | PUT               | DESCRIPTION                                       |

|-------------------------------|-----|-------|-----------|---------|--------|--------|-------------------|-------------------|---------------------------------------------------|

| WIODE                         | SUS | GP_EN | OE/INT    | DAT_SE0 | DAT_VP | SE0_VM | D+                | D-                | DESCRIPTION                                       |

|                               | 0   | 0     | 0         | 1       | 0      | 0      | 0                 | 1                 |                                                   |

| Functional                    | 0   | 0     | 0         | 1       | 1      | 0      | 1                 | 0                 |                                                   |

| DAT_SE0                       | 0   | 0     | 0         | 1       | 0      | 1      | 0                 | 0                 |                                                   |

|                               | 0   | 0     | 0         | 1       | 1      | 1      | 0                 | 0                 | USB functional mode transceiver and I2C interface |

|                               | 0   | 0     | 0         | 0       | 0      | 0      | 0                 | 0                 | are fully functional                              |

| Functional                    | 0   | 0     | 0         | 0       | 1      | 0      | 1                 | 0                 |                                                   |

| VP_VM                         | 0   | 0     | 0         | 0       | 0      | 1      | 0                 | 1                 |                                                   |

|                               | 0   | 0     | 0         | 0       | 1      | 1      | 1                 | 1                 |                                                   |

|                               | 1   | 0     | 0         | 1       | 0      | 0      | 0                 | 1                 |                                                   |

|                               | 1   | 0     | 0         | 1       | 1      | 0      | 1                 | 0                 |                                                   |

|                               | 1   | 0     | 0         | 1       | 0      | 1      | 0                 | 0                 |                                                   |

|                               | 1   | 0     | 0         | 1       | 1      | 1      | 0                 | 0                 |                                                   |

| Cuppond                       | 1   | 0     | 0         | 0       | 0      | 0      | 0                 | 0                 | LICD augnond made                                 |

| Suspend                       | 1   | 0     | 0         | 0       | 1      | 0      | 1                 | 0                 | - USB suspend mode                                |

|                               | 1   | 0     | 0         | 0       | 0      | 1      | 0                 | 1                 |                                                   |

|                               | 1   | 0     | 0         | 0       | 1      | 1      | 1                 | 1                 |                                                   |

|                               | 1   | 0     | 1         | Х       | Х      | Х      | Driver is<br>Hi-Z | Driver is<br>Hi-Z |                                                   |

| Receiving                     | 0   | 0     | 1         | Х       | Х      | Х      | Driver is<br>Hi-Z | Driver is<br>Hi-Z | See Table 4                                       |

| General-<br>purpose<br>buffer | Х   | 1     | 0         | 1       |        | See Ta | ble 2             |                   | General-purpose buffer mode                       |

Figure 14. Start and Stop Conditions

Figure 15. Slave Address

**Table 4. Receive Mode**

|                                         |                 | CON   | TROL PIN | /BIT    |       | INP | UTS |                      | ou     | TPUTS             |            |            |

|-----------------------------------------|-----------------|-------|----------|---------|-------|-----|-----|----------------------|--------|-------------------|------------|------------|

| MODE                                    | SUS<br>(NOTE 7) | GP_EN | OE/INT   | DAT_SE0 | BI_DI | D+  | D-  | DAT_VP               | SE0_VM | RCV               | VP         | VM         |

|                                         | 0               | 0     | 1        | 1       | 1     | 0   | 0   | Last value of DAT_VP | 1      | Last value of RCV |            |            |

|                                         | 0               | 0     | 1        | 1       | 1     | 1   | 0   | 1                    | 0      | 1                 |            |            |