#### **General Description**

The MAX3673 evaluation kit (EV kit) is a fully assembled and tested demonstration board that simplifies evaluation of the MAX3673 low-jitter frequency synthesizer with selectable input reference. The EV kit includes slide switches to allow easy selection of different modes of operation. Clock I/Os have SMA connectors and are AC-coupled to simplify connection to test equipment. The EV kit is powered by a +3.3V supply and uses LEDs for signal status indicators.

#### Features

- ♦ Fully Assembled and Tested

- **♦ Slide Switches for Mode Control**

- ♦ SMA Connectors and AC-Coupled Clock I/Os

- ♦ Powered by +3.3V Supply

- ♦ LED Signal Status Indicators

### **Ordering Information**

| PART          | TYPE   |

|---------------|--------|

| MAX3673EVKIT+ | EV Kit |

<sup>+</sup>Denotes lead(Pb)-free and RoHS compliant.

### **Component List**

| DESIGNATION                                                                                                    | QTY | DESCRIPTION                                                 |

|----------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------|

| C1, C6, C7<br>C11–C13, C16,<br>C18–C22,<br>C24–C27, C29,<br>C30, C32–C39,<br>C41, C42,<br>C46–C50,<br>C62, C63 | 35  | 0.1µF±10% ceramic capacitors (0402)                         |

| C2                                                                                                             | 1   | 33μF ±5% tantalum capacitor<br>(B case)                     |

| C3                                                                                                             | 1   | 2.2µF ±10% ceramic capacitor (0805)                         |

| C4                                                                                                             | 1   | 0.1µF ±10% ceramic capacitor (0603)                         |

| C5                                                                                                             | 1   | 0.01µF±10% ceramic capacitor (0603)                         |

| C28                                                                                                            | 1   | 0.22µF±10% ceramic capacitor (0402)                         |

| D1, D3, D8                                                                                                     | 3   | Green SMD LEDs (1206)<br>Panasonic LNJ311G8PRA              |

| D2, D4, D7                                                                                                     | 3   | Red SMD LEDs (1206)<br>Panasonic LNJ211R8ARA                |

| J1, J2,<br>J5–J12, J14,<br>J15, J19, J20,<br>J22–J29,<br>J44, J45                                              | 24  | SMA connectors, edge-mount, tab center Johnson 142-0701-851 |

| J4, J13                                                                                                        | 2   | Test points<br>Keystone 5000                                |

| L1                                                                                                             | 1   | 4.7µH ±20% inductor<br>Taiyo Yuden CBC3225T4R7M             |

| DESIGNATION                         | QTY | DESCRIPTION                                                                                       |

|-------------------------------------|-----|---------------------------------------------------------------------------------------------------|

| R1–R5, R15,<br>R16, R17,<br>R37–R46 | 18  | 150Ω ±1% resistors (0402)                                                                         |

| R6-R11                              | 6   | 49.9Ω ±1% resistors (0402)                                                                        |

| R12, R13, R14,<br>R18, R21, R22     | 6   | 332Ω ±1% resistors (0603)                                                                         |

| R23, R24, R25                       | 3   | 10kΩ ±1% resistors (0603)                                                                         |

| S1                                  | 1   | Switch, momentary, SPST-NO<br>Panasonic EVQQ2S02W                                                 |

| S2, S3, S5                          | 3   | Switches, slide, SPDT<br>Copal Electronics CUS-12TB                                               |

| S6, S7, S8                          | 3   | Switches, slide, SP4T<br>Copal Electronics CUS-14TB                                               |

| S9, S10                             | 2   | Switches, slide, SP3T<br>Copal Electronics CUS-13TB                                               |

| TP3, TP20                           | 2   | Test points<br>Keystone 5000                                                                      |

| U1, U2, U4                          | 3   | Dual inverters (6 SC-70)<br>TI SN74LVC2G14DCKR                                                    |

| U7                                  | 1   | Low-jitter, frequency synthesizer with selectable input reference (56 TQFN) Microsemi MAX3673ETN+ |

| None                                | 1   | PCB: MAX3673 EV Kit+ Circuit<br>Board, Rev A                                                      |

#### **Quick Start**

#### **Detailed Description**

1) Set the slide switches to the following settings:

PLL\_BYPASS = NORMAL

SEL\_CLK = REFCLK0

DM = 61.44M

DA = 122.88M

DB = 122.88M

$\overline{OUTA}_{EN} = A0, A1$

OUTB EN = B0

FB\_SEL = INTERNAL

- 2) Connect a +3.3V supply to VCC (J13) and GND (J4). Set the supply current limit to 450mA.

- 3) Using SMA cables, connect a low-jitter 61.44MHz differential clock source to the REFCLK<u>0</u> input. Verify that the green LEDs switch on for INOFAIL and LOCK.

- 4) Using SMA cables, connect the OUTA0 output to test equipment. Terminate all unused enabled outputs (OUTB0 and OUTA1).

The MAX3673 EV kit simplifies evaluation by providing the hardware needed to evaluate all the MAX3673 functions. Table 1 contains functional descriptions for the switches and indicators.

#### **Clock Inputs**

The clock inputs (REFCLK0, REFCLK1, FB\_IN) are AC-coupled at the SMA connectors and have on-board  $100\Omega$  differential terminations. For optimal jitter performance it is critical to use a low-jitter, differential, square-wave clock source. If such a source is not available, the clock inputs can be driven with a single-ended sinusoidal or square-wave clock source for functional testing.

#### **Clock Outputs**

The clock outputs (OUTA[3:0], OUTB[4:0]) have onboard DC-biasing and are AC-coupled at the SMA connectors to allow direct connection to  $50\Omega$ -terminated test equipment. Unused outputs should be disabled (using switches S9 and S10) or have  $50\Omega$  terminations placed on the SMA connectors.

**Table 1. Switch and Indicator Descriptions**

| COMPONENT | NAME         | FUNCTION                                                                                                                                                                                      |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1        | MASTER RESET | Momentary switch to reset internal dividers. Not required at power-up. If the output divider settings (DA, DB) are changed on the fly, a reset is required to phase align the outputs.        |

| S2        | PLL_BYPASS   | Selects normal PLL operation or PLL bypass.                                                                                                                                                   |

| S3        | SEL_CLK      | Selects the reference clock input.                                                                                                                                                            |

| S5        | FB_SEL       | Selects internal or external feedback for the PLL. If external is selected, connect any of the A-group or B-group outputs to the FB_IN input. If DA $\neq$ DB, a B-group output must be used. |

| S6        | DM           | Selects the frequency of the reference clock inputs.                                                                                                                                          |

| S7        | DA           | Selects the frequency of the A-group clock outputs.                                                                                                                                           |

| S8        | DB           | Selects the frequency of the B-group clock outputs.                                                                                                                                           |

| S9        | OUTA_EN      | Selects which A-group outputs are enabled (see Note).                                                                                                                                         |

| S10       | OUTB_EN      | Selects which B-group outputs are enabled (see Note).                                                                                                                                         |

| D1, D2    | INOFAIL      | REFCLK0 failure indicator (green = pass, red = fail).                                                                                                                                         |

| D3, D4    | ĪN1FAIL      | REFCLK1 failure indicator (green = pass, red = fail).                                                                                                                                         |

| D7, D8    | LOCK         | PLL lock indicator (green = PLL locked, red = PLL not locked).                                                                                                                                |

**Note:** Setting  $\overline{OUTA\_EN} =$  "—" and  $\overline{OUTB\_EN} =$  "B0" at the same time enables a factory test mode and is not a valid mode of operation.

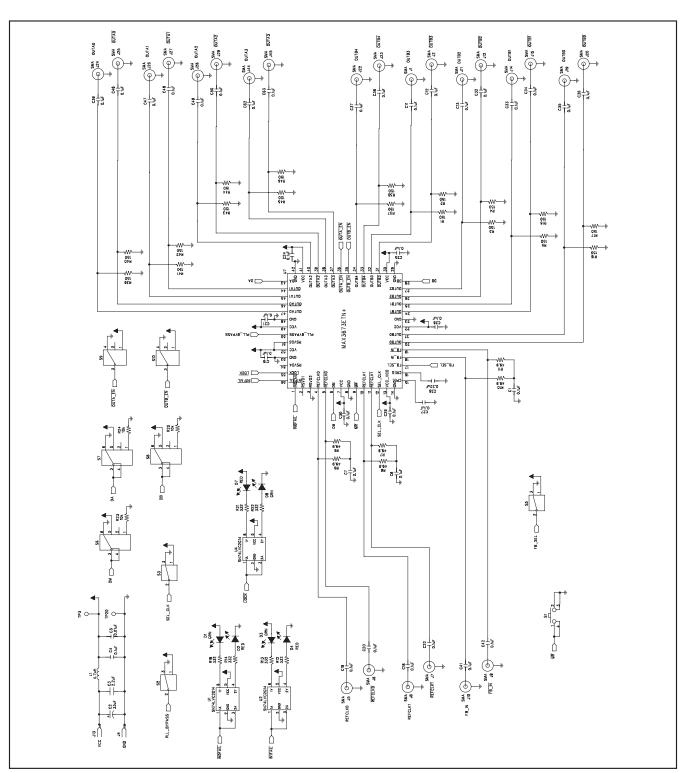

Figure 1. MAX3673 EV Kit Schematic

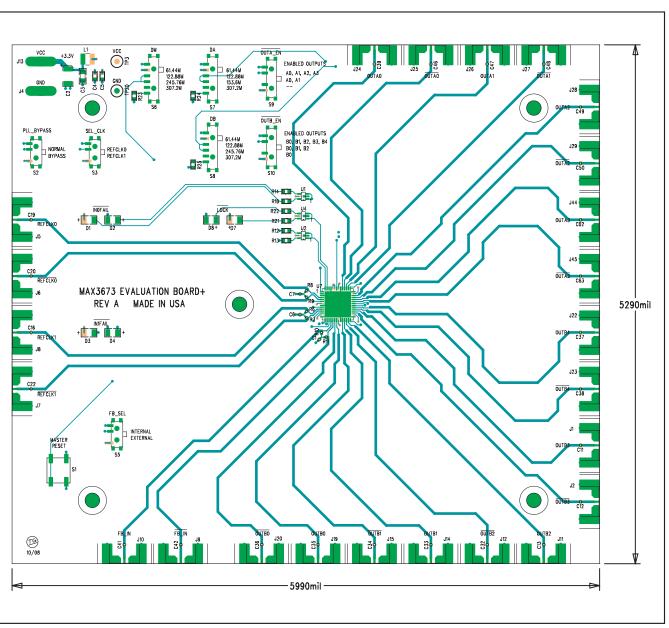

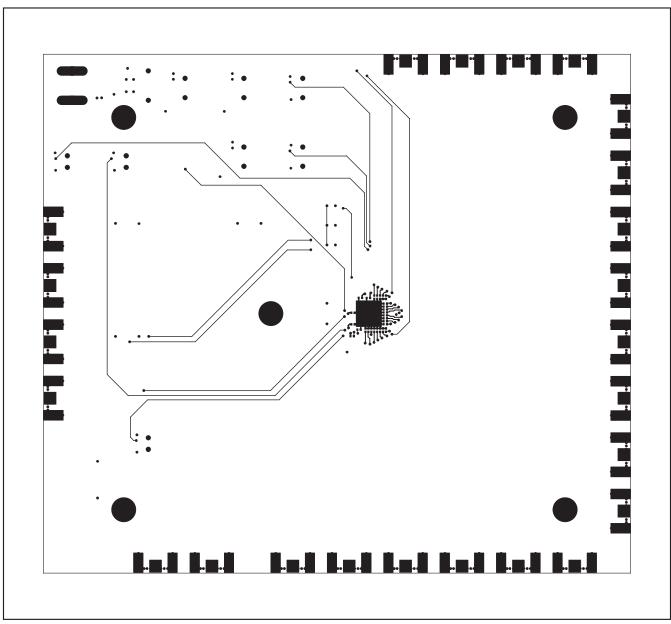

Figure 2. MAX3673 EV Kit Component Placement Guide—Component Side

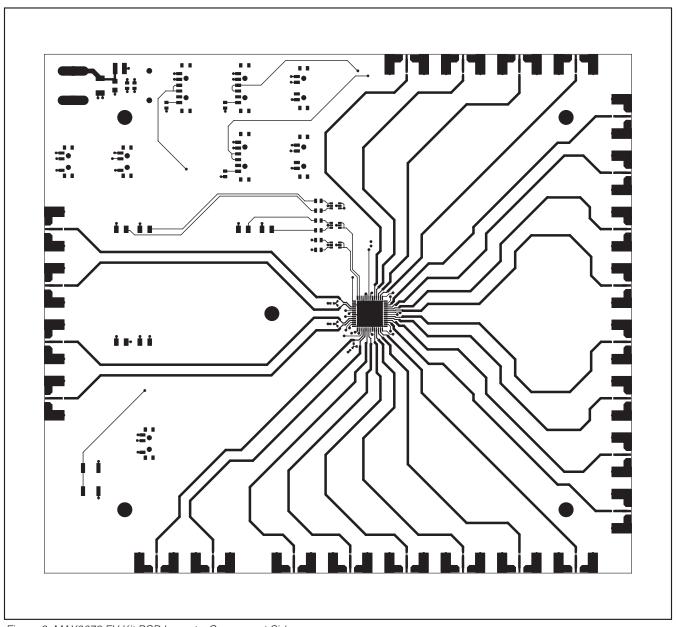

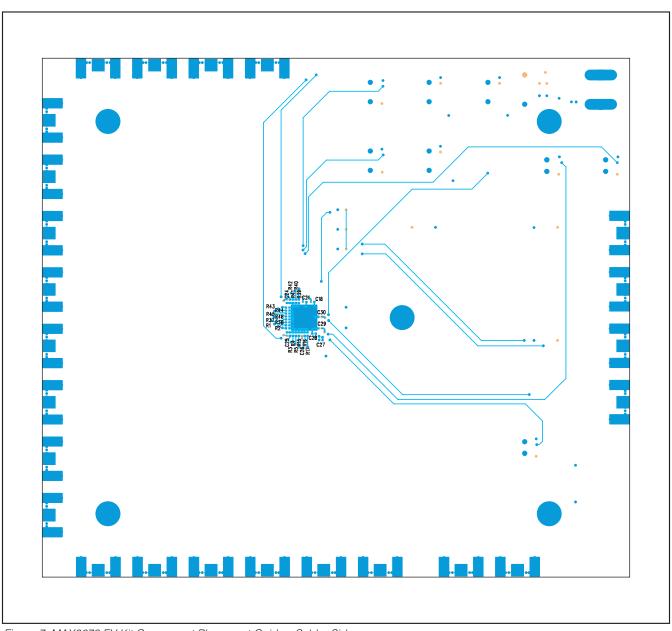

Figure 3. MAX3673 EV Kit PCB Layout—Component Side

Figure 4. MAX3673 EV Kit PCB Layout—Ground Plane

Figure 5. MAX3673 EV Kit PCB Layout—Power Plane

Figure 6. MAX3673 EV Kit PCB Layout—Solder Side

Figure 7. MAX3673 EV Kit Component Placement Guide—Solder Side

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microsemi: MAX3673EVKIT+