# **HDMI HIDER**

Check for Samples: TMDS141

#### **FEATURES**

- Supports 2.25 Gbps Signaling Rate for up to 1080p Resolutions Supporting 36-bits Per Pixel for Color Depth of 12-bits Per Color

- Compatible with HDMI 1.3a

- Integrated Receiver Termination

- 8-dB Equalizer Compensates Losses from 5-m or Longer HDMI Cables

- Selectable Output De-Emphasis Supports 1-m HDMI Transmission

- I<sup>2</sup>C<sup>™</sup> Repeater Isolates Bus Capacitance at Both Ends

- · High Impedance Outputs When Disabled

- TMDS Inputs HBM ESD Protection Exceeds 6 kV

- 3.3-V Supply Operation

- 40-Pin QFN Package (RHA)

- ROHS Compatible and 260°C Reflow Rated

- Accepts AC Couple DisplayPort Dual-Mode Signals and Translates Them into a HDMI1.3a Compatable TMDS Signal

## **APPLICATIONS**

- Digital TV

- DVD Player

- Set-Top-Box

- Audio Video Receiver

- Digital Projector

- DVI or HDMI cable

- DisplayPort Level Translator

#### **DESCRIPTION**

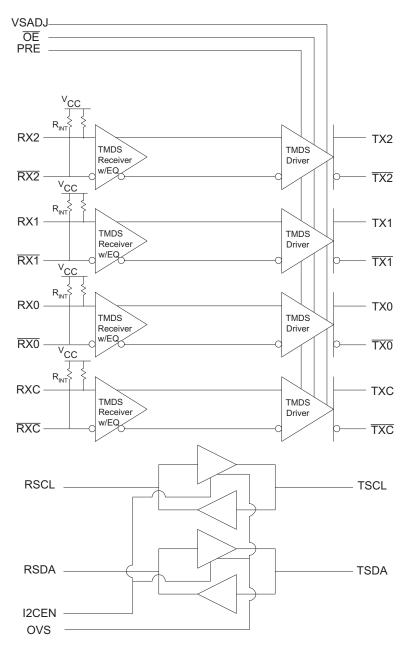

The TMDS141 HDMI hider is designed to accommodate a 1-m HDMI cable between a HDMI connector and a receiver. The internal cable causes signal distortion to high-speed TMDS signals, as well as increasing capacitance to the DDC channel. Each TMDS141 contains four TMDS repeaters to transmit digital content with signaling rates of up to 2.25-Gbps, and an I<sup>2</sup>C repeater to link extended display identification data (EDID) reading and high-bandwidth digital content protection (HDCP) key exchange under I<sup>2</sup>C standard mode operations.

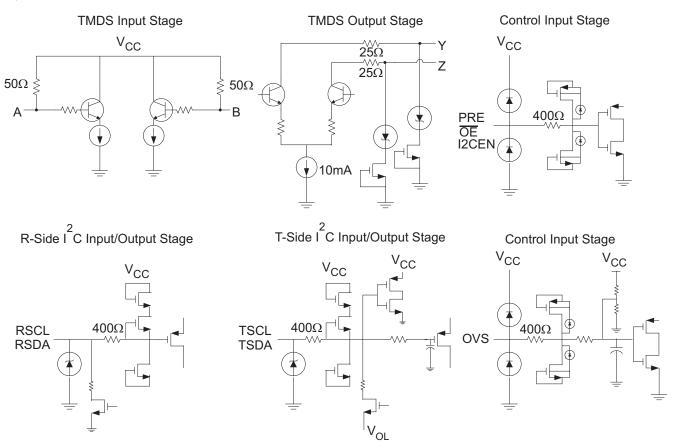

The device includes four TMDS compliant differential receivers with  $50-\Omega$  termination resistors and 3.3-V termination voltage integrated at each receiver input pin. External terminations are not required. A built-in frequency response equalization circuit, 8 dB at 825 MHz, compensates inter-symbol interference (ISI) losses from a 5-m or longer input cable link.

The device also includes four TMDS compliant differential drivers. A precision resistor is connected externally from the VSADJ pin to ground for setting the differential output voltage to be compliant with the TMDS standard. A selectable de-emphasis circuit is available via the PRE input to drive long PCB traces or cables. When PRE is high, the 3.5-dB high frequency gain offsets the losses due to the FR4 trace. PRE can be left open or kept low when the de-emphasis function is not desired.

Figure 1. TYPICAL APPLICATION

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments. I<sup>2</sup>C is a trademark of Philips Electronics.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION CONTINUED**

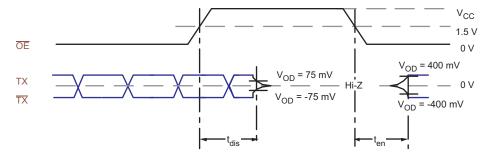

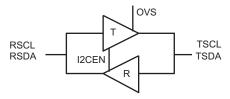

With standard TMDS terminations at the outputs, all TMDS outputs are forced high-impedance when  $\overline{\text{OE}}$  is set high. The I<sup>2</sup>C repeater isolates the buses without accumulating the capacitance of both sides. It allows DDC capacitance to be controlled under the desired load. The I<sup>2</sup>C outputs are high-impedance when device supply voltage is less than 1.5 V or I2CEN is low. The OVS pin, output voltage select, provides the flexibility of adjusting the output voltage level of the TSCL and TSDA side to optimize noise margins while interfacing to different HDMI receivers. The device is characterized for operation from 0°C to 70°C.

#### **FUNCTIONAL BLOCK DIAGRAM**

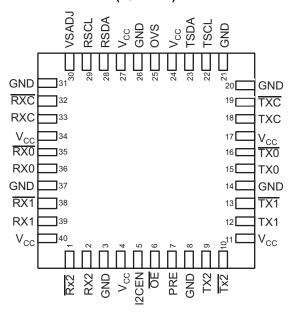

## RHA PACKAGE (TOP VIEW)

## **TERMINAL FUNCTIONS**

| TERMIN                                                                    | IAL                             | 1/0 | DESCRIPTION                                                     |  |  |  |  |

|---------------------------------------------------------------------------|---------------------------------|-----|-----------------------------------------------------------------|--|--|--|--|

| NAME                                                                      | NO.                             | I/O | DESCRIPTION                                                     |  |  |  |  |

| $\overline{RX2}$ , $\overline{RX1}$ , $\overline{RX0}$ , $\overline{RXC}$ | 1, 38, 35, 32                   | I   | TMDS Negative inputs                                            |  |  |  |  |

| RX2, RX1, RX0, RXC                                                        | 2, 39, 36, 33                   | I   | TMDS Positive inputs                                            |  |  |  |  |

| $\overline{TX2}$ , $\overline{TX1}$ , $\overline{TX0}$ , $\overline{TXC}$ | 10, 13, 16, 19                  | 0   | TMDS Negative outputs                                           |  |  |  |  |

| TX2, TX1, TX0, TXC                                                        | 9, 12, 15, 18                   | 0   | TMDS Positive outputs                                           |  |  |  |  |

| RSCL                                                                      | 29                              | I/O | DDC Bus clock line to source                                    |  |  |  |  |

| RSDA                                                                      | 28                              | I/O | DDC Bus data line to source                                     |  |  |  |  |

| TSCL                                                                      | 22                              | I/O | DDC Bus clock line to sink                                      |  |  |  |  |

| TSDA                                                                      | 23                              | I/O | DDC Bus data line to sink                                       |  |  |  |  |

| VSADJ                                                                     | 30                              | I   | TMDS Compliant voltage swing control                            |  |  |  |  |

| I2CEN                                                                     | 5                               | I   | I <sup>2</sup> C Repeater enable<br>Low: High-Z<br>High: Active |  |  |  |  |

| OVS                                                                       | 25                              | I   | TSCL/TSDA Output voltage select                                 |  |  |  |  |

| ŌĒ                                                                        | 6                               | I   | TMDS Output enable<br>Low: Active<br>High: High-Z               |  |  |  |  |

| PRE                                                                       | 7                               | 1   | TMDS Output de-emphasis adjustment<br>Low: 0 dB<br>High: 3.5 dB |  |  |  |  |

| Vcc                                                                       | 4, 11, 17, 24, 27,<br>34, 40    |     | Power supply                                                    |  |  |  |  |

| GND                                                                       | 3, 8, 14, 20, 21,<br>26, 31, 37 |     | Ground                                                          |  |  |  |  |

Copyright © 2006–2011, Texas Instruments Incorporated

## **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

# ORDERING INFORMATION(1)

| PART NUMBER | PART MARKING | PACKAGE              |

|-------------|--------------|----------------------|

| TMDS141RHAR | TMDS141      | 40-PIN QFN Tape/Reel |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|          |                      |                                       |                                                | UNIT  |  |  |  |

|----------|----------------------|---------------------------------------|------------------------------------------------|-------|--|--|--|

| $V_{CC}$ | Supply voltage range | (2)                                   | –0.5 V to 4 V                                  |       |  |  |  |

|          |                      | RX, RX                                | 2.0 V to 4 V                                   |       |  |  |  |

|          | Voltage range        | TX, TX, PRE, VSADJ, OE, I2CEN, OVS, H | -0.5V to 4 V                                   |       |  |  |  |

|          |                      | RSCL, RSDA, TSCL, TSDA                | –0.5 V to 6 V                                  |       |  |  |  |

|          |                      | Human body model <sup>(3)</sup>       | RX, RX                                         | ±6 kV |  |  |  |

|          | Electrostatic        | Human body model                      | All pins                                       | ±4 kV |  |  |  |

|          | discharge            | Charged-device model (4) (all pins)   | Charged-device model <sup>(4)</sup> (all pins) |       |  |  |  |

|          |                      | Machine model (5) (all pins)          | ±200 V                                         |       |  |  |  |

|          | Continuous power dis | See Dissipation Rating Table          |                                                |       |  |  |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

- (3) Tested in accordance with JEDEC Standard 22, Test Method A114-B

- 4) Tested in accordance with JEDEC Standard 22, Test Method C101-A

- (5) Tested in accordance with JEDEC Standard 22, Test Method A115-A

#### **DISSIPATION RATINGS**

| PACKAGE    | PCB JEDEC STANDARD    | T <sub>A</sub> ≤ 25°C | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |  |

|------------|-----------------------|-----------------------|---------------------------------------------------------------|---------------------------------------|--|

| 40-QFN RHA | Low-K <sup>(2)</sup>  | 839.7 mW              | 8.39 mW/°C                                                    | 461.8 mW                              |  |

| 40-QFN RHA | High-K <sup>(3)</sup> | 3030.3 mW             | 30.3 mW/°C                                                    | 1666.6mW                              |  |

- (1) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

- (2) In accordance with the Low-K thermal metric definitions of EIA/JESD51-3

- (3) In accordance with the High-K thermal metric definitions of EIA/JESD51-7

#### THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                            |                                                                                                   | MIN        | TYP | MAX   | UNIT |      |

|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------|------------|-----|-------|------|------|

| $R_{\theta JB}$ | Junction-to-board thermal resistance |                                                                                                   |            |     | 30.96 |      | °C/W |

| $R_{\theta JC}$ | Junction- to-case thermal resistance |                                                                                                   |            |     | 32.42 |      | °C/W |

|                 |                                      | $V_{IH} = V_{CC}, V_{IL} = V_{CC} - 0.5 \text{ V}, R_T = 50 \Omega,$                              | PRE = Low  |     | 344   | 370  | m\\/ |

| _               | Davies was dissination               | $V_{CC} = AV_{CC} = 3.3V$ , $R_{vsadj} = 4.64 \text{ k}\Omega$                                    | PRE = High |     | 381   | 407  | mW   |

| P <sub>D</sub>  | Device power dissipation             | $V_{IH} = V_{CC}, V_{IL} = V_{CC} - 0.6 \text{ V}, R_T = 50 \Omega,$                              | PRE = Low  |     |       | 484  | \^/  |

|                 |                                      | $V_{CC} = 3.6 \text{ V}, \text{ AV}_{CC} = 3.3 \text{V}, \text{ R}_{vsadj} = 4.6 \text{ k}\Omega$ | PRE = High |     |       | 526  | mW   |

Product Folder Link(s): TMDS141

## **RECOMMENDED OPERATING CONDITIONS**

|                       |                                                   | MIN                  | NOM  | MAX                 | UNIT  |

|-----------------------|---------------------------------------------------|----------------------|------|---------------------|-------|

| V <sub>CC</sub>       | Supply voltage                                    | 3                    | 3.3  | 3.6                 | V     |

| $T_A$                 | Operating free-air temperature                    | 0                    |      | 70                  | °C    |

| TMDS D                | IFFERENTIAL PINS (RX/ RXC)                        |                      |      |                     |       |

| $V_{IC}$              | Input common mode voltage                         | V <sub>CC</sub> -400 |      | V <sub>CC</sub> +10 | mV    |

| $V_{\text{ID}}$       | Receiver peak-to-peak differential input voltage  | 150                  |      | 1560                | mVp-p |

| R <sub>VSADJ</sub>    | Resistor for TMDS compliant voltage swing range   | 4.6                  | 4.64 | 4.68                | kΩ    |

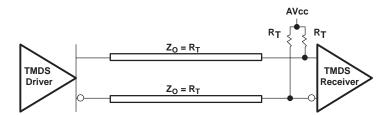

| $AV_{CC}$             | TMDS Output termination voltage, see Figure 2     | 3                    | 3.3  | 3.6                 | V     |

| R <sub>T</sub>        | Termination resistance, see Figure 2              | 45                   | 50   | 55                  | Ω     |

|                       | Signaling rate                                    | 0                    |      | 2.25                | Gbps  |

| CONTRO                | DL PINS (PRE, OE, I2CEN)                          |                      |      |                     |       |

| V <sub>IH</sub>       | LVTTL High-level input voltage                    | 2                    |      | $V_{CC}$            | V     |

| $V_{IL}$              | LVTTL Low-level input voltage                     | GND                  |      | 0.8                 | V     |

| CONTRO                | DL PINS (OVS)                                     |                      |      |                     |       |

| V <sub>IH</sub>       | LVTTL High-level input voltage                    | 3                    |      | 3.6                 | V     |

| V <sub>IL</sub>       | LVTTL Low-level input voltage                     | -0.5                 |      | 0.5                 | V     |

| I <sup>2</sup> C PINS | (TSCL, TSDA)                                      |                      |      | •                   |       |

| V <sub>IH</sub>       | High-level input voltage                          | 0.7V <sub>CC</sub>   |      | 5.5                 | V     |

| V <sub>IL</sub>       | Low-level input voltage                           | -0.5                 |      | 0.3V <sub>CC</sub>  | V     |

| V <sub>ICL</sub>      | Low-level input voltage contention <sup>(1)</sup> | -0.5                 |      | 0.4                 | V     |

| I <sup>2</sup> C PINS | (RSCL, RSDA)                                      | <u>.</u>             |      |                     |       |

| V <sub>IH</sub>       | High-level input voltage                          | 2.1                  |      | 5.5                 | V     |

| V <sub>IL</sub>       | Low-level input voltage                           | -0.5                 |      | 1.5                 | V     |

<sup>(1)</sup>  $V_{IL}$  specification is for the first low level seen by the SCL/SDA lines.  $V_{ICL}$  is for the second and subsequent low levels seen by the TSCL/TSDA lines.

## **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                                              | TEST CO                                                                                                                      | ONDITIONS                                                                                                      | MIN                   | TYP <sup>(1)</sup>  | MAX                   | UNIT                  |

|-------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|-----------------------|-----------------------|

| I <sub>cc</sub>         | Supply current                                                         | $V_{IH} = V_{CC}, V_{IL} = V_{CC} - AV_{CC} = 3.3 \text{ V}, R_{VSADJ} = 1.65\text{-Gbps HDMI data }$ 165-MHz Pixel clock, P | = 4.64 kΩ,<br>pattern,                                                                                         |                       | 108                 | 130 <sup>(2)</sup>    | mA                    |

| $P_D$                   | Power dissipation                                                      | $V_{IH} = V_{CC}, V_{IL} = V_{CC} - AV_{CC} = 3.3 \text{ V}, R_{VSADJ} = 1.65\text{-Gbps HDMI data }$ 165-MHz Pixel clock, P |                                                                                                                |                       | 497 <sup>(2)</sup>  | mW                    |                       |

| TMDS DIF                | FERENTIAL PINS (TX, TXC)                                               |                                                                                                                              |                                                                                                                |                       |                     |                       |                       |

| $V_{OH}$                | Single-ended high-level output voltage                                 |                                                                                                                              |                                                                                                                | AV <sub>CC</sub> -10  |                     | AV <sub>CC</sub> +10  | mV                    |

| $V_{OL}$                | Single-ended low-level output voltage                                  |                                                                                                                              |                                                                                                                | AV <sub>CC</sub> -600 |                     | AV <sub>CC</sub> -400 | mV                    |

| $V_{\text{swing}}$      | Single-ended output swing voltage                                      | See Figure 3, AV <sub>CC</sub> = 3                                                                                           | 2 \/                                                                                                           | 400                   |                     | 600                   | mV                    |

| $V_{OD(O)}$             | Overshoot of output differential voltage                               | $R_T = 50 \Omega$                                                                                                            | 5.5 v,                                                                                                         |                       |                     | 15%                   | 2× V <sub>swing</sub> |

| $V_{OD(U)}$             | Undershoot of output differential voltage                              |                                                                                                                              |                                                                                                                |                       |                     | 25%                   | 2× V <sub>swing</sub> |

| $\Delta V_{OC(SS)}$     | Change in steady-state common-mode output voltage between logic states |                                                                                                                              |                                                                                                                |                       |                     | 5                     | mV                    |

| I <sub>(O)OFF</sub>     | Single-ended standby output current                                    | $0 \text{ V} \le \text{V}_{CC} \le 1.5 \text{ V},$<br>$A\text{V}_{CC} = 3.3 \text{ V}, R_T = 50$                             | $0 \text{ V} \le \text{V}_{CC} \le 1.5 \text{ V},$<br>$A\text{V}_{CC} = 3.3 \text{ V}, \text{R}_T = 50 \Omega$ |                       |                     | 10                    | μΑ                    |

| V <sub>OD(pp)</sub>     | Peak-to-peak output differential voltage                               | 0 5 4 555 11                                                                                                                 | P. 1                                                                                                           | 800                   |                     | 1200                  |                       |

| V <sub>ODE(SS)</sub>    | Steady state output differential voltage with de-emphasis              | See Figure 4, PRE = H<br>$AV_{CC} = 3.3 \text{ V}, R_T = 50$                                                                 | 600                                                                                                            |                       | 820                 | mVp-p                 |                       |

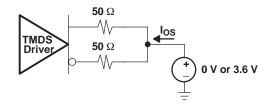

| I <sub>(OS)</sub>       | Short circuit output current                                           | See Figure 5                                                                                                                 |                                                                                                                | -12                   |                     | 12                    | mA                    |

| V <sub>I(open)</sub>    | Single-ended input voltage under high impedance input or open input    | Ι <sub>Ι</sub> = 10 μΑ                                                                                                       | V <sub>CC</sub> -10                                                                                            |                       | V <sub>CC</sub> +10 | mV                    |                       |

| R <sub>INT</sub>        | Input termination resistance                                           | V <sub>IN</sub> = 2.9 V                                                                                                      |                                                                                                                | 45                    | 50                  | 55                    | Ω                     |

| CONTROL                 | PINS (PRE, OE, I2CEN, OVS)                                             |                                                                                                                              |                                                                                                                | 1                     |                     |                       |                       |

| I <sub>IH</sub>         | High-level digital input current                                       | V <sub>IH</sub> = 2 V or V <sub>CC</sub>                                                                                     |                                                                                                                | -10                   |                     | 10                    | μΑ                    |

| I <sub>IL</sub>         | Low-level digital input current                                        | V <sub>IL</sub> = GND or 0.8 V                                                                                               |                                                                                                                | -10                   |                     | 10                    | μΑ                    |

| I <sup>2</sup> C PINS ( | TSCL, TSDA)                                                            |                                                                                                                              |                                                                                                                |                       |                     |                       |                       |

|                         |                                                                        | V <sub>I</sub> = 5.5 V                                                                                                       |                                                                                                                | -50                   |                     | 50                    |                       |

| I <sub>lkg</sub>        | Input leakage current                                                  | $V_I = V_{CC}$                                                                                                               |                                                                                                                | -10                   |                     | 10                    | μA                    |

| I <sub>OH</sub>         | High-level output current                                              | V <sub>O</sub> = 3.6 V                                                                                                       |                                                                                                                | -10                   |                     | 10                    | μΑ                    |

| I <sub>IL</sub>         | Low-level input current                                                | V <sub>IL</sub> = GND                                                                                                        |                                                                                                                | -40                   |                     | 40                    | μΑ                    |

|                         |                                                                        |                                                                                                                              | OVS = NC <sup>(3)</sup>                                                                                        | 0.47                  |                     | 0.6                   |                       |

| $V_{OL}$                | Low-level output voltage                                               | $I_{OL} = 400 \mu A \text{ or } 4 \text{ mA}$                                                                                | OVS = GND <sup>(3)</sup>                                                                                       | 0.6                   |                     | 0.75                  | V                     |

|                         |                                                                        |                                                                                                                              | OVS = V <sub>CC</sub> (3)                                                                                      | 0.75                  |                     | 0.95                  |                       |

|                         |                                                                        |                                                                                                                              | OVS = NC <sup>(3)</sup>                                                                                        |                       | 70                  |                       |                       |

| $V_{OL}$ - $V_{ILC}$    | Low-level input voltage below output<br>low-level voltage level        | Ensured by design                                                                                                            | OVS = GND <sup>(3)</sup>                                                                                       |                       | 220                 |                       | mV                    |

|                         | low level voltage level                                                |                                                                                                                              | OVS = V <sub>CC</sub> (3)                                                                                      |                       | 370                 |                       |                       |

| 0                       | land the standard and a standard                                       | V <sub>I</sub> = 5.0 V or 0 V, Freq                                                                                          | = 100 kHz                                                                                                      |                       |                     | 25                    |                       |

| C <sub>IO</sub>         | Input/output capacitance                                               | V <sub>I</sub> = 3.0 V or 0 V, Freq                                                                                          | = 100 kHz                                                                                                      |                       |                     | 10                    | pF                    |

| I <sup>2</sup> C PINS ( | RSCL, RSDA)                                                            |                                                                                                                              |                                                                                                                |                       |                     |                       |                       |

|                         |                                                                        | V <sub>I</sub> = 5.5 V                                                                                                       |                                                                                                                | -50                   |                     | 50                    |                       |

| I <sub>lkg</sub>        | Input leakage current                                                  | $V_I = V_{CC}$                                                                                                               |                                                                                                                | -10                   |                     | 10                    | μA                    |

| I <sub>OH</sub>         | High-level output current                                              | V <sub>O</sub> = 3.6 V                                                                                                       |                                                                                                                | -10                   |                     | 10                    | μA                    |

| I <sub>IL</sub>         | Low-level input current                                                | V <sub>IL</sub> = GND                                                                                                        |                                                                                                                | -10                   |                     | 10                    | μA                    |

| V <sub>OL</sub>         | Low-level output voltage                                               | I <sub>OL</sub> = 4 mA                                                                                                       |                                                                                                                |                       | 0.2                 | V                     |                       |

|                         | lanut conscitores                                                      | V <sub>I</sub> = 5.0 V or 0 V, Freq                                                                                          | = 100 kHz                                                                                                      |                       |                     | 25                    |                       |

| C <sub>I</sub>          | Input capacitance                                                      | V <sub>I</sub> = 3.0 V or 0 V, Freq                                                                                          | = 100 kHz                                                                                                      |                       |                     | 10                    | pF                    |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

(2) The maximum rating is characterized under 3.6 V V<sub>CC</sub> and 600 mV V<sub>ID</sub>.

(3) The patent of the OVS pin is filed.

#### SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                                  | TEST CONDITIONS                                                                                        | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| TMDS I               | DIFFERENTIAL PINS (TX/TXC)                                                 |                                                                                                        |     |                    |     |      |

| t <sub>PLH</sub>     | Propagation delay time, low-to-high-level output                           |                                                                                                        | 100 |                    | 500 | ps   |

| t <sub>PHL</sub>     | Propagation delay time, high-to-low-level output                           |                                                                                                        | 100 |                    | 500 | ps   |

| t <sub>r</sub>       | Differential output signal rise time (20% - 80%)                           |                                                                                                        | 75  |                    | 240 | ps   |

| t <sub>f</sub>       | Differential output signal fall time (20% - 80%)                           | See Figure 3, $AV_{CC} = 3.3 \text{ V}$ ,                                                              | 75  |                    | 240 | ps   |

| t <sub>sk(p)</sub>   | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) <sup>(2)</sup>         | $R_T = 50 \Omega$                                                                                      |     |                    | 50  | ps   |

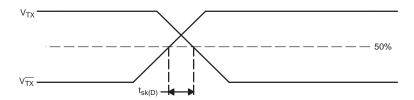

| t <sub>sk(D)</sub>   | Intra-pair differential skew, see Figure 6                                 |                                                                                                        |     |                    | 35  | ps   |

| t <sub>sk(o)</sub>   | Inter-pair channel-to-channel output skew(3)                               |                                                                                                        |     |                    | 80  | ps   |

| t <sub>sk(pp)</sub>  | Part-to-part skew (4)                                                      |                                                                                                        |     |                    | 200 | ps   |

| t <sub>en</sub>      | Enable time                                                                | Con Figure 7                                                                                           |     |                    | 10  | ns   |

| t <sub>dis</sub>     | Disable time                                                               | See Figure 7                                                                                           |     |                    | 10  | ns   |

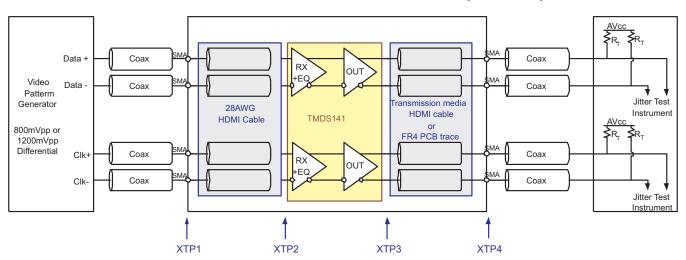

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from TXC, residual jitter <sup>(5)</sup>        | See Figure 8, RXC = 165-MHz clock,                                                                     |     | 14                 | 30  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from TX0 - TX2, residual jitter <sup>(5)</sup>  | RX = 1.65-Gbps HDMI pattern,<br>Input: 5m 28AWG HDMI cable,<br>Output: 1m 28AWG HDMI cable, PRE = high |     | 30                 | 88  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from TXC, residual jitter <sup>(5)</sup>        | See Figure 8, RXC = 225-MHz clock,                                                                     |     | 25                 |     |      |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from TX0 - TX2, residual jitter (5)             | RX = 2.25-Gbps HDMI pattern,<br>Input: 5m 28AWG HDMI cable,<br>Output: 1m 28AWG HDMI cable, PRE = high |     | 42                 | 88  | ps   |

| I2C PIN              | IS (RSCL, RSDA, TSCL, TSDA)                                                |                                                                                                        |     |                    | I   |      |

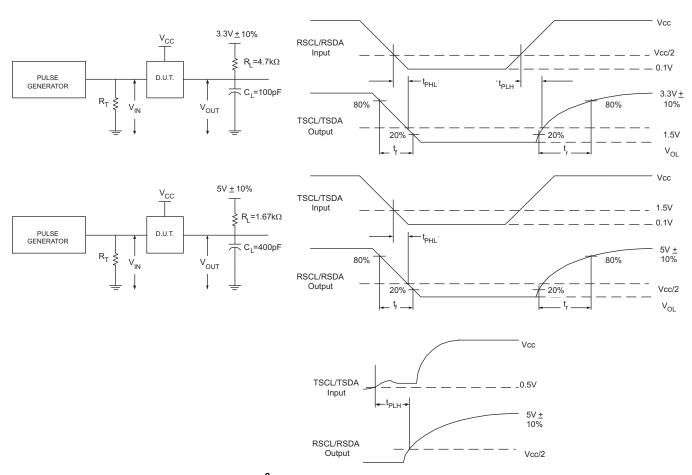

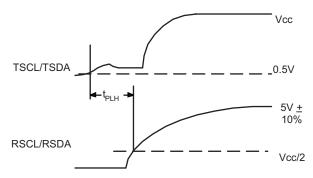

| t <sub>PLH</sub>     | Propagation delay time, low-to-high-level output TSCL/TSDA to RSCL/RSDA    |                                                                                                        | 204 |                    | 459 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high-to-low-level output TSCL/TSDA to RSCL/RSDA    |                                                                                                        | 35  |                    | 120 | ns   |

| t <sub>PLH</sub>     | Propagation delay time, low-to-high-level output<br>RSCL/RSDA to TSCL/TSDA |                                                                                                        | 194 |                    | 351 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high-to-low-level output RSCL/RSDA to TSCL/TSDA    | See Figure 9, OVS = NC                                                                                 | 35  |                    | 120 | ns   |

| t <sub>r</sub>       | TSCL/TSDA Output signal rise time                                          |                                                                                                        | 500 |                    | 800 | ns   |

| t <sub>f</sub>       | TSCL/TSDA Output signal fall time                                          |                                                                                                        | 30  |                    | 72  | ns   |

| t <sub>r</sub>       | RSCL/RSDA Output signal rise time                                          |                                                                                                        | 796 |                    | 999 | ns   |

| t <sub>f</sub>       | RSCL/RSDA Output signal fall time                                          |                                                                                                        | 20  |                    | 72  | ns   |

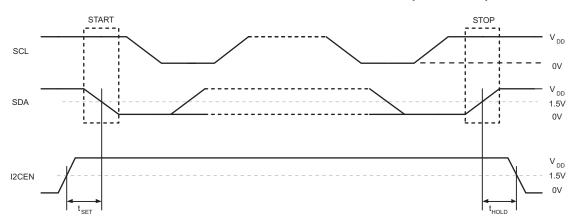

| t <sub>set</sub>     | Enable to start condition                                                  | 0 5 40                                                                                                 | 100 |                    |     | ns   |

| t <sub>hold</sub>    | Enable after stop condition                                                | See Figure 10                                                                                          | 100 |                    |     | ns   |

Jitter specifications are ensured by design and characterization and measured in BER-12

$t_{sk(p)}$  is the magnitude of the time difference between  $t_{PLH}$  and  $t_{PHL}$  of a specified terminal.  $t_{sk(0)}$  is the magnitude of the difference in propagation delay times between any specified terminals of channel 2 to 4 of a device when inputs are tied together.

$t_{sk(pp)}$  is the magnitude of the difference in propagation delay times between any specified terminals of channel 2 to 4 of two devices, or between channel 1 of two devices, when both devices operate with the same source, the same supply voltages, at the same temperature, and have identical packages and test circuits.

## PARAMETER MEASUREMENT INFORMATION

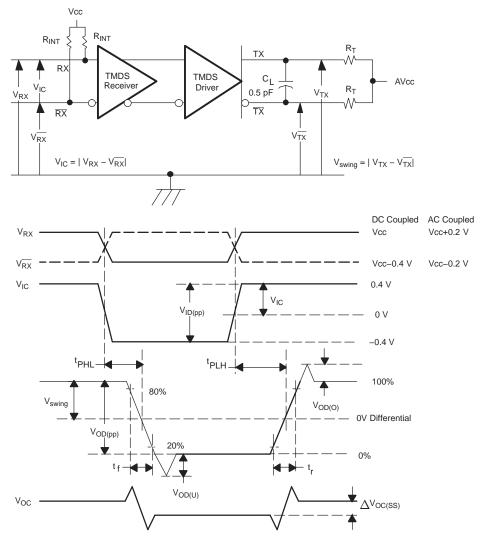

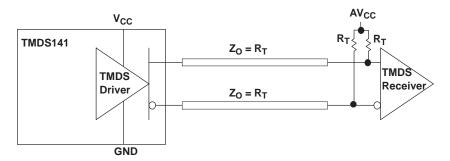

Figure 2. Typical Termination for TMDS Output Driver

NOTE: PRE = low. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f$  < 100 ps, 100 MHz from Agilent 81250.  $C_L$  includes instrumentation and fixture capacitance within 0.06 m of the D.U.T. Measurement equipment provides a bandwidth of 20 GHz minimum.

Figure 3. TMDS Timing Test Circuit and Definitions

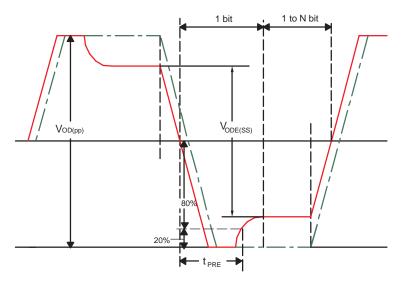

# PARAMETER MEASUREMENT INFORMATION (continued)

Figure 4. De-Emphasis Output Voltage Waveforms and Duration Measurement Definitions

Figure 5. Short Circuit Output Current Test Circuit

Figure 6. Definition of Intra-Pair Differential Skew

Figure 7. TMDS Enable and Disable Timing Definitions

# **PARAMETER MEASUREMENT INFORMATION (continued)**

- A. All jitters are measured in BER of 10<sup>-12</sup>

- B. The residual jitter reflects the total jitter measured at XTP4, subtract the total jitter at XTP1

Figure 8. Jitter Test Circuit

Figure 9. I<sup>2</sup>C Timing Test Circuit and Definition

# PARAMETER MEASUREMENT INFORMATION (continued)

Figure 10. I<sup>2</sup>C Setup and Hold Definition

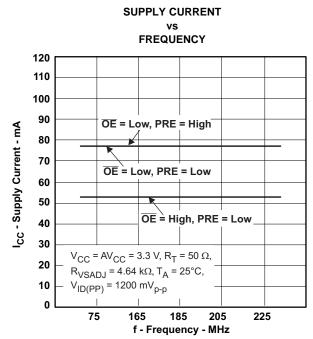

#### TYPICAL CHARACTERISTICS

Figure 11.

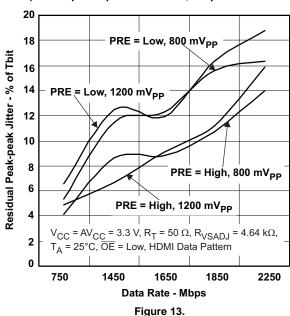

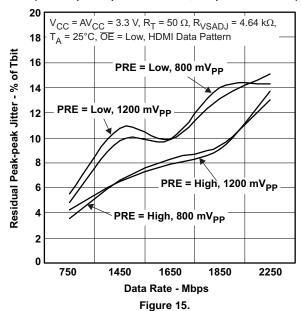

# RESIDUAL PEAK-TO-PEAK JITTER vs

# DATA RATE (DC Coupled Input: 5m 28AWG, Output: 1m 28AWG)

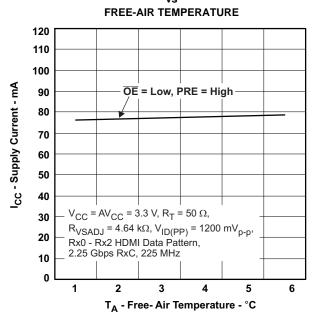

# SUPPLY CURRENT

Figure 12.

#### **RESIDUAL PEAK-TO-PEAK JITTER**

#### DATA RATE

# (DC Coupled Input: 3m 30AWG, Output: 1m 28AWG)

Figure 14.

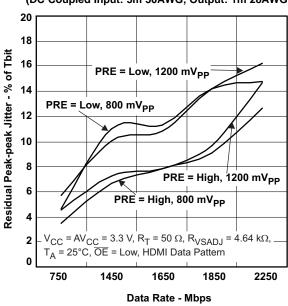

## TYPICAL CHARACTERISTICS (continued)

#### **RESIDUAL PEAK-TO-PEAK JITTER**

# DATA RATE

## (AC Coupled Input: 3m 30AWG, Output: 1m 28AWG)

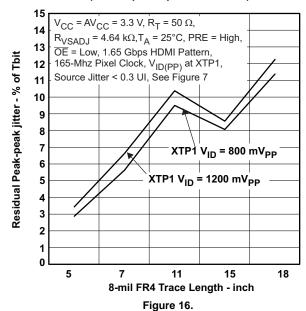

## **RESIDUAL PEAK-TO-PEAK JITTER**

## vs

# 8-MIL FR4 TRACE OUTPUT (DC Coupled Input: 5m 28AWG)

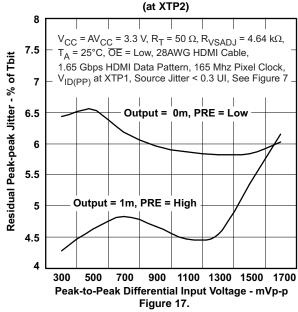

#### **RESIDUAL PEAK-TO-PEAK JITTER**

#### ٧S

# PEAK-TO-PEAK DIFFERENTIAL INPUT VOLTAGE

#### APPLICATION INFORMATION

## Supply Voltage

All V<sub>CC</sub> pins can be tied to a single 3.3-V power source. A 0.01-µF capacitor is connected from each V<sub>CC</sub> pin directly to ground to filter supply noise.

## **TMDS Inputs**

Standard TMDS terminations are integrated on all TMDS inputs. External terminations are not required. Each input channel contains an 8-dB equalization circuit to compensate for cable losses. The voltage at the TMDS input pins must be limited per the absolute maximum ratings. An unused input should not be connected to ground as this would result in excessive current flow damaging the device. TMDS input pins do not incorporate failsafe circuits. An unused input channel can be externally biased to prevent output oscillation. The complementary input pin is recommended to be grounded through a 1-k $\Omega$  resistor and the other pin left open.

## **TMDS Outputs**

A 1% precision resistor, 4.64-k $\Omega$ , connected from VSADJ to ground is recommended to allow the differential output swing to comply with TMDS signal levels. The differential output driver provides a typical 10-mA current sink capability, which provides a typical 500-mV voltage drop across a  $50-\Omega$  termination resistor.

Figure 18. TMDS Driver and Termination Circuit

Referring to Figure 18, if both V<sub>CC</sub> (TMDS141 supply) and AV<sub>CC</sub> (sink termination supply) are both powered, the TMDS output signals is high impedance when OEB = high. Both supplies being active is the normal operating condition.

Again refer to Figure 18, if V<sub>CC</sub> is on and AV<sub>CC</sub> is off, the TMDS outputs source a typical 5-mA current through each termination resistor to ground. A total of 10-mW of power is consumed by the terminations independent of the OEB logical selection. When AV<sub>CC</sub> is powered on, normal operation (OEB controls output impedance) is resumed.

When the power source of the device is off and the power source to termination is on, the I<sub>O(off)</sub>, output leakage current, specification ensures the leakage current is limited 10-µA or less.

The PRE pin provides 3dB de-emphasis, allowing output signal pre-conditioning to offset interconnect losses from the TMDS141 outputs to a TMDS receiver. PRE is recommended to be set low while connecting to a receiver throw short PCB route.

## I<sup>2</sup>C Function Description

The RSCL/RSDA and TSCL/TSDA pins are 5-V tolerant when the device is powered off and high impedance under low supply voltage, 1.5 V or below. If the device is powered up and the I<sup>2</sup>C circuits are enabled, and I2CEN = high, the driver T (see Figure 19) is turned on or off depending up on the corresponding R side voltage

When the R side is pulled low below 1.5 V, the corresponding T side driver turns on and pulls the T side down to a low level output voltage, Vol. The value of Vol depends on the input to the OVS pin. When OVS is left floating

Copyright © 2006-2011, Texas Instruments Incorporated

or not connected,  $V_{OL}$  is typically 0.5 V. When OVS is connected to GND,  $V_{OL}$  is typically 0.65 V. When OVS is connected to  $V_{CC}$ ,  $V_{OL}$  is typically 0.8 V.  $V_{OL}$  is always higher than the driver R input threshold,  $V_{IL}$ , which is typically 0.4 V, preventing lockup of the repeater loop. The  $V_{OL}$  value can be selected to improve or optimize noise margins between  $V_{OL}$  and the  $V_{IL}$  of the repeater itself or the  $V_{IL}$  of some external device connected on the T side.

When the R side is pulled up, above 1.5 V, the T side driver turns off and the T side pin is high impedance.

Figure 19. I<sup>2</sup>C Drivers in TMDS141

When the T side is pulled below 0.4 V by an external  $I^2C$  driver, both drivers R and T are turned on. Driver R pulls the R side to near 0 V, and driver T is on, but is overridden by the external  $I^2C$  driver. If driver T is already on, due to a low on the R side, driver R just turns on.

When the T side is released by the external  $I^2C$  driver, driver T is still on, so the T side is only able to rise to the  $V_{OL}$  of driver T. Driver R turns off, since  $V_{OL}$  is above its 0.4-V  $V_{IL}$  threshold, releasing the R side. If no external  $I^2C$  driver is keeping the R side low, the R side rises, and driver T turns off once the R side rises above 1.5 V, see Figure 20.

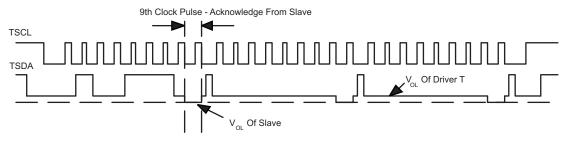

Figure 20. Waveform of Turning Driver T Off

It is important that any external  $I^2C$  driver on the T side is able to pull the bus below 0.4 V to ensure full operation. If the T side cannot be pulled below 0.4 V, driver R may not recognize and transmit the low value to the R side.

## I<sup>2</sup>C Enable

The I2CEN pin is active high with an internal pull-up to  $V_{CC}$ . It can be used to isolate a badly behaved slave during power up. It should never change state during an  $I^2C$  operation because disabling during a bus operation may hang the bus and enabling part way through a bus cycle could confuse the  $I^2C$  parts being enabled.

## I<sup>2</sup>C Behavior

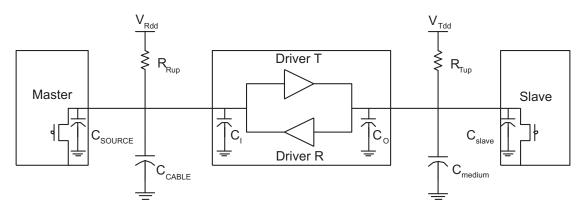

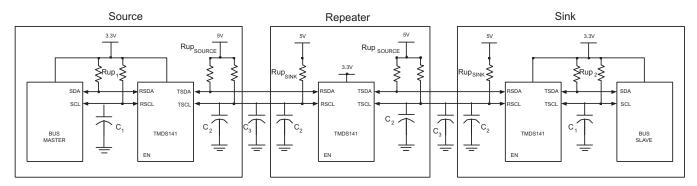

The typical application of the TMDS141 is as a repeater in a TV connecting the HDMI input connector and an internal HDMI Rx through flat cables. The I<sup>2</sup>C repeater is 5-V tolerant, and no additional circuitry is required to translate between 3.3-V to 5-V bus voltages. In the following example, the system master is running on an R-side I<sup>2</sup>C-bus while the slave is connected to a T-side bus. Both buses run at 100 kHz supporting standard-mode I<sup>2</sup>C operation. Master devices can be placed on either bus.

Figure 21. Typical Application

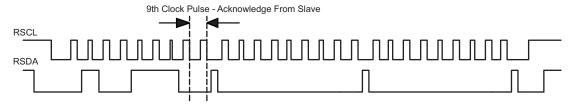

Figure 22 illustrates the waveforms seen on the R-side I<sup>2</sup>C-bus when the master writes to the slave through the I<sup>2</sup>C repeater circuit of the TMDS141. This looks like a normal I<sup>2</sup>C transmission, and the turn on and turn off of the acknowledge signals are slightly delayed.

Figure 22. Bus R Waveform

Figure 23 illustrates the waveforms seen on the T-side  $I^2$ C-bus under the same operation in Figure 22. On the T-side of the  $I^2$ C repeater, the clock and data lines would have a positive offset from ground equal to the  $V_{OL}$  of the driver T. After the 8th clock pulse, the data line is pulled to the  $V_{OL}$  of the slave device which is very close to ground in this example. At the end of the acknowledge, the slave device releases and the bus level rises back to the  $V_{OL}$  set by the driver until the R-side rises above  $V_{CC}/2$ , after which it continues to high. It is important to note that any arbitration or clock stretching events require that the low level on the T-side bus at the input of the TMDS141  $I^2$ C repeater is below 0.4 V to be recognized by the device and then transmitted to the R-side  $I^2$ C bus.

Figure 23. Bus T Waveform

The I<sup>2</sup>C circuitry inside the TMDS141 allows multiple stage operation as shown in Figure 24. I<sup>2</sup>C-Bus slave devices can be connected to any of the bus segments. The number of devices that can be connected in series is limited by repeater delay/time of flight considerations for the maximum bus speed requirements.

Figure 24. Typical Series Application

# I<sup>2</sup>C Pull-up Resistors

The pull-up resistor value is determined by two requirements:

1. The maximum sink current of the I<sup>2</sup>C buffer:

The maximum sink current is 3 mA or slightly higher for an I<sup>2</sup>C driver supporting standard-mode I<sup>2</sup>C operation.

$$R_{up(min)} = V_{DD}/lsink$$

(1)

2. The maximum transition time on the bus:

The maximum transition time, T, of an I<sup>2</sup>C bus is set by an RC time constant, where R is the pull-up resistor value, and C is the total load capacitance. The parameter, k, can be calculated from equation 3 by solving for t, the times at which certain voltage thresholds are reached. Different input threshold combinations introduce different values of t. Table 1 summarizes the possible values of k under different threshold combinations.

$$T = k \times RC \tag{2}$$

$$V(t) = V_{DD}(1 - e^{-t/RC})$$

(3)

Table 1. Value k Upon Different Input Threshold Voltages

| $V_{th}-V_{th+}$    | $0.7V_{DD}$ | $0.65V_{DD}$ | $0.6V_{DD}$ | 0.55V <sub>DD</sub> | 0.5V <sub>DD</sub> | 0.45V <sub>DD</sub> | 0.4V <sub>DD</sub> | 0.35V <sub>DD</sub> | $0.3V_{DD}$ |

|---------------------|-------------|--------------|-------------|---------------------|--------------------|---------------------|--------------------|---------------------|-------------|

| 0.1V <sub>DD</sub>  | 1.0986      | 0.9445       | 0.8109      | 0.6931              | 0.5878             | 0.4925              | 0.4055             | 0.3254              | 0.2513      |

| 0.15V <sub>DD</sub> | 1.0415      | 0.8873       | 0.7538      | 0.6360              | 0.5306             | 0.4353              | 0.3483             | 0.2683              | 0.1942      |

| 0.2V <sub>DD</sub>  | 0.9808      | 0.8267       | 0.6931      | 0.5754              | 0.4700             | 0.3747              | 0.2877             | 0.2076              | 0.1335      |

| 0.25V <sub>DD</sub> | 0.9163      | 0.7621       | 0.6286      | 0.5108              | 0.4055             | 0.3102              | 0.2231             | 0.1431              | 0.0690      |

| 0.3V <sub>DD</sub>  | 0.8473      | 0.6931       | 0.5596      | 0.4418              | 0.3365             | 0.2412              | 0.1542             | 0.0741              | -           |

From equation 1,  $R_{up(min)} = 5.5 \text{V}/3\text{mA} = 1.83 \text{ k}\Omega$  to operate the bus under a 5-V pull-up voltage and provide less than 3 mA when the  $I^2C$  device is driving the bus to a low state. If a higher sink current, for example 4 mA, is allowed,  $R_{up(min)}$  can be as low as 1.375 k $\Omega$ .

Given a 5-V  $I^2C$  device with input low and high threshold voltages at 0.3  $V_{dd}$  and 0.7  $V_{dd}$ , the valued of k is 0.8473 from Table 1. Taking into account the 1.83-k $\Omega$  pull-up resistor, the maximum total load capacitance is  $C_{(total-5V)} = 645$  pF.  $C_{cable(max)}$  should be restricted to be less than 545 pF if  $C_{source}$  and  $C_i$  can be as heavy as 50 pF. Here the  $C_i$  is treated as  $C_{sink}$ , the load capacitance of a sink device.

Fixing the maximum transition time from Table 1,  $T = 1 \mu s$ , and using the k values from Table 1, the recommended maximum total resistance of the pull-up resistors on an  $I^2C$  bus can be calculated for different system setups.

To support the maximum load capacitance specified in the HDMI spec,  $C_{cable(max)} = 700 pF/C_{source} = 50 pF/C_i = 50 pF$ ,  $R_{(max)}$  can be calculated as shown in Table 2.

Table 2. Pull-Up Resistor Upon Different Threshold Voltages and 800-pF Loads

| $V_{th}-V_{th+}$    | $0.7V_{\mathrm{DD}}$ | 0.65V <sub>DD</sub> | 0.6V <sub>DD</sub> | 0.55V <sub>DD</sub> | $0.5V_{DD}$ | 0.45V <sub>DD</sub> | 0.4V <sub>DD</sub> | 0.35V <sub>DD</sub> | 0.3V <sub>DD</sub> | UNIT |

|---------------------|----------------------|---------------------|--------------------|---------------------|-------------|---------------------|--------------------|---------------------|--------------------|------|

| 0.1V <sub>DD</sub>  | 1.14                 | 1.32                | 1.54               | 1.80                | 2.13        | 2.54                | 3.08               | 3.84                | 4.97               | kΩ   |

| 0.15V <sub>DD</sub> | 1.20                 | 1.41                | 1.66               | 1.97                | 2.36        | 2.87                | 3.59               | 4.66                | 6.44               | kΩ   |

| $0.2V_{DD}$         | 1.27                 | 1.51                | 1.80               | 2.17                | 2.66        | 3.34                | 4.35               | 6.02                | 9.36               | kΩ   |

| $0.25V_{DD}$        | 1.36                 | 1.64                | 1.99               | 2.45                | 3.08        | 4.03                | 5.60               | 8.74                | 18.12              | kΩ   |

| 0.3V <sub>DD</sub>  | 1.48                 | 1.80                | 2.23               | 2.83                | 3.72        | 5.18                | 8.11               | 16.87               | -                  | kΩ   |

Or, limiting the maximum load capacitance of each cable to be 400 pF to accommodate with  $I^2C$  spec version 2.1.  $C_{cable(max)} = 400 pF/C_{source} = 50 pF/C_i = 50 pF$ , the maximum values of  $R_{(max)}$  are calculated as shown in Table 3.

Table 3. Pull-Up Resistor Upon Different Threshold Voltages and 500-pF Loads

| $V_{th}-V_{th+}$    | $0.7V_{DD}$ | $0.65V_{DD}$ | $0.6V_{DD}$ | 0.55V <sub>DD</sub> | 0.5V <sub>DD</sub> | 0.45V <sub>DD</sub> | 0.4V <sub>DD</sub> | 0.35V <sub>DD</sub> | $0.3V_{DD}$ | UNIT |

|---------------------|-------------|--------------|-------------|---------------------|--------------------|---------------------|--------------------|---------------------|-------------|------|

| 0.1V <sub>DD</sub>  | 1.82        | 2.12         | 2.47        | 2.89                | 3.40               | 4.06                | 4.93               | 6.15                | 7.96        | kΩ   |

| 0.15V <sub>DD</sub> | 1.92        | 2.25         | 2.65        | 3.14                | 3.77               | 4.59                | 5.74               | 7.46                | 10.30       | kΩ   |

| 0.2V <sub>DD</sub>  | 2.04        | 2.42         | 2.89        | 3.48                | 4.26               | 5.34                | 6.95               | 9.63                | 14.98       | kΩ   |

| 0.25V <sub>DD</sub> | 2.18        | 2.62         | 3.18        | 3.92                | 4.93               | 6.45                | 8.96               | 13.98               | 28.99       | kΩ   |

| 0.3V <sub>DD</sub>  | 2.36        | 2.89         | 3.57        | 4.53                | 5.94               | 8.29                | 12.97              | 26.99               | -           | kΩ   |

Obviously, to accommodate the 3-mA drive current specification, a narrower threshold voltage range is required to support a maximum 800-pF load capacitance for a standard-mode I<sup>2</sup>C bus.

When the input low and high level threshold voltages,  $V_{th-}$  and  $V_{th+}$ , are 0.7 V and 1.9 V, which is 0.15  $V_{DD}$  and 0.4  $V_{DD}$  approximately with  $V_{DD}$  = 5 V, from Table 2, the maximum pull-up resistor is 3.59 k $\Omega$ . The allowable pull-up resistor is in the range of 1.83 k $\Omega$  and 3.59 k $\Omega$ .

#### **Thermal Dissipation**

On a high-K board – It is always recommended to solder the PowerPAD™ onto the thermal land. A thermal land is the area of solder-tinned-copper underneath the PowerPAD package. On a high-K board the TMDS141 can operate over the full temperature range by soldering the PowerPAD onto the thermal land without vias.

On a low-K board – In order for the device to operate across the temperature range on a low-K board, a 1-oz Cu trace connecting the GND pins to the thermal land must be used. A simulation shows  $R_{\theta JA} = 100.84$ °C/W allowing 545 mW power dissipation at 70°C ambient temperature.

A general PCB design guide for PowerPAD packages is provided in the document SLMA002 - PowerPAD Thermally Enhanced Package.

Product Folder Link(s): TMDS141

## **REVISION HISTORY**

| Ch | anges from Revision A (August 2006) to Revision B                                                                                                                                                                                                                                 | Page     |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| •  | Changed Features                                                                                                                                                                                                                                                                  | 1        |

| •  | Changed Signaling rate from 1.65 Gbps to 2.25 Gbps                                                                                                                                                                                                                                | 6        |

| •  | Added PRE = Low to supply current test conditions                                                                                                                                                                                                                                 | <b>7</b> |

| •  | Added PRE = Low to power dissipation test conditions                                                                                                                                                                                                                              | <b>7</b> |

| •  | Deleted TTL high- and low-level output voltages                                                                                                                                                                                                                                   | <b>7</b> |

| •  | Changed Peak-to-peak output jitter from TX0 - TX2, residual jitter from 90 to 88 ps                                                                                                                                                                                               | 8        |

| •  | Added Peak-to-peak output jitter from TXC, residual jitter                                                                                                                                                                                                                        | 8        |

| •  | Added Peak-to-peak output jitter from TX0 - TX2, residual jitter                                                                                                                                                                                                                  | 8        |

| •  | Changed Figure 11                                                                                                                                                                                                                                                                 | 13       |

| •  | Changed Figure 12                                                                                                                                                                                                                                                                 | 13       |

| •  | Changed Figure 13                                                                                                                                                                                                                                                                 | 13       |

| •  | Changed Figure 14                                                                                                                                                                                                                                                                 | 13       |

| •  | Changed Figure 15                                                                                                                                                                                                                                                                 | 14       |

| Ch | anges from Revision B (April 2007) to Revision C                                                                                                                                                                                                                                  | Page     |

| •  | Added Feature - Accepts AC Couple DisplayPort Dual-Mode Signals and Translates Them into a HDMI1.3a Compatable TMDS Signal                                                                                                                                                        | 1        |

| •  | Added Application - DisplayPort Level Translator                                                                                                                                                                                                                                  | 1        |

| •  | Changed SWITCHING CHARACTERISTICS - t <sub>sk(D)</sub> max from 60 to 35 ps                                                                                                                                                                                                       | 8        |

| Ch | anges from Revision C (June 2007) to Revision D                                                                                                                                                                                                                                   | Page     |

| •  | Changed the first Features list item From: Supports 2.25 Gbps Signaling Rate for 480i/p, 720i/p, and 1080i/p Resolution to 12-Bit Color Depth To: Supports 2.25 Gbps Signaling Rate for up to 1080p Resolutions Supporting 36-bits Per Pixel for Color Depth of 12-bits Per Color | 1        |

## PACKAGE OPTION ADDENDUM

6-Feb-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | _       | Pins | _    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| TMDS141RHAR      | ACTIVE | VQFN         | RHA     | 40   | 2500 | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-3-260C-168 HR | 0 to 70      | TMDS141        | Samples |

| TMDS141RHARG4    | ACTIVE | VQFN         | RHA     | 40   | 2500 | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-3-260C-168 HR | 0 to 70      | TMDS141        | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

6-Feb-2020

PACKAGE MATERIALS INFORMATION

www.ti.com 22-Jan-2015

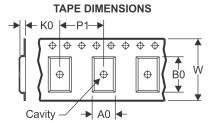

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

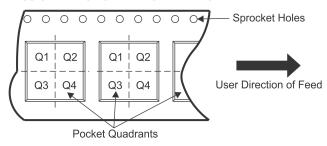

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

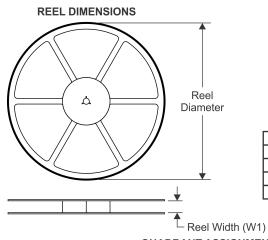

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TMDS141RHAR | VQFN            | RHA                | 40 | 2500 | 330.0                    | 16.4                     | 6.3        | 6.3        | 1.1        | 12.0       | 16.0      | Q2               |

www.ti.com 22-Jan-2015

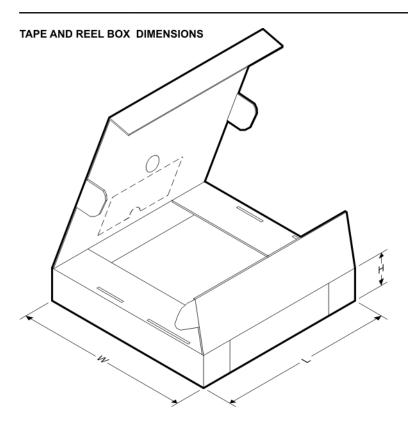

#### \*All dimensions are nominal

| ĺ | Device Package Type |      | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|---------------------|------|-----------------|------|------|-------------|------------|-------------|--|

|   | TMDS141RHAR         | VQFN | RHA             | 40   | 2500 | 367.0       | 367.0      | 38.0        |  |

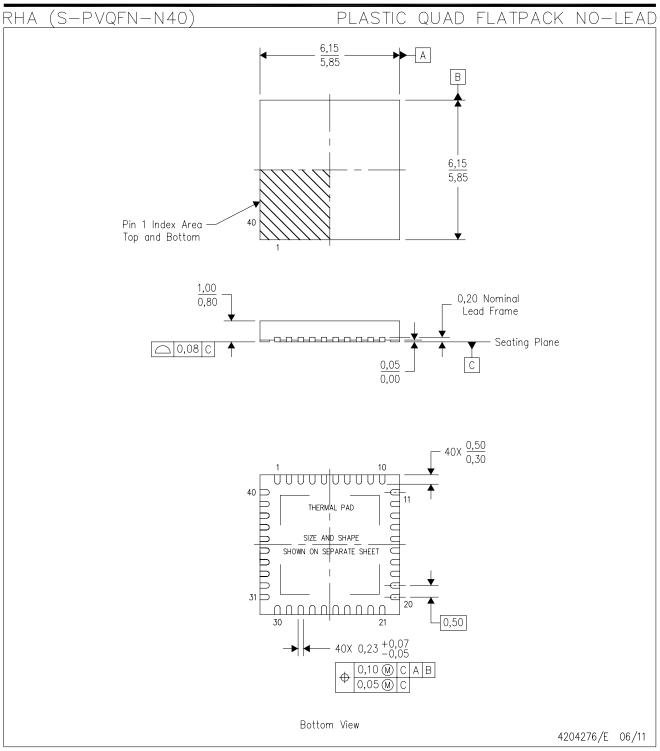

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) Package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Package complies to JEDEC MO-220 variation VJJD-2.

# RHA (S-PVQFN-N40)

# PLASTIC QUAD FLATPACK NO-LEAD

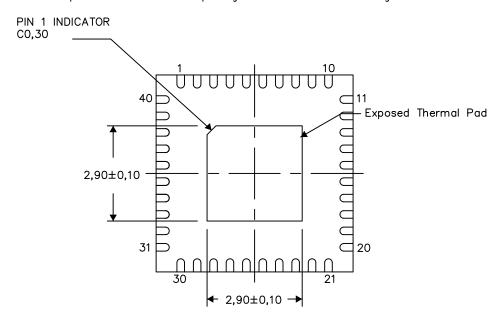

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

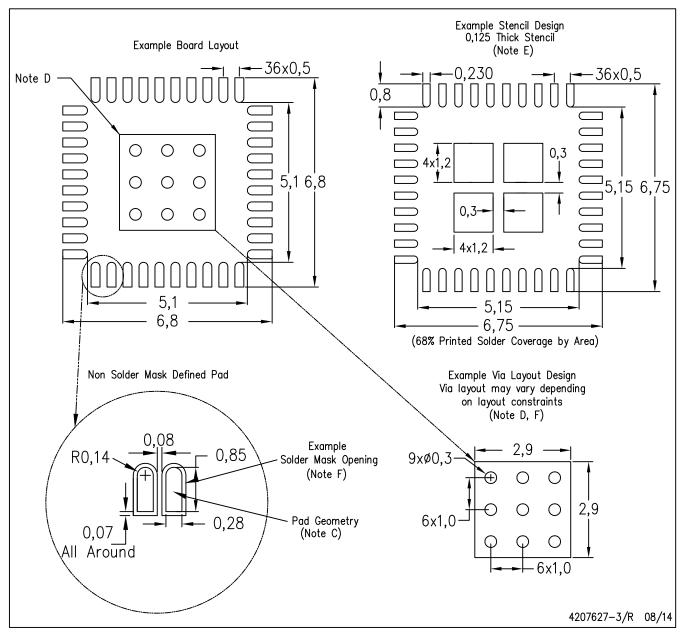

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

Exposed Thermal Pad Dimensions

4206355-3/X 08/14

NOTES: A. All linear dimensions are in millimeters

# RHA (S-PVQFN-N40)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated